• Plug-in replacement for Static RAM chips

• Retains data for up to 10 years

· No erasure required

• Functions as Data or Program RAM

No limit to number of programming cycles

• Fits standard 24-pin socket

NVR2 is a 2 kilobyte non-volatile memory module which is pincompatible with normal Static RAM chips, and offers immediate conversion to non-volatile memory of all or part of a system, able to retain data and survive power-downs for up to 10 years.

REPLACES: 2016 6116 8416 5517 4016

2128 5128 PD446 8128 4802

5116 etc.

#### **MAXIMUM RATINGS**

| Symbol           | Min  | Max                | Unit      |

|------------------|------|--------------------|-----------|

| V <sub>dd</sub>  | -0.3 | 7.0                | Volts     |

| V <sub>i/o</sub> | -0.3 | V <sub>dd</sub> +0 | 0.3 Volts |

| Temp.            | -10  | + 70               | deg. C    |

#### **OPERATING CONDITIONS**

| Symbol                             | Min | Тур | Max          | Unit |

|------------------------------------|-----|-----|--------------|------|

| $V_{dd}$                           | 4.5 | 5.0 | 5.5          | ٧    |

| V <sub>in</sub> (1)                | 2.2 |     | $V_{dd} + 3$ | ٧    |

| V <sub>in</sub> (0)                | 3   |     | 0.8          | ٧    |

| I <sub>in</sub> (any pin)*         | -1  |     | + 1          | uA   |

| $V_{out}$ (1) ( $I_{out} = -1mA$ ) | 2.4 |     |              | V    |

| $V_{out}$ (0) ( $I_{out} = -2mA$ ) |     |     | 0.4          | V    |

| I <sub>dd</sub> (Active)           |     | 25  |              | mΑ   |

| I <sub>dd</sub> (Standby)          |     | 5   |              | uA   |

| T <sub>cycle</sub>                 |     |     | 200          | nS   |

| C <sub>in</sub> (any pin)          |     | 7   |              | рF   |

\*INH: 4 70 kohm pull-up to V<sub>dd</sub>

#### **FUNCTION MODE**

| INH | CE |     | R MODE | OUTPUT           | l <sub>dd</sub> |

|-----|----|-----|--------|------------------|-----------------|

| X   | Н  | ΧХ  | Unsel. | Hi-Z             | Standby         |

| Х   | L  | н н | Unsel. | Hi-Z             | Active          |

| Х   | L  | L H | Read   | D <sub>out</sub> | Active          |

| H   | L  | ΧL  | Write  | D <sub>in</sub>  | Active          |

| L   | L  | ΧL  | WRITE  | INHIBIT          | Active          |

REPRESENTATIVE/IMPORTER

3401 MONRO€ RD. • CHARLOTTE, NC 28205 (704) 376-7805, TELEX: 358-905

## 2K x 8 NON-VOLATILE RAM

# NVR2

| Dimensions | mm   |

|------------|------|

| Length     | 32.5 |

| Width      | 18   |

| Height     | 7.3  |

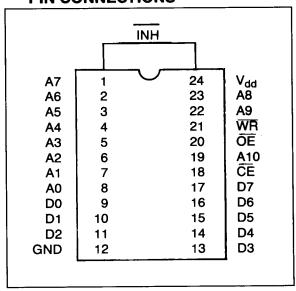

#### **PIN DESIGNATIONS**

| Pin Function  A0-A10 Address I/Ps  D0-D7 Data in/out  OE Output Enable  CE Chip Enable |

|----------------------------------------------------------------------------------------|

| D0-D7 Data in/out  OE Output Enable  CE Chip Enable                                    |

| OE Output Enable CE Chip Enable                                                        |

| CE Chip Enable                                                                         |

|                                                                                        |

| TATES NATIONAL Discussion                                                              |

| WR Write Input                                                                         |

| V <sub>dd</sub> +5V power                                                              |

| GND Ground                                                                             |

| INH Extra I/P                                                                          |

#### **PIN CONNECTIONS**

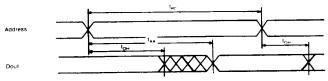

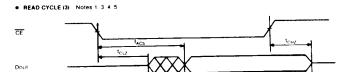

### TIMING DIAGRAMS (units — nano-seconds)

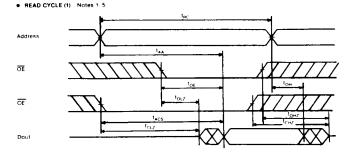

#### **READ CYCLE**

| Characteristic       | Label            | Min | Max |

|----------------------|------------------|-----|-----|

| Read cycle time      | T <sub>rc</sub>  | 200 |     |

| Address to O/P valid | Taa              |     | 200 |

| CE to O/P valid      | Tacs             |     | 200 |

| OE to O/P valid      | T <sub>oe</sub>  |     | 100 |

| Output hold time     | Toh              | 20  |     |

| CE to O/P enable     | T <sub>clz</sub> | 10  |     |

| OE to O/P enable     | Tolz             | 10  |     |

| CE to O/P disable    | T <sub>chz</sub> | 100 |     |

| OE to O/P disable    | T <sub>ohz</sub> | 100 |     |

(EOW = End of Write)

#### **NOTES — READ CYCLE**

- 1. WE is high for read cycle.

- 2. Device is continuously selected,  $CE = V_{il}$ .

- 3. Address valid prior to or coincident with CE transition low.

- 4. OE =  $V_{ij}$ .

- 5. When CE is low, address inputs must not be in the high impedace state.

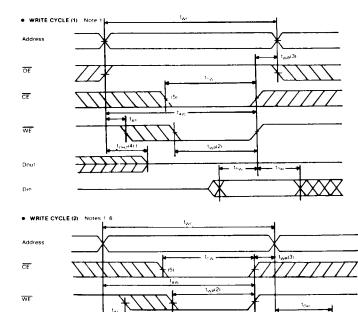

#### WRITE CYCLE

| Characteristic    | Label            | Min | Max |

|-------------------|------------------|-----|-----|

| Write cycle time  | T <sub>wc</sub>  | 200 |     |

| CE to EOW         | T <sub>cw</sub>  | 170 |     |

| Addr valid to EOW | Taw              | 170 |     |

| Addr set-up time  | Tas              | 0   | }   |

| Write pulse width | T <sub>wp</sub>  | 170 |     |

| WR recovery time  | Twr              | 0   |     |

| Data valid to EOW | T <sub>dw</sub>  | 100 |     |

| Data hold time    | T <sub>dh</sub>  | 0   |     |

| WR to O/P disable | T <sub>whz</sub> |     | 100 |

| OE from EOW       | Tow              | 20  |     |

| OE to O/P disable | Tohz             | 0   |     |

#### **NOTES — WRITE CYCLE**

- 1. WE must be high during address transitions.

- 2. A Write occurs during the overlap of a low CE and a low WE.

- 3. Twr measured from the earlier of CE or WE going high to end of write cycle.

- 4. During this period, I/O pins are in the O/P state.

- 5. If a CE low transition occurs simultaneously with or after a WE transition, O/Ps remain in a high impedance state.

- 6.  $\overline{OE}$  is continuously low  $(\overline{OE} = V_{ii})$ .

- 7. Dout is the same phase of write data of this write cycle.

- 8.  $D_{out}$  is the read data of next address.

MAY 2 5 1993

9. If CE is low during this period, I/O pins are in the output state. 036885 🛂

2