## **DIGITAL TUNING SYSTEM**

## **DESCRIPTION**

The SC9318-033 is a single-chip digital tuning system optimum for portable sets such as headphone radio, etc... 5-band of FM/MW/LW/TV/SW are provided compatibly with worldwide destinations.

#### **FEATURE**

#### **Tuning function:**

- Manual tuning (up/down)

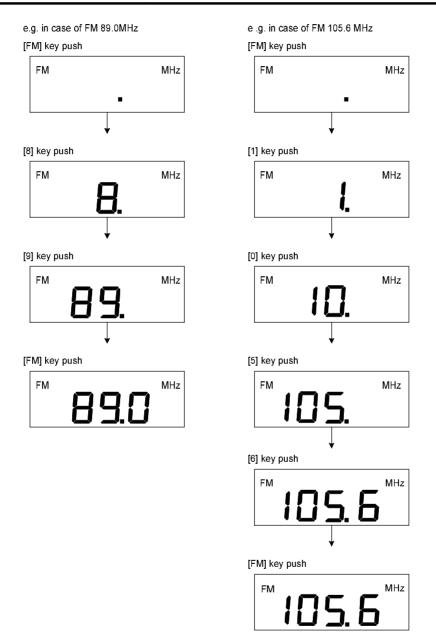

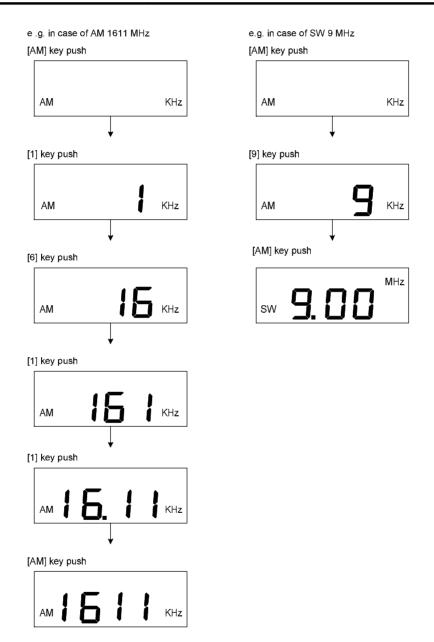

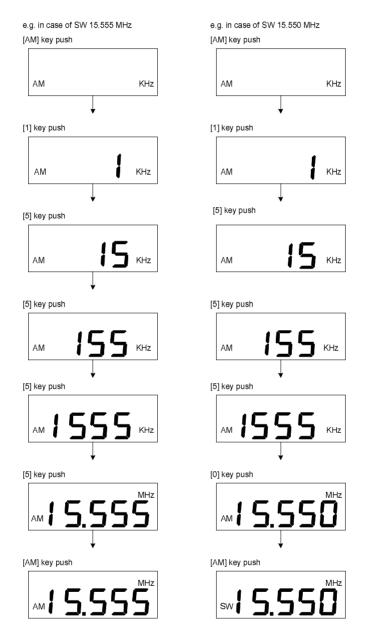

- Direct tuning

- Seek tuning

#### Memory function:

• FM/MW/LW or TV/SW/WB each band 10 stations

#### **Clock function:**

- Dual clock function

- 12/24H clock

- Sleep timer function

- Alarm timer function

#### Other function:

Battery check input

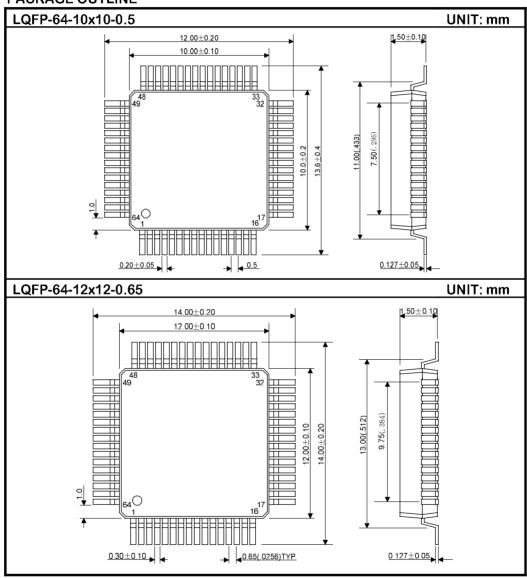

## ORDERING INFORMATION

| Device   | Package            |

|----------|--------------------|

| SC9318FA | LQFP-64-10x10-0.5  |

| SC9318FB | LQFP-64-12x12-0.65 |

----- HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD ---

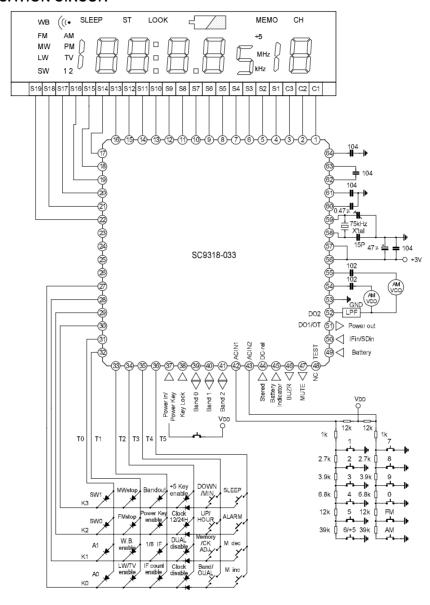

## **PIN CONFIGURATION**

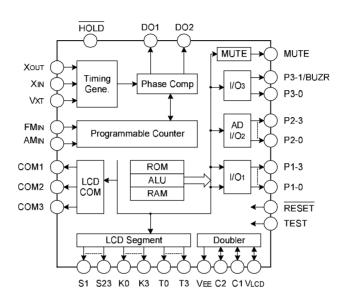

## **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATING**

| Characteristic        | Symbol | Value         | Unit |

|-----------------------|--------|---------------|------|

| Supply Voltage        | VDD    | 1.3           | V    |

| Input Voltage         | VIN    | -0.3~ VDD+0.3 | V    |

| Power Dissipation     | PD     | 100           | mW   |

| Operating Temperature | Topr   | -10~60        | °C   |

| Storage Temperature   | Tstg   | -55~125       | °C   |

## ELECTRICAL CHARACTERISTICS (Tamb=25°C, VDD =3.0V, unless otherwise specified)

| Characteristic                    | Symbol | Test Condition                                             | MIN | TYP | MAX | Unit |

|-----------------------------------|--------|------------------------------------------------------------|-----|-----|-----|------|

| Range of Operating Supply Voltage | VDD    | *                                                          | 1.8 | 3.0 | 3.6 | ٧    |

| Range of Memory Retention Voltage | VHD    | * Crystal oscillation stopped (CKSTP instruction executed) | 1.0 | _   | 3.6 | mA   |

(To be continued)

(Continued)

| Characteristic                               | Symbol        | Test Condition                                                                         | MIN  | TYP | MAX         | Unit      |

|----------------------------------------------|---------------|----------------------------------------------------------------------------------------|------|-----|-------------|-----------|

|                                              | IDD4          | Under ordinary operation and PLL on operation, on output VDD=3V load FMIN=230MHz input |      | 7.0 | 12          |           |

| 0                                            | IDD1          | Under ordinary operation and PLL on operation, no output load FMIN=130MHz input        |      | 6.0 | 10          |           |

| Operating Current                            | IDD2          | Under CPU operation only (PLL off, display turned on)                                  |      | 40  | 80          |           |

|                                              | IDD3          | Soft wait mode (crystal oscillator, display circuit operating, CPU stopped, PLL off)   |      | 25  | 50          | μΑ        |

|                                              | IDD4          | Hard wait mode (crystal oscillator operating only)                                     |      | 15  | 30          |           |

| Memory Retention Current                     | IHD           | Crystal oscillation stopped (CKSTP instruction executed)                               |      | 0.1 | 10          |           |

| Crystal Oscillation<br>Frequency             | fXT           | *                                                                                      |      | 75  |             | kHz       |

| Crystal Oscillation<br>Startup Time          | tst           | Crystal oscillation fXT=75kHz                                                          |      |     | 1.0         | S         |

| Voltage Doubler Circui                       | it            |                                                                                        |      |     |             |           |

| Voltage Doubler<br>Reference Voltage         | VEE           | GND reference (VEE)                                                                    | 1.3  | 1.5 | 1.7         | V         |

| Constant Voltage Temperature Characteristics | DV            | GND reference (VEE)                                                                    |      | -5  | -           | mV/º<br>C |

| Voltage Doubler<br>Boosting Voltage          | VLCD          | GND reference (VLCD)                                                                   | 2.6  | 3.0 | 3.4         | V         |

| Operating frequency ra                       | anges for pro | ogrammable counter and IF counter                                                      |      |     |             |           |

| FMIN (VHF Mode)                              | f∨HF          | Sine wave input when VIN =0.2Vp-p                                                      | 50   | ~   | 230         |           |

| FMIN (FM Mode)                               | fFM           | Sine wave input when VIN =0.2Vp-p                                                      | 40   | ~   | 130         |           |

| AMIN (HF Mode)                               | fHL           | Sine wave input when VIN =0.2Vp-p                                                      | 1    | ~   | 45          | MHz       |

| AMIN (LF Mode)                               | fLF           | Sine wave input when VIN =0.2Vp-p                                                      | 0.5  | ~   | 12          |           |

| IFIN                                         | fIF           | Sine wave input when VIN =0.2Vp-p                                                      | 0.35 | ~   | 12          |           |

| Input Amplitude                              | VIN           | FMIN, AMIN, IFIN input                                                                 | 0.2  | ~   | VDD<br>-0.8 | Vp-p      |

(To be continued)

## (Continued)

| Chara                     | Characteristic Symbo |              | Test Condition                              |      | TYP  | MAX         | Unit |

|---------------------------|----------------------|--------------|---------------------------------------------|------|------|-------------|------|

| LCD com                   | mon output/s         | segment outp | out (COM1~COM3, S1~S23)                     |      |      |             |      |

| Output                    | "H" Level            | IOH1         | VLCD =3V, VOH=2.7V                          | -0.5 | -1.0 |             | mΑ   |

| Current                   | "L" Level            | IOL1         | VLCD =3V, VOH =0.3V                         | 0.5  | 1.0  |             | IIIA |

| Output V                  | oltage 1/2           | VBS          | No load                                     | 1.3  | 1.5  | 1.7         | V    |

| Level                     |                      | VDS          | NO IOAO                                     | 1.3  | 1.0  | 1.7         | v    |

| HOLD in                   | put port             |              |                                             |      |      |             |      |

| In put Lea                | ak Current           | ILI          | VIH=3.0V, VIL=0V                            |      | -    | ±1.0        | μΑ   |

| Input                     | "H" Level            | VIH1         | -                                           | 2.4  | ~    | 3.0         | v    |

| Voltage                   | Voltage "L" Level V  |              | -                                           | 0    | ?    | 1.2         | V    |

| A/D (N) c                 | onverter (A/D        | DIN2, DC-RE  | F)                                          |      |      |             |      |

| Analog In<br>Voltage F    | •                    | VAD          | ADIN1, ADIN2                                | 0    | ~    | VDD         | ٧    |

| Analog R<br>Voltage F     |                      | VREF         | DC-REF, VDD =2.0~3.6V                       | 1.0  | ~    | VDD<br>×0.9 | V    |

| Resolution                |                      | VRES         |                                             |      | 6.0  |             | bit  |

| Conversion Total<br>Error |                      |              | VDD =2.0~3.6V                               |      | ±1.0 | ±4.0        | LSB  |

| Analog In                 | put Leak             | lLi          | VIH=3.0V, VIL=0V<br>(ADIN1, ADIN2, DC-REF)  |      | -    | ±1.0        | μΑ   |

| KEY inpu                  | t port (K0~K         | 3)           | ,                                           | 1    |      | ı           |      |

| N-ch/P-ch<br>Resistan     | •                    | RIN1         |                                             | 75   | 150  | 300         | kΩ   |

| Input                     | "H" Level            | VIH2         | When input with pull-down resistance        | 1.8  | ~    | 3.0         | V    |

| Voltage                   | "L" Level            | VIL2         | When input with pull-down resistance        | 0    | ~    | 0.3         |      |

| Input                     | "H" Level            | VIH3         | When input with pull-up resistance          | 2.7  | ~    | 3.0         | V    |

| Voltage                   | "L" Level            | VIL3         | When input with pull-up resistance          | 0    | ~    | 1.2         |      |

| Input Leak Current        |                      | <b>I</b> LI  | When input resistance off, VIH=3.0V, VIL=0V | -    | -    | ±1.0        | μΑ   |

| Timing ou                 | utput port (T0       | )~T5)        |                                             |      |      |             |      |

| Output                    | "H" Level            | IOH1         | VOH =2.7V                                   | -0.5 | -1.0 |             | m A  |

| Current                   | "L" Level            | IOL1         | VOL=0.3V,Use LCD key-return mode            | 0.5  | 1.0  |             | mA   |

| N-ch Loa<br>Resistan      | -                    | lπL          | No used LCD key-return mode                 | 75   | 150  | 300         | kΩ   |

(To be continued)

| (Cnr | tini | Ind) |

|------|------|------|

| Characteristic                                   |                           | Symbol       | Test Condition     | MIN  | TYP     | MAX  | Unit           |

|--------------------------------------------------|---------------------------|--------------|--------------------|------|---------|------|----------------|

| DO1/OT,                                          | DO2 output;               | MUTE outpu   | ıt                 |      |         |      |                |

| Output                                           | "H" Level                 | IOH1         | VOH =2.7V          | -0.5 | -1.0    |      | m <sub>A</sub> |

| Current                                          | "L" Level                 | lOL1         | Vol =0.3V          | 0.5  | 1.0     |      | IIIA           |

| Output Off Leak                                  |                           | IπL          | VTLH=3.0V, VTLL=0V |      |         | ±100 | l nA           |

| Current                                          |                           | ! ILE        | (DO1, DO2)         |      |         | ±100 | _ ''^          |

| General-                                         | purpose I/O p             | orts (P1-0~F | 23-1)              |      |         |      |                |

| Output                                           | "H" Level                 | IOH1         | VOH =2.7V          | -0.5 | -1.0    |      | m <sub>A</sub> |

| Current                                          | "L" Level                 | IOL1         | VoL =0.3V          | 0.5  | 1.0     |      | ША             |

| Input Le                                         | t "H" Level VIH4 24 ~ 3.0 |              | μΑ                 |      |         |      |                |

| Input                                            | "H" Level                 | VIH4         |                    | 2.4  | ~       | 3.0  | <sub>V</sub>   |

| Voltage                                          | /oltage "L" Level         |              |                    | 0    | ~       | 0.6  | _ v            |

| IN, RESE                                         | <br>ET input port         |              |                    |      |         |      |                |

| Input Le                                         | ak Current                | ILI          | VIH=3.0V, VIL=0V   |      |         | ±1.0 | μА             |

| Input                                            | "H" Level                 | VIH4         | -                  | 2.4  | ~       | 3.0  | ] ,,           |

| Voltage                                          | oltage "L" Level VIL4     |              | -                  | 0    | 0 ~ 0.6 | 0.6  | V              |

| Others                                           |                           |              |                    |      |         |      |                |

| Input Pull<br>Resistan                           |                           | RIN2         | (TEST)             | 25   | 50      | 100  | kΩ             |

| XIN Amp<br>Resistan                              | Feedback<br>ce            | RfXT         | (XIN-XOUT)         |      | 20      | 1    | МΩ             |

| XOUT Ou<br>Resistan                              | •                         | Rout         | (ХОИТ)             |      | 3       | ŀ    | kΩ             |

| Input Am                                         | p Feedback                | RfIN1        | (FMIN, AMIN)       | 150  | 300     | 600  | 1.0            |

| Resistance                                       |                           | RfIN2        | (IFIN)             | 500  | 1000    | 2000 | kΩ             |

| Voltage Used to<br>Detect Supply<br>Voltage Drop |                           | VSTP         | VDD                | 1.3  | 1.5     | 1.6  | V              |

|                                                  | oltage Drop<br>n<br>ture  | DS           | VDD                |      | -2      |      | mV/°C          |

## **PIN DESCRIPTION**

| Pin<br>No. | Symbol       | Pin Name                            | Internal<br>Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | COM1         |                                     | N.CD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output common signal to the LCD panel.  Through a matrix with pins S1~S23, a maximum of 69 segments can be displayed.                                                                                                                                                                                                                                                           |

| 2          | COM2         | LCD common output                   | VEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Three levels, VLCD, VEE, and GND, are output at 83Hz every 2ms. VEE is output after                                                                                                                                                                                                                                                                                             |

| 3          | СОМ3         |                                     | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SYSTEM RESET and CLOCK STOP are released, and a common signal is output after the DISP OFF bit is set to "0".                                                                                                                                                                                                                                                                   |

| 4~18       | S1~S15       | LCD segment<br>output               | V.c.o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Segment signal output pins for the LCD panel. Together with COM1, COM2, and COM3, a matrix is formed that can display a maximum of 69 segments. The signals for the key matrix                                                                                                                                                                                                  |

| 19~26      | S16/KR7<br>~ | LCD segment output/Key              | S16/KR7~S23/KR0 are output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | and the segment signals from pins S16/KR7~S23/KR0 are output on a time division basis. 4 X 8=32 key matrix can be                                                                                                                                                                                                                                                               |

|            | S23/KR0      | return timing<br>output             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | created in conjunction with key input ports K0~K3.                                                                                                                                                                                                                                                                                                                              |

| 27~30      | K0~K3        | Key input<br>ports                  | THE THE PERSON OF THE PERSON O | 4 bit input ports for key matrix input. Combined in a matrix with key return timing outputs the LCD segment pins, data from a maximum of 4X8=32 keys can be input and pins are pulled up. On the key setting output pin, data from 4X6=24 keys can be input and pins are pulled down. The WAIT mode is released when high level is applied to key input ports set to pull-down. |

| 31~36      | T0~T5        | Key return<br>timing output<br>port | Row Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | These ports output the timing signal for key matrix. To form the key matrix, load resistance has been built-in the N-channel side. When the key matrix combined with push-key that does not need a key matrix diode.                                                                                                                                                            |

(To be continued)

|   | _      | 4.       | 11     |  |

|---|--------|----------|--------|--|

| • | 1 'n   | ntır     | nued)  |  |

| 1 | $\sim$ | 1 1 [ 11 | IUCU I |  |

| Pin No. | Symbol                                                      | Pin Name                                                                                                | Internal<br>Connection                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37~40   | P1-0<br>~<br>P1-3                                           | I/O port 1                                                                                              |                                         | The input and output of these 4 bit I/O ports can be programmed in 1 bit units. By altering the input to I/O ports set to input, the CLOCK STOP and WAIT modes can be released, and the MUTE bit of the MUTE pin can be set to "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 41~44   | P2-0<br>P2-1/<br>ADIN1<br>P2-2/<br>ADIN2<br>P2-3/<br>DC-REF | I/O port 2<br>/AD analog<br>voltage input<br>/AD analog<br>voltage input<br>/Reference<br>voltage input | To A/D converter (P2-0 pin is excluded) | 4 bit I/O ports. Input and output may be programmed in 1 bit units. Pins P2-1 through P2-2 can also be used for analog input to the built-in 6 bit, 2-channel A/D converter. Conversion time of the built-in A/D converter using the successive comparison method is 280μs. The necessary pin can be programmed to A/D analog input in 1 bit units, and P2-3 can be set to the reference voltage input. Internal power supply (VDD) or constant voltage (VEE) can be used as the reference voltage. In addition, constant voltage (VEE) can be input to the A/D analog input so battery voltage, etc., can be easily detected. The reference voltage input, for which a built-in operational amp is used, has high impedance. The A/D converter, and their control are all executed by program. |

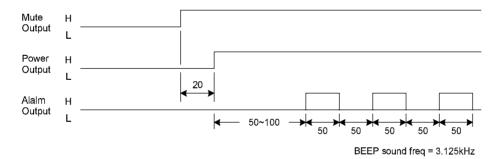

| 45~46   | P3-0<br>P3-1/<br>BUZR                                       | I/O port 3<br>/Buzzer<br>output                                                                         |                                         | 2 bit I/O ports, whose input/output can be programmed in 1 bit units.  The P3-1 pin also functions as the output for the built-in buzzer circuit. The buzzer sound can be output in 254 different tones between 18.75kHz and 147Hz, and at a duty of 50%.  The buzzer output, and all associated controls can be programmed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

— HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD ——

| (Continue  | (Continued) |                            |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|------------|-------------|----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin<br>No. | Symbol      | Pin Name                   | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

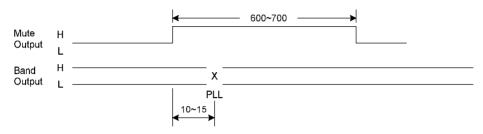

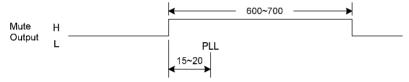

| 47         | MUTE        | Muting output<br>port      |                        | 1 bit output port. Normally, this port is used for muting control signal output. This pin can set the internal MUTE bit to "1" according to a change in the input of I/O port 1. MUTE bit output logic can be changed; PLL phase difference can also be output using this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 49         | HOLD        | HOLD mode<br>control input |                        | Input pin for request/release HOLD mode.  Normally, this pin is used to input radio mode selection signals or battery detection signals.  HOLD mode includes CLOCK STOP mode (stops crystal oscillation) and WAIT mode (halts CPU). Setting is implemented with the CKSTP instruction or the WAIT instruction. When the CKSTP instruction is executed, request/release of the HOLD mode depends on the internal MODE bit. If the MODE bit is "0" (MODE-0), executing the CKSTP instruction while the HOLD pin is at low level stops the clock generator and the CPU and changes to memory back-up mode. If the MODE bit is "1" (MODE-1), executing the CKSTP instruction enters memory back-up mode regardless of the level of the HOLD pin. Memory back-up is release when the HOLD pin goes high in MODE-0, or when the level of the HOLD pin low in MODE-1.  When memory back-up mode is entered by executing a WAIT instruction, any change in the HOLD pin input releases the mode.  In memory back-up mode, current consumption is low (below 10µA), and all the output pins (e.g., display output, output ports) are automatically set to low level. |  |  |  |  |

| (Continue | d) |  |

|-----------|----|--|

|           |    |  |

| Pin No. | Symbol  | Pin Name                                      | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|---------|-----------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48      | TEST    | TEST mode<br>control input                    | RINZ -                 | Input pin used for controlling TEST mode. High level indicates TEST mode, while low level indicates normal operation. The pin is normally used at low level or no-connection (NC). (A pull-down resistor is built-in).                                                                                                                                                                                                                                                                                                        |

| 50      | IFIN/IN | IF signal<br>input/Input<br>port              | Rinn2                  | IF counter's IF signal input for counting the IF signals of the FM and AM bands and detecting the automatic stop position.  The input frequency is between 0.35~12MHz (0.2VP-P(Min)). A built-in input amp and C coupling allow operation at low-level input.  The IF counter is a 20 bit counter with optional gate times of 1, 4, 16, and 64ms. 20 bit of data can be readily stored in memory.  This input pin can be programmed for use as an input port (IN port). CMOS input is used when the pin is set as an IN port. |

| 51      | DO1/OT  | Phase<br>comparison<br>output /Output<br>port |                        | PLL's phase comparison tri-state output pins. When the programmable counter's prescaler output is higher than the reference frequency, output is at high level. When output is lower than the reference frequency, high impedance output is obtained.                                                                                                                                                                                                                                                                         |

| 52      | DO2     | Phase<br>comparison<br>output                 |                        | Because DO1 and DO2 are output in parallel, optimal filter constants can be designed for the FM/VHF and AM bands. Pin DO1 can be programmed to high impedance or programmed as an output port (OT). Thus the pins can be used to improve lock-up time or used as output ports.                                                                                                                                                                                                                                                |

(Continued)

| Pin<br>No. | Symbol | Pin Name                                | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|--------|-----------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56         | VDD    | Power-supply                            | VDD<br>O—              | Pins to which power is applied.  Normally, VDD=1.8~3.6V (3.0V Typ.) is applied.  In back-up mode (when CKSTP instructions are being executed), voltage can be lowered to 1.0V. If voltage falls below 1.5V while the CPU is operating, the CPU stops to prevent malfunction (STOP mode). When the voltage rises above 1.5V, the CPU restarts.  STOP mode can be detected by checking the STOP F/F bit. If necessary, execute initialization or adjust clock by program.    |

| 53         | GND    | Power-supply pins                       | ○ GND                  | When detecting or preventing CPU malfunctions using an external circuit, STOP mode can be invalidated and rendered non-operative by program. In that case, all four bits of the internal TEST port should be set to "1". If more than 1.8V is applied when the pin voltage is 0, the device's system is reset and the program starts from address "0". (power on reset).(Note)  To operate the power on reset, the power supply should start up in 10~100ms.               |

| 54         | FMIN   | FM<br>programmabl<br>e counter<br>input | Rfin2                  | Programmable counter input pin for FM,VHF band. The 1/2+pulse swallow system (VHF mode) and the pulse swallow system (FM mode) are selectable freely by program. At the VHF mode, local oscillation output (VCO output) of 50~230MHz (0.2VP-P(Min)) is input and FM mode, 40~130MHz (0.2VP-P (Min)) is input. A built-in input amp and C coupling allow operation at low-level input. (Note) when in the PLL OFF mode or when set to AMIN input, the input is pulled down. |

(To be continued)

—— HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD ——

#### (Continued)

| Pin<br>No. | Symbol | Pin Name                               | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------|----------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55         | AMIN   | AM local<br>oscillator<br>signal input | Rfin2                  | Programmable counter input pin for AM band. The pulse swallow system (HF mode) and direct dividing system (LF mode) are freely selectable by program. At the HF mode, local oscillation output (VCO output) of 1~45MHz (0.2VP-P(Min)) is input and LF mode, 0.5~12MHz (0.2VP-P(Min)) is input. Built-in input amp operates with low-level input using a C coupling. (Note) When in PLL OFF mode or when set to FMIN input, the input is pulled down. |

| 57         | RESET  | Reset input                            |                        | Input pin for system reset signals.  RESET takes place while at low level; at high level, the program starts from address"0".  Normally, if more than 1.8V is supplied to VDD when the voltage is 0, the system is reset (Power on reset).  Accordingly, this pin should be set to high level during operation.                                                                                                                                      |

| 58         | Xout   |                                        | XOUT () ROUT           | Crystal oscillator pins.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 59         | XIN    |                                        | RIXT                   | A reference 75kHz crystal oscillator is                                                                                                                                                                                                                                                                                                                                                                                                              |

| 60         | VxT    | Crystal<br>oscillator pins             | XIN O                  | connected to the XIN and XOUT pins. The oscillator stops oscillating during CKSTP instruction execution.  The VXT pin is the power supply for the crystal oscillator. A stabilizing capacitor (0.47µF Typ.) is connected.                                                                                                                                                                                                                            |

(To be continued)

| IC. | nnt | inı | ied) |  |

|-----|-----|-----|------|--|

| Pin<br>No. | Symbol | Pin Name                          | Internal<br>Connection | Description                                                                                                                                                                                                                         |

|------------|--------|-----------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61         | VLCD   |                                   |                        | Voltage doubler boosting pin for driving the LCD.  A capacitor (0.1µF Typ.) is connected to boost the voltage.  The VLCD pin outputs voltage (3.0V), which has                                                                      |

| 62         | C1     | Voltage<br>double<br>boosting pin | VICD                   | been doubled from the constant voltage (VEE: 1.5V) using the capacitors connected between C1 and C2. That potential is supplied to the LCD drivers. If the internal VLCD OFF bit is set to "1" by program, an external power supply |

| 63         | C2     |                                   |                        | can be input through the VLCD pin to drive the LCD.  At this time, the VLCD/2 potential, whose VLCD voltage is divided using registers, is output from the C2 pin.                                                                  |

| 64         | VEE    | Constant<br>voltage supply<br>pin |                        | 1.5V constant voltage supply pin for driving the LCD.  A stabilizing capacitor (0.1µF Typ.) is connected. This is a reference voltage for the A/D converter, key input, and the LCD common output's bias potential.                 |

Note: 1. When the device is reset (voltage higher than 1.8V, or when RESET=low-high), I/O ports are set to input,

the pins for I/O ports and additional functions (e.g., A/D converter) are set to I/O port input pins, while the IFIN/IN pins become IF input pins.

- 2. When in PLL OFF mode (when the three bits in the internal reference ports all show "1"), the IFIN and FMIN, AMIN pins are pulled down, and DO1 And DO2 are at high impedance.

- 3. When in CLOCK STOP mode (during execution of CKSTP instruction), the output port and the LCD output pins are all at low level, while the constant voltage circuit (VEE), the voltage doubler circuit (VLCD), and the power supply for the crystal oscillator (VXT) are all off.

- 4. When the device is being reset, the contents of the output ports and internal ports are undefined and initialization by program is necessary.

## **FUNCTIONAL DESCRIPTION**

#### RECEIVING BAND

|                                                     | Band     | Code       |     |                  | Step       | Fref. |        |        |

|-----------------------------------------------------|----------|------------|-----|------------------|------------|-------|--------|--------|

| Area                                                |          | <b>A</b> 1 | A0  | Receiving range  | (Hz)       | (Hz)  | IF(Hz) |        |

|                                                     | FM       |            |     | 87.5~108.0M      | 50/200k    | 25k   | 10.7M  |        |

| 11.5.4                                              | B 41 A / |            |     | 522~1620k        | 9k         | 3k    | 4501   |        |

|                                                     | MW       | 0          | 0   | 520~1710k        | 10k        | 5k    | 450k   |        |

| "1                                                  | TV       |            |     | 2~13ch           | 1ch        | 25k   | 40.714 |        |

|                                                     | WB       |            |     | 162.400~162.550M | 25k        | 12.5k | 10.7M  |        |

|                                                     | FM       |            |     | 87.5~108.0M      | 50/100k    | 25k   | 10.7M  |        |

| General                                             | B 43.07  |            | ,   | 522~1620k        | 9k         | 3k    | 450k   |        |

|                                                     | MW       | 0          | 1   | 520~1620k        | 10k        | 5k    |        |        |

|                                                     | LW       |            |     | 144~281k         | 1k         | 1k    |        |        |

| U.S.A. *1  General  Europe east/Europe *2  Japan *3 | FM       |            | 0   | 65.0~74.0M       | 50k        | 25k   | 10.7M  |        |

|                                                     |          | 1          |     | 87.5~108.0M      | 50k        | 25k   | 10.7M  |        |

|                                                     | MW       |            |     | 531~1611k        | 9k         | 3k    | 450k   |        |

|                                                     | IVIVV    |            |     | 530~1610k        | 10k        | 5k    |        |        |

|                                                     | LW       |            |     | 144~281k         | 1k         | 1k    |        |        |

|                                                     |          |            |     | 76.0~108.0M      | 100k       | 25k   | -10.7M |        |

| •                                                   | FM       | FM         |     |                  | 76.0~90.0M | 100k  | 25k    | -10.7M |

|                                                     |          | 1          | 1   | 76.0~3ch         | 100k       | 25k   | -10.7M |        |

|                                                     | MW       | '          | !   | 522~1629k        | 9k         | 3k    | 4501   |        |

|                                                     | IVIVV    |            |     | 520~1620k        | 10k        | 5k    | 450k   |        |

|                                                     | TV       |            |     | 1~12ch           | 1ch        | 25k   | -10.7M |        |

|                                                     |          | SW1        | SW0 |                  |            |       |        |        |

|                                                     | CIM      | 0          | 1   | 5.95~15.6        |            | El.   | 4501   |        |

|                                                     | SW       | 0          | 1   | 3.8~12.5         | 5k         | 5k    | 450k   |        |

Note: \*1. If step is 200kHz. Range is 87.5~108.1MHZ

<sup>\*2.</sup> The frequency range of FM in Europe area is according to FM step jumper.

<sup>\*3.</sup> The frequency range of FM in Japan area is according to FM step and LW/TV enable jumper.

#### **KEY MATRIX**

|            | K0                   | <b>K</b> 1        | K2                   | K3                |

|------------|----------------------|-------------------|----------------------|-------------------|

| T0         | A0 *                 | A1 *              | SW0 *                | SW1 *             |

| <b>T</b> 1 | LW/TV *<br>Enable    | WB*<br>Enable     | FM step *            | MW step *         |

| T2         | IF count *<br>Enable | 1/8 IF *          | POWER<br>KEY *enable | BAND *<br>OUT     |

| Т3         | CLOCK *<br>disable   | DUAL *<br>disable | CLOCK *<br>12/24 H   | +5KEY *<br>enable |

| <b>T</b> 4 | BAND/DUAL            | MEMORY/<br>CK ADJ | UP/ HOUR             | DOWN/ MIN         |

| T5         | Minc                 | Mdec              | ALARM                | SLEEP             |

(\*: Diode jumper)

## KEY MATRIX (AD in1 and AD in2)

| AD1  | AD2 |

|------|-----|

| 1    | 7   |

| 2    | 8   |

| 3    | 9   |

| 4    | 0   |

| 5    | FM  |

| 6/+5 | AM  |

#### KEY MATRIX EXPLANATION OF FUNCTION

| Symbol    | Explanation of function                                         |

|-----------|-----------------------------------------------------------------|

| 0~9       | Calling and writing preset memory.                              |

| +5        | Indirect tuning mode, used for input frequency                  |

| АМ        | Indirect tuning mode. Changing direct tuning mode of each band. |

| FM        | When the key pushing again, mode is released.                   |

| BAND/DUAL | The receiving band is changed.                                  |

|           | In clock mode, the two clocks is changed cyclically             |

(To be continued)

—— HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD —

(Continued)

| 100      |                                                          |

|----------|----------------------------------------------------------|

| Symbol   | Explanation of function                                  |

| MEMORY/  | The writing preset memory in frequency display.          |

| CK ADJ   | The clock adjustment in clock display.                   |

| UP/ HOUR | The receiving frequency is up.                           |

|          | The hour of time is up in clock adjustment mode.         |

| DOWN/    | The receiving frequency is down.                         |

| MIN      | The minute of time is up in clock adjustment mode.       |

| Minc     | In calling and writing preset memory, select of channel. |

| Mdec     |                                                          |

| ALARM    | The alarm function is on/off                             |

| SLEEP    | The sleep function is on/off                             |

## **DIODE MATRIX**

## **EXPLANATION OF FUNCTION**

| Symbol |                                     |               | Explanation of func   | tion |   |

|--------|-------------------------------------|---------------|-----------------------|------|---|

|        | Setting area                        |               |                       |      |   |

|        | A1                                  | A0            | ARAE                  |      |   |

| A0     | 0                                   | 0             | U.S.A                 |      |   |

| A1     | 0                                   | 1             | General               |      |   |

|        | 1                                   | 0             | Europe/ E-Europe      |      |   |

|        | 1                                   | 1             | Japan                 |      |   |

|        | Setting of the receiving band of SW |               |                       | _    |   |

|        | SW1                                 | SW0           | Receiving band (MHz)  | Note |   |

| SW0    | 0                                   | 0             | No SW                 |      |   |

| SW1    | 0                                   | 1             | 5.95~15.6             | SWA  |   |

|        | 1                                   | 0             | 3.80~12.50            | SWB  |   |

|        |                                     |               |                       |      | _ |

|        | Setting of LW                       | //TV band     |                       |      |   |

| LW/TV  | The with di                         |               |                       |      |   |

| Enable | The with di                         | ode: LW ena   | ble (other)           |      |   |

| Enable | The withou                          | t diode: TV d | isable (Japan, U.S.A) |      |   |

|        | The withou                          | t diode: LW   | disable (other)       |      |   |

(To be continued)

| ( | C | 10 | ٦t | ır | ıu | е | d | ) |

|---|---|----|----|----|----|---|---|---|

|   |   |    |    |    |    |   |   |   |

| Symbol    | Explanation of function                              |                                       |                           |              |  |  |

|-----------|------------------------------------------------------|---------------------------------------|---------------------------|--------------|--|--|

| WB enable | Setting of WB ba<br>The with diode<br>The without di |                                       |                           |              |  |  |

|           | Setting of FM st                                     | ер                                    |                           |              |  |  |

|           | FM step                                              | Step                                  | FM receiving frequen      | су           |  |  |

|           | 0                                                    | 200kHz                                | 87.5~108.0M               |              |  |  |

|           | 1                                                    | 50kHz                                 | 87.5~108.0M               |              |  |  |

|           | General area                                         |                                       |                           |              |  |  |

|           | FM step                                              | Step                                  | FM receiving frequen      | су           |  |  |

|           | 0                                                    | 100kHz                                | 87.5~108.0M               |              |  |  |

|           | 1                                                    | 50kHz 87.5~108.0M                     |                           |              |  |  |

|           | Europe area                                          |                                       |                           |              |  |  |

|           | FM step                                              | Step                                  | FM receiving frequent     | су           |  |  |

| FM STEP   | 0                                                    | 50kHz                                 | 65.0~74.0M<br>87.5~108.0M |              |  |  |

|           | 1                                                    | 50kHz                                 | 87.5~108.0M               |              |  |  |

|           | Japan area (step=100kHz)                             |                                       |                           |              |  |  |

|           | FM step                                              | LW/TVena                              | FM receiving              | TV receiving |  |  |

|           |                                                      |                                       | frequency                 | frequency    |  |  |

|           | 0                                                    | 0                                     | 76.0~108.0M               | 4 40-1-      |  |  |

|           | 0                                                    | 0                                     | 76.0~108.0M               | 1~12ch       |  |  |

|           | 1                                                    | 1                                     | 76.0~3ch<br>76.0~90.0M    | <br>1~12ch   |  |  |

|           | <u>                                   </u>           | <u> </u>                              | 70.0~90.0W                | 1~12CH       |  |  |

| MW STEP   |                                                      | e: MW 10kHz stej                      |                           |              |  |  |

|           |                                                      | ode: MW 9kHz st                       |                           |              |  |  |

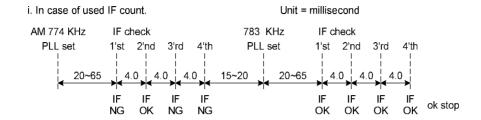

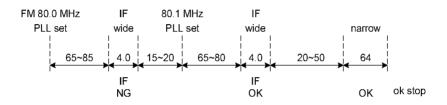

| IF count  | Setting of the IF                                    |                                       |                           |              |  |  |

| Enable    |                                                      | : IF count detect                     |                           |              |  |  |

|           |                                                      | ode: SD input de                      | tection                   |              |  |  |

| 1/8 IF    | Setting of IF cou                                    | · · · · · · · · · · · · · · · · · · · |                           |              |  |  |

| 1/8 IF    | The with diode                                       | •                                     | ut                        |              |  |  |

|           | i ne without ai                                      | ode: IF direct inp                    | uı                        |              |  |  |

—— HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD ——

(Continued)

| (Continuea)      |                                                          |

|------------------|----------------------------------------------------------|

| Symbol           | Explanation of function                                  |

| POWER            | Setting of power key                                     |

| KEY              | The with diode: tact key                                 |

| enable           | The without diode: slide key                             |

|                  | Setting of BAND IN/OUT                                   |

| BAND OUT         | The with diode: BAND OUT                                 |

|                  | The without diode: BAND IN                               |

| CLOCK<br>disable | Setting of clock function  The with diode: clock disable |

| uisable          | The without diode: clock enable                          |

| Dual             | Setting of dual clock function                           |

| disable          | The with diode: dual clock disable                       |

| disable          | The without diode: dual clock enable                     |

| CLOCK            | Setting of clock function                                |

| 12/24H           | The with diode: 24H CLOCK                                |

| 12/24/1          | The without diode: 12 CLOCK                              |

| +5 KEY           | Setting of +5 key                                        |

| enable           | The with diode: +5 key enable                            |

| CHABIE           | The without diode: +5 key disable                        |

### I/O MAP

| Port   | Pin | Name                 | I/O | Function                                                          | Active | Init | Case of<br>Not use |

|--------|-----|----------------------|-----|-------------------------------------------------------------------|--------|------|--------------------|

| DO1/OT | 51  | POOWER out           | 0   | Power output                                                      | Н      | ١    | Open               |

| IN     | 50  | IF IN/SDIN           | Ι   | IF count input/SD input                                           |        |      |                    |

| HOLD   | 48  | BATTERY              | _   | Battery input L: back up,<br>H: normal                            | Н      | ı    | GND                |

| MUTE   | 47  | MUTE                 | 0   | MUTE output                                                       | Н      | Н    | Open               |

| P3-1   | 46  | BUZR                 | 0   | BUZR output                                                       |        |      | Open               |

| P3-0   | 45  | BATTERY<br>INDICATOR | Ι   | Battery indicator input<br>L: battery mark flashing H: no<br>mark | Ħ      | I    | VDD                |