#### DATA SHEET

# BIPOLAR ANALOG INTEGRATED CIRCUIT $\mu PC8104GR$

# UP CONVERTER + QUADRATURE MODULATOR IC FOR DIGITAL MOBILE COMMUNICATION SYSTEMS

#### **DESCRIPTION**

The  $\mu$ PC8104GR is a silicon monolithic integrated circuit designed as quadrature modulator for digital mobile communication systems. This modulator consists of 1.9 GHz up-converter and 400 MHz quadrature modulator which are packaged in 20 pin SSOP. The device has power save function and can operate 2.7 to 5.5 V supply voltage, therefore, it can contribute to make RF block small, high performance and low power consumption.

#### **FEATURES**

- 20 pin SSOP suitable for high density surface mounting.

- High linearity up converter is incorporated; PRFout(sat) = -6 dBm TYP.

- Low phase difference due to digital phase shifter is adopted.

- Wide operating frequency range. Up converter; fRFout = 800 MHz to 1.9 GHz

Modulator ; fMODout = 100 MHz to 400 MHz, fI/Q = DC to 10 MHz

- External IF filter can be applied between modulator output and up converter input terminal.

- Supply voltage: Vcc = 2.7 to 5.5 V

- Equipped with power save function.

#### **APPLICATION**

- Digital cordless phones

- · Digital cellular phones

#### ORDERING INFORMATION

| PART NUMBER  | PACKAGE             | SUPPLYING FORM                                                                            |

|--------------|---------------------|-------------------------------------------------------------------------------------------|

| μPC8104GR-E1 | 20 pin plastic SSOP | Embossed tape 12 mm wide. QTY 2.5 kp/Reel.<br>Pin 1 indicates pull-out direction of tape. |

<sup>\*</sup> For evaluation sample order, please contact your local NEC sales office. (Order number: µPC8104GR)

Caution electro-static sensitive device

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

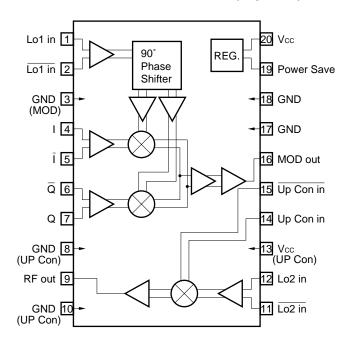

#### INTERNAL BLOCK DIAGRAM AND PIN CONNECTIONS (Top View)

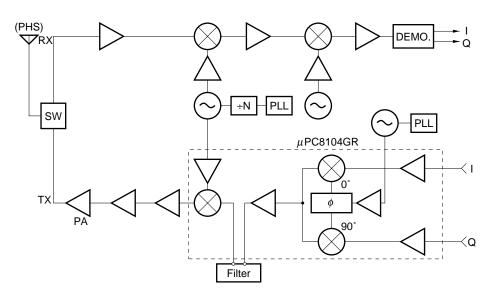

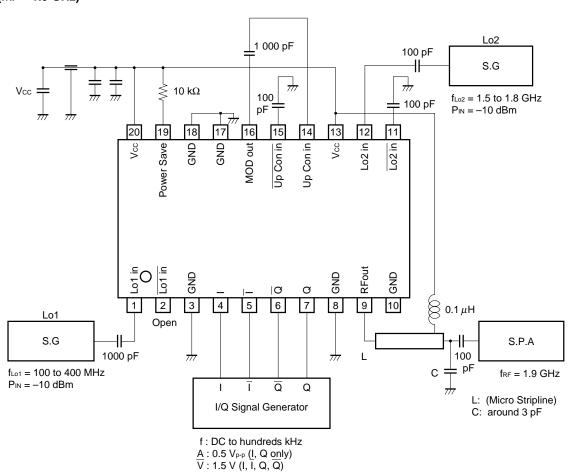

#### **APPLICATION EXAMPLE**

#### ABSOLUTE MAXIMUM RATINGS

| PARAMETER             | SYMBOL | RATING      | UNIT | TEST CONDITION                           |

|-----------------------|--------|-------------|------|------------------------------------------|

| Supply Voltage        | Vcc    | 6.0         | V    | T <sub>A</sub> = +25 °C                  |

| Power Save Voltage    | Vps    | 6.0         | V    | T <sub>A</sub> = +25 °C                  |

| Power Dissipation     | Po     | 430         | mW   | T <sub>A</sub> = +85 °C <sup>Note1</sup> |

| Operating Temperature | TA     | -40 to +85  | °C   |                                          |

| Storage Temperature   | Tstg   | -55 to +150 | °C   |                                          |

Note 1: Mounted on  $50 \times 50 \times 1.6$  mm double copper clad epoxy glass board

#### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                  | SYMBOL             | MIN. | TYP. | MAX. | UNIT | TEST CONDITIONS                                               |  |

|----------------------------|--------------------|------|------|------|------|---------------------------------------------------------------|--|

| Supply Voltage             | Vcc                | 2.7  | 3.0  | 5.5  | V    |                                                               |  |

| Operating Temperature      | TA                 | -40  | +25  | +85  | °C   |                                                               |  |

| Up Converter RF Frequency  | fRFout             | 0.8  |      | 1.9  | GHz  |                                                               |  |

| Up Converter Input Freq.   | fUpConin           | 100  |      | 400  | MHz  |                                                               |  |

| Modulator Output Frequency | fMODout            |      |      |      |      |                                                               |  |

| Lo1 Input Frequency        | <b>f</b> Lo1in     |      |      |      |      | P <sub>Lo1in</sub> = -10 dBm                                  |  |

| Lo2 Input Frequency        | <b>f</b> Lo2in     | 800  |      | 1800 | MHz  | P <sub>Lo2in</sub> = -10 dBm                                  |  |

| I/Q Input Frequency        | f <sub>I/Qin</sub> | DC   |      | 10   | MHz  | P <sub>I/Qin</sub> = 600 mV <sub>p-p</sub> MAX (Single ended) |  |

#### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = +25 °C, Vcc = 3.0 V, Unless Otherwise Specified V<sub>PS</sub> ≥ 1.8 V)

| PARAMETER                                | SYMBOL                                    | MIN.  | TYP.  | MAX. | UNIT | TEST CONDITIONS                                           |  |  |

|------------------------------------------|-------------------------------------------|-------|-------|------|------|-----------------------------------------------------------|--|--|

| UP CONVERTER + QUADRATU                  | UP CONVERTER + QUADRATURE MODULATOR TOTAL |       |       |      |      |                                                           |  |  |

| Total Circuit Current                    | IccTOTAL                                  | 18    | 28    | 37   | mA   | No input signal                                           |  |  |

| Total Circuit Current at Power-Save Mode | Icc(PS)TOTAL                              |       | 0.1   | 10   | μΑ   | V <sub>PS</sub> ≤ 1.0 V                                   |  |  |

| Total Output Power                       | PrFout                                    | -18.5 | -13.5 | -8.5 | dBm  | I/Q DC = 1.5 V                                            |  |  |

| Lo Carrier Leak <sup>Note2</sup>         | LOL                                       |       | -40   | -30  | dBc  | P <sub>I/Qin</sub> = 500 mV <sub>p-p</sub> (Single ended) |  |  |

| Image Rejection (Side Band Leak)         | ImR                                       |       | -40   | -30  | dBc  |                                                           |  |  |

Note 2: Lo1 + Lo2

Data Sheet P10099EJ4V0DS00

#### STANDARD CHARACTERISTICS FOR REFERENCE

(TA = +25 °C, Vcc = 3.0 V, Unless Otherwise Specified Vps  $\geq$  1.8 V)

| PARAMETER                                   | SYMBOL                | MIN. | TYP.  | MAX. | UNIT | TEST CONDITIONS                                                                               |  |

|---------------------------------------------|-----------------------|------|-------|------|------|-----------------------------------------------------------------------------------------------|--|

| UP CONVERTER BLOCK                          |                       |      |       |      |      |                                                                                               |  |

| Up Con. Circuit Current                     | IccUpCon              |      | 12    |      | mA   | No input signal                                                                               |  |

| Up Con. Circuit Current at Power-Save Mode  | Icc(PS)UpCon          |      |       | 5    | μΑ   | V <sub>PS</sub> ≤ 1.0 V                                                                       |  |

| Conversion Gain                             | CG                    |      | 4     |      | dB   | frFout = 1.9 GHz                                                                              |  |

| Maximum Output Power                        | P <sub>RF(sat)</sub>  |      | -6    |      | dBm  | f <sub>UpConin</sub> = 240.0 MHz/240.2 MHz                                                    |  |

| Output Intercept Point                      | OIP3                  |      | 0     |      | dBm  |                                                                                               |  |

| QUADRATURE MODULATOR                        | BLOCK                 |      |       |      |      |                                                                                               |  |

| MOD. Circuit Current                        | IccMOD                | 10   | 16    | 21   | mA   | No input signal                                                                               |  |

| MOD. Circuit Current at Power-Save Mode     | Icc(PS)MOD            |      |       | 5    | μΑ   | V <sub>PS</sub> ≤ 1.0 V                                                                       |  |

| Output Power                                | PMODout               |      | -16.5 |      | dBm  | I/Q DC = 1.5 V                                                                                |  |

| Lo1 Carrier Leak                            | LOL                   |      | -40   | -30  | dBc  | P <sub>I/Qin</sub> = 500 mV <sub>p-p</sub> (Single ended)                                     |  |

| Image Rejection<br>(Side Band Leak)         | ImR                   |      | -40   | -30  | dBc  |                                                                                               |  |

| I/Q 3rd Order Intermodulation<br>Distortion | <b>І</b> мзі/Q        |      | -50   | -30  | dBc  |                                                                                               |  |

| I/Q Input Impedance                         | ZI/Q                  |      | 20    |      | kΩ   | I/Q DC = 1.5 V                                                                                |  |

| I/Q Bias Current                            | I <sub>I/Q</sub>      |      | 5     |      | μΑ   | $P_{VQin} = 500 \text{ mV}_{P-P} \text{ (Single ended)}$ $(I \rightarrow I, Q \rightarrow Q)$ |  |

| Lo1 Input VSWR                              | Z <sub>Lo1</sub>      |      | 1.2:1 |      | X:1  |                                                                                               |  |

| Power Save Rise Time                        | T <sub>PS(RISE)</sub> |      | 2.0   | 5.0  | μs   | $V_{PS(OFF)} \rightarrow V_{PS(ON)}$                                                          |  |

| Power Save Fall Time                        | Tps(fall)             |      | 2.0   | 5.0  | μs   | $V_{PS(ON)} \rightarrow V_{PS(OFF)}$                                                          |  |

#### PIN EXPLANATION

| PIN<br>NO. | ASSIGN-<br>MENT   | SUPPLY<br>VOL. (V) | PIN<br>VOL.(V) | FUNCTION AND APPLICATION                                                                                                                          | EQUIPMENT CIRCUIT |

|------------|-------------------|--------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1          | Lo1in             | -                  | 0              | Lo1 input for phase shifter. This input impedance is 50 $\Omega$ matched internally.                                                              | ① \$ 50 Ω         |

| 2          | Lo1in             | _                  | 2.4            | Bypass of Lo1 input. This pin is grounded through internal capacitor. Open in case of single ended.                                               |                   |

| 3          | GND for modulator | 0                  | _              | Connect to the ground with minimum inductance. Track length should be kept as short as possible.                                                  |                   |

| 4          | I                 | Vcc/2              | -              | Input for I signal. This input impedance is larger than 20 k $\Omega$ . Relations between amplitude and Vcc/2 bias of input signal are following. | 4                 |

| 5          | T                 | Vcc/2              | _              | Input for I signal. This input impedance is larger than 20 k $\Omega$ . Vcc/2 biased DC signal should be input.                                   |                   |

| 6          | Q                 | Vcc/2              | _              | Input for Q signal. This input impedance is larger than 20 k $\Omega$ . Vcc/2 biased DC signal should be input.                                   |                   |

| 7          | Q                 | Vcc/2              | -              | Input for Q signal. This input impedance is larger than 20 k $\Omega$ . Relations between amplitude and Vcc/2 bias of input signal are following. | 7                 |

| 16         | MODout            | -                  | 1.5            | Output from modulator. This is emitter follower output.                                                                                           | 16                |

Note In case of that I/Q input signals are single ended.

Of course, I/Q signal inputs can be used either single endedly or differentially with proper terminations.

#### PIN EXPLANATION

| PIN<br>NO. | ASSIGN-<br>MENT             | SUPPLY<br>VOL. (V) | PIN<br>VOL.(V) | FUNCTION AND APPLICATION                                                                                                                  | EQUIPMENT CIRCUIT                     |

|------------|-----------------------------|--------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 8          | GND<br>for Up-<br>converter | 0                  | _              | Connect to the ground with minimum inductance. Track length should be kept as short as possible.                                          | 12                                    |

| 11         | Lo2in                       | -                  | 2.0            | Bypass of Lo2 input. Grounded through external capacitor.                                                                                 | • • • • • • • • • • • • • • • • • • • |

| 12         | Lo2in                       | -                  | 0              | Lo2 input of Up-converter. This pin is high impedance input.                                                                              |                                       |

| 13         | Vcc for Up-<br>converter    | 2.7 to 5.5         | _              | Supply voltage pin for Upconverter.                                                                                                       |                                       |

| 9          | RFout                       | Vcc                | -              | RF output from Up-Converter. This pin is open collector output.                                                                           |                                       |

| 14         | UpConin                     | -                  | 2.0            | IF input for Up-converter. This pin is high impedance input.                                                                              |                                       |

| 15         | UpConin                     | _                  | 2.0            | Bypass of IF input. Grounded through external capacitor.                                                                                  |                                       |

| 17         | GND                         | 0                  | _              | Connect to the ground with minimum inductance. Track length should be kept as                                                             |                                       |

| 18         |                             |                    |                | short as possible.                                                                                                                        |                                       |

| 19         | Power<br>Save               | V <sub>P/S</sub>   | _              | Power save control pin can be controlled ON/SLEEP state with bias as follows;  VP/S (V) STATE  1.8 to 5.5 ON  0 to 1.0 SLEEP              | (19)<br>**                            |

| 20         | Vcc for<br>Modulator        | 2.7 to 5.5         | -              | Supply voltage pin for modulator. Internal regulator can be kept stable condition of supply bias against the variable temperature or Vcc. |                                       |

: Externally

#### **EXPLANATION OF INTERNAL FUNCTION**

| BLOCK                | FUNCTION/OPERATION                                                                                                                                                                                                                                                                                                             | BLOCK DIAGRAM          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 90° PHASE<br>SHIFTER | Input signal from Lo1 is send to digital circuit of T-type flip-flop through frequency doubler. Output signal from T-type F/F is changed to same frequency as Lo1 input and that have quadrature phase shift, 0°, 90°, 180°, 270°. These circuits have function of self phase correction to make correctly quadrature signals. | from Lo1in  ×2  ÷2 F/F |

| BUFFER AMP.          | Buffer amplifiers for each phase signals to send to each mixers.                                                                                                                                                                                                                                                               |                        |

| MIXER                | Each signals from buffer amp. are quadrature modulated with two double-balanced mixers. High accurate phase and amplitude inputs are realized to good performance for image rejection.                                                                                                                                         | Q Q                    |

| ADDER                | Output signals from each mixers are added with adder and send to final amplifier.                                                                                                                                                                                                                                              | to MODout              |

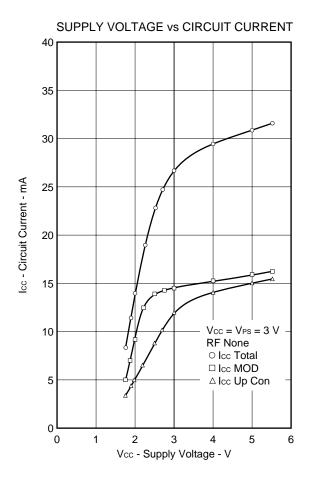

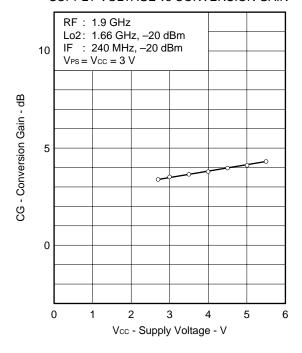

#### TYPICAL CHARACTERISTICS (TA = +25 °C)

Unless otherwise specified  $Vcc = V_{PS} = 3 \text{ V}$ , I/Q DC offset = I/Q DC offset = 1.5 V, I/Q Input Signal = 500 mV<sub>P-P</sub> (single ended),  $P_{Lo1in} = -10 \text{ dBm}$ ,  $P_{Lo2in} = -10 \text{ dBm}$ , (continuous wave)

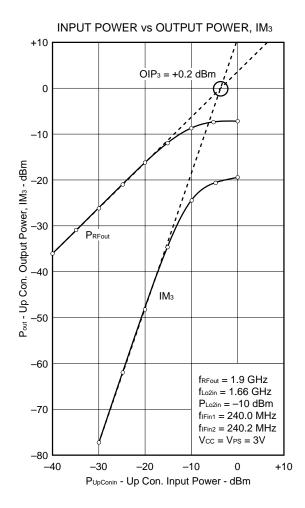

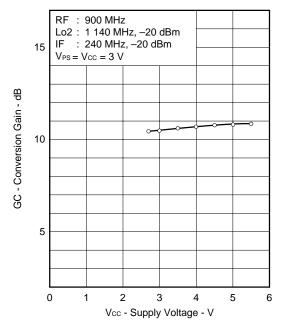

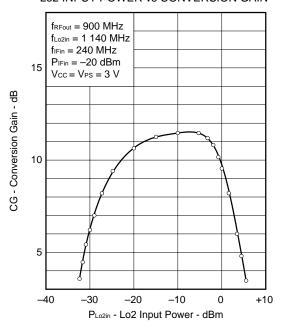

#### [UP CONVERTER BLOCK]

#### SUPPLY VOLTAGE vs CONVERSION GAIN

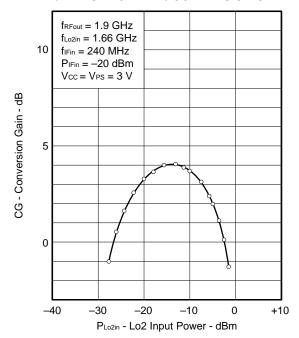

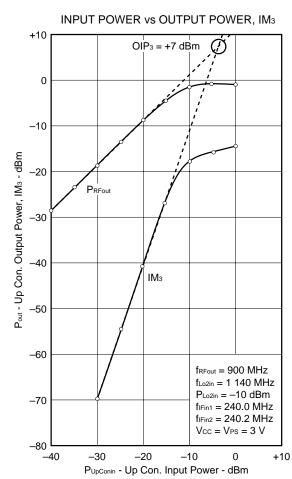

#### [UP CONVERTER BLOCK]

#### [UP CONVERTER BLOCK]

#### Lo2 INPUT POWER vs CONVERSION GAIN

#### [UP CONVERTER BLOCK]

#### SUPPLY VOLTAGE vs CONVERSION GAIN

#### [UP CONVERTER BLOCK]

#### [UP CONVERTER BLOCK]

#### Lo2 INPUT POWER vs CONVERSION GAIN

#### [MODULATOR BLOCK]

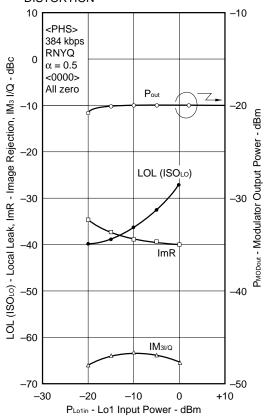

Lo1 INPUT POWER vs OUTPUT POWER, LOCAL LEAK, IMAGE REJECTION, I/Q 3RD ORDER INTERMODULATION DISTORTION

#### [MODULATOR BLOCK]

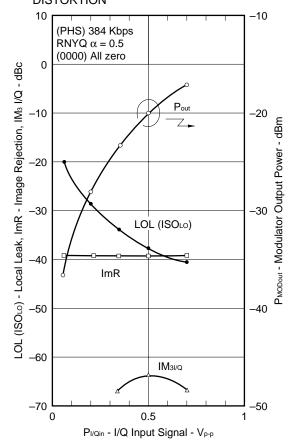

I/Q INPUT SIGNAL vs OUTPUT POWER, LOCAL LEAK, IMAGE REJECTION, I/Q 3RD ORDER INTERMODULATION DISTORTION

#### [MODULATOR BLOCK]

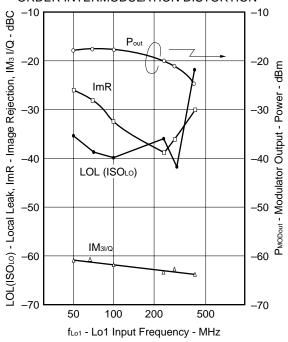

LO1 INPUT FREQUENCY vs OUTPUT POWER, LOCAL LEAK, IMAGE REJECTION, I/Q 3RD, ORDER INTERMODULATION DISTORTION

#### [MODULATOR + UP CONVERTER]

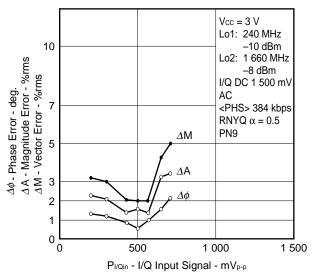

I/Q INPUT SIGNAL vs VECTOR ERROR, MAGNITUDE ERROR, PHASE ERROR

#### [MODULATOR BLOCK]

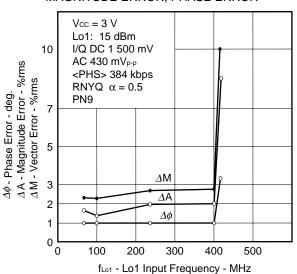

Lo1 INPUT FREQUENCY vs VECTOR ERROR, MAGNITUDE ERROR, PHASE ERROR

#### [MODULATOR + UP CONVERTER]

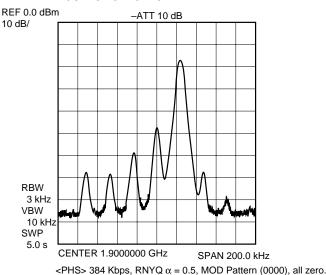

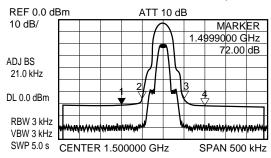

## TYPICAL SINE WAVE MODULATION OUTPUT SPECTRUM

#### [MODULATOR BLOCK]

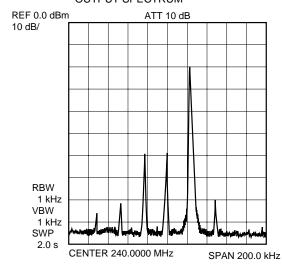

### TYPICAL SINE WAVE MODULATION OUTPUT SPECTRUM

#### [MODULATOR + UP CONVERTER]

#### [MODULATOR BLOCK]

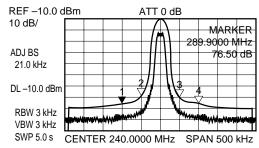

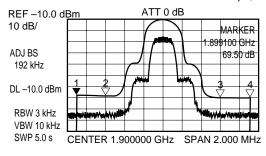

## TYPICAL $\pi/4$ DQPSK MODULATION OUTPUT SPECTRUM <PDC> 42 kbps, RNYQ $\alpha$ = 0.5, MOD Pattern <PN9>

#### [MODULATOR + UP CONVERTER]

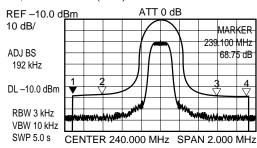

#### [MODULATOR BLOCK]

## TYPICAL $\pi/4$ DQPSK MODULATION OUTPUT SPECTRUM <PHS> 384 kbps, RNYQ $\alpha$ = 0.5, MOD Pattern (PN9)

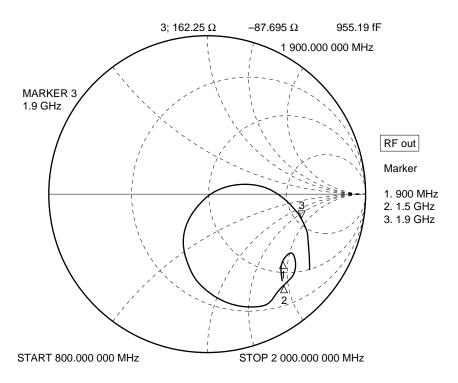

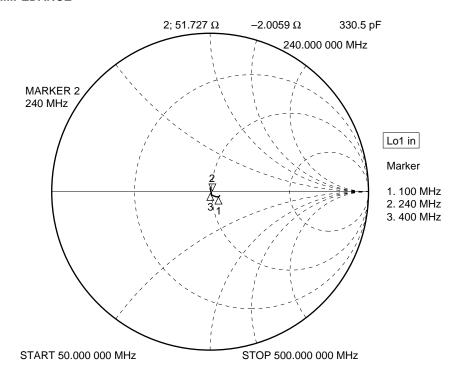

#### **RFout OUTPUT IMPEDANCE**

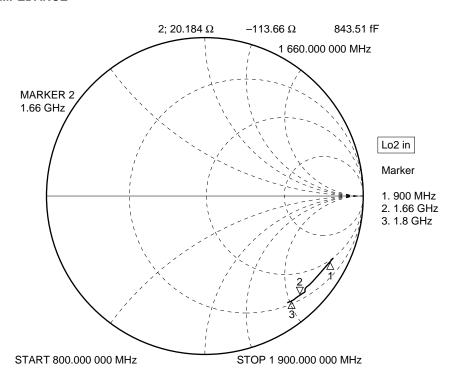

#### Lo2in INPUT IMPEDANCE

Data Sheet P10099EJ4V0DS00

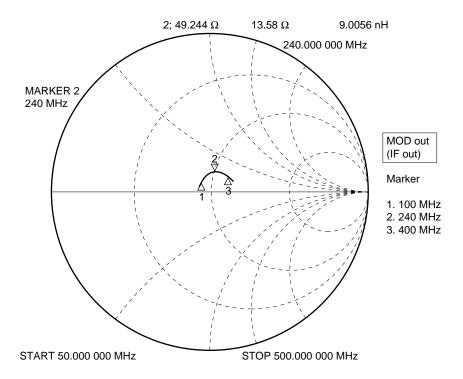

#### **MODout OUTPUT IMPEDANCE**

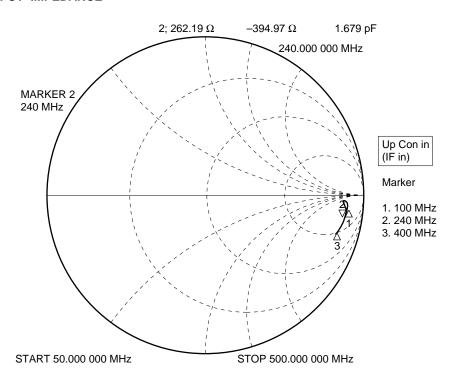

#### **UP CON. in INPUT IMPEDANCE**

#### Lo1in INPUT IMPEDANCE

# TEST CIRCUIT (fRF = 1.9 GHz)

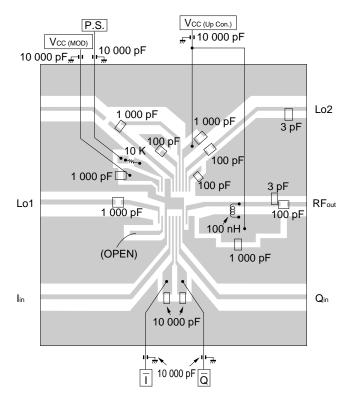

#### **TEST BOARD**

In case of this test board, the output signal from MOD. is directly connected to the up converter input port through 1000 pF, which is DC coupling.  $f_{RF} = 1.9 \text{ GHz}$   $f_{Lo2} = 1.66 \text{ GHz}$  $f_{Lo1} = 240 \text{ MHz}$

We recommend to insert a low pass filter between MOD output and up converter input port to reject harmonics of the Lo1 signal and to avoid saturation of the up converter.

GND

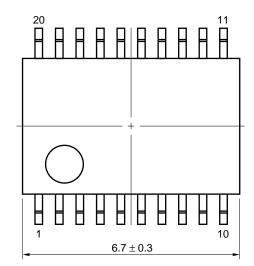

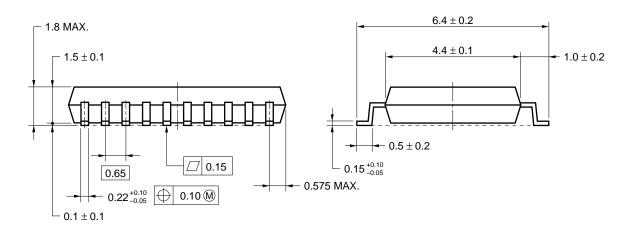

#### PACKAGE DIMENSIONS

**★** 20 PIN PLASTIC SSOP (225 mil) (UNIT: mm)

detail of lead end

**NOTE** Each lead centerline is located within 0.10 mm of its true position (T.P.) at maximum material condition.

#### NOTE ON CORRECT USE

- (1) Observe precautions for handling because of electrostatic sensitive devices.

- (2) Form a ground pattern as wide as possible to keep the minimum ground impedance (to prevent undesired oscillation).

- (3) Keep the track length of the ground pins as short as possible.

- (4) Connect a bypass capacitor (e.g. 1 000 pF) to the Vcc pin.

- (5) I, Q DC offset voltage should be same as the I, Q DC offset voltage (to prevent changing the local leak level with power save control.)

#### RECOMMENDED SOLDERING CONDITIONS

This product should be soldered in the following recommended conditions. Other soldering methods and conditions than the recommended conditions are to be consulted with our sales representatives.

#### $\mu$ PC8104GR

| Soldering Method       | Soldering Conditions                                                                                                                                                               | Symbol    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Infrared ray reflow    | Peak package's surface temperature: 235 °C or below,<br>Reflow time: 30 seconds or below (210 °C or higher),<br>Number of reflow process: 3, Exposure limit <sup>Note</sup> : None | IR35-00-3 |

| VPS                    | Peak package's surface temperature: 215 °C or below,<br>Reflow time: 40 seconds or below (200 °C or higher),<br>Number of reflow process: 3, Exposure limit <sup>Note</sup> : None | VP15-00-3 |

| Wave soldering         | Solder temperature: 260 °C or below Flow time: 10 seconds or below, Number of reflow process: 1, Exposure limit <sup>Note</sup> : None                                             | WS60-00-1 |

| Partial heating method | Terminal temperature: 300 °C or below Flow time: 3 seconds/pin or below, Exposure limit <sup>Note</sup> : None                                                                     |           |

**Note** Exposure limit before soldering after dry-pack package is opened.

Storage conditions: 25 °C and relative humidity at 65 % or less.

Caution Apply only a single process at once, except for "Partial heating method".

For details of recommended soldering conditions for surface mounting, refer to information document SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL (C10535E)

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

[MEMO]

- The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these circuits,

software, and information in the design of the customer's equipment shall be done under the full responsibility

of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third

parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

- "Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

M7 98.8