Empowered by Innovation

850

Embedded Controller

#

**Embedded Controller**

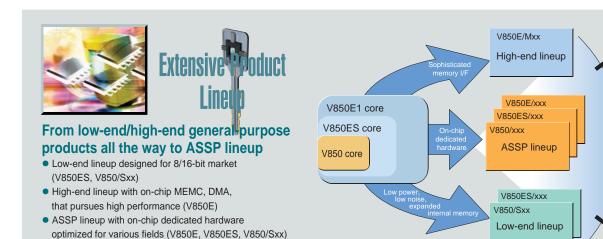

The V850 Series<sup>™</sup> of embedded microcontrollers answers diversified needs in all kinds of application systems. It realizes lower power consumption and noise while achieving higher performance and multiple functions. Consisting of a rich lineup, the V850 Series offers optimum solutions for nextgeneration embedded systems.

Inverter-type air conditioners

Digital video cameras

Automotive electronics

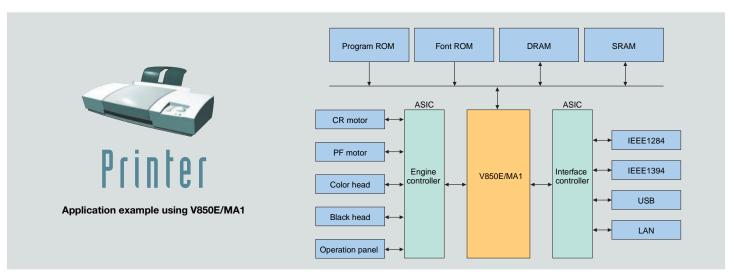

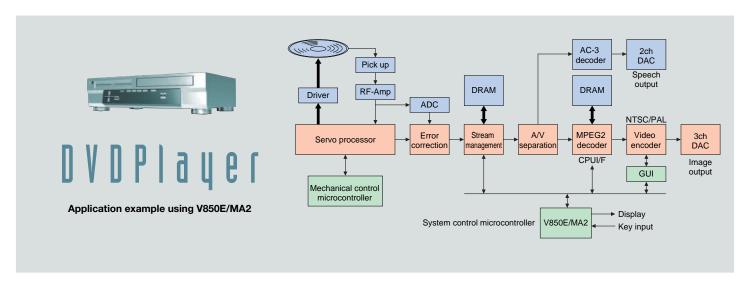

**DVD** players

Digital still cameras

Cellular phones

Storage devices

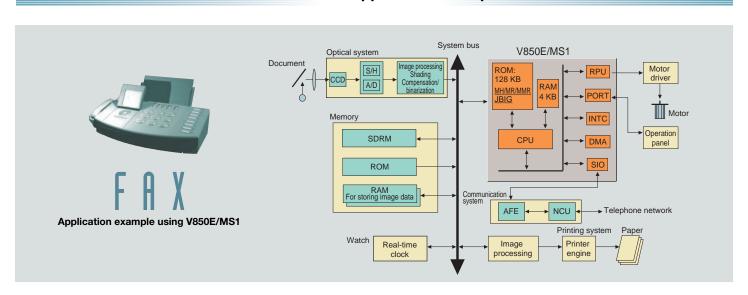

Fax machines

Single-lens reflex cameras

Network modems

Microwave ranges

Printers

Home audio

Vending machines

Electronic music instruments

Car audio

Car AV centers

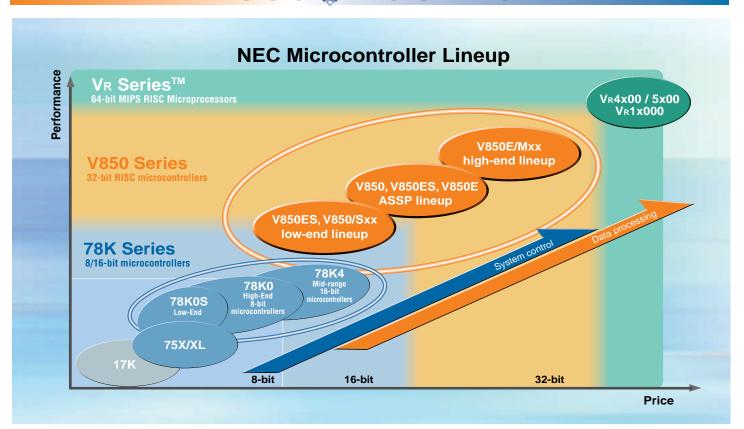

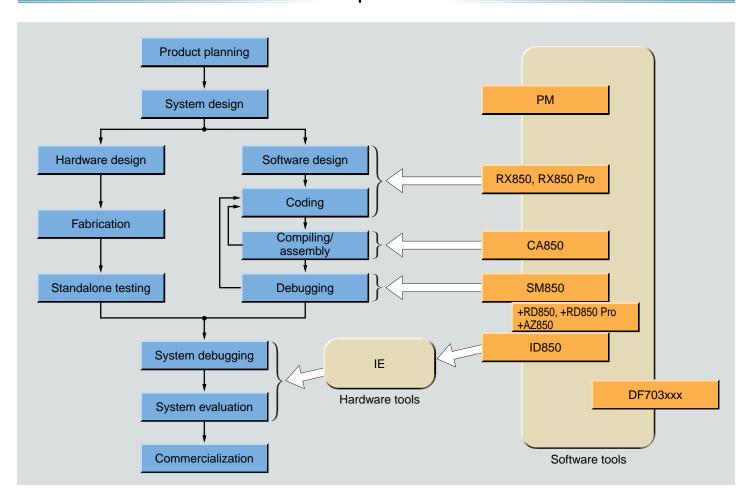

### V850 POSITION

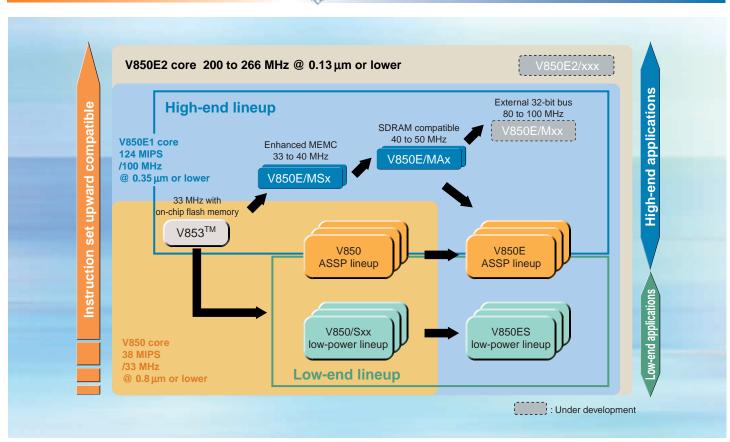

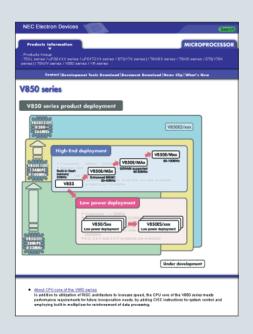

### V850 PROADMAP

#

| 5KEYS V850               | Perioher              | 06         |

|--------------------------|-----------------------|------------|

| Architecture             | reriphi               | 18         |

| Variety of Peripheral Fu | nctions               | 27         |

| Low Power & Low Noise    | )                     | 32         |

| Middleware               |                       | 36         |

| Flash Memory Microcor    | trollers              | 38         |

| Functional Outline       | Flashm                | 42         |

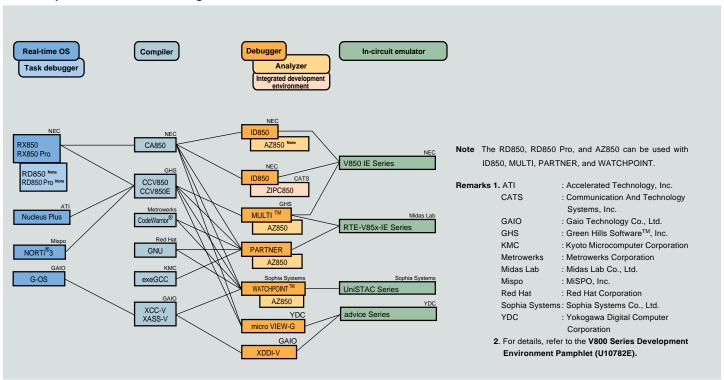

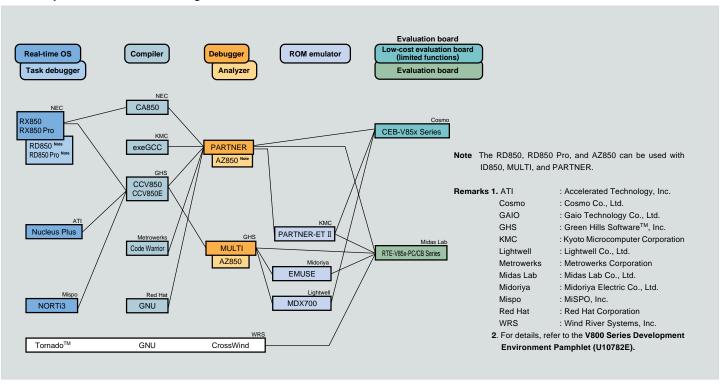

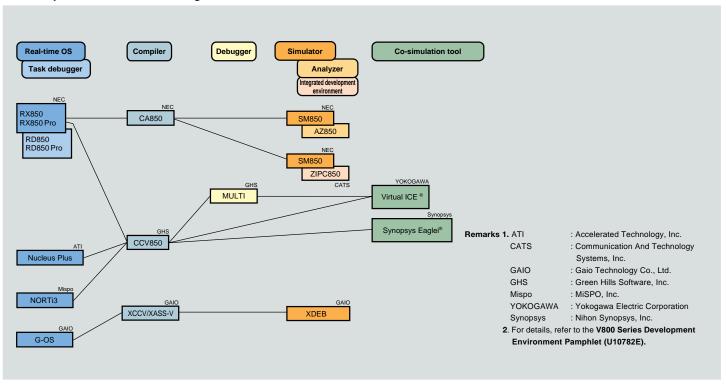

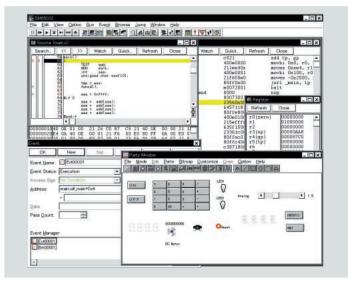

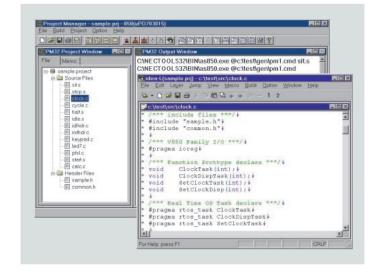

| Comfortable Development  | Environment           | 53         |

| Information              | Activity<br>al Activi | <b>6</b> 1 |

### 5KEYS V850

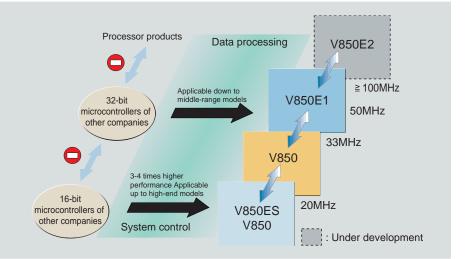

- 3 to 4 times higher performance at same frequency compared to 16-bit microcontrollers

- V850, V850ES, and V850E1 cores are upward compatible at object level.

- V850 Series covers a broad range from middle to high-end market with a single instruction set

Automotive

OA

Industrial

Communications )

Information

appliances

Consumer electronics

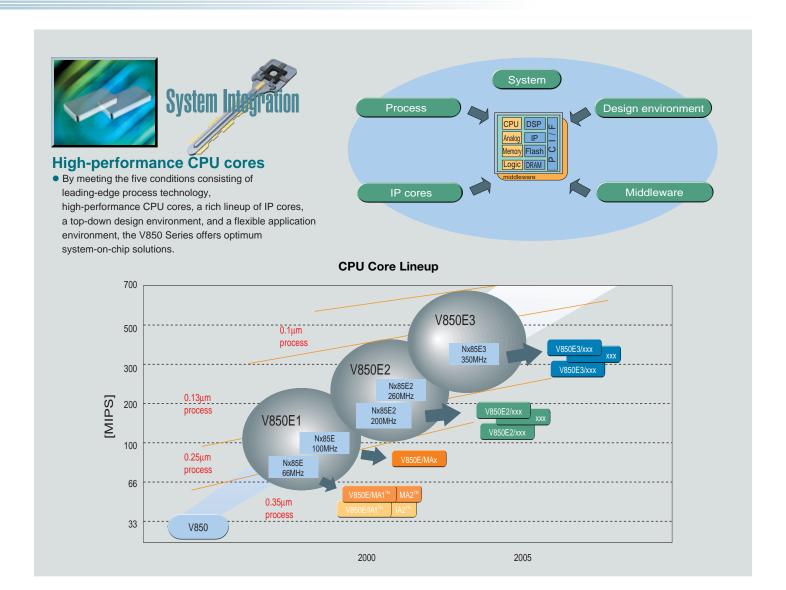

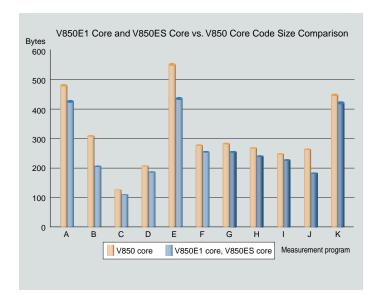

#### **V850E Product Development Concept**

# Pursuit of high performance

High-performance CPU using V850E core

- 10% higher performance than V850 CPU at same frequency

- 10% to 20% higher code efficiency than V850 CPU through addition of C-compatible instructions

- Upward compatibility at object level with V850 CPU cores

# **Enhanced external bus performance**

On-chip direct interface for various memories

SRAM, page ROM, EDO DRAM, synchronous DRAM, etc.

On-chip DMA controller

Realization of voluminous data processing and high-performance control on one chip

#### **V850E Product Features**

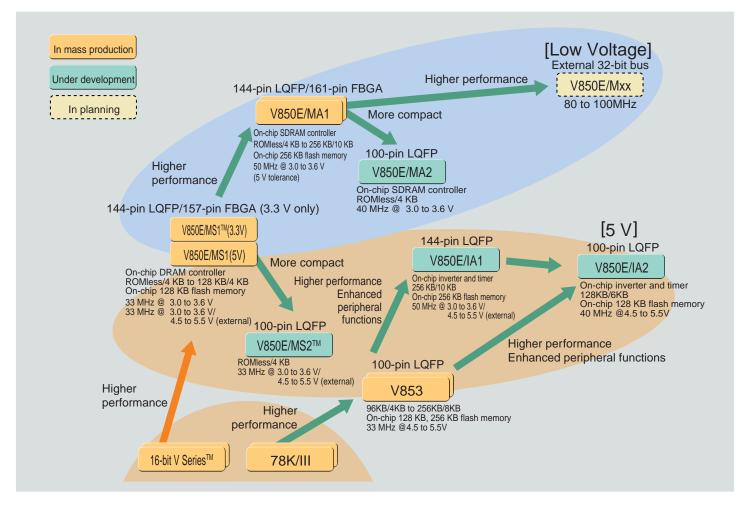

# V850E/MS1

- Performance of 43 MIPS @ 33 MHz

- On-chip memory controllers for EDO DRAM, etc.

- Lineup of products for 5 V systems and 3.3 V systems

# V850E/MS2

- Support of 5 V interface enables connection of existing external I/Os

- Contributes to higher cost performance of sets through use of V850E CPU architecture

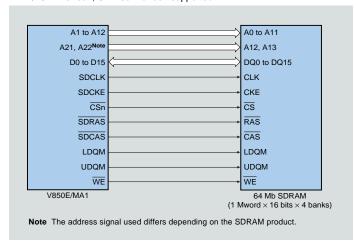

# V850E/MA1

- High performance of 62 MIPS @ 50 MHz

- On-chip memory controllers for SDRAM, etc.

- Various peripheral functions such as timer, serial interface, and A/D converter

# V850E/MA2

- On-chip SDRAM controller

- Contributes to smaller applications, lighter weight, and higher cost performance through use of 14 × 14 mm, 100-pin package

# V850E/IA1

On-chip 3-phase sine wave PWM timer, 2-phase encoder input up/down counter,

A/D converter, 2-system motor driving enabled through inverter control

6-system serial I/F including FCAN for automotive LAN (Ver. 2.0 Part B compliant)

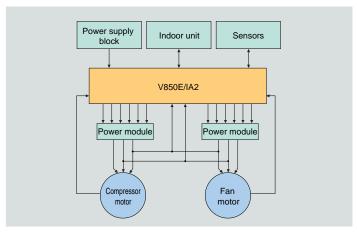

### V850E/IA2

- 2-system motor driving enabled through on-chip peripheral functions almost the same as those of V850E/IA1

- System can be configured with single 5 V power supply thanks to on-chip regulator

#### **V850E Product Application Examples**

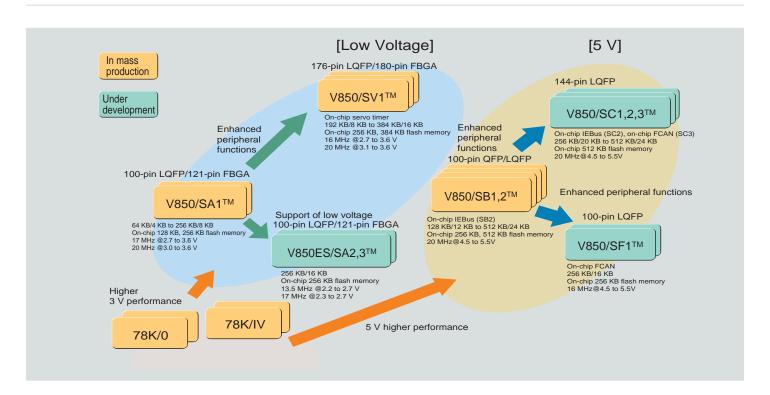

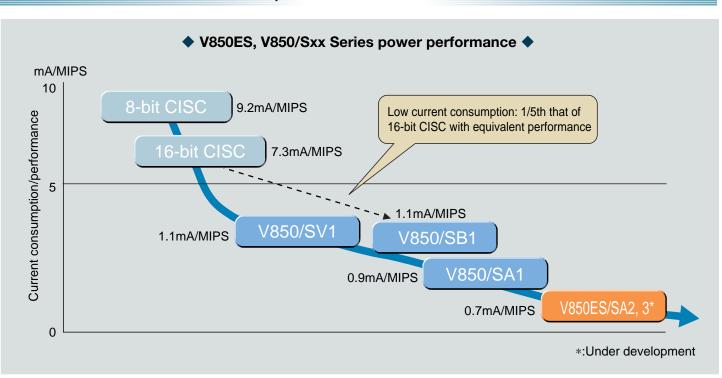

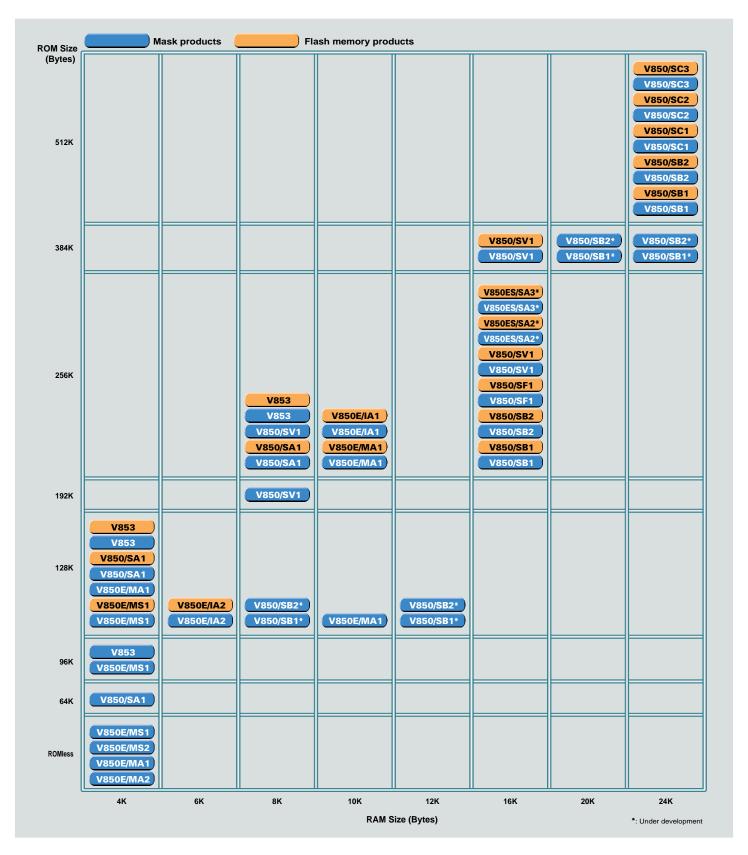

#### V850ES, V850/Sxx Product Development Concept

### **High Performance**

■ 3 to 4 times higher performance compared to 16-bit CISC microcontrollers ■ Middleware support (JPEG, speech recognition, etc.)

### Low noise & low power

Optimum design for maximum operating frequency of 20 MHz — Thorough EMI noise countermeasures

### Low-voltage support

■ Realization of 2.2 V low voltage operation (V850ES/SA2, SA3)

### Variation in memory and 1/0

- Various memory capacities (ROM: 64 KB to 512 KB, RAM: 4 KB to 24 KB) Various packages (100-pin to 180-pin)

- Various ASSPs (automotive bus support (IEBus<sup>TM</sup>, CAN), servo timer, etc.)

### Peripheral functions inherited from 78K Series

- Standard peripheral functions of 78K Series (timer, serial interface, etc.)

Designed for 8/16-bit application market

- Pursuit of high cost performance

#### V850ES, V850/Sxx Product Features

# **V850ES/SA2, SA3**

- Ultra-low power consumption/high-speed operation (30 mW @ 2.5 V, 17 MHz)

- Low-voltage operation of 2.2 V Min. (1.8 V under planning)

- On-chip single power supply flash memory

- On-chip V850ES core

## V850/SA1

- Ultra-low power consumption (66 mW (20 MHz @ 3.3 V, mask ROM version, Typ.))

- Rich memory lineup (ROM 64 KB to 256 KB/RAM 4 KB to 8 KB)

- Support of CSP package (121-pin FBGA)

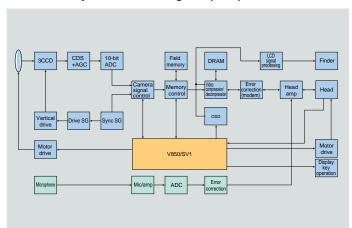

### V850/SV1

- Various on-chip peripheral functions including servo timer

- Rich memory lineup (ROM 192 KB to 384 KB/RAM 8 KB to 16 KB)

- Support of high-pin-count CSP package (180-pin FBGA)

- ASSP lineup for DVC

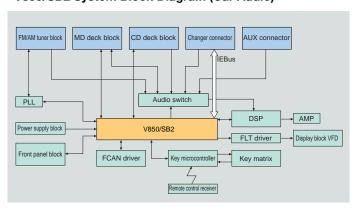

# V850/SB1, SB2

- Low EMI noise

- On-chip large-capacity memory (512 KB/24 KB Max.)

- Rich memory lineup (ROM 128 KB to 512 KB/RAM 12 KB to 24 KB)

- Automotive bus support (V850/SB2 only)

### V850/SF1

- Low EMI noise

- On-chip FCAN controller (2 ch Max.)

- ASSP lineup for car audio

# V850/SC1, SC2, SC3

- Low EMI noise

- Enhanced peripheral functions for V850/SB1, SB2 (100-pin → 144-pin)

- Automotive bus support (IEBus, FCAN)

#### V850ES, V850/Sxx Product Features

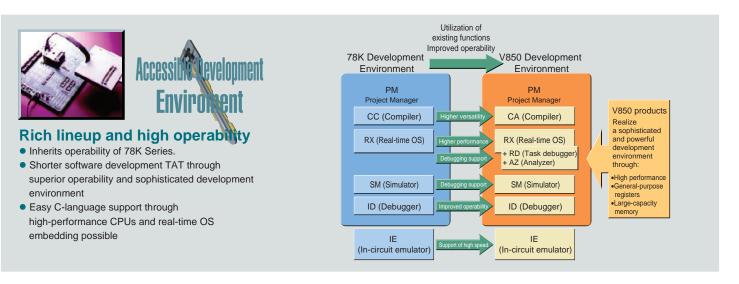

#### Smooth transition from CISC to RISC

#### CISC-like use enabled

- Bit manipulation instructions (SET1, CLR1, NOT1, TST1)

- Multi-status flags

- 32-bit barrel shifter

### On-chip standard peripheral functions of 78K Series

- Timers (8-bit, 16-bit)

- Serial interface (3-wire CSI, UART)

- Watchdog timer, etc.

#### High code efficiency

- Equals CISC code efficiency (1.0 to 1.2)

- High-level language (C language) programming supported

#### ◆ Comparison of peripheral functions of 78K Series and V850/Sxx products ◆

|                            | 78K/0 Series | 78K/IV Series           |          |            | V850 Series |          |              |

|----------------------------|--------------|-------------------------|----------|------------|-------------|----------|--------------|

|                            | μPD78003x    | μPD78421x               | V850/SA1 | V850/SB1,2 | V850/SV1    | V850/SF1 | V850/SC1,2,3 |

| 16-bit timer               | TM0          | <b>+</b>                | <b>←</b> | <b>←</b>   | <b>←</b>    | <b>←</b> | <b>←</b>     |

| 8-bit timer                | TM5          | <b>←</b>                | <b>←</b> | <b>←</b>   | <b>←</b>    | <b>←</b> | _            |

| Serial interface (CSI)     | SIO3         | <b>+</b>                | <b>←</b> | <b>←</b>   | <b>←</b>    | <b>←</b> | <b>←</b>     |

| Serial interface (UART)    | UART0        | <b>←</b>                | UART3    | <b>←</b>   | <b>←</b>    | <b>←</b> | <b>+</b>     |

| I <sup>2</sup> C interface | IIC0         | <b>←</b>                | <b>+</b> | <b>←</b>   | <b>←</b>    | <b>←</b> | <b>←</b>     |

| AD converter               | ADCTL0       | <b>+</b>                | <b>+</b> | <b>←</b>   | <b>←</b>    | <b>←</b> | <b>←</b>     |

| Real-time output           | _            | RT00                    | <b>+</b> | <b>←</b>   | <b>←</b>    | _        | _            |

| Watchdog timer             | WDT          | Separate specifications | WDT      | <b>←</b>   | <b>←</b>    | <b>←</b> | <b>←</b>     |

| Watch timer                | WT           | <b>+</b>                | <b>+</b> | WTN0       | <b>←</b>    | <b>←</b> | <b>+</b>     |

| Key return function        | _            | Separate specifications | _        | KR0        | <b>←</b>    | <b>←</b> | <b>←</b>     |

<sup>←:</sup>Listed on left

<sup>— :</sup>Not provided

# <u>vo</u>

#### **V850 ASSP Lineup**

#### ■V850E/IA2 inverter air conditioner application example

#### ■V850/SV1 System Block Diagram (DVC)

#### ■V850/SB2 System Block Diagram (Car Audio)

14

Pamphlet U15412EJ1V0PF

#### **Memory Lineup**

#### **Package Lineup**

| Package Name                      | Applicable Products                                            |

|-----------------------------------|----------------------------------------------------------------|

| 100-pin plastic QFP (14 × 20 mm)  | V850/SB1, SB2, SF1                                             |

| 100-pin plastic LQFP (14 × 14 mm) | V850E/MA2, MS2, IA2, V850ES/SA2, V850/SA1, SB1, SB2, SF1, V853 |

| 144-pin plastic LQFP (20 × 20 mm) | V850E/MA1, IA1, MS1, V850/SC1, SC2, SC3                        |

| 176-pin plastic LQFP (24 × 24 mm) | V850/SV1                                                       |

| 121-pin plastic FBGA (12 × 12 mm) | V850ES/SA3, V850/SA1                                           |

| 157-pin plastic FBGA (14 × 14 mm) | V850E/MS1                                                      |

| 161-pin plastic FBGA (13 × 13 mm) | V850E/MA1                                                      |

| 180-pin plastic FBGA (13 × 13 mm) | V850/SV1                                                       |

#### QFP package photos

100-pin plastic QFP 0.65 mm pitch, 14  $\times$  20 mm, 3.0 mm thick

100-pin plastic LQFP 0.5 mm pitch, 14  $\times$  14 mm, 1.4 mm thick

144-pin plastic LQFP 0.5 mm pitch,  $20 \times 20$  mm, 1.4 mm thick

$\label{eq:local_problem} 176\mbox{-pin plastic LQFP} \\ 0.5\mbox{ mm pitch, } 24\times24\mbox{ mm, } 1.4\mbox{ mm thick}$

#### ● FBGA package photos

121-pin plastic FBGA  $0.8 \text{ mm pitch, } 12\times12 \text{ mm, } 1.48 \text{ mm thick}$

180-pin plastic FBGA 0.8 mm pitch, 13  $\times$  13 mm, 1.48 mm thick

The Eco Symbol mark is applied to products that comply with NEC's environmental standard, which is one of the world's toughest. Such products are antimony-free and use smaller amounts of halogen, and are subject to product assessment and green procurement.

#### **Architecture**

#### V850 Common Architecture

The V850 Series, which consists of single-chip RISC microcontrollers that use an architecture optimized for embedding, has the following features.

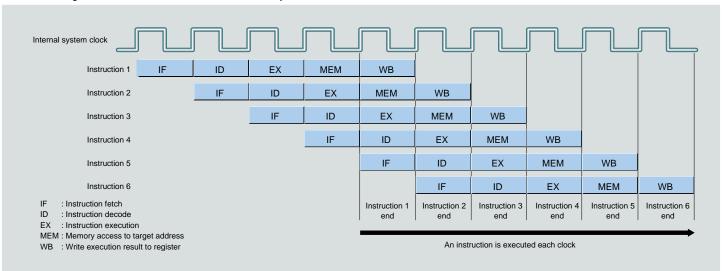

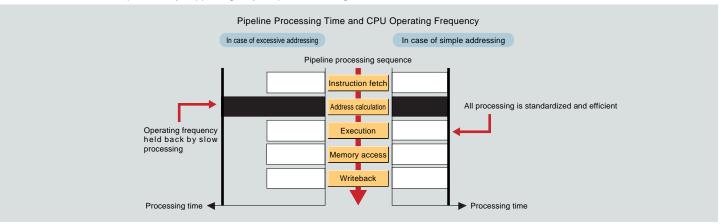

#### ■5-stage pipeline processing

The V850 Series uses a 5-stage pipeline structure (5 stages from instruction fetch to writeback) that supports simultaneous processing of 5 instructions, thus enabling the execution of almost all instructions in just one clock.

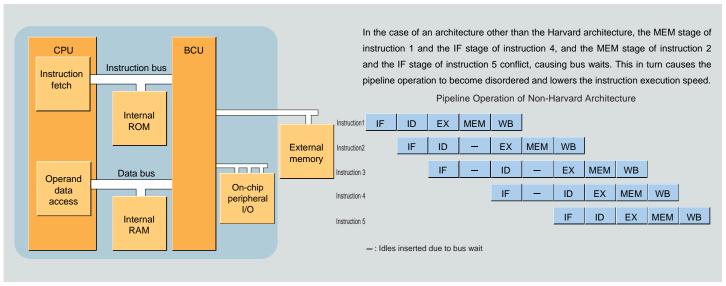

#### ■Harvard architecture

The V850 Series uses the Harvard architecture, which is designed so that the instruction bus and data bus can operate completely independently from each other, thereby preventing pipeline operation problems and ensuring efficient instruction execution.

#### ■32 general-purpose registers

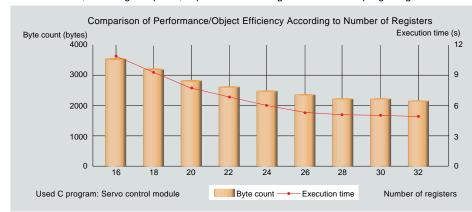

The V850 Series provides 32 general-purpose registers. Along with a hardware environment that is ideal for program execution, the development environment, including compilers, exploits these 32 registers to achieve program generation with superior code efficiency and execution performance.

For example, looking at the program execution time and code size changes when the number of registers used by the compiler is changed using the servo control module, we can see that the larger the number of registers, the better the program execution speed and the smaller the code size. However, from about 26 registers, the improvement in terms of execution speed and code size becomes smaller, and in the neighborhood of 32 registers, there are no more changes. This is why the V850 Series has been provided with 32 registers as the strict minimum requirement.

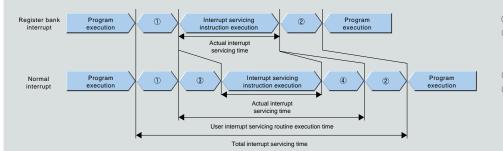

#### ■Software register bank

The number of registers can be selected from among 22, 26, and 32 as a compiler option to efficiently execute application programs. Unused registers can be used as a software register bank for which save and restore processing is not required during interrupt servicing or task switching, which increases the processing speed.

- ① Save the program counter, etc., to a save register.

- ② Execute the interrupt restore instruction. Restore the program counter value, etc., from the save register.

- ③ Save general-purpose registers to stacks.

- ④ Restore general-purpose registers from stacks.

#### ■General-purpose register configuration

| r0 Zero Register<br>r1 Reserved for Address Generation         | Name   | Application                            | Operation                                                                                         |

|----------------------------------------------------------------|--------|----------------------------------------|---------------------------------------------------------------------------------------------------|

| r2<br>r3 Stack Pointer(SP)                                     | r0     | Zero register                          | Always holds "0"                                                                                  |

| r4 Global Pointer(GP) r5 Text Pointer(TP) r6                   | r1     | Assembler reservation                  | Used as working register for address generation                                                   |

| r7<br>r8<br>r9<br>r10<br>r11                                   | r2     | Address/data var<br>(If real-time OS b | iable register<br>peing used does not use r2)                                                     |

| 113<br>114<br>115<br>116                                       | r3     | Stack pointer                          | Used for stack frame generation during function call                                              |

| 116<br>117<br>118                                              | г4     | Global pointer                         | Used when accessing globa variables in the data area                                              |

| 120<br>121<br>122<br>123<br>123<br>124<br>125                  | r5     | Text pointer                           | Used as register<br>for specifying<br>the beginning of the text area<br>(program code allocation) |

| r26<br>r27<br>r28<br>r29                                       | r6-r29 | Address/data var                       | riable register                                                                                   |

| 30 Element Pointer(EP) 31 Link Pointer(LP) CPC Program Counter | r30    | Element pointer                        | Used as base pointer<br>for address<br>generation during memory<br>access                         |

|                                                                | r31    | Link pointer                           | Used during function call by compiler                                                             |

|                                                                | PC     | Program counter                        | Holds instruction addresses during program execution                                              |

#### ■System register configuration

|                            | No.          | System        |                         | rand<br>fication | Application                              |

|----------------------------|--------------|---------------|-------------------------|------------------|------------------------------------------|

|                            |              | Register Name | LDSR                    | STSR             |                                          |

|                            | 0            | EIPC          | 0                       | 0                | Register for saving status               |

|                            | 1            | EIPSW         | 0                       | 0                | during interrupt                         |

|                            | 2            | FEPC          | 0                       | 0                | Register for saving status               |

|                            | 3            | FEPSW         | 0                       | 0                | during NMI                               |

|                            | 4            | ECR           | ×                       | 0                | Interrupt source register                |

|                            | 5            | PSW           | 0                       | 0                | Program status word                      |

| []                         | 16           | CTPC          | 0                       | 0                | Register for saving status               |

| Only supported by          | 17           | CTPSW         | 0                       | 0                | during CALLT execution                   |

| V850E1 CPU (               | 18           | DBPC          | 0                       | 0                | Register for saving status               |

| core products<br>supported | 19           | DBPSW         | 0                       | 0                | during exception/debug trap              |

| · · · [                    | 20           | CTBP          | 0                       | 0                | CALLT base pointer                       |

|                            | 6-15, 21-31  | Reserved      | ×                       | ×                |                                          |

| >                          | : Access pro |               |                         |                  | d general-purpose register<br>m register |

|                            | : Access en  |               | Instruction<br>general- |                  | e system register contents t<br>register |

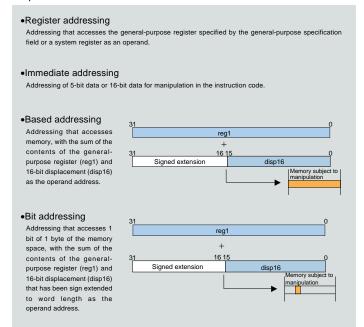

#### ■Simple addressing

The increased amount of address calculations in the CPU in the case of complex addressing causes disturbances in the pipeline operation. As a result, address calculation becomes a bottleneck for pipeline processing and raising the frequency to increase the performance becomes difficult. The V850 Series avoids this problem by supporting only simple addressing.

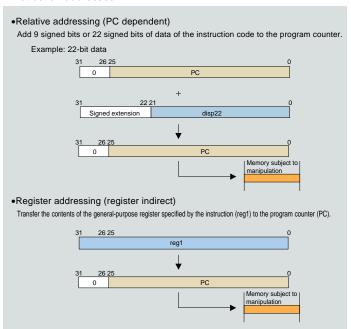

#### ■Addressing mode

#### Instruction addresses

#### Operand addresses

1.48

#### ■2-byte basic instruction set

The V850 Series employs a 2-byte instruction code to perform basic processing to enable compact program development equivalent to 16-bit CISC microcontrollers.

Improved object efficiency through ROMization programming

Application of 2-byte instructions to all basic processing, consisting of load, store, arithmetic/

logic operations, and branching.

To realize ease of use, restrictions on 16-bit fixed-length instructions are partially removed through incorporation of 32-bit instructions.

Bit manipulation instructions, etc.

78K/IV(CISC)

1.00

78K/IV(CISC)

1.02

V<sub>R</sub>/MIPS32(RISC)

#### ■ CISC-like instructions for embedding (bit manipulation instructions)

The V850 Series supports bit manipulation instructions suitable for flag manipulation on I/O registers, which play a large role in embedding control.

- Improvement of operability of memory mapped I/ Os for control purposes

- Manipulation of any 1 bit of byte data in the memory space

- Provision of test (tst1)/set (set1)/clear (clr1)/invert (not1)

- Effective for reducing object size and execution time since flags can be manipulated in 1-bit units with 1 instruction

|                              | Example: Setting   | (1) bit 6 of ASIM00 registe                                          | er                                                                                                                                                             |

|------------------------------|--------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Manipulation Instruction |                    | When                                                                 | Used                                                                                                                                                           |

| Coding example               | set1 6, ASIM00[r0] | ld.b ASIM00[r0], r20<br>ori 0x0040, r20, r20<br>st.b r20, ASIM00[r0] | add -4, sp<br>st.w r20, 0[sp] ] Save r20<br>ld.b ASIM00[r0], r20<br>ori 0x0040, r20, r20<br>st.b r20, ASIM00[r0]<br>ld.w 0[sp], r20<br>add 4, sp ] Restore r20 |

| Object size                  | 4 bytes            | 12 bytes                                                             | 24 bytes                                                                                                                                                       |

| Execution time               | 4 clocks           | 4 clocks                                                             | 8 clocks                                                                                                                                                       |

#### ■ Multi-status flags

In the V850 Series, calculation results are reflected in registers as status flags. As a result, delay branching such as can be seen in the RISC microcontrollers of other manufacturers does not occur and programs can be coded with the same feel as CISC microcontrollers.

- Easy recording with assembler

- Improved object efficiency and execution speed

ZERO: Zero processing

PLUS: Positive processing

MINUS: Negative processing

Example: Program that branches to positive/negative/zero according to register contents

| CISC Microcontroller                          | V850                                          | Other Manufacturer's RISC Microcontroller                                                                                                                                      |

|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cmp ax, 0<br>jz ZERO<br>jgt PLUS<br>jmp MINUS | cmp 0, r10<br>bz ZERO<br>bgt PLUS<br>br MINUS | cmp/eq         #0, r10           bt         ZERO           cmp/pl         r10           bt         PLUS           bra         MINUS           nop         ;For delay branching |

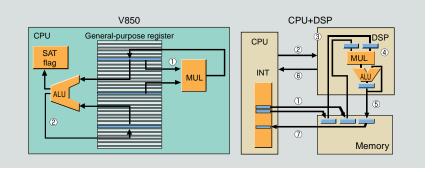

#### **■ DSP function**

The V850 Series provides a DSP function for executing high-speed calculations and product-sum operations indispensable for digital signal processing such as image and speech processing.

- Direct data handling via general-purpose registers

- Realization of digital signal processing through generalpurpose CPU

- High-speed 16-bit (V850 CPU), 32-bit (V850E1 CPU) multiply/sum-of-products

- (Multiply: 1 to 2 clocks, sum-of-products: 3 clocks)

- Effective for filter operations and matrix operations for feedback calculations in speed, position, and other servo control.

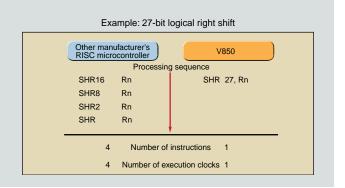

#### ■ 32-bit barrel shifter

V850 Series can realize bit manipulations frequently used during signed data and image data processing in 1 instruction per clock.

Shifting of any number of bits (0 to 31) executable in 1 instruction per clock Improved execution speed/object efficiency

Effective for extracting arbitrary bit lengths of image data and signed data (extracting code during MH/MR/MMR encoding, etc.)

#### Strengths of V850E1 and V850ES Cores

The V850E1 and V850ES cores are CPU cores that enhance the functions of the V850 core.

#### ■ V850E1 core

- Higher performance and improved operating frequency of 50 to 100 MHz

- •Improved external memory access function

- •Improved code efficiency (10 to 15% higher than V850 core)

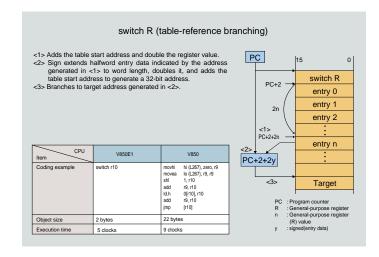

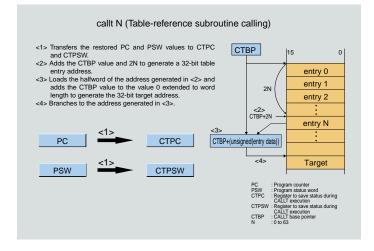

- •Addition of C language compatible instructions (Switch instruction, CALLT instruction, etc.)

- ●High performance high-end lineup (V850E products), system-on-chip core lineup

#### ■ V850ES core

- ●Next-generation CPU core of low-end lineup

- ●Support of lower voltage for V850/Sxx products

- ●Improved code efficiency through use of same architecture as V850E1 (10 to 15% higher than V850 core)

| CPU Core<br>Function         | V850                                                   | V850ES                                                                                                                                                            | V850E1                         |

|------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Maximum operating frequency  | 20/33 MHz                                              | 20 MHz                                                                                                                                                            | 50→100MHz                      |

| Maximum program memory space | 16 MB                                                  | 16 MB                                                                                                                                                             | 64 MB                          |

| Maximum data memory space    | 16 MB                                                  | 16 MB                                                                                                                                                             | 256 MB                         |

| Higher performance           | Use of 5-stage pipeline<br>Use of Harvard architecture | Improvement of pipeline  Non-blocking load/store Parallel execution of instructions internal ROM)  Addition of branch/load pipes Shift to 3-operand manipulations |                                |

| Higher code efficiency       | Use of 2-byte instructions<br>Use of CISC instructions | Addition of C language compatible (Addition of Switch instruction, Call instruction, Prepare/Dispose instru                                                       | t instruction, data conversion |

| Multiplier                   | 16 × 16 bit→32 bit                                     | 16 × 16 bit → 32 bit<br>(32-bit multiply instruction support)                                                                                                     | 32 × 32 bit →64 bit            |

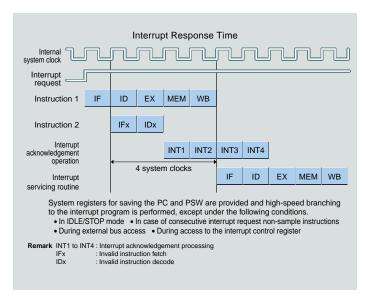

| Interrupt responsiveness     | 11 to 18 clocks                                        | 4 to 10 clocks                                                                                                                                                    |                                |

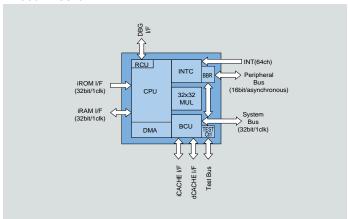

#### **Employment as ASIC CPU Cores**

- ♦ Smooth transition to ASIC microcontroller development using V850E1 CPU cores

- 1. Introduction to market with short TAT through use of standard V850E1 products

- 2. Optimization of system through switch to ASIC

- ♦ Easy securing of compatibility from traditional systems made into ASICs through use of same device development methods for both standard products and ASIC microcontrollers

- ◆ Development of CPU cores bearing in mind shift to ASIC

- Software debugging support

Release of CPU core that supports on-chip debugging through full-function in-circuit emulator, JTAG method (N-Wire ICE) and on-chip debugging with trace function

Internal system bus configuration

Independent high-speed 32-bit synchronous system bus and 16-bit asynchronous bus for low-speed peripheral function macro connection, realizing both high-speed processing, low-power consumption and easy design

Provision of large assortment of peripheral function macros

Cache memory, memory controller, ROM/RAM, USB, etc.

◆ Covering required performance and power consumption through support of a large variety of processes

| Process               | Cell-based IC family |

|-----------------------|----------------------|

| $0.35 \mu m$          | CB-9VX               |

| $0.25 \mu \mathrm{m}$ | CB-10VX              |

| 0.13 <i>μ</i> m       | CB-12                |

#### ■V850E1 core

- Realization of excellent performance/power ratio of 827 MIPS/W for 100 MHz Max. (at 2.5 V operation)

- Improved object efficiency

- A flexible and high-performance bus system can be configured through independent buses such as a high-speed system bus that enables 400 MB/s data transfer and a low-speed peripheral macro connection bus.

- Support of on-chip debugging function

#### ■V850E1 core

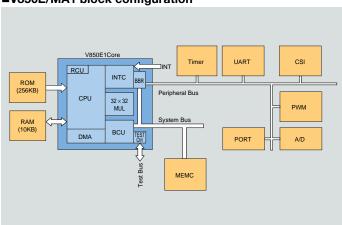

#### ■V850E/MA1 block configuration

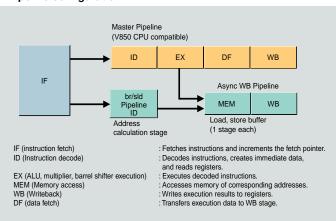

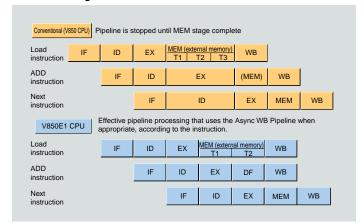

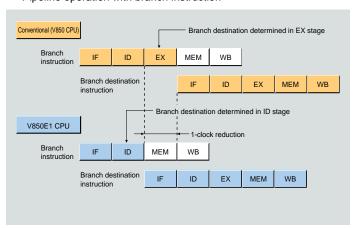

#### ■V850E1, V850ES architecture

The V850E1 and V850ES cores achieve high performance and higher code efficiency through the implementation of the following improvements to the V850 CPU core.

#### Non-blocking load/store

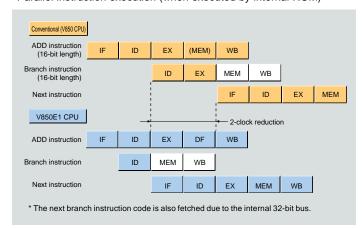

#### Addition of branch/load pipes

- · Improved bus use efficiency

- Shorter interrupt insensitivity period

- 2-clock branching

- Parallel execution of instructions

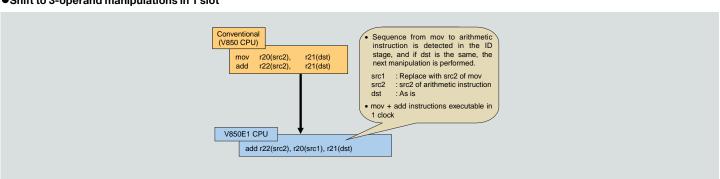

#### Shift to 3-operand manipulations in 1 slot

- Improved absolute performance

- Example: Synchronous processing of mov + add

#### Addition of high-level language-compatible instruction

- Improved code efficiency

- 10 to 15% improvement in object efficiency mainly when C compiler used

#### Pipeline configuration

#### ●Non-blocking load/store

#### Addition of branch/load pipes

•Pipeline operation with branch instruction

•Parallel instruction execution (when executed by internal ROM)

#### Shift to 3-operand manipulations in 1 slot

Pamphlet U15412EJ1V0PF

#### Addition of high-level language compatible instructions

The V850E1 and V850ES cores have enhanced the instruction set of the V850 core as follows.

- ◆ switch (2 bytes)

- C language switch statement processing converted into instruction

- callt (2 bytes)/ctret (4 bytes)

- Table-reference branching

- Reducing size of call code that frequently appears

- ◆ Data conversion instructions (2 bytes)

- char, short type cast executed with 1 instruction

- sxh, sxb, zxb, and zxh instructions

- ◆ prepare/dispose (4 bytes)

- Function start/end processing executed in 1 instruction

- unsigned Load

- Reduction of unsigned manipulation code

- ♦ mov imm32, reg (6 bytes/2 clocks)

- Reduction of address setting code

- ♦ mul/mulu (4 bytes)

- Reduction of array address calculation

- Improvement of sum-of-products performance

- ◆ Other

- Bit manipulation (register indirect bit specification)

- cmov (Conditional Move), divide (div/divu/divhu)

- · sasf, endian conversion

#### **Middleware Performance**

#### ■Measurement conditions

●Common

CPU : V850 core (33 MHz)

Measurement results are frequency-converted values (50 MHz).

Bus width : 16 bits Number of waits : 1

(The basic bus cycle is 3 clocks, so 1 bus cycle = 4 clocks.)

Compiler : CA850

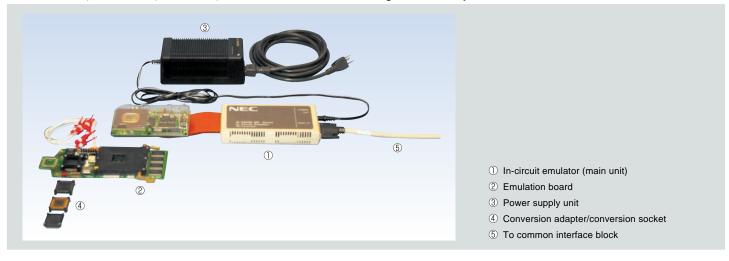

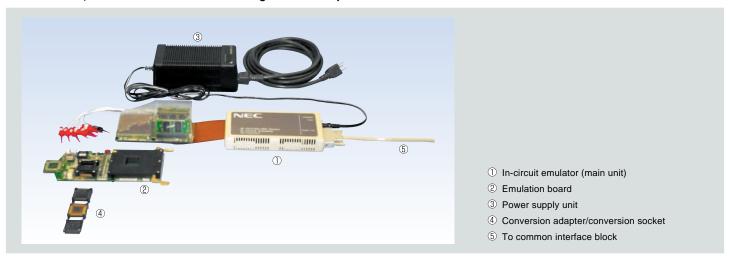

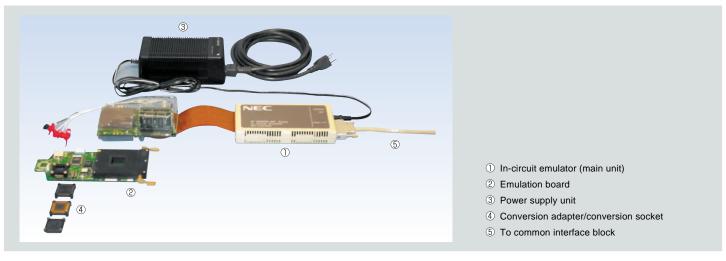

Tool : V850 in-circuit emulator (IE) (product of NEC)

#### JPEG

Internal ROM : Program

Internal RAM : Stack, work area (one part)

External memory (SRAM) : Data and remaining work area

Data I/O : RGB

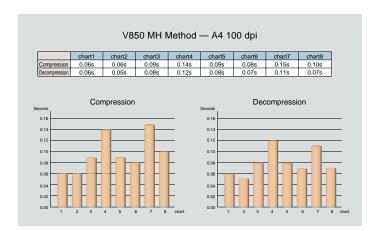

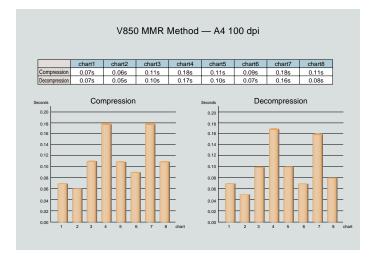

#### ●MH/MR/MMR

• Internal ROM : Program

• External memory (SRAM) : Encoding/decoding table, change point table,

stacks (including I/O parameters)

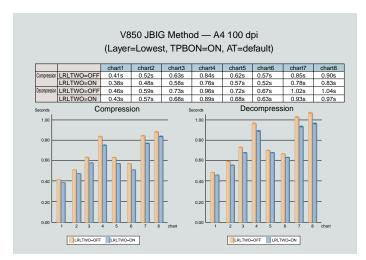

#### JBIG

Internal ROM : Program (including probability assumption table (1 KB))

External memory (SRAM) : Learning table, stacks (including I/O parameters)

|               | chart1   | chart2    | chart3 | chart4   | chart5  | chart6                     | chart7    | chart8 |

|---------------|----------|-----------|--------|----------|---------|----------------------------|-----------|--------|

| Compression   | 0.07s    | 0.06s     | 0.10s  | 0.17s    | 0.11s   | 0.09s                      | 0.18s     | 0.11s  |

| Decompression | 0.07s    | 0.06s     | 0.10s  | 0.16s    | 0.10s   | 0.08s                      | 0.15s     | 0.08s  |

| conds         | Con      | npression |        |          | Seconds | Dec                        | compressi | on     |

| 0.20          |          |           |        | _        | 0.20    |                            |           |        |

| 0.18          |          |           |        | _        | 0.18    |                            |           |        |

| 0.16          |          | 1         |        | _        | 0.16    |                            |           |        |

| 0.14          |          | _         | _      | _        | 0.14    |                            |           |        |

| 0.12          |          |           | _      | _        | 0.12    |                            |           |        |

| 0.10          |          |           |        | L        | 0.10    |                            |           |        |

|               |          |           | - 11   |          |         |                            |           |        |

| 0.08          |          | ΠП        |        |          | 0.08    |                            |           |        |

| 0.06          |          | HH        | HH     | _        | 0.06    |                            |           | HH     |

| 0.04          | $\vdash$ | H         | H      | <u> </u> | 0.04    | $\vdash$ $\vdash$ $\vdash$ |           | HH     |

|                          | V850 JI     | PEG Metho     | d           |               |

|--------------------------|-------------|---------------|-------------|---------------|

|                          |             | Process       | ing Time    |               |

| Sample ratio             | QVGA(320    | 0×240×24)     | VGA(640     | ×480×24)      |

| Sample ratio             | Compression | Decompression | Compression | Decompression |

| 4 : 1 : 1<br>(Quality75) | 0.27s       | 0.21s         | 1.09s       | 0.85s         |

| 4 : 2 : 2<br>(Quality75) | 0.33s       | 0.26s         | 1.33s       | 1.04s         |

### Variety of Peripheral Functions

#### **Memory Access Functions**

#### **■SDRAM** controller

Products: V850E/MA1, MA2

- ◆ SDRAM connectable without external circuit

- ◆ CAS latency: 2, 3 supported

- ◆ CBR refresh, CBR self refresh supported

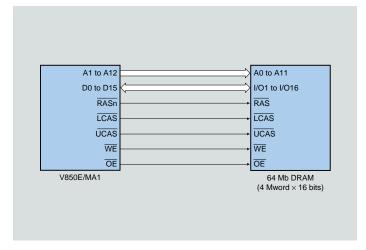

#### **■DRAM** controller

Products: V850E/MS1, MS2, MA1

- ◆ EDO DRAM directly connectable without external circuit

- ◆ 2CAS type DRAM supported

- ◆ CBR refresh, CBR self refresh supported

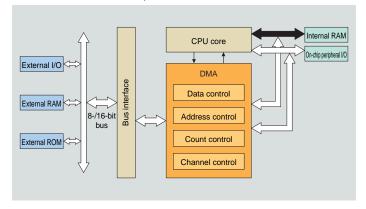

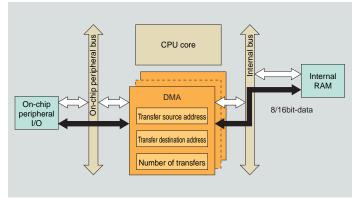

#### ■DMA controller (provided in V850E products)

Products: V850E/MA1, MA2, MS1, MS2, IA1, IA2

- ◆ Transfer targets: Memory-peripheral I/O, memory-memory

- ◆ Single, single step, block transfer

- ♦ 8-/16-bit data units

- ◆ Transfer type: 1-cycle transfer, 2-cycle transfer

- ◆ Number of transfers: 65,536 Max.

#### ■DMA controller (provided in V850/Sxx products)

Products: V850/SA1, SB1, SB2, SV1, SF1, SC1, SC2, SC3

- ◆Transfer targets: Internal RAM-on-chip peripheral I/O

- ◆Single transfer

- ♦ 8-/16-bit data units

- ◆Transfer clock: 4 clocks Min.

- ♦Number of transfers: 256 Max.

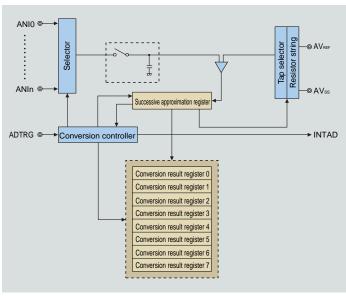

### A/D Converters

#### ■Multi-stage buffer type

Products: V853, V850/SV1, V850E/MA1, IA1, IA2, MS1

- ◆ Conversion can be started by both software and hardware

- ◆ Eight conversion result registers are incorporated

- ◆ Select/scan modes can be switched

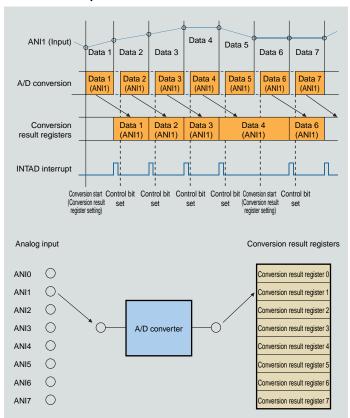

#### ■Select mode operation

28

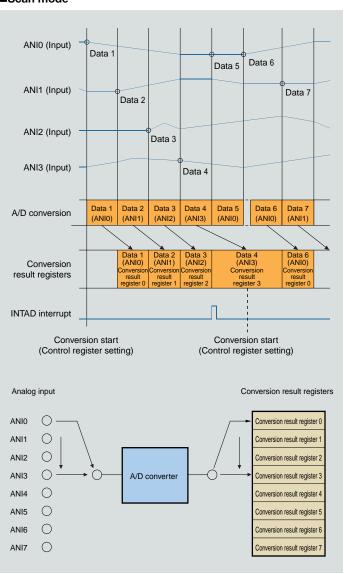

#### ■Scan mode

Pamphlet U15412EJ1V0PF

#### **Timer/Counter Functions**

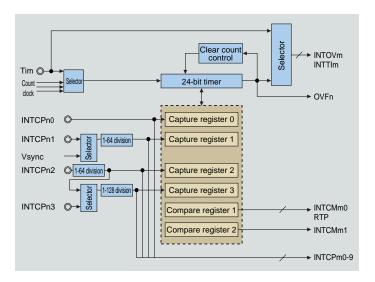

#### ■24-bit servo timer

Product: V850/SV1

- ◆ 24-bit timer unit for servo control

- Capture registers: 4Compare registers: 2

- ◆ External input detector with 1-64/1-128 divider

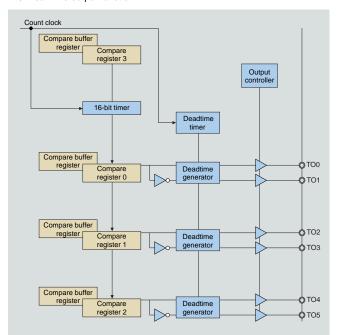

#### ■3-phase inverter control timer

Products: V850E/IA1, IA2

- ◆ 3-phase PWM output function

- Symmetric triangular wave, asymmetric triangular wave, sawtooth wave

- ◆ Interrupt culling function

Culling rate: 1/1, 1/2, 1/3, 1/4, 1/8, 1/16

- ◆ 3-phase PWM forcible output stop function

- ♦ Real-time output function

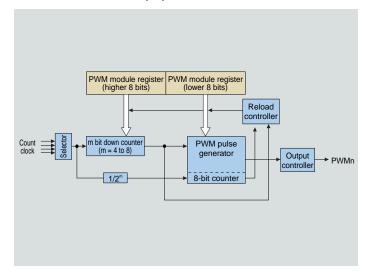

#### **■**PWM

Product: V850/SV1

- ◆ 12- to 16-bit PWM output

- Main pulse + additional pulse configuration Main pulse: 4/5/6/7/8 bits

Additional pulse: 8 bits

- ◆ Active level of PWM output pulse selectable

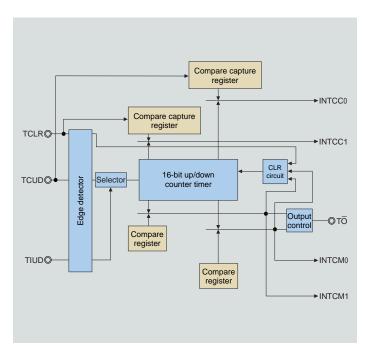

#### ■Up/down counter

Products: V850E/IA1, IA2

- ◆ 16-bit 2-phase encoder input supported

- ◆ Compare registers: 2

- ◆ Capture/compare registers: 2

#### **Serial Interface**

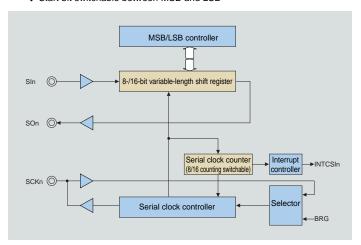

#### ■Variable-length serial interface

Products: V850/SB1, SB2, SV1, SF1, SC1, SC2, SC3

- ◆ 3-wire serial I/O

- ◆ Data length switchable between 8 bits and 16 bits

- ◆ Start bit switchable between MSB and LSB

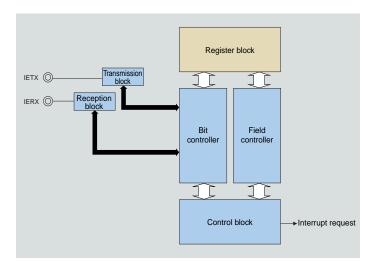

#### ■IEBus controller

30

Products: V850/SB2, SC2

◆ Supports communication mode 1

◆ Maximum number of transfer bytes: 32 bytes/frame

◆ Maximum transfer speed: Approx. 17 Kbps

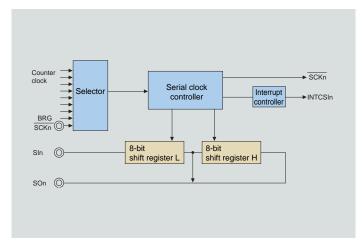

#### ■8-/16-bit serial interface

Products: V850/SC1, SC2, SC3, V850E/IA1, IA2

- ♦ 3-wire serial I/O

- ◆ Data length switchable between 8 bits and 16 bits

- ◆ Start bit switchable between MSB and LSB

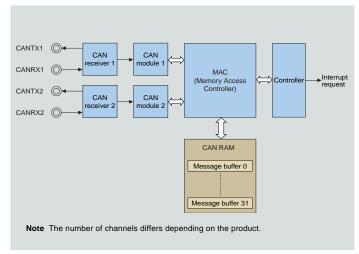

#### **■**CAN

Products: V850E/IA1, V850/SF1, SC3

◆ CAN protocol Ver. 2.0 Part B

(Transmission/reception of standard and extended frames)

- ◆ Maximum transfer rate: 1 Mbps

- ♦ 32 message buffers

Pamphlet U15412EJ1V0PF

#### **Distinctive Peripheral Functions of V850**

#### ■Watch timer

Products: V850/SB1, SB2, SV1, SC1, SC2, SC3

- ◆ 0.5-second interrupt generation using watch timer function

- ◆ Interval timer supported

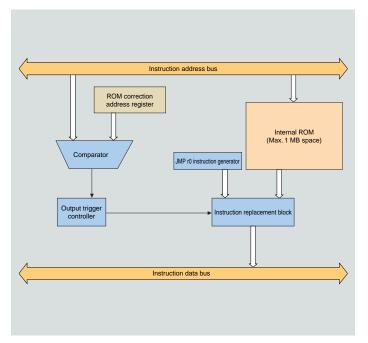

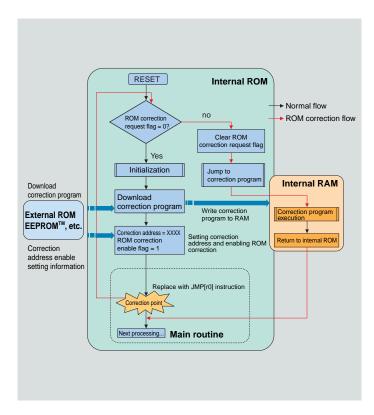

#### ■ROM correction function

Products: V850/SB1, SB2, SV1, SF1, SC1, SC2, SC3

- ◆ Substitutes JMP r0 instruction for instruction of address to be corrected and branches to 0000H

- ◆ Program can be modified following creation of mask ROM

- ◆ Correction addresses: 4 points

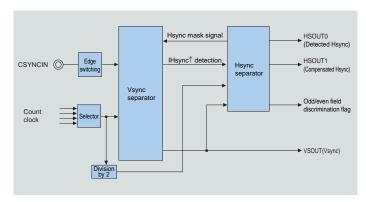

#### ■Hsync/Vsync separator

Product: V850/SV1

- Separation of Vsync (vertical) signal and Hsync (horizontal) signal from decoding sync signal of VCR

- ◆ Odd/even field discrimination

#### **■ROM** correction operation

#### Low Power & Low Noise

#### **Low Power Consumption Measures**

Low-power-consuming, high-speed microcontrollers are required for portable devices and battery-operated devices such as DVCs and cellular phones. The V850 Series incorporates various functions to lower the power consumption.

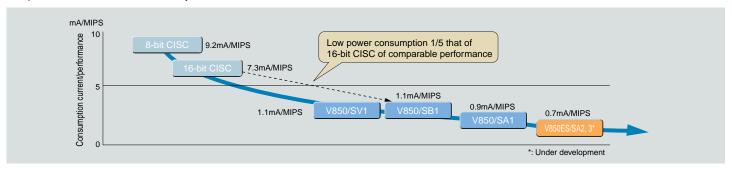

#### ■Superior power performance

The V850ES and V850/Sxx products feature a thorough power-saving design that realizes a superb power/performance ratio of 1.1 to 0.7 mA/MIPS. As a result, these products realize a low consumption current only one fifth that of a 16-bit CISC microcontroller of comparable performance. By featuring such extremely high power performance, these products enable the simultaneous realization of lower power consumption and more sophisticated functions in various systems.

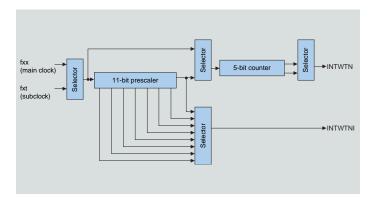

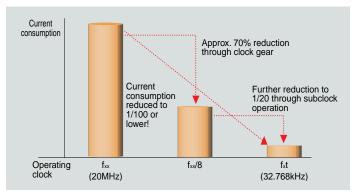

#### **■Clock** gear function

The V850/Sxx products come with two oscillators: a main clock and a subclock. 1/1/, 1/2, 1/4, or 1/8 of the main clock or the subclock  $^{\text{Note}}$  can be selected as the CPU operating clock, making it possible to minimize the power consumption according to the system's operating status.

Note Not selectable in V850/SV1

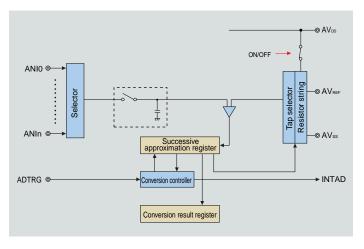

### ■Function to cut voltage between A/D converter VREF and resistor string

Voltage application to the A/D converter's resistor string can be switched on and off. The power consumption can be minimized by switching off voltage application to the resistor string when the A/D converter is not used.

Main products: V850/SB1, SB2, SC1, SC2, SC3, SF1

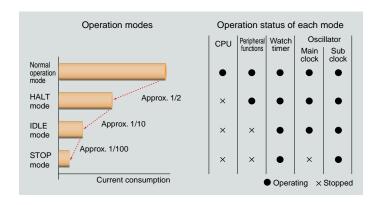

#### **■**Standby mode

An efficient low-power-consumption system can be realized by using the three standby modes, STOP, IDLE, and HALT, according to the usage purpose.

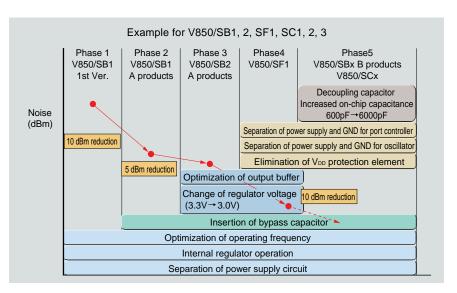

#### **EMI Countermeasures**

Minimizing the influence of electromagnetic interference (EMI) from the microcontroller in AV equipment such as car audio systems is a major requirement, making the reduction of EMI one of the highest technological priorities for microcontroller manufacturers. Various EMI countermeasures are implemented in the V850 Series.

#### ■EMI countermeasures for individual chip

Noise reduction measures focusing on the following three points are implemented as noise countermeasures in individual V850 Series chips.

- ◆ Reduction of noise generation

- Use of low-voltage internal logic power supply

- · Optimization of oscillator

- ◆ Reduction of noise propagation

- Separation of internal logic sound source and power supply of pins

- Reduction of cross talk between different power supply wires

- Confining of noise inside

- On-chip decoupling capacitor between power supply and GND inside microcontroller

- · Separation of power supply and GND for oscillator

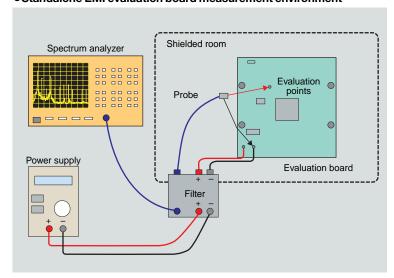

#### ■Standardization of evaluation methods (1/2)

There are no rules regarding the EMI measurement testing method for individual microcontrollers. NEC aims to standardize evaluation circuit constants through the use of a standalone EMI evaluation board and evaluate products in a measuring environment that uses a shielded room and power supply filters. This approach enables the evaluation of different products (8-bit and 16-bit NEC CISC microcontrollers, etc.) in the same environment.

#### ●Standalone EMI evaluation board

#### Standalone EMI evaluation board measurement environment

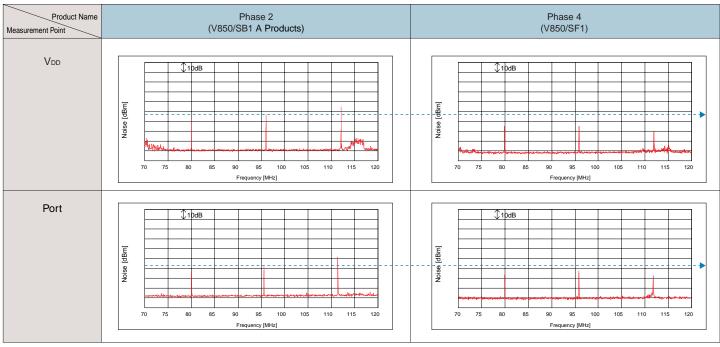

#### ■Standardization of evaluation methods (2/2)

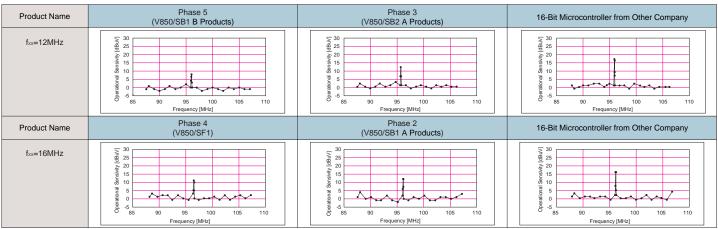

#### ●EMI evaluation results

A comparison of the EMI evaluation results for Phase 2 products (V850/SB1 A products) and Phase 4 products (V850/SF1) is shown below.

Remark Oscillation frequency = 16 MHz

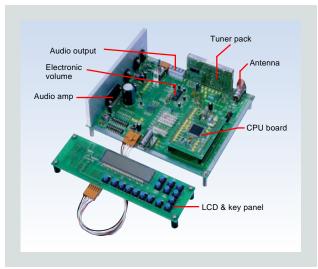

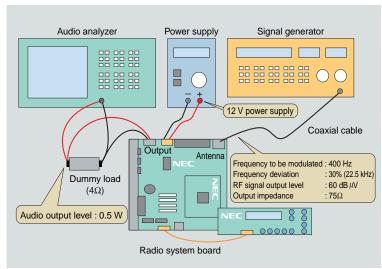

#### ■Evaluation of characteristics using radio system board (1/2)

In addition to EMI measurement using a standalone EMI evaluation board, NEC has also established an evaluation method employing set evaluation criteria using a radio system board. Since the evaluation results obtained with the radio evaluation board match the evaluation method established by the customer, the influence of EMI can be judged directly.

#### ●Radio system board

34

#### • Radio system board measurement environment

Pamphlet U15412EJ1V0PF

#### ■Evaluation of characteristics using radio system board (2/2)

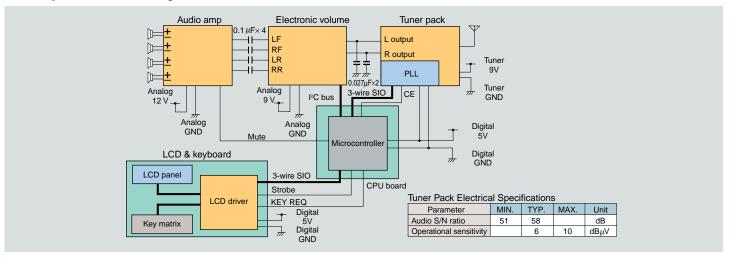

#### •Radio system board block diagram

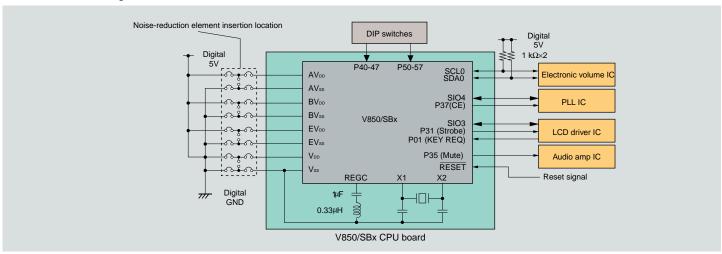

#### ●CPU board block diagram

#### •Results of characteristics evaluation using radio system board

The EMI reduction efficiency can be ascertained with a radio system board in the same way as standalone microcontroller evaluation.

Remark fxx: Oscillation frequency

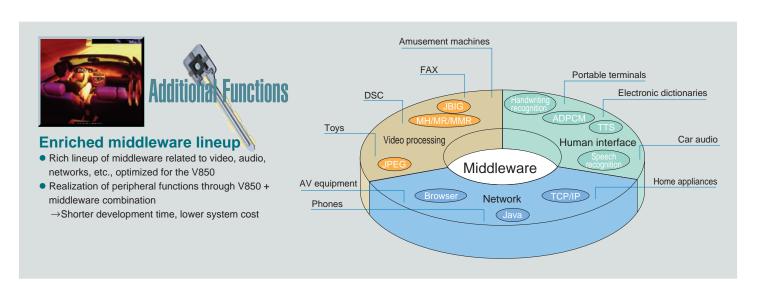

#### **Middleware**

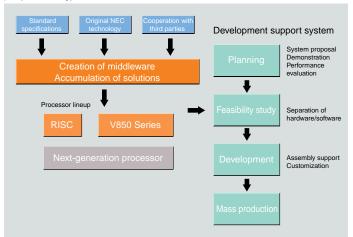

#### Middleware Development System

NEC is developing a range of middleware products suitable to processors for various systems. NEC middleware is realized by original NEC technology, superior third-party technology, and established standards.

#### **JPEG**

#### Conforms to JPEG international standard

Conforms to DCT baseline process (non-reverse coding)

#### Versatile compression and decompression processing

- <Compression functions>

- User-customizable VRAM input module

- User-specified Huffman and quantization tables

- APPn marker insertion

- Compression suspend function

- <Decompressing processing>

- User-customizable VRAM output module

- Support of various JPEG markers (DRI, RSTn, DNL)

- Decompressing suspend function

|                                  |                                                 |          |           |         | Proces                 | sing Time               |               |

|----------------------------------|-------------------------------------------------|----------|-----------|---------|------------------------|-------------------------|---------------|

| CPU                              | Sample F                                        | Ratio    | QVG       | A (320  | 0×240×24)              | VGA (64                 | 0×480×24)     |

|                                  |                                                 |          | Compressi | ion     | Decompression          | Compression             | Decompression |

| V850E/MS                         |                                                 |          | 0.32s     |         | 0.24s                  | 1.3s                    | 0.97s         |

|                                  |                                                 | M, and   |           | k areas | s (one part) are place | ed in internal RAM. [   | Data and the  |

| lote Programs are remaining work | placed in internal RC<br>k area are placed in e | M, and   | RAM.      |         | s (one part) are place | Led in internal RAM. [  | Data and the  |

| lote Programs are remaining work | placed in internal RC                           | M, and : | RAM.      |         | s (one part) are place | Leed in internal RAM. [ | Data and the  |

| lote Programs are remaining work | placed in internal RC<br>k area are placed in e | M, and : | RAM.      | AM.     | s (one part) are place | Led in internal RAM. I  | Data and the  |

#### Middleware Development

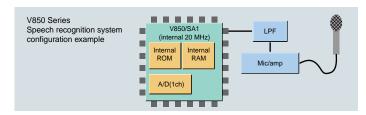

#### **V850 Series Speech Recognition**

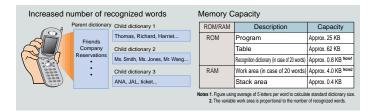

The V850 Series uses internal memory and peripheral I/Os to realize speech recognition on one chip. This makes this series ideal for applications that require speech recognition in sets with large constraints, such as games and home appliances.

- Speech recognition realized using just the internal memory and peripheral I/Os of V850 Series

- Increased number of recognized words

Number of recognized words: 30 (for V850/SA1, 20 MHz)

#### Speech recognition evaluation system

In introducing speech recognition, NEC has provided an environment that allows easy evaluation.

For details about this system or how to purchase it, contact NEC.

# **Handwriting Recognition (Japanese Only)**

- Easy to use because of flexibility regarding stroke order and count Pattern matching method based on "non-linear normalization matching method" Conversion of pen-drawn lines into image

- High recognition rate, high-speed recognition Recognition of 95% or higher in 0.1 s (V85x: 25 MHz)

- Support of up to JIS No. 2 standard JIS No. 1 Standard: Approx. 3,400 characters, JIS No. 2 Standard: Approx. 800

- New characters can be added (pictographs, etc., can be freely

A dictionary can be created from character data using a dictionary compilation tool.

| ROM/RAM | Description                                | Capacity       |

|---------|--------------------------------------------|----------------|

| ROM     | Program                                    | Approx. 60 KB  |

|         | Dictionary data (approx. 4,200 characters) | Approx. 450 KB |

|         | Data                                       | Approx. 60 KB  |

| RAM     | Work area                                  | Approx. 32 KB  |

|         | Stack area                                 | Approx. 2 KB   |

# Text to Speech (TTS) (For Japanese Text)

- Speech synthesized from Japanese Kana and Kanji texts (SJIS code)

- Versatile speech synthesis

Synthesis of male and female voices (2 types)

Various parameters such as intonation and reading speed can be adjusted.

●TTS rhythm data (pitch, phoneme duration) can be designed (Support of Speech Designer)

TTS using natural rhythm possible (synthesis of more natural sounding speech)

- Support of characters with special readings (character readings) can be set using the user dictionary)

- Synthesis speed (V853: 25 MHz)

Speech: Between 1.9 s<sup>Note</sup> and 3 s; Text analysis: 163 ms; speech generation:

Note Varies depending on the input character string.

| ROM/RAM | Description                            | Capacity                 |

|---------|----------------------------------------|--------------------------|

| ROM     | Program data                           | Approx. 103 KB           |

|         | Dictionary data (approx. 80,000 words) | Approx. 1.2 MB           |

|         | Phoneme data                           | Approx. 670 KB to 1.4 MB |

| RAM     | Work area                              | Approx. 160 KB           |

|         | Stack area                             | Approx. 256 KB           |

|         | Speech output buffer                   | Approx. 8 KB × n blocks  |

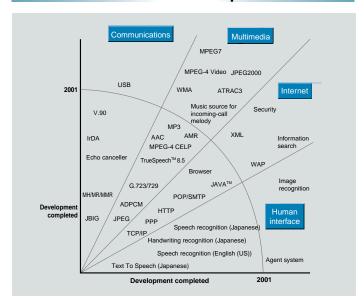

# Middleware Product List

### ■ Middleware list

| Category    | Mic                       | dleware                         | V850 Series |

|-------------|---------------------------|---------------------------------|-------------|

| Image       | MH/MR/MMR                 |                                 | 0           |

|             | JBIG                      |                                 | 0           |

|             | JPEG                      |                                 | 0           |

| Speech      | Text To Speech            | Japanese                        | 0           |

|             | Speech CODEC              | G.726 (ADPCM)                   | 0           |

| Recognition | Speech recognition        | Japanese (small vocabulary)     | 0           |

|             | Speech recognition        | English (US) (small vocabulary) | 0           |

|             | Handwriting recognition   | Japanese (input frame required) | 0           |

| Internet    | Browser                   |                                 | 0           |

|             | TCP/IP                    |                                 | 0           |

| Drivers     | IrDA protocol stack       |                                 | 0           |

|             | USB                       |                                 | Δ           |

|             | IEEE1394                  |                                 | 0           |

|             | PCMCIA/CF card            |                                 | 0           |

|             | PC-compatible file system |                                 | 0           |

| Other       | Font                      |                                 | 0           |

- 1. ①: Development completed; ○: Under development; △: In planning

2. Third-party products included.

3. For details about middleware products, refer to the following http://www.ic.nec.co.jp/apsoft/english/middle\_top.html

### Middleware performance

| Middleware                            | Performance                   | Power(MIPS)    | ROM     | RAM        |

|---------------------------------------|-------------------------------|----------------|---------|------------|

| MH/MR/MMR                             | MH Chart1 : Enc0.12s/Dec0.08s | _              | 64 KB   | 200 bytes  |

| JBIG                                  | Chart1: Enc0.73s/Dec0.83s     | _              | 21 KB   | 2.6 KB     |

| JPEG                                  | QVGA × 24 : Enc0.32s/Dec0.24s | _              | 17.5 KB | 15 KB      |

| G.726(ADPCM)                          | 32Kbps, 16Kbps                | Enc8/Dec8.2    | 9 KB    | 80 bytes   |

| Speech recognition (small vocabulary) | 0.4s                          | 19 (20 words)  | 82 KB   | 3.5 KB     |

|                                       |                               | 63 (100 words) |         | (15 words) |

| Handwriting recognition               | 0.1s/character                | 14             | 570 KB  | 34 KB      |

| (Japanese, input frame required)      |                               |                |         |            |

| IrDA protocol stack                   |                               | _              | 60 KB   | 16 KB      |

# Flash Memory Microcontrollers

### **Features**

To answer the need for shorter development time and maintenance after shipping, NEC offers microcontrollers with on-chip flash memory available in a large range of capacities from 128 KB to 512 KB as part of the V850 Series. NEC's flash memory microcontrollers offer the following features.

- ◆ Support of batch rewrite of entire memory and rewrite in area units

- ◆ Flash memory programming with self-rewrite in area units

- Support of on-board programming through serial communication using a flash memory programmer

- ◆ Erase/write voltage: 2.5 V, 7.8 V, 10.3 V

| Flash Memory Size<br>(Bytes) | 12 | 8K |    | 256K |     | 384K | 512K |

|------------------------------|----|----|----|------|-----|------|------|

| RAM Size (Bytes)             | 4K | 6K | 8K | 10K  | 16K | 16K  | 24K  |

| V850E/MA1                    |    |    |    | 0    |     |      |      |

| V850E/IA1                    |    |    |    | 0    |     |      |      |

| V850E/IA2                    |    | 0  |    |      |     |      |      |

| V850E/MS1                    | 0  |    |    |      |     |      |      |

| V853                         | 0  |    | 0  |      |     |      |      |

| V850/SA1                     | 0  |    | 0  |      |     |      |      |

| V850/SV1                     |    |    |    |      | 0   | 0    |      |

| V850/SB1                     |    |    |    |      | 0   |      | 0    |

| V850/SB2                     |    |    |    |      | 0   |      | 0    |

| V850/SF1                     |    |    |    |      | 0   |      |      |

| V850/SC1                     |    |    |    |      |     |      | 0    |

| V850/SC2                     |    |    |    |      |     |      | 0    |

| V850/SC3                     |    |    |    |      |     |      | 0    |

| V850ES/SA2*                  |    |    |    |      | 0   |      |      |

| V850ES/SA3*                  |    |    |    |      | 0   |      |      |

\*: Under development

# **Rewrite Mode**

The V850 Series supports a programmer rewrite mode that uses serial communication supporting on-board programming, as well as a self-programming mode that rewrites flash memory with user programs, to enable continuous use from development to maintenance.

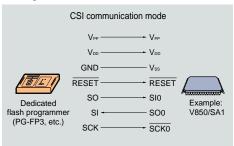

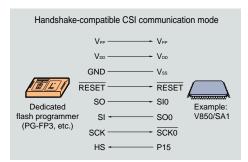

### **■**Programmer rewrite mode

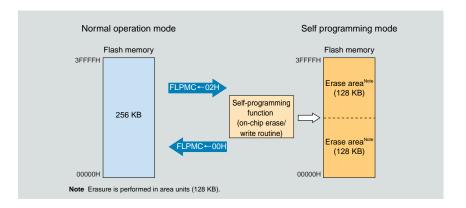

### ■Self-Programming Mode

Flash memory can be erased and rewritten by calling a self-programming function (device-internal processing) using a self-programming interface, from a program placed in an area other than the flash memory. The self-programming function is called by switching from the normal operation mode to the self-programming mode using the flash programming mode control register (FLPMC).

# **Specifications**

| Part No.           | Flash Memory | Power Supply                    | Max. Operating | Package                  | Rewrite         | Voltage         | Rewrite Mode                    | W/E Count       |

|--------------------|--------------|---------------------------------|----------------|--------------------------|-----------------|-----------------|---------------------------------|-----------------|

|                    | Capacity     | Voltage                         | Frequency      |                          | V <sub>DD</sub> | V <sub>PP</sub> |                                 |                 |

| V850E/MA1          | 256 KB       | 3.0 to 3.6 V                    | 50 MHz         | 144-pin LQFP (20 × 20mm) | 3.3 V           | 7.8 V           | CSI, HS-compatible<br>CSI       | 100             |

|                    |              |                                 |                | 161-pin FBGA (13 × 13mm) |                 |                 |                                 |                 |

| V850E/IA1          | 256 KB       | 3.0 to 3.6 V<br>(Internal unit) | 50 MHz         | 144-pin LQFP (20 × 20mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    |              | 4.5 to 5.5 V<br>(External pin)  |                |                          |                 |                 |                                 |                 |

| V850E/MS1          | 128 KB       | 3.0 to 3.6 V                    | 33 MHz         | 144-pin LQFP (20 × 20mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    |              |                                 |                | 157-pin FBGA (14 × 14mm) | -               |                 |                                 |                 |

|                    | 128 KB       | 3.0 to 3.6 V<br>(Internal unit) |                | 144-pin LQFP (20 × 20mm) |                 |                 |                                 |                 |

|                    |              | 4.5 to 5.5 V<br>(External pin)  |                |                          |                 |                 |                                 |                 |

| V853               | 128 KB       | 4.5 to 5.5 V                    | 33 MHz         | 100-pin LQFP (14 × 14mm) | 5 V             | 10.3 V          | CSI, UART,<br>HS-compatible CSI | 20              |

|                    | 256 KB       |                                 |                | 100-pin LQFP (14 × 14mm) | -               |                 |                                 |                 |

| V850/SA1           | 128 KB       | 3.0 to 3.6 V                    | 20 MHz         | 100-pin LQFP (14 × 14mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    | 256 KB       |                                 |                | 100-pin LQFP (14 × 14mm) |                 |                 |                                 |                 |

|                    |              |                                 |                | 121-pin FBGA (12 × 12mm) | -               |                 |                                 |                 |

| V850/SV1           | 256 KB       | 3.1 to 3.6 V                    | 20 MHz         | 176-pin LQFP (24 × 24mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    |              |                                 |                | 180-pin FBGA (13 × 13mm) |                 |                 |                                 |                 |

|                    | 384 KB       |                                 |                | 180-pin FBGA (13 × 13mm) |                 |                 |                                 |                 |

| V850/SB1           | 256 KB       | 4.0 to 5.5 V                    | 20 MHz         | 100-pin LQFP (14 × 14mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    |              |                                 |                | 100-pin QFP (14 × 20mm)  |                 |                 |                                 |                 |

|                    | 512 KB       |                                 |                | 100-pin QFP (14 × 20mm)  |                 |                 |                                 |                 |

| V850/SB2           | 256 KB       | 4.0 to 5.5 V                    | 13 MHz         | 100-pin LQFP (14 × 14mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    |              |                                 |                | 100-pin QFP (14 × 20mm)  |                 |                 |                                 |                 |

|                    | 512 KB       |                                 |                | 100-pin QFP (14 × 20mm)  |                 |                 |                                 |                 |

| V850/SF1           | 256 KB       | 4.0 to 5.5 V                    | 16 MHz         | 100-pin LQFP (14 × 14mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

|                    |              |                                 |                | 100-pin QFP (14 × 20mm)  |                 |                 |                                 |                 |

| V850/SC1, SC2, SC3 | 512 KB       | 4.0 to 5.5 V                    | 20 MHz         | 144-pin LQFP (20 × 20mm) | 3.3 V           | 7.8 V           | CSI, UART,<br>HS-compatible CSI | 100             |

| V850ES/SA2*        | 256 KB       | 2.3 to 2.7 V                    | 17 MHz         | 100-pin LQFP (14 × 14mm) | 2.5 V           | 2.5 V           | CSI, UART                       | 100             |

| V850ES/SA3*        | 256 KB       | 2.3 to 2.7 V                    | 17 MHz         | 121-pin FBGA (12 × 12mm) | 2.5 V           | 2.5 V           | CSI, UART                       | 100             |

|                    |              | 1                               | 1              | L                        | 1               |                 | * · I Inc                       | ler Development |

# **Flash Memory Programmers**

### ■NEC flash memory programmer (PG-FP3)

### [Features]

- ◆ Supports write to all NEC microcontrollers with dual-power supply flash memory

- Device-specific information required for writing can be automatically set with parameter files.

- Supports both on-board writing and program adapter writing.

- ◆ Easy-to-carry A5 size

- Simple operation either on standalone basis or with a dedicated application (Flashpro III) on Windows™ 95, 98, 2000, or Windows NT™ Ver. 4.0

<Standalone>

Executed in one of the following modes: PROMLOAD, ERASE, PROGRAM, VERIFY, E.P.V.

<On Windows>

Operated via GUI screen.

### ■Third-party flash memory programmers (1/2)

### ●Programming system Y1000-8

[Manufacturer/Marketing] Wave Technology Co., Ltd.

[Target Devices] V850E/MA1, V850/SV1

### [Features]

- Gang programmer enabling simultaneous programming and verification of up to 8 devices

- ◆ Enables reading of master data directly from floppy disk to internal memory.

- Data dump display and editing functions

- Master data storable on internal hard disk

- Emphasizes simple and comfortable operation via touch panel and workability via PASS/FAIL display, check-sum display, and task count display supporting sockets

### [Additional information]

TEL: +81-3-5304-1885

FAX: +81-3-5304-1886

E-mail: sales@y1000.com

Website: http://www.y1000.com/en/index.html

### ●Flashpro III FL-PR3

[Manufacturer/Marketing] Naito Densei Machida Mfg. Co., Ltd.

[Target Devices] V850 Series

### [Features]

- Supports writing to all NEC microcontrollers with dual-power supply flash memory

- Device-specific information required for writing can be automatically set with parameter files.

- Supports both on-board writing and program adapter writing.

- ◆ Easy-to-carry A5 size

- ◆ Simple operation either on standalone basis or with a dedicated application (Flashpro III) on Windows 95, 98, 2000, or Windows NT Ver. 4.0

### [Additional Information]

FAX: +81-45-475-4091

E-mail: info@ndk-m.co.jp

Website: http://www.ndk-m.co.jp/eng/index.html

### ■Third-party flash memory programmers (2/2)

### **•NET IMPRESS**

[Manufacturer/Marketing] Yokogawa Digital Computer Corporation

[Target Devices] V850E/IA1, V850/SB1 (μPD70F3033A)

### [Features]

This in-circuit programmer for flash memory microcontrollers (NET IMPRESS) is used to program the microcontrollers with on-chip flash memory of each company, which have various writing specifications, while solder mounted on the user system board.

This programmer comes in four models (AF220, AF210, AF120, AF110) to be used according to the intended application field.

- One control module is the key to this product's versatility. Microcontrollers of the same family are supported by changing parameters, and microcontrollers of different families are supported by purchasing the license for the descriptor part.

- ◆ Can be used on standalone basis as well as via a host machine.

- ◆ Rich lineup of freeware

### [Additional Information]

TEL : Japan +81-42-333-6224 U.S.A +408-244-1932 Europe +44-1256-811998 FAX : Japan +81-42-352-6109 U.S.A +408-244-1881 Europe +44-1256-811761 E-mail : info@advice.ydc.co.jp

Website: http://www.ydc.co.jp/micom/index\_E.htm

# **Flash Memory Programmers**

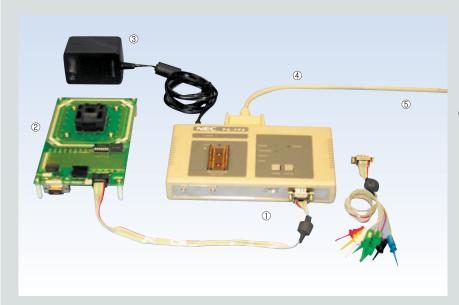

NEC's flash memory programmer (PG-FP3) supports all NEC microcontrollers with dual-power-supply on-chip flash memory. The PG-FP3 stores the device-specific information required for rewriting in a parameter file and the rewriting environment for each microcontroller can be automatically set by downloading this file. After the parameter file is downloaded, the PG-FP3 can be used on a standalone basis. Combined with a program adapter (FA series (manufactured by Naito Densei Machida Mfg. Co., Ltd.)), this programmer can be used to write single microcontrollers. On-board writing is also possible using a target cable.

An example of the rewriting environment when using the program adapter is described below.

### •Example of rewriting environment

- ① Flash memory programmer (PG-FP3)

- 2 Target system

- 3 Power supply unit

- ④ Host machine interface (RS-232-C)

- ⑤ To host machine

Cautions 1. Install the control software of the PG-FP3 and the parameter file of the target device in the host machine.

- PG-FP3 control software: Provided with PG-FP3

- · Parameter files: Distributed via online delivery

- 2. In addition to using the program adapter, rewriting can also be done on-board on the target system.

# **Functional Outline**

|                      |                      |                                                                             |                                                                         | V850E/MA1                                            |                      |                          | V850E/MA2                                                                                 |

|----------------------|----------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|----------------------|--------------------------|-------------------------------------------------------------------------------------------|

|                      | tom                  |                                                                             |                                                                         |                                                      |                      |                          |                                                                                           |

| II.                  | tem                  | μPD703103A                                                                  | μPD703105A                                                              | μPD703106A                                           | μPD703107A           | μPD70F3107A              | μPD703108                                                                                 |

| CPU core             |                      | V850E1                                                                      |                                                                         |                                                      |                      |                          | V850E1                                                                                    |

| CPU performance (    | [Dhrystone]          | _                                                                           | 62MIPS (@ 50 MHz)                                                       |                                                      |                      |                          | _                                                                                         |

| Internal ROM         |                      | None                                                                        | 128 KB<br>(Mask ROM)                                                    |                                                      | 256 KB<br>(mask ROM) | 256 KB<br>(flash memory) | None                                                                                      |

| Internal RAM         |                      | 4 KB                                                                        |                                                                         |                                                      | 10 KB                | 1                        | 4 KB                                                                                      |

| External             | Address bus          | 26 bits                                                                     |                                                                         |                                                      |                      |                          | 25 bits                                                                                   |

| bus interface        | Data bus             | 16 bits                                                                     |                                                                         |                                                      |                      |                          | 16 bits                                                                                   |

|                      | Programmable waits   | 0 to 7                                                                      |                                                                         |                                                      |                      |                          | 0 to 7                                                                                    |

| Interrupt sources    |                      | External: 25 (17) <sup>Note</sup><br>Internal: 33                           |                                                                         |                                                      |                      |                          | External: 8 (4) <sup>Note</sup><br>Internal: 23                                           |

| DSP function         | 32×32→64             | 0.02 to 0.04μs (@ 50 MH                                                     | lz)                                                                     |                                                      |                      |                          | 0.025 to 0.05μs<br>(@ 40 MHz)                                                             |

|                      | 32×32+32→32          | 0.06μs (@ 50 MHz)                                                           |                                                                         |                                                      |                      |                          | 0.075μs (@ 40 MHz)                                                                        |

|                      | 16×16 →32            | _                                                                           |                                                                         |                                                      |                      |                          | _                                                                                         |

|                      | 16×16+32→32          | _                                                                           | _                                                                       |                                                      |                      |                          |                                                                                           |

| Timer/counter (RPL   |                      | 16-bit timer/event counter<br>16-bit interval timer × 4 cl                  | 16-bit timer/event<br>counter × 2 ch<br>16-bit interval<br>timer × 4 ch |                                                      |                      |                          |                                                                                           |

| Serial interface     | CSI                  | 1 ch                                                                        |                                                                         |                                                      |                      |                          | _                                                                                         |

| (SIO)                | CSI/I <sup>2</sup> C | _                                                                           |                                                                         |                                                      |                      |                          | _                                                                                         |

|                      | CSI/UART             | 2 ch                                                                        |                                                                         |                                                      |                      |                          | 2 ch                                                                                      |

|                      | UART                 | 1 ch                                                                        |                                                                         |                                                      |                      |                          | _                                                                                         |

|                      | Dedicated BRG        | 3 ch                                                                        |                                                                         |                                                      |                      |                          | 2 ch                                                                                      |

| A/D converter        |                      | 8 ch (10-bit resolution)                                                    |                                                                         |                                                      |                      |                          | 4 ch (10-bit resolution                                                                   |

| DMA controller       |                      | 4 ch                                                                        |                                                                         |                                                      |                      |                          | 4 ch                                                                                      |

| Real-time output po  | ort                  | _                                                                           |                                                                         |                                                      |                      |                          | _                                                                                         |

| Ports                | I/O                  | 106                                                                         |                                                                         |                                                      |                      |                          | 74                                                                                        |

|                      | Input                | 9                                                                           |                                                                         |                                                      |                      |                          | 5                                                                                         |

| Other peripheral I/C | ) functions          | Memory access control fr<br>(SDRAM, SRAM, EDO D<br>PWM: 2 ch (8/9/10/12-bit | RAM, page ROM, etc., dire                                               | ectly connectable)                                   |                      |                          | Memory access control<br>function (SDRAM,<br>SRAM, page ROM, etc<br>directly connectable) |