# Integrated V.22 bis/V.42 bis Data/Fax/Voice Modem Device Set with Telephone Answering Machine (TAM) Support

## INTRODUCTION

The merging of the personal computer and telephone is the first step in the evolution of the PC to a full-fledged communications tool. Rockwell modems provide this all-important link between the PC and the desktop or portable phone. Using the RCV229ATF/2-BA modem, the OEM can cost-effectively develop products that, in addition to data and facsimile modem capabilities, support a variety of voice applications such as voice annotation, voice mail, and telephone answering machine (TAM).

The integrated Rockwell RCV229ATF/2-BA data/fax/voice modem device set consists of a modem data pump (MDP) and a microcontroller unit (MCU). Optimized for low-cost desk-top designs, the RCV229ATF/2-BA with OEM-supplied 32k-byte EPROM, provides maximum integration and functionality through a low power, small footprint, minimum supporting component design.

As a data modem, the RCV229ATF/2-BA transmits and receives at communication speeds up to 2400 bps.

As a fax modem, the RCV229ATF/2-BA transceives at Group 3 communication speeds up to 9600 bps, controlled by a built-in EIA-578 Class 1 command interface.

As a voice modem, the RCV229ATF/2-BA uses linear pulse code modulation (PCM) and samples audio data at 11025 or 7200 Hz for record and playback. When DTMF detection is on, the modem will record and playback at 7200 Hz. When DTMF detection is off, the modem will record and playback voice at 11025 Hz. OEM-provided audio control and status register logic supports record and playback functions.

A dedicated DMA channel passes audio data between the host bus and the modem. Latches in the OEM-supplied DMA control logic support DMA data transfer using terminal count signaling, DMA requests, and DMA acknowledgements.

An enhanced "AT" command set, is implemented along with AT+F fax, AT# voice, and caller ID commands.

The modem operates over a dial-up or leased telephone line, provides auto-dial and auto-answer capabilities, and can operate in asynchronous modes.

Full error correction (V.42 LAPM, MNP2-4) and data compression (V.42 bis, MNP 5) capabilities are supported through the Rockwell Protocol Interface (RPI™) and host communication software supporting the RPI. A list of communication software supporting the RPI can be obtained from your local Rockwell sales representative.

The 16C450-compatible interface allows direct connection to a notebook, laptop, or PC-compatible bus without an external UART.

## **FEATURES**

- Data modes

- CCITT V.22 bis (2400 bps), V.22 (1200 bps),

V.23 (1200 HDX), V.21 (300 bps)

- Bell 212A (1200 bps) and 103 (300 bps)

- Group 3 fax modes

- V.29 (9600/7200 bps) transmit and receive

- V.27 ter (4800/2400 bps) transmit and receive

- V.21 Channel 2 (300 bps) transmit and receive

- Voice

- DMA channel for audio data record and playback

- Linear PCM sampling at 11025 or 7200 Hz

- DTMF detection concurrent with record/playback

- Supports Business Audio applications, e.g., digital answering machine (TAM), voice mail, voice annotation, audio file (xxx.WAV) play and record, and text-to-speech

- · Caller ID support

- Enhanced "AT" command set

- Fax Class 1 commands (EIA/TIA 578)

- Error correction (V.42 LAPM, MNP 2-4) and data compression (V.42 bis, MNP 5) supported through RPI™ and host software without additional hardware

- High-speed HDLC commands support Binary File Transfer (BFT) and Error Correction Mode (ECM) facsimile

- · Programmable speaker volume control

- Automatic adaptive/ fixed compromise equalization

- Auto retrain

- Parallel host/DTE interface

- 16450 UART-compatible interface

- Support for DMA transfer of audio data

- Support for audio control and status registers

- Direct connect telco/transformer built-in hybrid

- Full-duplex data mode test capabilities: Analog loop, local digital loop, and remote digital loop

- Half-duplex fax mode test capabilities

- Power-on self test

- User modification of transmit levels

- Single voltage operation: +5 VDC ± 5%

- Low power CMOS

- Operating: 245 mW

- Sleep: 25 mW

- Package options:

- MCU: 68-pin plastic leaded chip carrier (PLCC) or 80-pin plastic quad flat pack (PQFP)

- MDP: 68-pin PLCC or 100-pin PQFP

MNP is a trademark of Microcom, Inc. RPI is a trademark of Rockwell International.

## Data/Fax/Voice Modem

## **TECHNICAL OVERVIEW**

#### **GENERAL DESCRIPTION**

The RCV229ATF/2-BA modem is a full-featured. self-contained data/fax solution. Dialing, call progress, and telephone line interface functions are fully supported and controlled through the AT command set and the Audio Control Register.

Data modes perform complete handshake and data rate negotiations. All tone and pattern detection required by the applicable CCITT or Bell standard are supported.

Fax modes support Group 3 fax requirements. Fax data and fax control (V.21 Channel 2, 300 bps) performed by the modem is controlled and monitored through the fax EIA-578 Class 1 command interface. Full HDLC formatting, flag insertion/deletion, and CRC generation/checking is provided.

#### Modem Data Pump (MDP)

The MDP is a Rockwell single device RC223DP data/fax modem data pump. The MDP includes both digital signal processor and integrated analog functions.

Digital Signal Processor (DSP). The DSP performs the digital signal processing and line control functions.

integrated Analog (IA). The IA includes transmitter, receiver, and telephone line interface sections. The transmitter provides transmitter digital-to-analog (D/A) conversion, bandsplit and lowpass filtering, guard tone generation, and transmit level attenuation. The receiver provides automatic gain control (AGC), bandsplit filtering, and analog-to-digital (A/D) conversion. The telephone interface circuitry provides off-hook and caller ID relay drivers.

## Microcontroller (MCU)

The MCU is a Rockwell C19 microcomputer. The MCU connects to the host/DTE via a 16450 UART-compatible parallel microcomputer bus. Interface signals are provided to connect to external DMA control logic and DMA control and status registers which also connect to the parallel microcomputer bus. The MCU connects to the modem data pump via dedicated lines and an external bus.

#### **MCU Firmware**

The RCV229ATF/2 MCU firmware performs processing of general modem control; AT, AT+F, and AT#V command: audio control and status register; and DTE interface functions. The MCU firmware is provided by Rockwell in object code form for the OEM to program into an external 32k x 8 EPROM.

#### SUPPORTED INTERFACES

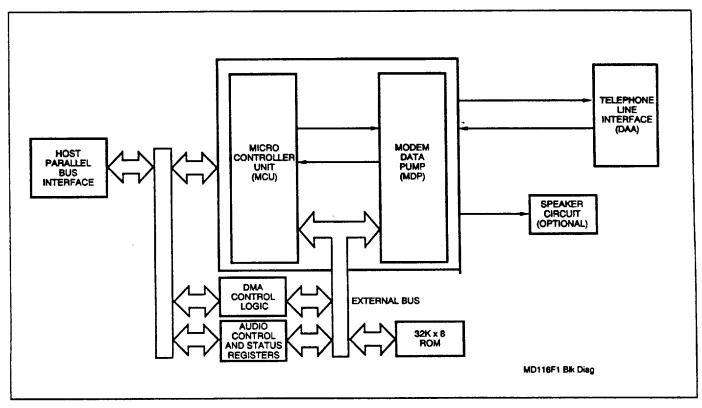

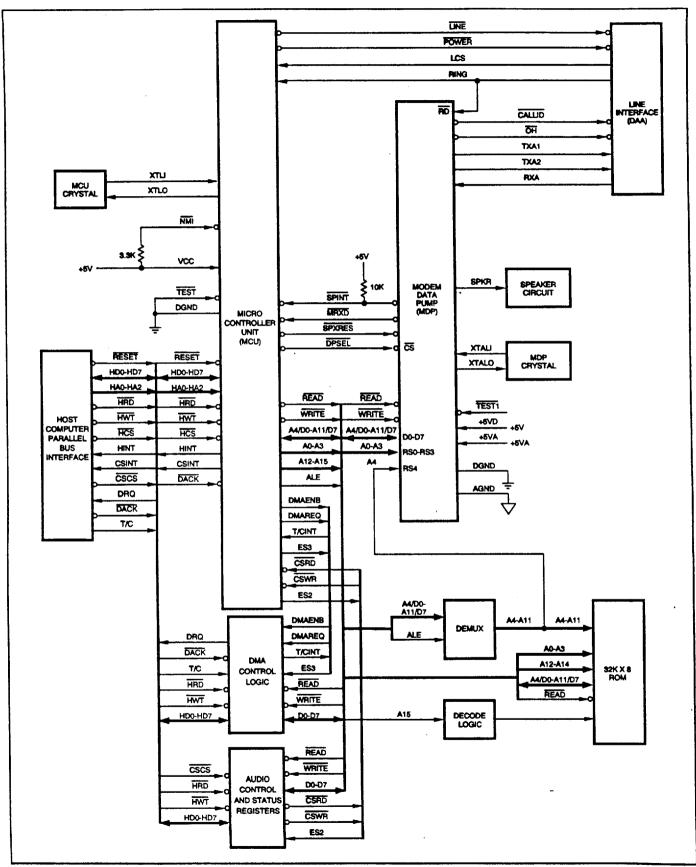

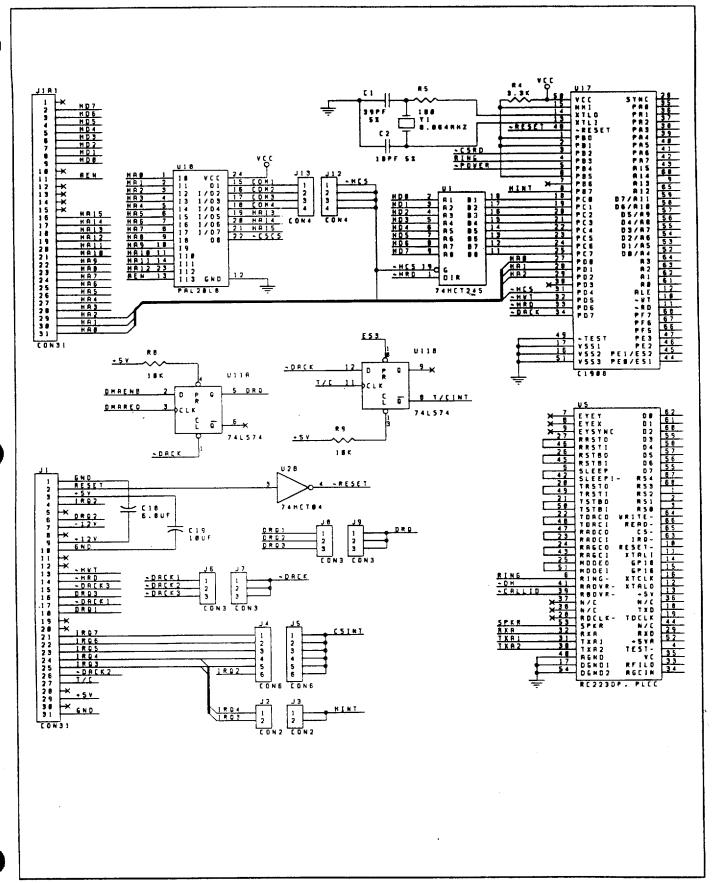

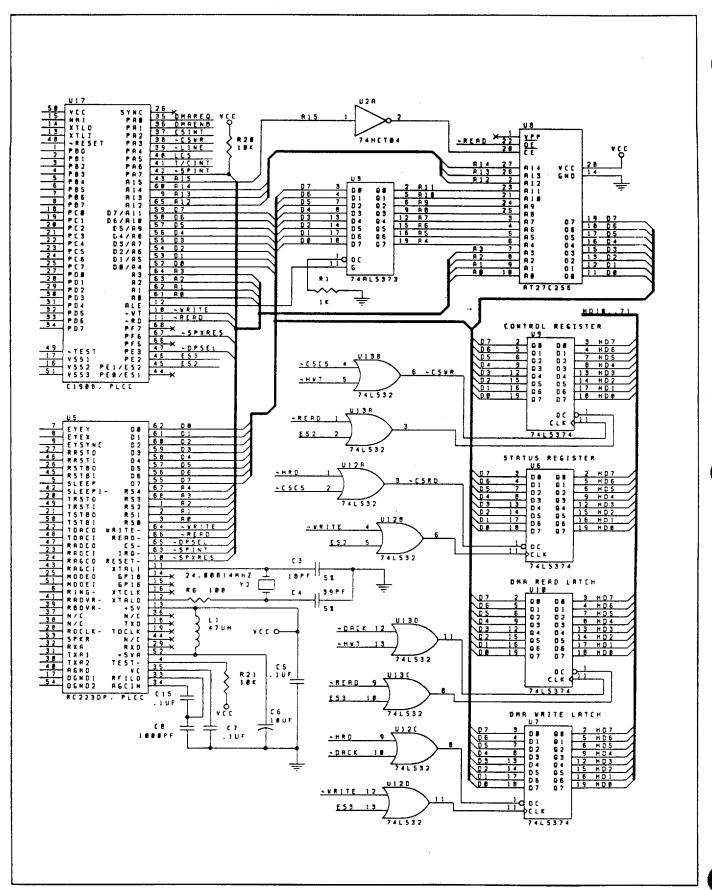

The major hardware signal interfaces of the RCV229ATF/2 modem device set are illustrated in Figure 1.

#### Parallel DTE/Host Interface

Eight bidirectional data lines (HD0-HD7), three address input lines (HA0-HA2, three control inputs (HCS, HRD, and HWT), a host interrupt output (HINT), and a reset input (RESET) are supported. A 16C450 UART-compatible parallel interface is provided.

## **DMA Control Logic Interface**

Two 8-bit data latches are supported to transfer audio data via direct memory access (DMA) between the host bus and memory connected to the modem external bus. The DMA Read Latch transfers audio playback data from the host bus and the DMA Write Latch transfers audio record data to the host bus. Two D-flip-flops are also supported: one to control the DMA request to the host bus and one to generate an interrupt request to the MCU when the terminal count of the DMA transfer is complete.

Four dedicated signals are supported: a DMA latch chip select output (ES3) to enable latch operation, DMA enable and DMA request outputs, and a terminal count interrrupt input.

## Audio Control and Status (C/S) Registers Interface

Two 8-bit audio control and status registers are supported. The Audio Control Register (ACR) is written by the host to enable record, playback, speaker, and handset functions. select 11.025 kHz or 7.2 kHz sampling rate, and four levels of speaker volume. The Audio Status Register (ASR) is written by the modem to report DTMF enable/disable. busy/idle, sample overrun, and terminal count conditions.

Three dedicated signals are supported: an audio C/S chip select (ES2) output to enable register operation and C/S read and C/S write status inputs to determine host read and write status.

#### MCU External Bus Interface

The MCU external bus connects to the MDP, ROM, RAM, the DMA latches, and the audio C/S registers The bus supports eight dedicated address line outputs (A0-A3 and A12-A15), eight multiplex bidirectional data lines and address line outputs (A4/D0-A11/D7), and three control outputs (ALE, READ, and WRITE).

#### Line Interface

MDP. The MDP connects to the line interface circuitry via a receive analog input (RXA), two transmit analog outputs (TXA1 and TXA2), two relay driver outputs (CALLID and OH), and a ring (RING) input. The CALLID and OH relay outputs may be used to drive Caller ID and voice relays, respectively.

Figure 1. RCV229ATF/2-BA Modem Functional Interface

MCU. The MCU provides two relay control outputs (LINE and POWER) to the line interface. When a line connection does not exist, the LINE output can be used to control a relay which disconnects the line from the hanset and the POWER output can be used to control a relay which connects power to the handset. The MCU also accepts ring (RING) and loop current sense (LCS) signals from the line interface.

## Speaker Interface

An interface to an OEM-supplied speaker circuit is provided. The speaker can be used to monitor call progress. The AT Ln command can be used to adjust the volume.

## **CONFIGURATIONS AND LINE RATES**

The supported modern configurations and telephone line rates are listed in Table 1.

#### **HOST/DTE RATES**

## **Data Modem Modes**

## **Automatic Speed/Format Sensing**

The modem can automatically determine the speed and format of the data coming into the modem from the DTE. The modem senses speeds of 300, 1200, 2400, 4800, 9600, and 19200 bps and the following data format:

| Parity | Data Length<br>( No. of Bits) | No. of<br>Stop Bits | Character Length (No. of Bits) |

|--------|-------------------------------|---------------------|--------------------------------|

| None   | 8                             | 1                   | 10                             |

#### Fax Mode

In fax modes, the DTE rate is 19200 bps.

## AT COMMANDS

The modem supports data modem, fax class 1 and voice commands and S Registers (see Tables 2 and 3) depending on the modem model.

**Data Modem Operation.** Data modem functions operate in response to AT commands when +FCLASS=0.

Fax Modem Operation. Facsimile functions operate in response to fax class 1 commands when +FCLASS=1.

**Voice Operation.** Voice mode functions operate in response to voice commands when #CLS = 8.

Table 1. Telephone Line Connection Speed Options

| Configuration  | Data Rate (bps) |

|----------------|-----------------|

| Data Mode      |                 |

| V.22 bis       | 2400 or 1200    |

| V.22           | 1200            |

| V.21           | 0-300           |

| Bell 212A      | 1200            |

| Bell 103       | 300             |

| Fax Mode       |                 |

| V.29           | 9600 or 7200    |

| V.27 ter       | 4800 or 2400    |

| V.21 Channel 2 | 300             |

#### **AT Command Format**

AT commands are interpreted via the parallel host interface. Each command line must start with the AT prefix and be terminated with a carriage return (CR). Several commands may be included on one command line. A command line may contain up to 40 characters excluding the AT prefix and the terminating CR. A separator is not required between data commands. A semicolon (;) separator is required between fax commands.

#### **DATA MODEM OPERATION**

#### Dialing

**DTMF Dialing.** DTMF (dual tone multi-frequency) dialing using DTMF tone pairs is supported in accordance with CCITT Q.23. The transmit tone level complies with Bell Publication 47001.

**Pulse Dialing.** Pulse dialing is supported in accordance with EIA/TIA-496-A.

Blind Dialing. Blind dialing allows the modem to dial in the absence of a dial tone. The calling unit waits the number of seconds specified in the S6 register (minimum 2 seconds) after going off-hook before reading the dial string initiating the dialing sequence. Blind dialing can be enabled by issuing the ATX0, ATX1, or ATX3 command.

## **Modem Handshaking Protocol**

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

#### **Call Progress Tone Detection**

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard.

#### **Answer Tone Detection**

Answer tone detection can be detected over the frequency range of 2100  $\pm$  40 Hz in CCITT modes and 2225  $\pm$  40 Hz in Bell modes.

#### **Ring Detection**

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

## **Billing Protection**

When an incoming call is answered, both transmission and reception of data are prevented for at least 2 seconds after the modern transfers to the off-hook state to allow transmission of the telephone company's billing signal.

Table 2. "AT" Command Set Summary

| Basic        |                                                                                              |

|--------------|----------------------------------------------------------------------------------------------|

| AT           | Attention Code.                                                                              |

| A            | Go off-hook and attempt to answer a call.                                                    |

| À            | Re-execute command.                                                                          |

| B0           | Select V.22 2100 Hz answer tone.                                                             |

| B1           | Select Bell 212A 2225 Hz answer tone.                                                        |

| B3<br>C1     | Select V.23 modulation. Return OK message.                                                   |

| Dn           | Dial Modifier.                                                                               |

| E0           | Turn off command echo.                                                                       |

| E1           | Turn on command echo.                                                                        |

| F1           | On-line character echo disabled.                                                             |

| H0<br>  H1   | Initiate a hang-up sequence. If on-hook, go off-hook and enter command mode.                 |

| l 10'        | Identify product via product code.                                                           |

| iii          | ROM checksum request.                                                                        |

| 12           | ROM checksum status request.                                                                 |

| 13           | ROM part number and revision level request.                                                  |

| 14<br>  15   | OEM string request. PROM revision level request.                                             |

| LO           | Set low speaker volume.                                                                      |

| L1           | Set low speaker volume.                                                                      |

| 12           | Set medium speaker volume.                                                                   |

| L3           | Set high speaker volume.                                                                     |

| M0<br>M1     | Turn speaker off.  Turn speaker on during handshaking, and turn                              |

| <b>''</b> '' | speaker off while receiving carrier.                                                         |

| M2           | Turn speaker on during handshaking and                                                       |

| 1            | while receiving carrier.                                                                     |

| M3           | Turn speaker off during dialing and receiving carrier, and turn speaker on during answering. |

| 00           | Go on-line.                                                                                  |

| 01           | Go on-line and initiate a V.22 bis retrain sequence.                                         |

| P            | Force pulse dialing.                                                                         |

| Q0           | Allow result codes to DTE.                                                                   |

| Q1<br>Sn     | Inhibit result codes to DTE.<br>Select S Register as default.                                |

| Sn?          | Return the value of S Register n.                                                            |

| T            | Force DTMF dialing.                                                                          |

| V0           | Report short form (terse) result codes.                                                      |

| V1<br>X0     | Report long form (verbose) result codes.  CONNECT result codes are enabled, CONNECT          |

| Λ0           | XXXX result codes are disabled, and busy signal                                              |

|              | and dial tone are not detected.                                                              |

| X1           | The modern blind dials, CONNECT XXXX result                                                  |

|              | codes are enabled, and busy signal and dial tone                                             |

| X2           | are not detected.  The modern waits for dial tone before dialing,                            |

| ~            | CONNECT XXXX result codes are enabled, and                                                   |

| 1            | busy signal is not detected.                                                                 |

| ХЗ           | The modern blind dials, CONNECT XXXX result                                                  |

|              | codes are enabled, and the modern sends the                                                  |

| X4           | BUSYresult code if busy signal is detected. The modern waits for dial tone before dialing,   |

| ^7           | CONNECT XXXX result codes are enabled, and the                                               |

| 1            | modern sends the BUSY result code if busy signal                                             |

| 1            | is detected.                                                                                 |

| Y0           | Disable long space disconnect before on-hook.  Enable long space disconnect before on-hook.  |

| Y1<br>Z0     | Restore stored profile 0 after warm reset.                                                   |

| Z1           | Restore stored profile 1 after warm reset.                                                   |

| +++          | Escape code sequence.                                                                        |

| ?            | Returns last addressed S Register.                                                           |

|              | <del> </del>                                                                                 |

Table 2. "AT" Command Set Summary (Cont'd)

| Command          | i Function                                         |

|------------------|----------------------------------------------------|

| +Hn              | Rockwell Protocol Interface (RPI) Enable.          |

| Dial<br>Modifier | Function                                           |

| P                | Select pulse dialing.                              |

|                  | Dial Stored Telephone Number (n=0:1)*.             |

|                  | Touch Tone Dial.                                   |

|                  | Wait for Dial Tone.                                |

| •                | Return to Idle State.                              |

| _                | Wait for silence.                                  |

| •                | Flash.                                             |

|                  | Pause.                                             |

| 0-9              | DTMF digits 0 to 9.                                |

| A-D              | DTMF digits A, B, C, and D.                        |

| #                | The 'gate digit' (tone dialing only).              |

| *                | The 'star' digit (tone dialing only).              |

| &<br>Comman      | d Function                                         |

|                  | Force RLSD active regardless of carrier state.     |

|                  | Allow RLSD to follow the carrier state.            |

| &DO              | The modern ignores DTR.                            |

| &DI              | Asynchronous escape.                               |

| &D2              | The modern hangs-up and autoanswer is disabled.    |

| &D3              | The modern performs soft reset.                    |

| &F               | Load factory defaults.                             |

| &G0              | No guard tone selected.                            |

| &G1              | No guard tone selected.                            |

| &G2              | 1800 Hz guard tone selected.                       |

| &LO              | Select dial-up operation.                          |

| &MO              | Asynchronous Communications Mode selected.         |

| &Pn              | Make to Break Ratio Selection.                     |

| &Q0              | Select direct asynchronous mode.                   |

| &S0              | DSR is always active.                              |

| &S1              | DSR is limited active.                             |

| &TO              | Terminate any test in progress.                    |

| &T1              | Initiate local analog loopback.                    |

| &T3              | Initiate local digital loopback.                   |

| &T4              | Allow remote digital loopback.                     |

| &T5              | Disallow remote digital loopback request.          |

| &T6              | Request remote digital loopback without self-test. |

| &T7              | Request remote digital loopback with self-test.    |

| &T8              | Initiate local analog loop with self-test.         |

| &V               | Display current configurations.                    |

| &X0              | Select internal timing for the transmit clock.     |

| %                |                                                    |

| Comman           | d Function                                         |

| %Dn              | DTMF level attenuation                             |

| %Ln              | Transmit level attenuation                         |

| %J               | Load secondary defaults                            |

Table 2. AT Command Set Summary (Cont'd)

| #                                                                            |              |                                           |

|------------------------------------------------------------------------------|--------------|-------------------------------------------|

| Comman                                                                       |              | Function                                  |

| #CLS                                                                         | Select data  | , fax, or voice.                          |

| 1                                                                            | 0            | Data modem                                |

| ļ                                                                            | 1            | Fax modem                                 |

| I                                                                            | 8            | Voice                                     |

| #VTD=i                                                                       |              | detection/report enable (i = hex value    |

| l                                                                            |              | g functions enabled/disabled for voice).  |

| ŀ                                                                            | Bit 0        | DTMF tone                                 |

| ł                                                                            | Bit 1        | V.25 1300 Hz tone                         |

|                                                                              | Bit 2        | T.30 1100 Hz tone                         |

|                                                                              | Bit 3        | V.25/T.30 21:00 Hz tone                   |

|                                                                              | Bit 4        | Bell 2225 answer tone                     |

|                                                                              | Bit 5        | Call progress tone and cadence            |

|                                                                              | Bit 6-7      | Reserved                                  |

| Voice me                                                                     | odem respor  |                                           |

|                                                                              | 0-9, A-D, #, |                                           |

|                                                                              | b            | Busy tone detected                        |

|                                                                              | C            | Calling tone detection                    |

|                                                                              | d            | Dialtone detected                         |

|                                                                              | e            | European data modem calling               |

|                                                                              |              | tone detected                             |

|                                                                              | h            | Handset hang up detected                  |

|                                                                              | S            | Silence detected                          |

|                                                                              | t            | Handset out of cradle detected            |

|                                                                              | ×            | ептог                                     |

| #CID                                                                         |              | er ID detection and select report format. |

|                                                                              | Ō            | Disable caller ID (default)               |

|                                                                              | 4            | Enable formatted caller ID                |

| Fax Cor                                                                      | nmand        | Function                                  |

| +FCLAS                                                                       | S=n          | Select Service Class                      |

| +F <com< td=""><td>mand&gt;?</td><td>Report Active Configuration</td></com<> | mand>?       | Report Active Configuration               |

|                                                                              | mand>=?      | Report Operating Capabilities             |

| +FAA=n                                                                       |              | Data/Fax Auto Answer                      |

| +FF                                                                          |              | Enhanced Flow Control                     |

| +FTS=n                                                                       |              | Stop Transmission and Wait                |

| +FRS=n                                                                       |              | Receive Silence                           |

| +FTM=n                                                                       |              |                                           |

| +FRM=n Receive Data                                                          |              |                                           |

| +FTH=n                                                                       |              | Transmit Data with HDLC Framing           |

| +FRH=n                                                                       |              | Receive Data with HDLC Framing            |

| + <u>FRT</u> n                                                               |              | Receive Test Data                         |

| +FTTn=r                                                                      | n            | Transmit Test Data                        |

| <del></del>                                                                  |              |                                           |

Table 3. S Register Summary

| Register    | Function                           |

|-------------|------------------------------------|

| SO          | Rings to Answer On                 |

| S1          | Ring Counter                       |

| S2          | Escape Character                   |

| S3          | Carriage Return Character          |

| S4          | Line Feed Character                |

| S5          | Backspace Character                |

| S6          | Wait Time for Dial Tone            |

| S7          | Wait Time for Carrier              |

| S8          | Pause Time for Dial Delay Modifier |

| S9          | Carrier Detect Response Time       |

| S10         | Carrier Loss Disconnect Time       |

| S11         | DTMF Dialing Speed                 |

| S12         | Escape Code Guard Time             |

| S14         | Bit Mapped Options Register        |

| S16         | Test Mode Bit Mapped Options       |

| S17         | Fax Mode Null Byte Timer           |

| S18         | Test Timer                         |

| S19         | Bit Mapped Options Register        |

| S20         | Fax Mode Inactivity Timer          |

| S21         | Bit Mapped Options Register        |

| S22         | Bit Mapped Options Register        |

| S23         | Bit Mapped Options Register        |

| S24         | Sleep Mode Inactivity Timer        |

| <b>S</b> 25 | Delay to DTR Off                   |

| S26         | RTS to CTS Delay                   |

| S27         | Bit Mapped Options Register        |

| S28         | Bit Mapped Options Register        |

| S29         | Flash Duration                     |

## Connection Speeds

The possible modem to modem connection data modes/speeds are Beil 103 300 bps. Bell 212A 1200 bps. V.21 300 bps, V.22 1200 bps, and V.22 bis 2400 bps. Data rate selection is determined by the speed of the originating and answering modems per the appropriate AT command as follows:

#### AT Command: B0

| <b>A.</b> 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. | Connect Speed Based on  |      |      |  |

|--------------------------------------------------|-------------------------|------|------|--|

| Originate Modem                                  | Answer Modem Rate (bps) |      |      |  |

| Rate (bps)                                       | 300                     | 1200 | 2400 |  |

| 300                                              | 300                     | 300  | 300  |  |

| 1200                                             | 300                     | 1200 | 1200 |  |

| 2400                                             | 300                     | 1200 | 2400 |  |

#### AT Command: B1

|                 | Conne                   | ct Speed Ba | sed on |  |

|-----------------|-------------------------|-------------|--------|--|

| Originate Modem | Answer Modem Rate (bps) |             |        |  |

| Rate (bps)      | 300                     | 1200        | 2400   |  |

| 300             | 300                     | 300         | 300    |  |

| 1200            | 1200                    | 1200        | 1200   |  |

| 2400            | 1200                    | 1200        | 2400   |  |

#### **Transmit Tones**

Answer Tone: An answer tone of 2100 Hz (V.22 bis, V.22, or T.30) or 2225 Hz (Bell 212A or 103) is generated.

Guard Tone: An 1800 Hz guard tone can be generated in all PSK data modes.

Calling Tone: A 1100 Hz (0.5 seconds on, 3 seconds off) calling tone (T.30) is generated in the originate fax mode.

## **Modem Handshaking Protocol**

An abort call timer is initiated when the last digit is dialed and is reset when the modern detects either answer tone or busy. If a tone is not detected during the time specified in the S7 register (default is 30 seconds), the modem aborts the call attempt.

#### Receive Level

The receiver satisfies performance requirements for a received signal from -9 dBm to -43 dBm. The carrier detect is ON at -43 dBm and OFF at -48 dBm with a minimum of 2 dB hysterisis.

#### Receiver Tracking

The modem can accommodate carrier frequency offset up to ±7 Hz, and a transmit timing error of ± 0.01% (V.22 bis or V.27 ter) or ± 0.02% (V.22 or Bell 212A).

#### Equalization

Automatic adaptive equalization and fixed compromise equalization compensate for line distortions and minimize the effects of intersymbol interference.

#### Scrambler/Descrambler

The modem incorporates a self-synchronizing scrambler/descrambler satisfying the applicable CCITT or Bell requirements.

#### Transmit Level

The transmit level is adjustable (see S91 in Table 4).

#### **DATA MODE**

Data mode exists when a telephone line connection has been established between moderns and all handshaking has been completed.

## **Escape Sequence Detection**

The S2 register holds the decimal value of the ASCII code used for the escape character. The default character is a '+'. Detection of the escape sequence can be disabled by setting the S2 register to a value greater than 127. When the escape sequence is executed, the escape characters are also transmitted to the telco line in all modes.

#### **BREAK Detection**

The modern can detect a BREAK signal from either the DTE or the remote modem. The \Kn command determines the modern response to a received BREAK signal.

## Telephone Line Monitoring

Loss of Carrier. If carrier is not detected for time specified in the S10 register, the modern disconnects from the line.

Receive Space Disconnect. If selected by the ATY1 command, the modern disconnects after receiving 1.6 seconds ± 10% of continuous SPACE.

Send Space on Disconnect. If selected by the ATY1 command, the modem sends 4 seconds ± 10% of continuous SPACE If DTR goes OFF or if ATH is issued.

## Retrain

The modem may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modern continues to retrain until an acceptable connection is achieved or until 30 seconds elapse which will result in telephone line disconnect.

#### **FAX MODE**

#### **Fax Commands**

In the fax mode, the on-line behavior of the modem is different compared to the data (non-fax) mode. After dialing, the modem behaves as controlled by the fax commands. Some AT commands are still valid but may operate differently than in the data mode.

#### Fax Mode

The possible modem to modem connection fax modes are V.21 Channel 2, V.29, and V.27 ter depending on the selected configuration.

Fax modes are negotiated as defined in T.30 and are implemented by AT+F commands. The AT+FCLASS=1 command causes entry into the fax mode from the data mode. Most other fax class 1 commands, which start with the AT+F prefix, are valid only in the fax mode. All data commands are valid in the fax mode except A/, On, &Tn, and the escape sequence (+++). The AT+FCLASS=0 command terminates the fax mode and causes entry into the data mode.

Fax Mode Buffers. Each terminal and modem buffer contains 100 bytes. For the modem buffer, the high water mark is reached when the buffer is 80% full (80 characters) and the low water mark is reached when the buffer is 20% full (20 characters).

## Data/Fax Auto Answering

The modem can automatically determine if the incoming call is from a data or fax modem, make the appropriate connection, and inform the DTE of the connection type.

#### **LOW POWER SLEEP MODE**

To conserve power, the modem has a sleep (power down) mode. If enabled by the IDLEN0 and IDLEN1 inputs, sleep mode is entered whenever the modem is inactive. The sleep mode indicator output, SLEEP, is provided to allow external circuits to be powered down when the modem is in sleep mode.

#### DIAGNOSTICS

Modem diagnostics comply with EIA TR30.2. Diagnostics are performed in response to AT &T commands.

**Analog Loopback.** Data from the local DTE is sent to the modem, which loops the data back to the local DTE.

Analog Loop Self Test. An internally generated test pattern of alternating 1s and 0s (reversals) is sent to the modern. An error detector within the modern checks for errors in the string of reversals.

Remote Digital Loopback (RDL). Data from the local DTE is sent to the remote modem which loops the data back to the local DTE.

Remote Digital Loopback with Self Test. An internally generated pattern is sent from the local to the remote modern which loops the data back to the local modern.

**Digital Loopback.** When digital loop is requested from the local DTE, two data paths are set up in the local modem. Data from the local DTE is looped back to the local DTE (path 1) and data received from the remote modem is looped back to the remote modem (path 2).

#### **POWER ON RESET DIAGNOSTICS**

Upon power on, or receipt of the ATZ command, the modem performs diagnostic testing.

#### HARDWARE INTERFACE SIGNALS

The modem hardware interface signals are shown in Figure 2.

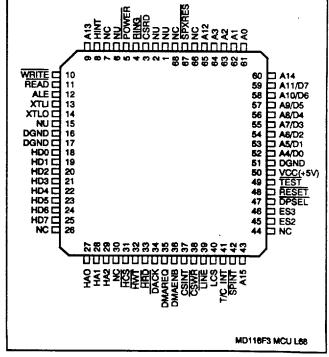

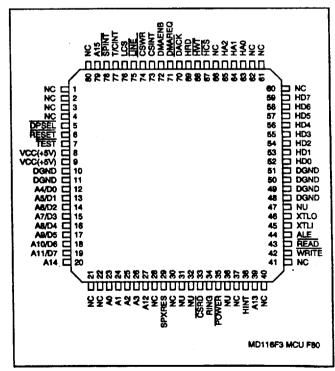

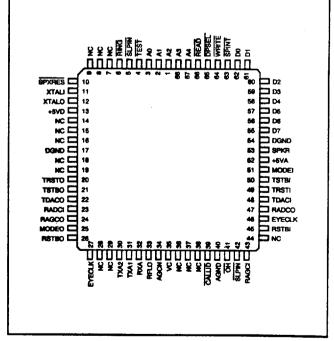

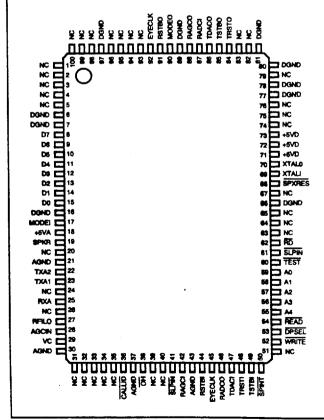

MCU pin assignments are listed in Table 5 and shown in Figure 3 for the 68-pin PLCC and are listed in Table 6 and shown in Figure 4 for the 80-pin PQFP.

MDP pin assignments are listed in Table 7 and shown in Figure 5 for the 68-pin PLCC and are listed in Table 8 and shown in Figure 6 for the 100-pin PQFP.

The MCU and MDP hardware interface signals are defined in Tables 9 and 10, respectively.

Digital and analog electrical characteristics for the hardware interface signals are listed in Tables 11 and 12, respectively.

The modem device current and power requirements are listed in Table 13.

The absolute maximum ratings are listed in Table 14.

Table 15 shows the parallel interface registers and the corresponding bit assignments.

Table 16 shows the audio control and status registers and corresponding bit assignments.

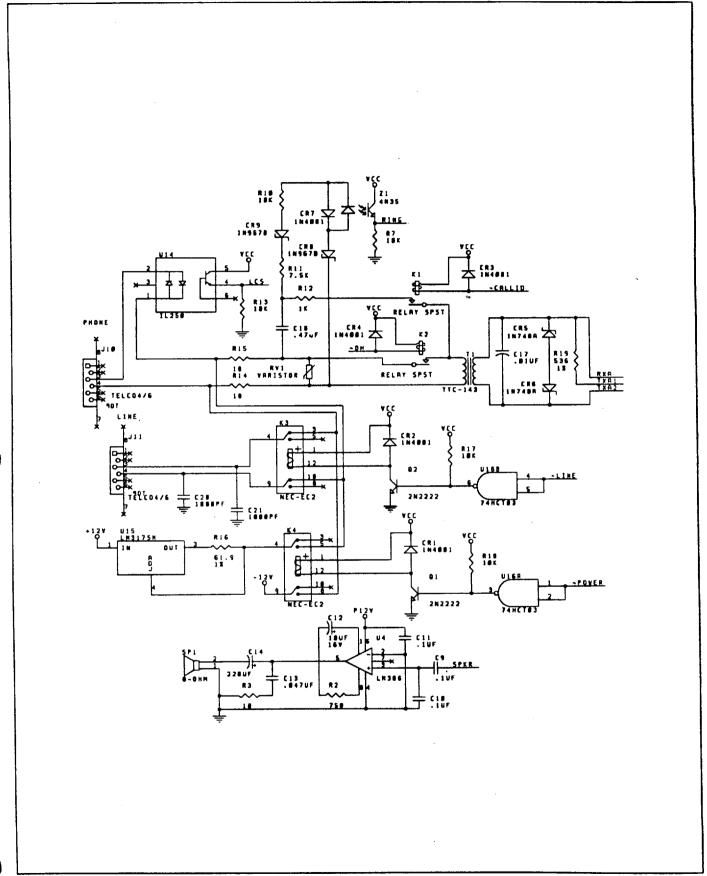

A schematic for a typical application circuit is shown in Figure 7.

#### ADDITIONAL INFORMATION

The RCV229ATF/2-BA Designer's Guide (Order No. 1026) provides detailed interface information. The RC229ATF AT Command Reference Manual (Order No. 1027) provides detailed AT command and S register information.

Figure 2. RCV229ATF/2-BA Interface Signals

Table 5. MCU Signals - 68-Pin PLCC

| Pin No.                                               | MCU Signal          | VO Type        | RCV229ATF/2 Signal        |

|-------------------------------------------------------|---------------------|----------------|---------------------------|

| 1                                                     | PB0                 |                | NU (Note 5)               |

| 2                                                     | PB1                 | ا 🔒 ا          | NU (Note 5)               |

| 3<br>4                                                | PB2<br>PB3          | IA<br>IA       | CSRD<br>RING              |

| 5                                                     | PB4                 | OÃ             | POWER                     |

| 6                                                     | PB5                 | •              | NU (Note 5)               |

| 7                                                     | PB6                 | 1              | NC                        |

| 8                                                     | PB7                 | OA             | HINT                      |

| 9<br>10                                               | A13<br>WT           | OA<br>OA       | A13<br>WRITE              |

| 11                                                    | RD                  | OA             | READ                      |

| 12                                                    | ALE                 | OA             | ALE                       |

| 13                                                    | XTLI                | IE             | XTU                       |

| 14                                                    | XILO                | OE             | XTLO                      |

| 15<br>16                                              | NMI<br>VSS2         | GND            | NU (Note 5) DGND          |

| 17                                                    | VSS1                | GND            | DGND                      |

| 18                                                    | PCO                 | IA/OA          | HD0                       |

| 19                                                    | PC1                 | IA/OA          | HD1                       |

| 20                                                    | PC2                 | IA/OA          | HD2                       |

| 21<br>22                                              | PC3<br>PC4          | IA/OA<br>IA/OA | HD3                       |

| 23                                                    | PC5                 | IAVOA          | HD4<br>HD5                |

| 24                                                    | PC6                 | IA/OA          | HD6                       |

| 25                                                    | PC7                 | IA/OA          | HD7                       |

| 26                                                    | SYNC                |                | NC                        |

| 27                                                    | PD0                 | I IA           | HAO                       |

| 28<br>29                                              | PD1<br>PD2          | IA<br>IA       | HA1<br>HA2                |

| 30                                                    | PD3                 | ^              | NC_                       |

| 31                                                    | PD4                 | I IA           | HČS                       |

| 32                                                    | PD5                 | IA             | HWT                       |

| 33                                                    | PD6                 | IA             | HRD                       |

| 34<br>35                                              | PD7                 | IA I           | DACK                      |

| 36                                                    | PA0<br>PA1          | OA<br>OA       | DMAREQ<br>DMAENB          |

| 37                                                    | PA2                 | I ÖÄ           | CSINT                     |

| 38                                                    | PA3                 | ΪÂ             | CSWR                      |

| 39                                                    | PA4                 | OA             | LINE                      |

| 40<br>41                                              | PA5<br>PA6          | I IA I         | LCS                       |

| 42                                                    | PA0<br>PA7          | I IA           | T/C INT<br>SPINT (Note 6) |

| 43                                                    | A15                 | ÖÄ             | A15                       |

| 44                                                    | PE0/ES1             | OA             | NC                        |

| 45                                                    | PE1/ES2             | OA             | ES2                       |

| 46                                                    | PE2/ES3             | OA             | ES3                       |

| 47                                                    | PE3/ES4             | OA             | DPSEL                     |

| 48<br>49                                              | RES<br>TEST         | IC             | RESET<br>TEST (Note 4)    |

| 50                                                    | VCC                 | PWR            | VCC(+5V)                  |

| 51                                                    | VSS3                | GND            | DGND                      |

| 52                                                    | A4/D0               | IA/OA          | A4/D0                     |

| 53                                                    | A5/D1               | IA/OA          | A5/D1                     |

| 54<br>55                                              | A6/D2<br>A7/D3      | IA/OA<br>IA/OA | A6/D2<br>A7/D3            |

| 56                                                    | A8/D4               | IAVOA          | A8/D4                     |

| 57                                                    | A9/D5               | IA/OA          | A9/D5                     |

| 58                                                    | A10/D6              | IAVOA          | A10/D6                    |

| 59                                                    | A11/D7              | IA/OA          | A11/D7                    |

| 60<br>61                                              | A14<br>PF0/A0       | OA OA          | A14                       |

| 62                                                    | PF1/A1              | I OA I         | A0<br>A1                  |

| 63                                                    | PF2/A2              | I ÖÄ           | A2                        |

| 64                                                    | PF3/A3              | QA             | A3                        |

| 65                                                    | PF4/A12             | OA             | A12                       |

| 66<br>67                                              | PF5                 |                | NC<br>CRYDEC              |

| 67<br>68                                              | PF6<br>PF7          | MI             | SPXRES<br>NC              |

| - 55                                                  |                     | <u> </u>       | 110                       |

| Notes:                                                |                     |                |                           |

| 1.                                                    | MI = Modern interco |                | diagana askad dan ant     |

| 2. NC = No connection; leave pin disconnected (open). |                     |                |                           |

- NU = Not used; connect as noted. Connect to GND. Connect to +5 VDC through 3.3 KΩ. Connect to +5 VDC through 10 KΩ.

Figure 3. MCU Signals - 68-Pin PLCC

Table 6. MCU Signals - 80-Pin PQFP

|          | MOUSI              |                |                        |

|----------|--------------------|----------------|------------------------|

| Pin No.  | MCU Signal<br>NC   | I/O Type       | RCV229ATF/2 Signal     |

| 1 2      | PE0/ES1            | OA             | NC                     |

| 3        | PE1/ES2            | OA             | ES2<br>ES3             |

| 5        | PE2/ES3<br>PE3/ES4 | OA OA          | DPSEL                  |

| 6        | RES                | IC             | RESET                  |

| 7 8      | TEST<br>VCC        | PWR            | TEST (Note 4) VCC(+5V) |

| 9        | VCC                | PWR            | VCC(+5V)               |

| 10       | VSS<br>VSS         | GND            | DGND<br>DGND           |

| 12       | A4/D0              | IAVOA          | A4/D0                  |

| 13<br>14 | A5/D1<br>A6/D2     | IA/OA<br>IA/OA | A5/D1<br>A6/D2         |

| 15       | A7/D3              | IAVOA          | A7/D3                  |

| 16       | A8/D4              | IAVOA          | A8/D4                  |

| 17       | A9/D5<br>A10/D6    | IA/OA<br>IA/OA | A9/D5<br>A10/D6        |

| 19       | A11/D7             | IA/OA          | A11/D7                 |

| 20<br>21 | A14<br>NC          | OA             | A14<br>NC              |

| 22       | NC                 |                | NC                     |

| 23<br>24 | PF0/A0<br>PF1/A1   | OA<br>OA       | A0<br>A1               |

| 25       | PF2/A2             | OA             | A2                     |

| 26       | PF3/A3             | OA<br>OA       | A3<br>A12              |

| 27<br>28 | PF4/A12<br>PF5     | J 00           | NC                     |

| 29       | PF6                | MI             | SPXRES<br>NC           |

| 30<br>31 | PF7<br>PB0         |                | NU (Note 5)            |

| 32       | PB1                | 1              | NU (Note 5)            |

| 33<br>34 | PB2<br>PB3         | IA<br>IA       | CSRD                   |

| 35       | PB4                | ÖÄ             | POWER                  |

| 36<br>37 | PB5<br>PB6         |                | NU (Note 5)<br>NC      |

| 38       | PB7                | OA             | HINT                   |

| 39<br>40 | A13<br>NC          | OA             | A13<br>NC              |

| 41       | NC<br>NC           |                | NC NC                  |

| 42       | <u> </u>           | OA             | WRITE<br>READ          |

| 43<br>44 | RD<br>ALE          | OA<br>OA       | ALE                    |

| 45       | XTLI               | IE             | XTLI                   |

| 46<br>47 | XTLO<br>NMI        | OE<br>MI       | XTLO<br>NU (Note 5)    |

| 48       | VSS                | GND            | DGND                   |

| 49<br>50 | VSS<br>VSS         | GND            | DGND<br>DGND           |

| 51       | VSS                | GND            | DGND                   |

| 52<br>53 | PC0<br>PC1         | IA/OA<br>IA/OA | HD0<br>HD1             |

| 54       | PC2                | IA/OA          | HD2                    |

| 55<br>56 | PC3<br>PC4         | IA/OA<br>IA/OA | HD3<br>HD4             |

| 57       | PC5                | IA/OA          | HD5                    |

| 58       | PC6<br>PC7         | IA/OA<br>IA/OA | HD6<br>HD7             |

| 59<br>60 | SYNC               | 1 1/2/04       | NC                     |

| 61       | NC                 | 1              | NC<br>NC               |

| 62<br>63 | NC<br>PD0          | IA.            | NC<br>HA0              |

| 64       | PD1                | IA             | HA1                    |

| 65<br>66 | PD2<br>PD3         | IA.            | HA2<br>NC              |

| 67       | PD4                | IA.            | HCS                    |

| 68<br>69 | PD5<br>PD6         | IA<br>IA       | HWT                    |

| 70       | PD7                | IA             | DACK                   |

| 71 72    | PA0<br>PA1         | OA<br>OA       | DMAREQ<br>DMAENB       |

| 73       | PA2                | OA             | CSINT                  |

| 74<br>75 | PA3<br>PA4         | IA<br>OA       | LINE                   |

|          | F/14               | 1 0            | I #114F                |

Table 6. MCU Signals - 80-Pin PQFP

| Pin No.                                                                                                                                                                                                                         | MCU Signal | I/O Type | RC229ATF/2-W Signal |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|---------------------|--|

| 76                                                                                                                                                                                                                              | PA5        | IA       | LCS                 |  |

| 77                                                                                                                                                                                                                              | PA6        | i ia     | T/C INT             |  |

| 78                                                                                                                                                                                                                              | PA7        | Mi       | SPINT (Note 6)      |  |

| 79                                                                                                                                                                                                                              | A15        | OA       | A15                 |  |

| 80                                                                                                                                                                                                                              | NC         | i        | NC                  |  |

| Notes:  1. MI = Modern interconnect.  2. NC = No connection; leave pin disconnected (open).  3. NU = Not used; connect as noted.  4. Connect to GND.  5. Connect to +5 VDC through 3.3 KΩ.  6. Connect to +5 VDC through 10 KΩ. |            |          |                     |  |

Figure 4. MCU Signals - 80-Pin PQFP

Table 7. MDP Signals - 68-Pin PLCC

| Pin No.  | Signal Name      | 124            | T DAI MAR ATEM Alamat |

|----------|------------------|----------------|-----------------------|

|          |                  | I/O Type       | RCV229ATF/2 Signal    |

| 1 2      | RS2<br>RS1       | IA<br>IA       | A2<br>A1              |

| 3 4      | RS0<br>TEST      | IA             | A0<br>TEST (Note 3)   |

| 5        | SLEEP            | OA             | SLPIN                 |

| 6 7      | RING<br>EYEY     | IA<br>OB       | RING                  |

| l é      | EYEX             | OB             | NC<br>NC              |

| 9        | EYESYNC<br>RESET | OB<br>Mi       | NC<br>SPXRES          |

| 11       | XTALI            | IE             | XTALI                 |

| 12<br>13 | XTALO<br>+5VD    | OB<br>PWR      | XTALO<br>+5VD         |

| 14       | GP18             | OA             | NC                    |

| 15<br>16 | RLSD<br>XTCLK    | OA<br>IA       | NC<br>NC              |

| 17       | DGND             | GND            | DGND                  |

| 18<br>19 | TXD<br>TDCLK     | IA<br>OA       | NC<br>NC              |

| 20       | TRSTO            | MI             | TRSTO                 |

| 21<br>22 | TSTBO<br>TDACO   | MI<br>MI       | TSTBO<br>TDACO        |

| 23       | RADCI            | Mi             | RADCI                 |

| 24<br>25 | RAGCO<br>MODEO   | MI<br>MI       | RAGCO<br>MODEO        |

| 26       | RSTBO            | MI             | RSTBO                 |

| 27<br>28 | RRSTO<br>RDCLK   | MI<br>OA       | EYECLK<br>NC          |

| 29<br>30 | RXD<br>TXA2      | OA<br>O(DD)    | NC<br>TYAO            |

| 31       | TXA1             | O(DD)<br>O(DD) | TXA2<br>TXA1          |

| 32<br>33 | RXA<br>RFILO     | I(DA)<br>MI    | RXA<br>RFILO          |

| 34       | AGCIN            | MI             | AGCIN                 |

| 35<br>36 | VC<br>NC         | OA             | VC<br>NC              |

| 37       | NC               |                | NC                    |

| 38<br>39 | NC<br>RBDVR      | QO             | NC<br>CALLID          |

| 40       | AGND             | GND            | AGND                  |

| 41<br>42 | RADVR<br>SLEEPI  | OD<br>IA       | OH<br>SLPIN           |

| 43       | RAGCI            | Mi             | RAGCI                 |

| 44<br>45 | NC<br>RSTBI      | MI             | NC<br>RSTBI           |

| 46       | RRSTI            | MI             | EYECLK                |

| 47<br>48 | RADCO<br>TDACI   | MI<br>MI       | RADCO<br>TDACI        |

| 49<br>50 | TRSTI<br>TSTBI   | MI<br>MI       | TRSTI<br>TSTBI        |

| 51       | MODE             | MI             | MODE                  |

| 52<br>53 | +5VA<br>SPKR     | PWR<br>O(OF)   | +5VA<br>SPKR          |

| 54       | DGND             | GND            | DGND                  |

| 55<br>56 | D7<br>D6         | IA/OB<br>IA/OB | D7<br>D6              |

| 57       | D5               | IA/OR          | D5                    |

| 58<br>59 | D4<br>D3         | IA/OB<br>IA/OB | D4<br>D3              |

| 60       | D2               | IA/OB          | D2                    |

| 61<br>62 | D1<br>D0         | IA/OB<br>IA/OB | D1<br>D0              |

| 63       | ĪRQ              | MI             | SPINT                 |

| 64<br>65 | WRITE<br>CS      | IA<br>IA       | WRITE<br>DPSEL        |

| 66       | READ             | IA             | READ                  |

| 67<br>68 | RS4<br>RS3       | IA<br>IA       | A4<br>A3              |

| Notos    |                  |                |                       |

Notes:

- 1. Mi = Modem Interconnection.

- NC = No connection [may have internal connection; leave pin disconnected (open)].

Figure 5. MDP Pin Signals - 68-Pin PLCC

Table 8. MDP Signals - 100-Pin PQFP

| Pin No.  | Signal Name    | I/O Type       | RCV229ATF/2 Signal     |

|----------|----------------|----------------|------------------------|

| 1 2      | NC<br>NC       |                | NC<br>NC               |

| 3        | NC<br>NC       |                | NC                     |

| 4        | NC             |                | NC                     |

| 5<br>6   | NC<br>DGND     | GND            | NC<br>DGND             |

| 7        | DGND           | GND            | DGND                   |

| 8 9      | D7<br>D6       | IA/OB<br>IA/OB | D7<br>D6               |

| 10       | D5             | INOR           | D5                     |

| 11       | D4             | IA/OB          | D4                     |

| 12<br>13 | D3<br>D2       | IA/OB<br>IA/OB | D3<br>D2               |

| 14       | D1             | IA/OB          | D1                     |

| 15<br>16 | D0<br>DGND     | IA/OB<br>GND   | D0<br>DGND             |

| 17       | MODE           | MI             | MODEI                  |

| 18       | +5VA           | PWR            | +5VA                   |

| 19<br>20 | SPKR<br>NC     | O(OF)          | SPKR<br>NC             |

| 21       | AGND           | GND            | AGND                   |

| 22       | TXA2           | O(DD)          | TXA2<br>TXA1           |

| 23<br>24 | TXA1<br>NC     | O(DD)          | NC                     |

| 25       | RXA            | I(DA)          | RXA                    |

| 26<br>27 | NC<br>RFILO    | MI             | NC<br>RFILO            |

| 28       | AGCIN          | MI             | AGCIN                  |

| 29<br>30 | VC<br>AGND     | OA<br>GND      | VC<br>AGND             |

| 31       | NC NC          | GIVE           | NC                     |

| 32       | NC NC          |                | NC<br>NC               |

| 33<br>34 | NC<br>NC       |                | NC NC                  |

| 35       | NC             |                | NC NC                  |

| 36<br>37 | RBDVR<br>AGND  | OD<br>GND      | CALLID<br>AGND         |

| 38       | RADVR          | OD             | OH                     |

| 39<br>40 | NC<br>NC       |                | NC<br>NC               |

| 41       | SLEEP          | IA.            | SLPIN                  |

| 42       | RAGCI          | M!             | RAGCI<br>AGND          |

| 43<br>44 | AGND<br>RSTBI  | GND<br>MI      | RSTBI                  |

| 45       | RRSTI          | MI             | EYECLK                 |

| 46<br>47 | RADCO<br>TDACI | MI<br>MI       | RADCO<br>TDACI         |

| 48       | TRSTI          | M              | TRSTI                  |

| 49       | TSTBI          | MI             | TSTBI                  |

| 50<br>51 | IRQ<br>NC      | oc             | SPINT<br>NC            |

| 52       | WRITE          | IA.            | WRITE                  |

| 53<br>54 | CS<br>READ     | IA<br>IA       | DPSEL<br>READ          |

| 55       | RS4            | IA             | A4                     |

| 56<br>57 | RS3<br>RS2     | I IA           | A3<br>A2               |

| 58       | RS1            | I IA           | 1 A1                   |

| 59       | RS0            | IA             | AO TEST (Nets 2)       |

| 60<br>61 | TEST<br>SLEEP  | OA             | TEST (Note 3)<br>SLPIN |

| 62       | RD             | IA             | RING                   |

| 63<br>64 | EYEX           | OB<br>OB       | NC<br>NC               |

| 65       | EYESYNC        | ОВ             | NC .                   |

| 66<br>67 | DGND<br>NC     | GND            | DGND<br>NC             |

| 68       | RESET          | MI             | SPXRES                 |

| 69       | XTALI          | IE OB          | XTALI                  |

| 70<br>71 | XTALO<br>+5VD  | OB<br>PWR      | XTALO<br>+5VD          |

| 72       | +5VD           | PWR            | +5VD                   |

Table 8. MDP Signals - 100-Pin PQFP (Cont'd)

| Pin No. | Signal Name                             | VO Type             | RCV229ATF/2 Signal |  |  |  |  |

|---------|-----------------------------------------|---------------------|--------------------|--|--|--|--|

| 73      | +5VD                                    | PWR                 | +5VD               |  |  |  |  |

| 74 .    | GP18                                    | OA                  | NC                 |  |  |  |  |

| 75      | RLSD                                    | OA                  | NC I               |  |  |  |  |

| 76      | XTCLK                                   | IA I                | NC I               |  |  |  |  |

| 77      | DGND                                    | GND                 | DGND               |  |  |  |  |

| 78      | DGND                                    | GND                 | DGND               |  |  |  |  |

| 79      | TXD                                     | IA I                | NC                 |  |  |  |  |

| 80      | DGND                                    | GND                 | DGND               |  |  |  |  |

| 81      | DGND                                    | GND                 | DGND               |  |  |  |  |

| 82      | NC                                      |                     | NC                 |  |  |  |  |

| 83      | TDCLK                                   | OA                  | NC                 |  |  |  |  |

| 84      | TRSTO                                   | Mi                  | TRSTO              |  |  |  |  |

| 85      | TSTBO                                   | MI                  | TSTBO              |  |  |  |  |

| 86      | TDACO                                   | MI                  | TDACO              |  |  |  |  |

| 87      | RADCI                                   | MI                  | RADCI              |  |  |  |  |

| 88      | RAGCO                                   | MI<br>GND           | RAGCO              |  |  |  |  |

| 89      | DGND                                    | MI                  | DGND               |  |  |  |  |

| 90      | MODEO                                   |                     | MODEO              |  |  |  |  |

|         | 91 RSTBO MI RSTBO<br>92 RRSTO MI EYECLK |                     |                    |  |  |  |  |

| 92      | RDCLK                                   | I OA                | NC                 |  |  |  |  |

| 94      | RXD                                     | OA                  | NC<br>NC           |  |  |  |  |

| 95      | NC NC                                   | 0^                  | NC<br>NC           |  |  |  |  |

| 96      | NC NC                                   | 1                   | l NC               |  |  |  |  |

| 97      | DGND                                    | GND                 | DGND               |  |  |  |  |

| 98      | NC NC                                   | 1 3,40              | NC                 |  |  |  |  |

| 99      | NC NC                                   | 1                   | NC NC              |  |  |  |  |

| 100     | NČ                                      |                     | NC                 |  |  |  |  |

| Notes:  |                                         | 1                   | 4                  |  |  |  |  |

| 1.      | Mi = Modem Inter                        |                     |                    |  |  |  |  |

| 2       | NC = No connecti                        |                     |                    |  |  |  |  |

|         | connection; leave                       |                     |                    |  |  |  |  |

| 3.      | Connect to +5V th                       | <u>irough 10K c</u> | hms.               |  |  |  |  |

Figure 6. MDP Pin Signais - 100-Pin PQFP

## Table 9. MCU Signal Definitions

| Label      | I/O Type | Signal Name/Description                                                                                                                                                                                                                                  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          | OVERHEAD                                                                                                                                                                                                                                                 |

| XTLI, XTLO | IE, OE   | MCU Crystal/Clock in and Crystal Out. Connect the MCU XTLI and XTLO pins to an external crystal circuit consisting of a 8.064 MHz crystal and a suitable capacitance network. Alternatively, connect XTLI to a buffered clock and leave XTLO open.       |

| RESET      | IC       | MCU Reset. The active low RESET input resets the MCU logic and returns the AT command set to the original factory default values and to "stored values" in NVRAM. The RESET input is typically connected to the host bus RESET line through an inverter. |

| VCC        | PWR      | + 5V Digital Supply. Connect VCC to +5V ± 5%.                                                                                                                                                                                                            |

| DGND       | GND      | Digital Ground. Connect DGND to ground.                                                                                                                                                                                                                  |

|            |          | LINE INTERFACE                                                                                                                                                                                                                                           |

| LINE       | OA       | Line Relay Driver. The active low LINE output controls a normally closed relay used to disconnect the handset from the line in local voice mode.                                                                                                         |

| POWER      | OA       | Power Relay Driver. The active low POWER output controls a normally openrelay used to connect power to the handset in local voice mode.                                                                                                                  |

| LCS        | IA.      | Loop Current Sense. LCS is an active high input to the modern that indicates whether the associated handset is off-hook (loop current is flowing) or if the line is incorrectly connected to the handset jack.                                           |

## PARALLEL HOST INTERFACE (SERIAL INTERFACE SELECTED)

The parallel interface emulates a 16C450 UART interface. The parallel interface is compatible with communications software designed to operate with a 16C450 interface on a PC. Table 15 identifies the parallel interface registers and bits.

Parallel interface operation is equivalent to 16C450 operation with CS0 and CS1 inputs high and DISTR, DOSTR, and ADS inputs low. The corresponding RCV229ATF/2 and 16C450 signals are shown below.

| 16C450 Signal | RCV229ATF/2 Signal            |

|---------------|-------------------------------|

| A0 - A2       | HA0 - HA2                     |

| D0 - D7       | HD0 - HD7                     |

| MR            | RESET (Active low)            |

| CS2           | HCS                           |

| DISTR         | <del>HWT</del>                |

| DOSTR         | HRD                           |

| INTRPT        | HINT                          |

| DDIS          | HDIS                          |

| OUT1          | None (implemented internally) |

| OUT2          | None (implemented internally) |

# Table 9. MCU Signal Definitions (Cont'd)

| Label          | I/O Type  |                                                                                                                                                                                                                                                            |           | Signal N           | ame/Desc   | eription                                                                                                                                    |  |  |  |

|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HAO-HA2        | IA        | Host Bus Address Lines 0-2. During a host read or write operation, HA0-HA2 select an internal MCU 16C450-compatible register. The state of the divisor tatch access bit (DLAB) affects the selection of certain MCU registers. The register addresses are: |           |                    |            |                                                                                                                                             |  |  |  |

|                |           | DLAB                                                                                                                                                                                                                                                       | HA2       | HA1                | HAO        | Register                                                                                                                                    |  |  |  |

|                |           | 0                                                                                                                                                                                                                                                          | 0         | 0                  | 0 .        | Receiver Buffer Register (Read), Transmitter Holding Register (Write)                                                                       |  |  |  |

|                |           | 0                                                                                                                                                                                                                                                          | 0         | 0                  | 1          | Interrupt Enable Register                                                                                                                   |  |  |  |

|                |           | X                                                                                                                                                                                                                                                          | 0         | 1                  | 0          | Interrupt Identification Register (Read Only)                                                                                               |  |  |  |

|                |           | ×                                                                                                                                                                                                                                                          | 0         | 1                  | 1          | Line Control Register                                                                                                                       |  |  |  |

|                |           | X                                                                                                                                                                                                                                                          | 1         | 0                  | 0          | Modern Control Register                                                                                                                     |  |  |  |

|                |           | X                                                                                                                                                                                                                                                          | 1         | 0                  | 1          | Line Status Register (Read Only)                                                                                                            |  |  |  |

|                |           | X                                                                                                                                                                                                                                                          | 1         | 1                  | 0          | Modern Status Register (Read Only)                                                                                                          |  |  |  |

|                |           | X                                                                                                                                                                                                                                                          | 1         | 1                  | 1          | Scratch Register                                                                                                                            |  |  |  |

|                |           | 1                                                                                                                                                                                                                                                          | 0         | 0                  | 0          | Divisor Latch Register (Least Significant Byte)                                                                                             |  |  |  |