## Description

The  $\mu$ PD42601 silicon file is an economical mass storage device specifically designed to replace magnetic disk drives in silicon disk, solid-state recording, and system backup applications in a variety of computer systems. Organized as 1,048,576 words by 1 bit, the  $\mu$ PD42601 provides a battery backup feature for enhanced system performance and a substantial savings in power consumption.

The device is capable of executing standard access or page-mode write and read cycles. Refreshing is accomplished by means of CAS before RAS refresh cycles, RAS-only refresh cycles, self-refresh cycles, or by normal read or write cycles on the 512 address combinations of A<sub>0</sub> through A<sub>8</sub> during a 32-ms period.

The  $\mu$ PD42601 is uniquely suitable for battery backup systems because it requires a very low power supply current for extended periods of self-refresh operation. If ambient temperature is limited to 50 °C (max), as little as 30  $\mu$ A (max) is required to maintain all data.

The  $\mu$ PD42601 is available in high-density 20-pin plastic ZIPor 26/20-pin plastic SOJ packaging.

### **Features**

- ☐ 1,048,576-word by 1-bit organization

- ☐ Single +5-volt ±10% power supply

- □ CMOS technology

- ☐ Low operating power: 12 mA maximum

- $\square$  30  $\mu$ A maximum self-refresh current at 0 to 50 °C

- ☐ Read or write cycle time: 1000 ns minimum

- ☐ Page-mode cycle time: 200 ns minimum

- ☐ CAS before RAS refreshing

- ☐ 512 refresh cycles during 32-ms period

- ☐ Automatic self-refreshing by RAS input cycling

### **Ordering Information**

| Part Number   | Page-Mode<br>Cycle (min) | Self-Refresh<br>Current<br>(max, 50°C) | Package               |

|---------------|--------------------------|----------------------------------------|-----------------------|

| μPD42601LA-60 | 200 ns                   | 120 µA                                 | 26/20-pin plastic SOJ |

| LA-60L        | 200 ns                   | 30 μΑ                                  |                       |

| μPD42601V-60  | 200 ns                   | 120 µA                                 | 20-pin plastic ZIP    |

| V-60L         | 200 ns                   | 30 μΑ                                  |                       |

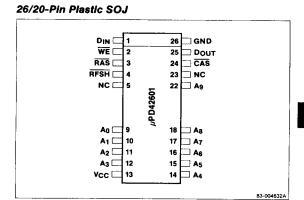

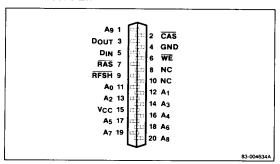

### Pin Configurations

#### 20-Pin Plastic ZIP

### Pin Identification

| Name                            | Function              |  |

|---------------------------------|-----------------------|--|

| A <sub>0</sub> - A <sub>9</sub> | Address inputs        |  |

| D <sub>IN</sub>                 | Data input            |  |

| D <sub>OUT</sub>                | Data output           |  |

| RAS                             | Row address strobe    |  |

| CAS                             | Column address strobe |  |

| WE                              | Write enable          |  |

| RFSH                            | Self-refresh control  |  |

| GND                             | Ground                |  |

| V <sub>CC</sub>                 | +5-volt power supply  |  |

| NC                              | No connection         |  |

# **Absolute Maximum Ratings**

| Voltage on any pin relative to GND, V <sub>T</sub> | -1.0 to +7.0 V |

|----------------------------------------------------|----------------|

| Operating temperature, T <sub>OPR</sub>            | 0 to +70°C     |

| Storage temperature, T <sub>STG</sub>              | -55 to +125°C  |

| Short-circuit output current, los                  | 50 mA          |

| Power dissipation, P <sub>D</sub>                  | 1.0 W          |

| Supply voltage, V <sub>CC</sub>                    | -1.0 to +7.0 V |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

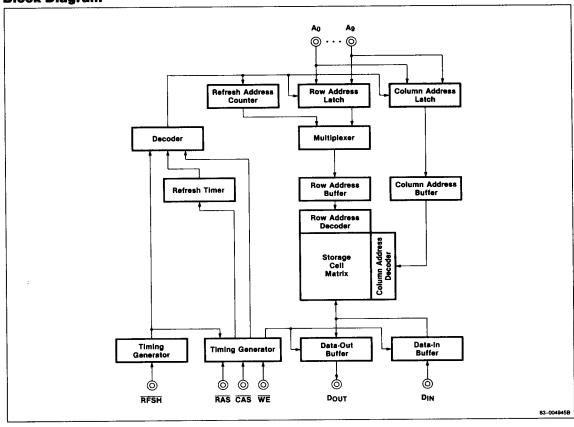

## **Block Diagram**

### Operation

### Write and Read Operation

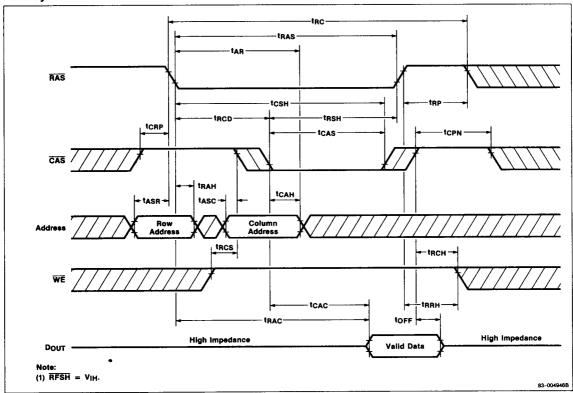

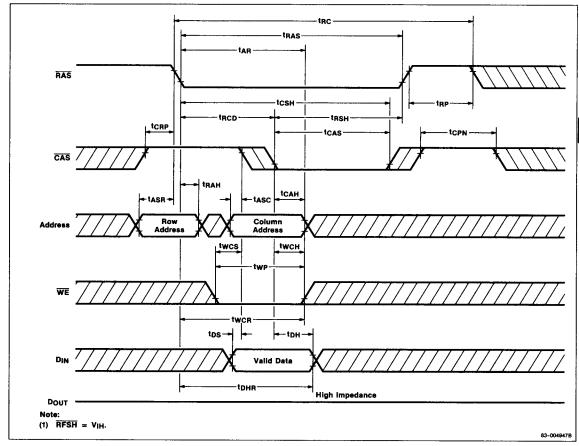

The  $\mu$ PD42601 is capable of standard write and read operation as well as page-mode operation. The ten row address bits are set up on pins  $A_0$  through  $A_9$  and latched onto the chip by RAS. Subsequently, ten column address bits are set up on pins  $A_0$  through  $A_9$  and latched onto the chip by CAS. An appropriate write or read cycle is executed according to the logical level of WE: a high WE initiates a read cycle and low WE initiates a write cycle.

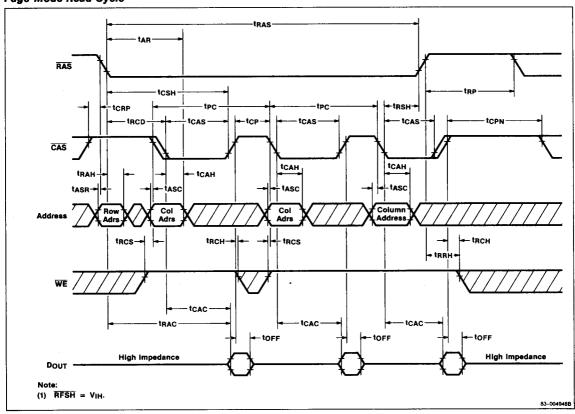

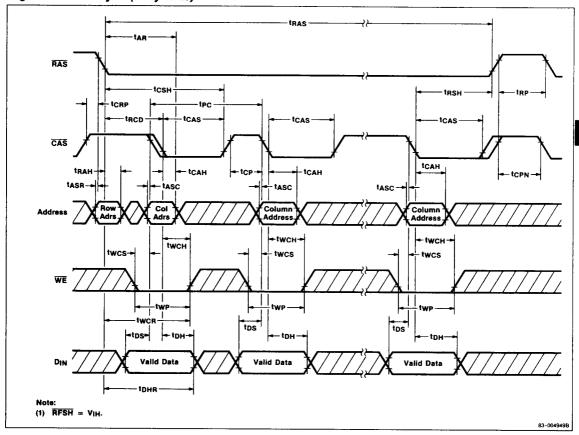

Page-mode operation may be executed by pulsing CAS repeatedly while maintaining a low RAS. The first word is accessed in the same manner as in standard write and read operation, with row addresses latched onto the chip by RAS and column addresses latched by CAS. Subsequent column addresses are accessed for each CAS cycle, repeated during a period up to the maximum RAS pulse width.

### **Refresh Operation**

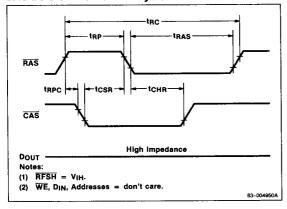

CAS before RAS Refreshing. This cycle may be initiated by bringing CAS low before RAS and holding it low after RAS falls. A built-in address counter makes external addressing unnecessary.

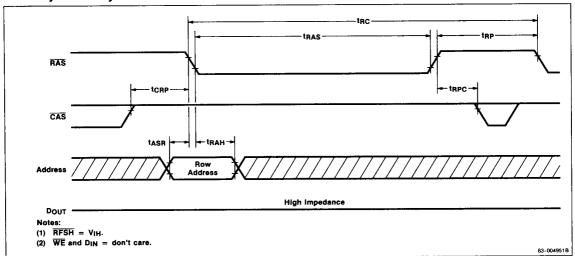

$\overline{\text{RAS-Only}}$  Refreshing.  $\overline{\text{RAS-only}}$  refreshing is executed by holding  $\overline{\text{CAS}}$  high as the row addresses are latched onto the chip by  $\overline{\text{RAS}}$ . Using this cycle, all storage cells are refreshed by the 512 address combinations of  $A_0$  through  $A_8$  during a 32-ms period.

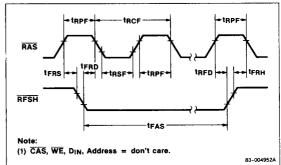

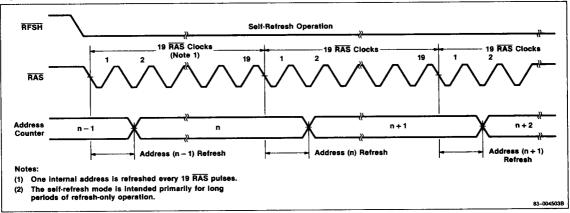

Self-Refreshing. A self-refresh cycle is initiated for the addresses generated by the internal counter whenever RFSH is active low and the RAS input is cycling (see figure 1). Since the minimum required RAS cycling frequency depends on ambient temperature, power consumption will also vary with temperature as shown in the AC and DC Characteristics. For extended periods of self-refresh operation, a low supply current is required; e.g., if ambient temperature is limited to 50°C (max), as little as 30  $\mu$ A (max) is required to maintain all data.

# **Recommended DC Operating Conditions**

$T_A = 0 \text{ to } +70 \text{ °C}; \text{ GND} = 0 \text{ V}$

| Parameter           | Symbol          | Min  | Тур | Max | Unit |

|---------------------|-----------------|------|-----|-----|------|

| Supply voltage      | V <sub>CC</sub> | 4.5  | 5.0 | 5.5 | ٧    |

| Input voltage, high | ViH             | 2.4  |     | 5.5 | ٧    |

| input voltage, low  | V <sub>IL</sub> | -1.0 |     | 0.8 | ٧    |

### Capacitance

TA = 25°C; f = 1 MHz

| Parameter          | Symbol          | Max | Unit | Pins Under Test          |

|--------------------|-----------------|-----|------|--------------------------|

| Input capacitance  | C <sub>I1</sub> | 5   | pF   | Address, D <sub>IN</sub> |

|                    | C <sub>12</sub> | 8   | pF   | RAS, CAS, WE,<br>RFSH    |

| Output capacitance | CD              | 7   | pF   | D <sub>OUT</sub>         |

### **DC Characteristics**

$\rm T_A=0$  to +70°C;  $\rm V_{CC}=+5.0~V\pm10\%$

| <u>-</u>                                                 |                  | 1   | Limit | 8   |      |                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------|------------------|-----|-------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                | Symbol           | Min | Тур   | Max | Unit | Test Conditions                                                                                                                                                                                                                                                   |

| Operating current, average                               | I <sub>CC1</sub> |     |       | 12  | mA   | $\begin{aligned} & \overline{\text{RAS}}, \overline{\text{CAS}} \text{ cycling;} \\ & I_0 = 0 \text{ mA;} \\ & t_{\text{RC}} = t_{\text{RC}} \text{ (min)} \end{aligned}$                                                                                         |

| Standby current                                          | I <sub>CC2</sub> |     |       | 2.0 | mA   | RAS = CAS = RFSH<br>= V <sub>IH</sub>                                                                                                                                                                                                                             |

|                                                          |                  |     |       | 0.5 | mA   | $\begin{array}{l} \overline{\text{RAS}} = \overline{\text{CAS}} = \overline{\text{RFSH}} \\ \geq V_{\text{CC}} - 0.4;  A_0\text{-}A_9, \\ D_{\text{IN}} \text{ and } \overline{\text{WE}} \geq V_{\text{CC}} \\ - 0.4 \text{ or } \leq 0.4 \text{ V} \end{array}$ |

| Operating current, RAS-only refresh, average             | I <sub>CC3</sub> |     |       | 10  | mΑ   | $t_{RC} = t_{RC} \text{ (min)};$ $t_0 = 0 \text{ mA}$                                                                                                                                                                                                             |

| Operating current,<br>CAS before RAS<br>refresh, average | I <sub>CC4</sub> |     |       | 10  | mA   | $t_{RC} = t_{RC} \text{ (min)};$ $t_0 = 0 \text{ mA}$                                                                                                                                                                                                             |

| Operating current, self-refresh mode,                    | I <sub>CC5</sub> |     |       | 30  | μΑ   | RAS cycling at 50 kHz (Notes 1, 2, 3, 4)                                                                                                                                                                                                                          |

| average                                                  |                  |     |       | 60  | μΑ   | RAS cycling at 100 kHz (Notes 1, 2, 3, 4)                                                                                                                                                                                                                         |

|                                                          |                  |     |       | 120 | μΑ   | RAS cycling at 200 kHz (Notes 1, 2, 3)                                                                                                                                                                                                                            |

| Operating current, page mode, average                    | I <sub>CC6</sub> |     |       | 12  | mA   | $t_{PC} = t_{PC} \text{ (min)};$ $t_0 = 0 \text{ mA}$                                                                                                                                                                                                             |

| Input leakage<br>current                                 | lιL              | -1  |       | 1   | μΑ   | $V_{IN} = 0$ to $V_{CC}$ ; all other pins not under test = 0 V                                                                                                                                                                                                    |

| Output leakage current                                   | I <sub>OL</sub>  | -1  |       | 1   | μΑ   | D <sub>OUT</sub> disabled;<br>V <sub>OUT</sub> = 0 to V <sub>CC</sub>                                                                                                                                                                                             |

| Output voltage,<br>low                                   | V <sub>OL</sub>  |     |       | 0.4 | ٧    | I <sub>0</sub> = 4.2 mA                                                                                                                                                                                                                                           |

| Output voltage,<br>high                                  | V <sub>OH</sub>  | 2.4 |       |     | ٧    | $I_0 = -5 \text{ mA}$                                                                                                                                                                                                                                             |

| Notes:                                                   |                  |     |       |     |      |                                                                                                                                                                                                                                                                   |

(1) When  $t_{FAS} \le 2.5$  ms,  $t_{CC5}$  does not depend on the  $\overline{RAS}$  clock;  $t_{CC5}$  (max) =  $500\,\mu\text{A}$ . When  $t_{FAS} \ge 2.5$  ms,  $t_{CC5}$  (max) =  $500\,\mu\text{A}$  in the first 2.5 ms after  $\overline{RFSH}$  falls (it does not depend on the  $\overline{RAS}$  clock). Subsequently,  $t_{CC5}$  is  $120\,\mu\text{A}$  for the  $\mu\text{PD42601}$ -L.

| Operating<br>Temperature [T <sub>A</sub> ] | Clock<br>Frequency [min] | Self-Refresh<br>Current [max] |

|--------------------------------------------|--------------------------|-------------------------------|

| 0 to 50°C                                  | 50 kHz                   | 30 μA at 50 kHz               |

| 0 to 60°C                                  | 100 kHz                  | 60 μA at 100 kHz              |

| 0 to 70 °C                                 | 200 kHz                  | 120 μA at 200 kHz             |

(2) t<sub>RCF</sub> depends on operating temperature as reflected in the table below (see figures 2 and 3).

| Operating                     | t <sub>RCF</sub> [max] |          |  |  |  |

|-------------------------------|------------------------|----------|--|--|--|

| Temperature [T <sub>A</sub> ] | μ <b>PD42601-L</b>     | μPD42601 |  |  |  |

| 0 to 50°C                     | 20 μs                  | 5 μs     |  |  |  |

| 0 to 60°C                     | 10 <i>μ</i> s          | 5 μs     |  |  |  |

| 0 to 70°C                     | 5 μs                   | 5 μs     |  |  |  |

- (3) Average power supply current required for self refreshing is measured according to the following conditions:  $\overline{AAS}$  is cycling at 50, 100 or 200 kHz;  $V_{IL} \ge V_{CC} = 0.4$  V;  $V_{IL} \le 0.4$  V;  $V_{IL} \le 0.5$  ns;  $A_0$  to  $A_9$ ,  $D_{IN}$ ,  $\overline{WE}$  and  $\overline{CAS} = V_{CC}$  to GND; RFSH =  $V_{IL}$ . When  $\overline{AFS}$  input must be cycled at or exceeding the minimum frequency requirements.

- (4) This specification applies to the  $\mu$ PD42601-L only. For the non-L version, I<sub>CC5</sub> is 120  $\mu$ A, maximum, at all T<sub>A</sub>.

### **AC Characteristics**

$T_A = 0 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%$

|                                     |                  | Limits |        |      |                 |

|-------------------------------------|------------------|--------|--------|------|-----------------|

| Parameter                           | Symbol           | Min    | Max    | Unit | Test Conditions |

| Random read or write cycle time     | t <sub>RC</sub>  | 1000   |        | ns   | (Note 5)        |

| Page-mode cycle time                | t <sub>PC</sub>  | 200    |        | ns   | (Notes 5, 15)   |

| Access time from RAS                | t <sub>RAC</sub> |        | 600    | ns   | (Notes 6, 7)    |

| Access time from CAS (falling edge) | tCAC             |        | 100    | ns   | (Notes 6, 8)    |

| Output buffer turnoff delay         | t <sub>OFF</sub> | 0      | 100    | ns   | (Note 9)        |

| Transition time (rise and fall)     | tΤ               | 3      | 50     | ns   | (Notes 3, 4)    |

| RAS precharge time                  | t <sub>RP</sub>  | 390    |        | ns   |                 |

| RAS pulse width                     | t <sub>RAS</sub> | 600    | 100000 | ns   |                 |

| RAS hold time                       | tRSH             | 100    |        | ns   |                 |

| CAS pulse width                     | t <sub>CAS</sub> | 100    | 10000  | ns   |                 |

| CAS hold time                       | tcsH             | 600    |        | ns   |                 |

| RAS to CAS delay time               | tRCD             | 150    | 500    | ns   | (Note 10)       |

| CAS to RAS precharge time           | t <sub>CRP</sub> | 30     |        | ns   | (Note 11)       |

| CAS precharge time (non-page cycle) | t <sub>CPN</sub> | 90     |        | ns   |                 |

| CAS precharge time (page cycle)     | t <sub>CP</sub>  | 90     |        | ns   | (Note 15)       |

| RAS precharge CAS<br>hold time      | tRPC             | 0      |        | ns   |                 |

## **AC Characteristics (cont)**

$T_A = 0 \text{ to } +70 \text{°C}; V_{CC} = +5.0 \text{ V} \pm 10\%$

|                                                       |                  | Lin  | iits |      |                                             |

|-------------------------------------------------------|------------------|------|------|------|---------------------------------------------|

| Parameter                                             | Symbol           | Min  | Max  | Unit | Test Conditions                             |

| Row address setup<br>time                             | tasr             | 0    |      | ns   |                                             |

| Row address hold time                                 | t <sub>RAH</sub> | 90   |      | ns   |                                             |

| Column address setup<br>time                          | tASC             | 0    |      | ns   |                                             |

| Column address hold<br>time                           | tCAH             | 90   |      | ns   |                                             |

| Column address ho <u>ld</u><br>time referenced to RAS | t <sub>AR</sub>  | 590  |      | ns   |                                             |

| Read command setup<br>time                            | t <sub>RCS</sub> | 0    |      | ns   |                                             |

| Read command hold<br>time referenced to RAS           | t <sub>RRH</sub> | 75   |      | ns   | (Note 12)                                   |

| Read command hold time referenced to CAS              | t <sub>RCH</sub> | 0    |      | ns   | (Note 12)                                   |

| Write command hold time                               | twch             | 90   |      | ns   |                                             |

| Write command hold time referenced to RAS             | twcr             | 590  |      | ns   |                                             |

| Write command pulse width                             | t <sub>WP</sub>  | 90   |      | ns   |                                             |

| Data-in setup time                                    | t <sub>DS</sub>  | 0    |      | ns   | (Note 14)                                   |

| Data-in hold time                                     | t <sub>DH</sub>  | 90   |      | ns   | (Note 14)                                   |

| Data-in hold time<br>referenced to RAS                | t <sub>DHR</sub> | 590  |      | ns   |                                             |

| Write command setup<br>time                           | twcs             | 0    |      | ns   |                                             |

| CAS setup time for<br>CAS before RAS refresh          | tcsr             | 30   |      | ns   |                                             |

| CAS hold time for CAS<br>before RAS refresh           | t <sub>CHR</sub> | 105  |      | ns   |                                             |

| Refresh period                                        | t <sub>REF</sub> |      | 32   | ms   | Addresses<br>A <sub>0</sub> -A <sub>8</sub> |

| Self-Refresh Cycle                                    | •                |      |      |      |                                             |

| RFSH pulse width                                      | t <sub>FAS</sub> | 810  |      | ns   | (Note 13)                                   |

| RAS to RFSH delay<br>time                             | t <sub>RFD</sub> | 100  |      | ns   |                                             |

| RAS setup time<br>to RFSH                             | t <sub>FRS</sub> | 200  |      | ns   |                                             |

| RAS cycle time in self-<br>refresh mode               | tace             | 1000 |      | ns   | (Note 16)                                   |

| RAS precharge time in self-refresh mode               | t <sub>RPF</sub> | 390  |      | ns   |                                             |

|                                        |                  | Lir | Limits |      |                 |

|----------------------------------------|------------------|-----|--------|------|-----------------|

| Parameter                              | Symbol           | Min | Max    | Unit | Test Conditions |

| Self-Refresh Cyc                       | le (cont)        | )   |        |      |                 |

| RAS pulse width in self-refresh mode   | t <sub>RSF</sub> | 600 |        | ns   |                 |

| RFSH to RAS delay<br>time              | t <sub>FRD</sub> | 100 |        | ns   |                 |

| RAS hold time in self-<br>refresh mode | t <sub>FRH</sub> | 200 |        | ns   |                 |

#### Notes:

- (1) All voltages are referenced to GND.

- (2) An initial pause of 100 µs is required after power-up (V<sub>CC</sub> = +5.0 V ±10%), followed by any eight RAS cycles, before proper device operation is achieved. RAS, CAS, and RFSH must equal V<sub>IH</sub> during the initial pause.

- (3) Ac measurements assume  $t_T = 5$  ns.

- (4) V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- (5) The minimum specifications are used only to indicate the cycle time at which proper operation over the full temperature range (T<sub>A</sub> = 0 to +70 °C) is assured.

- (6) Load = 2 TTL loads and 100 pF ( $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ ).

- (7) Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max). If t<sub>RCD</sub> is greater than the maximum recommended value in this table, t<sub>RAC</sub> increases by the amount that t<sub>RCD</sub> exceeds the value shown.

- (8) Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- (9) t<sub>OFF</sub> (max) defines the time at which the output achieves the open-circuit condition and is not referenced to V<sub>OH</sub> or V<sub>OL</sub>.

- (10) Operation within the t<sub>RCD</sub> (max) limit assures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than t<sub>RCD</sub> (max), access time is controlled exclusively by t<sub>CAC</sub>.

- (11) The t<sub>CRP</sub> requirement should be applicable for RAS/CAS cycles preceded by any cycle.

- (12) Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

- (13) When  $t_{FAS} \le 2.5$  ms,  $t_{CC5}$  does not depend on the  $\overline{RAS}$  clock;  $t_{CC5}$  (max) =  $500~\mu A$ . When  $t_{FAS} \ge 2.5$  ms,  $t_{CC5}$  (max) =  $500~\mu A$  for the first 2.5 ms after  $\overline{RFSH}$  falls (it does not depend on the  $\overline{RAS}$  clock). Subsequently,  $t_{CC5}$  is  $120~\mu A$  for the  $\mu PD42601$  or is as shown in the following table for the  $\mu PD42601$ -L.

| Operating<br>Temperature [T <sub>A</sub> ] | Clock<br>Frequency [min] | Self-Refresh<br>Current [max] |

|--------------------------------------------|--------------------------|-------------------------------|

| 0 to 50°C                                  | 50 kHz                   | 30 μA at 50 kHz               |

| 0 to 60°C                                  | 100 kHz                  | 60 μA at 100 kHz              |

| 0 to 70°C                                  | 200 kHz                  | 120 μA at 200 kHz             |

#### Notes [cont]:

- (14) These parameters are referenced to the falling edge of CAS for early write cycles.

- (15) This parameter is applicable to page-mode operation.

- (16) t<sub>RCF</sub> depends on operating temperature as reflected in the table below (see figures 2 and 3).

| Operating<br>Temperature [T <sub>A</sub> ] | t <sub>RCF</sub> [max] |                  |

|--------------------------------------------|------------------------|------------------|

|                                            | μPD42601-L             | μ <b>PD42601</b> |

| 0 to 50°C                                  | 20 <i>μ</i> s          | 5 μs             |

| 0 to 60°C                                  | 10 μs                  | 5 <b>μs</b>      |

| 0 to 70°C                                  | 5 <i>μ</i> s           | 5 μs             |

Figure 1. Internal Address Generation in Self-Refresh Operation

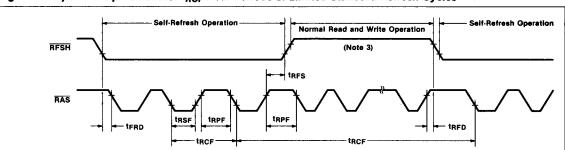

Figure 2. Special Requirement for t<sub>RCF</sub> Near Periods of Limited Standard Refresh Cycles

#### Notes:

[1] The value for tRCF [min] is specified in AC Characteristics. The value for tRCF [max] is dependent upon temperature and shown in the table below.

|      | tRCF [max] |          |  |

|------|------------|----------|--|

| TA   | μPD42601-L | μPD42601 |  |

| 50°C | 20 μs      | 5 μs     |  |

| 60°C | 10 μs      | 5 μs     |  |

| 70°C | 5 µs       | 5 μs     |  |

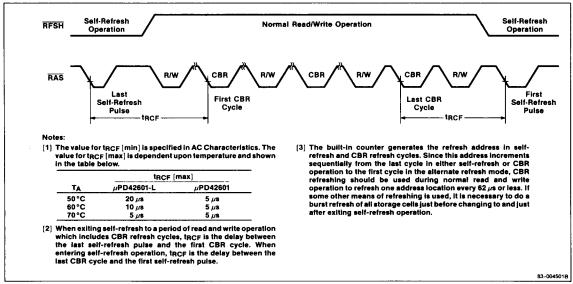

- [2] When exiting self-refresh to a period of read and write operation which includes CBR refresh cycles, tgcF is the delay between the last self-refresh pulse and the first CBR cycle. When entering self-refresh operation, tgcF is the delay between the last CBR cycle and the first self-refresh pulse.

- [3] In this period of normal read/write operation, there are no CBR refresh cycles or less than 512 RAS-only refresh cycles.

- [4] The time delay between the last self-refresh pulse in one self-refresh cycle, and the first self-refresh pulse in the next cycle, is defined by tRCF [max] when the intervening period of read and write operation meets the conditions in Note 3.

- [5] The built-in counter generates the refresh address in self-refresh and CBR refresh cycles. Since this address increments sequentially from the last cycle in either self-refresh or CBR operation to the first cycle in the alternate refresh mode, CBR refreshing should be used during normal read and write operation to refresh one address location every 62 µs or less. If some other means of refreshing is used, it is necessary to do a burst refresh of all storage cells just before changing to and just after exiting self-refresh operation.

83-004502B

Figure 3. Timing Restrictions for Entering and Exiting Self-Refresh Operation

# **Timing Waveforms**

# Read Cycle

# Write Cycle (Early Write)

### Page-Mode Read Cycle

# Page-Mode Write Cycle (Early Write)

## RAS-Only Refresh Cycle

# CAS Before RAS Refresh Cycle

## Self-Refresh Cycle