## NJU25301

Dolby® Digital (AC-3) Decoder

DOLEY

## Description

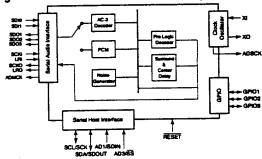

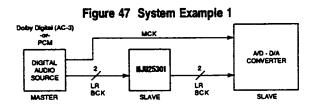

The NJU25301 is a complete low-cost 5.1 channel AC-3<sup>ext</sup> decoder intended for use in Dolby Digital consumer and multimedia applications. The NJU25301 contains on-chip firmware for decoding and processing Dolby Digital (AC-3) bitstreams and linear PCM data. It also includes a Dolby Pro Logic decoder for decoding matrix surround encoded PCM data or 2 channel Dolby Surround encoded digital data. It is also the industry's first Dolby certified, Class A Dolby Digital decoder IC to include 8 separate Bass Management Configurations. All features are implemented in on-chip memory (program ROM) eliminating the need for external memory devices. The decoder is controlled via a serial host interface which includes a choice of industry-standard I<sup>2</sup>C-Bus or SPI bus communication protocols. Standard digital audio data formats are supported, including I<sup>2</sup>S, MSB-first right-justified, and MSB-first left-justified.

NJU25301 utilizes a 24-bit DSP architecture developed by NJRC. The highly accurate processing of the NJU25301 makes it suitable for applications such as AV Receivers, DVD players, Digital Multimedia Speakers, and HDTV set-top decoders.

#### Features

- ◆ Complete Class A Dolby Digital Decoder

Supports 16-, 18-, 20-, or 24-bit data words

Audio sample rates: 32 kHz, 44.1 kHz, 48 kHz

Decodes up to 5.1 channel, 448 kbps Dolby Digital

bitstream

- ◆ Eight Dolby Certified Bass Management Modes 5 Dolby Configurations for Processing Dolby Digital 3 Dolby Configurations for Processing Dolby Pro Logic

- ◆ Automatic Bitstream Detection

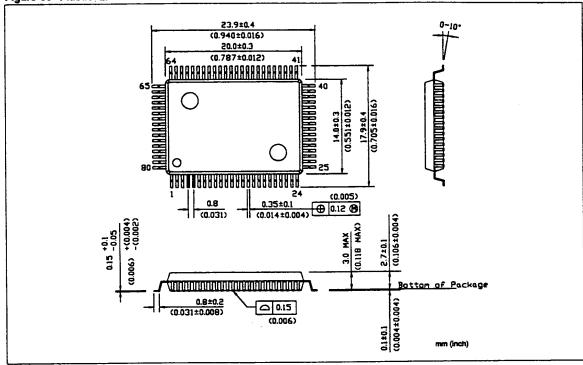

- ◆ Small 80-pin PQFP package

- ◆ On-chip features:

AC-3 Decoding

Dolby Pro Logic Decoding

Surround and Center Channel Delays

Pink Noise Generator

Automatic Bass Management Mode Adjustment (upon detection of change from 5.1 (AC-3) to Pro Logic encoded material, or vice versa)

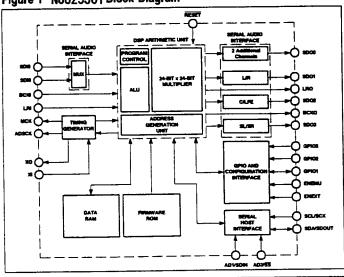

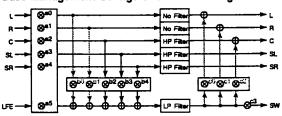

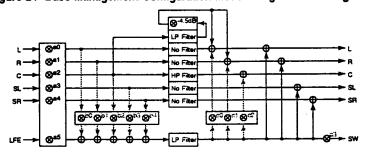

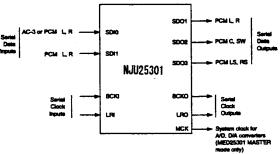

Figure 1 NJU25301 Block Diagram

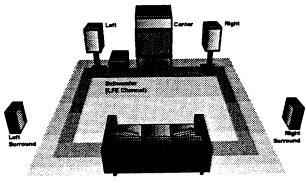

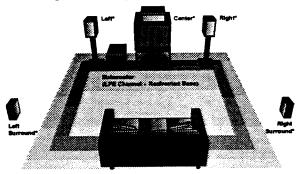

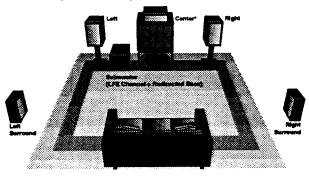

Figure 2 Typical Room Setup

"Dolby," "Pro Logic," "Dolby Digital," "AC-3," and the double-D symbol are trademarks of Dolby Laboratories. The ILJU25301 may only be supplied to licensees of or companies authorized by Dolby Laboratories. Please refer all licensing inquiries to Dolby Laboratories, phone 415.558.0200, fax 415.863.1373. "Typical Room Setup" graphic courtesy of Dolby Laboratories, I<sup>2</sup>C-8us is a registered trademark of Philips Electronics N.V.

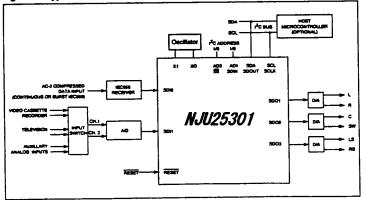

Figure 3 NJU25301 Pin Configuration 40 Reserved Reserved 65 39 Reserved Reserved 66 38 Reserved Reserved 67 37 Reserved Reserved 68 36 Reserved V<sub>SS</sub> 69 35 V<sub>DD</sub> V<sub>DD</sub> 70 34 V<sub>SS</sub> BCKI 71 33 Reserved LRI 72 *NJU25301* 32 Reserved VSS 73 31 Reserved V<sub>DO</sub> 74 30 Reserved SDI0 75 29 Reserved SDI1 76 28 V<sub>DD</sub> Reserved 77 27 V<sub>SS</sub> Reserved 78 26 RESET SDC3 79 25 ENEXT SDO2 80 SDA/SDOUT 14 SCL/SCK AD1/SDIN AD3/88

Figure 4 Typical AV Receiver Configuration with 5.1 Channels

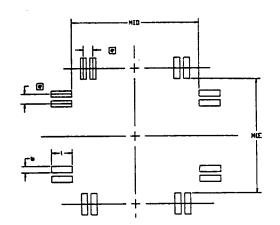

Figure 5 PQFP-80 Package

New Japan Radio Co., Ltd.

**Table 1 Pin Description**

| No. | Symbol             | vo         | Function                                                                                  | No. | Symbol     | W            | Function                                     |

|-----|--------------------|------------|-------------------------------------------------------------------------------------------|-----|------------|--------------|----------------------------------------------|

| 1   | SDO1               | 0          | Digital audio serial data output                                                          | 41  | NC         |              | No connect                                   |

| 2   | SDO0               | 0          | Digital audio serial data output                                                          | 42  | NC         |              | No connect                                   |

| 3   | LRO                | ō          | Left/right word clock output                                                              | 43  | NC         |              | No connect                                   |

| 4   | ВСКО               | 0          | Digital audio serial clock output                                                         | 44  | NC         |              | No connect                                   |

| 5   | VSS                | Ť          | Ground                                                                                    | 45  | NC         |              | No connect                                   |

| 6   | VDD                | 1          | Power supply terminal: +5V                                                                | 46  | vss        | 1            | Ground                                       |

| 7   | GPIO3 <sup>1</sup> |            | Host type select. SPI bus = L, I <sup>2</sup> C-bus = H                                   | 47  | VDD        | 1            | Power supply terminal: +5V                   |

| 8   | GP102 <sup>1</sup> | 1          | AC-3 Downmix Mode default power-up setting.<br>5.1 ch = L, 2.1 ch = H                     | 48  | NC         |              | No connect                                   |

| 9   | GPIO1              | 2          | General purpose interface                                                                 | 49  | NC         |              | No connect                                   |

| 10  | ENEMU              |            | Test pin (tie low for normal operation)                                                   | 50  | NC         | 1            | No connect                                   |

| 11  | VSS                | -          | Ground                                                                                    | 51  | NC         |              | No connect                                   |

| 12  | VDD                |            | Power supply terminal: +5V                                                                | 52  | VSS        |              | Ground                                       |

| 13  | SCL/SCK            | ı          | I <sup>2</sup> C-bus host serial clock/SPI bus host serial clock                          | 53  | VDD        |              | Power supply terminal: +5V                   |

| 14  | SDA/SDOUT          | vo         | 12C-bus host serial data/SPI bus host serial data output                                  | 54  | NC         |              | No connect                                   |

| 15  | AD1/SDIN           | 1          | I <sup>2</sup> C-bus host serial address/SPI bus host serial data input                   | 55  | NC         |              | No connect                                   |

| 16  | AD3/SS             | 1          | l <sup>2</sup> C-bus host serial address/SPI bus host slave select                        | 56  | NC         |              | No connect                                   |

| 17  | vss                | 1          | Ground                                                                                    | 57  | NC         | <u> </u>     | No connect                                   |

| 18  | VDD                | T          | Power supply terminal: +5V                                                                | 58  | NC         | <u> </u>     | No connect                                   |

| 19  | хо                 | 0          | Crystal                                                                                   | 59  | vss        | <u> </u>     | Ground                                       |

| 20  | VDD                | 1          | Power supply terminal: +5V                                                                | 60  | VDD        | 11           | Power supply terminat: +5V                   |

| 21  | ΧI                 | 1          | Crystal/External clock input                                                              | 61  | NC         | ļ            | No connect                                   |

| 22  | VSS                | 1          | Ground                                                                                    | 62  | NC         | <u> </u>     | No connect                                   |

| 23  | MCK                | 0          | 256Fs master clock for A/D, D/A converters                                                | 63  | NC         | L            | No connect                                   |

| 24  | ADSCK              | 0          | 32Fs/64Fs option serial clock for A/D, D/A converters and microcontrollers (default 32Fs) | 64  | NC         |              | No connect                                   |

| 25  | ENEXT              | 1          | Test pin (tie low for normal operation)                                                   | 65  | NC         | —            | No connect                                   |

| 26  | RESET              | 1          | Reset                                                                                     | 66  | NC         | <b>├</b> —   | No connect                                   |

| 27  | VSS                | 1          | Ground                                                                                    | 67  | NC         | $\vdash$     | No connect                                   |

| 28  | VDD                | 1          | Power supply terminal: +5V                                                                | 68  | NC         | <del> </del> | No connect                                   |

| 29  | NC                 | <u> </u>   | No connect                                                                                | 69  | VSS        | 1            | Ground St. St.                               |

| 30  | NC                 | <u> </u>   | No connect                                                                                | 70  | VDD        | 1            | Power supply terminal: +5V                   |

| 31  | NC                 | _          | No connect                                                                                | 71  | BCKI       | +            | Digital audio serial clock input             |

| 32  | NC                 | 1_         | No connect                                                                                | 72  | LRI        | 1            | Left/right frame clock input                 |

| 33  | NC                 | lacksquare | No connect                                                                                | 73  | VSS        | ╀            | Ground  Review events terminal: LEV          |

| 34  | vss                | 11         | Ground                                                                                    | 74  | VDD        | +-           | Power supply terminal: +5V                   |

| 35  | VDD                | 1          | Power supply terminal: +5V                                                                | 75  | SDI0       | +            | Digital audio serial data input              |

| 36  | NC                 | -          | No connect                                                                                | 76  | SDI1       | 1            | Digital audio serial data input              |

| 37  | NC                 |            | No connect                                                                                | 77  | NC<br>NC   | +-           | No connect                                   |

| 38  | NC                 | ļ          | No connect                                                                                | 78  | NC<br>CDO2 | +            | No connect  Digital audio serial data output |

| 39  | NC                 | ļ          | No connect                                                                                | 79  | SD03       | 10           |                                              |

| 40  | NC                 | 1          | No connect                                                                                | 80  | SDO2       | 0            | Digital audio serial data output             |

<sup>1.</sup> Only sensed upon power-up.

## Functional Description

The NJU25301 is a high performance dedicated digital signal processor designed to decode Dolby Digital, and matrix surround encoded (Dolby Surround) digital audio bitstreams. All decoding algorithms are contained in preprogrammed firmware, thus reducing time-to-market for the user. The DSP core has been optimized for audio processing which reduces cost compared to general-purpose DSPs.

The NJU25301 automatically detects the type of input data, allowing it to switch between compressed Dolby Digital or linear PCM bitstreams. No external commands are required to recognize and decode incoming bitstreams. The Dolby Digital bitstream contains decoding information which indicate how the audio is processed. Through a simple and flexible command protocol, the user can manually override certain bitstream elements (such as compression modes) to obtain desired audio playback characteristics.

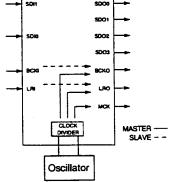

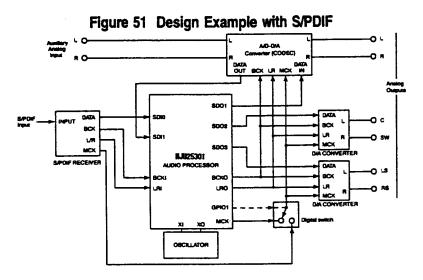

The NJU25301 includes two stereo digital audio inputs [SDI0:1] and four stereo digital audio outputs [SDO0:3], however only three of these stereo digital audio outputs [SDO1:3] are used for this Dolby Digital solution. Dolby digital data, conventionally formatted as a stereo digital audio signal, can be applied to the SDI0 input while an optional stereo A/D converter can be connected to the second input, SDI1. The digital inputs and outputs can be configured to 16, 18, 20 or 24 bits resolution using any of I<sup>2</sup>S, left-justified or right-justified formats allowing connection to virtually any type of audio A/D and D/A converters.

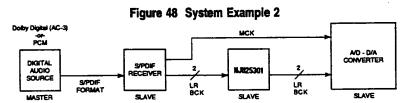

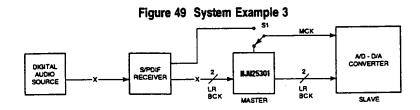

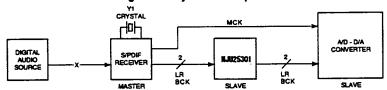

The :NJU25301 can also accept inputs from an IEC958 (S/PDIF) receiver. IEC958 is typically used to transfer Dolby Digital (AC-3) data between consumer audio equipment. The NJU25301 transfers serial audio clocking signals when receiving digital audio data from an external source such as an IEC958 receiver. This default (start-up) mode of operation is referred to as SLAVE mode as the external audio source establishes the audio clock rate. The NJU25301 can also be programmed to generate serial audio clocking signals (MASTER mode). MASTER mode can be used to receive analog audio inputs from an A/D converter when an external digital source is not chosen or is not available.

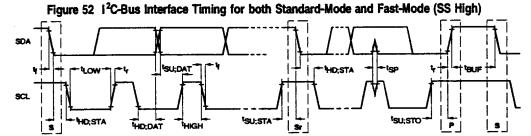

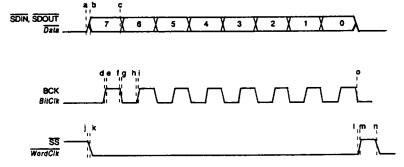

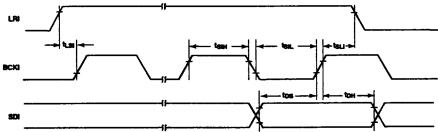

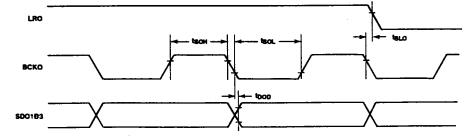

The NJU25301 serial host interface can be enabled to operate with either I<sup>2</sup>C-bus format or SPI bus format. The NJU25301 has a command-based instruction set simplifying microcontroller programming. No knowledge of DSP coding is required to use the NJU25301. Commands include AC-3 decoder parameters, compression modes, Pro Logic variables, channel delays, and downmix modes. For very simple applications, NJU25301 may be operated without a microcontroller as a 5.1 channel or 2.1 channel (downmixed) AC-3 decoder. The bitstream auto-detect feature allows proper decoding of either AC-3 or Linear PCM audio streams without user input.

The DSP core consists of a 24-bit processor with a 48-bit accumulator. All required memory elements, including data RAM, program ROM, and delay RAM are included on chip. The core's 24-bit processing allows for improved accuracy compared to 16-bit or 20-bit cores, delivering superior signal-to-noise performance for complex and low-level signals.

The NJU25301 is ideally suited for multi-channel home theater applications, where high performance Dolby Digital decoding must be performed at low cost. With an optional A/D converter connected to the second input, the NJU25301 can perform Pro Logic processing of analog source material.

The bass management engine alleviates the need for a system designer to handle bass management in the analog domain. The NJU25301 offers 8 different bass management modes, all of which have been approved by Dolby Laboratories. This method of bass management saves both time and money. It simplifies the system design, saves board real estate and shortens the approval period taken by Dolby Laboratories upon review of the "pre-production prototype" in a two fold method: Since bass management is performed in the digital domain, it will result in a much lower noise floor from the final product and since this method of bass management is already approved by Dolby, there is a reduced need to review post AC-3 decoding schematics.

## **Decoding Configurations**

The NJU25301 as different decoding configurations that take into consideration different speaker arrangements. This is helpful in handling situations where the user may not desire a full 5.1 channel output with all the corresponding speakers.

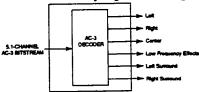

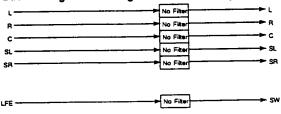

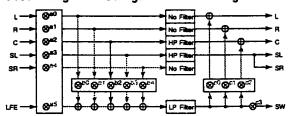

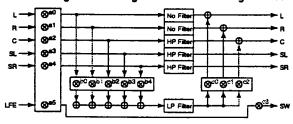

Figure 6 5.1-channel Dolby Digital Decoding

The default configuration for NJU25301 is 5.1-channel Dolby Digital decoding. No external components, memory elements, or microprocessor are required for this configuration. This is configuration is displayed above in Figure 6.

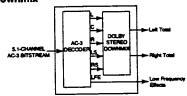

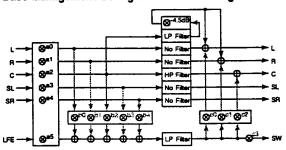

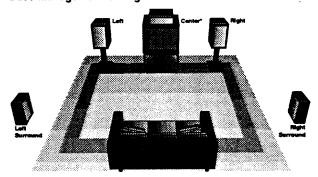

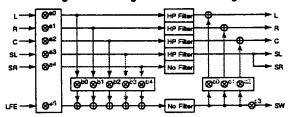

Figure 7 5.1-channel Dolby Digital with Dolby Surround (L., R.) Downmix

5.1-channel AC-3 bitstreams may be downmixed to two channels which contain Dolby Surround encoding. These outputs can be used with Dolby Pro Logic receivers. This mode can also be selected without a microcontroller.

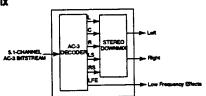

Figure 8 5.1-channel Dolby Digital with Stereo ( $L_0$ ,  $R_0$ ) Downmix

5.1-channel bitstreams can be decoded and downmixed into two channels for normal stereo output. The Low Frequency Effects channel is available as an optional subwoofer output.

Figure 9 2-channel encoded bitstream decoding

NJU25301 decodes Dolby Digital sources containing from 1 to 5.1 channels. Here, the NJU25301 decodes a 2-ch AC-3 bitstream.

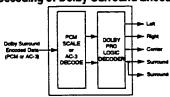

Figure 10 Decoding of Dolby Surround Encoded Material

PCM data which has Dolby Surround (Pro Logic) encoding can be decoded and processed by NJU25301. Surround channels are monaural by definition.

## Audio Processing Description

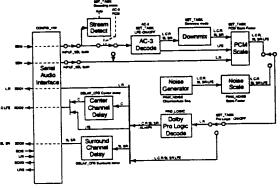

The NJU25301 processes audio signals received and returned by way of the Serial Audio Interface. Details of the audio processing functions are shown in Figure 12. Audio processing functions can be programmed by commands sent via the Serial Host Interface. Most commands as described in the Command Table change parameters of the audio processing functions. Other commands configure the Serial Audio Interface and read or write data at the General Purpose Input/Output (GPIO) Interface.

Figure 11 NJU25301 Functional Drawing

Figure 12 Detail of NJU25301 Audio Processing Functions

## Compression Modes Overview

## Custom Mode 0 (Analog) - Summary of features:

- · Dialog normalization (Dialnorm) always off

- · -11dB gain shift imposed when downmixing, in order to prevent peak level overload

- . Dynang compression variable used

- · Low-level boost compression (Dynschh) scaling allowed

- · High-level cut compression (Dynscll) scaling allowed

Custom Mode 0 (Analog) allows the degree of compression applied to be scaled down or defeated under any condition. The only restriction is that when downmixing is active, an -11dB gain shift is imposed to ensure no signal overload will occur. End products using the Custom Mode 0 (Analog) will require +11dB of selectable gain correction after the external D/A converter. Under these conditions, the final audio outputs may exhibit a higher noise floor. In addition, dialog normalization must be accomplished in analog circuitry external to the NJU25301 decoder IC. This is usually done in the master volume control, under the control of the dialnorm variable in the bitstream.

#### Custom Mode 1 (Digital) - Summary of features:

- · Dialog normalization (Dialnorm) always off

- · -11dB gain shift imposed when downmixing, in order to prevent peak level overload

- · Dynrng compression variable used

- · Low-level boost compression (Dynsch) scaling allowed

- · High-level cut compression (Dynscll) scaling allowed

Custom Mode 1 (Digital) allows the degree of compression applied to be scaled down or defeated under any condition. The only restriction is that when downmixing is active, an -11dB gain shift is imposed to ensure no signal overload will occur. End products using the Custom Mode 1 (Digital) will require +11dB of selectable gain correction after the external D/A converter. Under these conditions, the final audio outputs may exhibit a higher noise floor. However, unlike Custom Mode 0 (Analog), dialog normalization is handled internally.

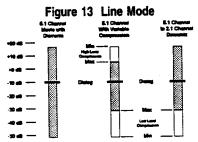

#### Line Mode - Summary of features:

- · Dialog normalization (Dialnorm) always on

- · Dialog is reproduced at a constant level

- Dynang compression variable is used

- Low-level boost compression scaling (Dynscih) is allowed

- High-level cut compression scaling (Dynscll) is allowed, provided no downmix is requested (downmix mode set to 111b)

One of the conditions of the Line Mode is the full high-level compression is applied whenever downmixing is active, so its effect cannot be reduced. Below, Figure 13 depicts the signal relationships, under different conditions when the device is in Line Mode. Note that the average program loudness remains constant, regardless of the downmix or compression settings.

#### RF Mode - Summary of features:

- · Dialog normalization is always on

- Dialog reproduced at a constant level (-20 dB FS)

- · Dynrng and compr compression variables used

- · Compression scaling not allowed

- · +11dB gain shift imposed

This mode is optimized for products generating a downmixed signal for subsequent "channel 3" RF demodulation. The overall program level is raised 11dB, while the peaks are limited to prevent signal overload in the external D/A converters. By limiting headroom to a maximum of 20 dB above average dialog level, overmodulation of television receivers is prevented while providing an average RF modulation level that compares well with quality television broadcasts and premium movie channels. Below, Figure 14 depicts the signal relationships, under different conditions when the device is in RF Mode. Note that the average program loudness remains constant, regardless of the downmix setting. Compression remains fully on at all times.

Figure 14 RF Mode

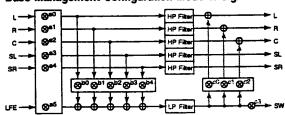

## Bass Management Overview

The traditional AC-3 speaker configuration consists of separate speakers for Front Left and Right, Center, Surround Left and Right, and Subwoofer. These are usually referred to as L, R, C, SL, SR, SW respectively. This configuration is commonly referred to as "5.1"channels of output, rather than "six", since the Subwoofer generally has a much lower bandwidth than the other five speakers. It is also assumed that the other five speakers are "full-range" speakers with good response below 100 Hz. Frequencies much lower than that are difficult for the ear to determine point-source direction, and are therefore usually placed on the "Subwoofer" (SW) channel.

In typical AC-3 systems, the "Low Frequency Effects" (LFE) goes directly to the Subwoofer. But for some systems, this may not be the optimal configuration. Often one or more of the five main speakers is capable of truly low frequency response, reaching down into the lowest octave of audible range. This is most often the case in systems which were upgraded from a high-quality stereo (two speaker) system. Usually in such arrangements, the Left and Right Stereo speakers become the Front Left and Right speakers in a multichannel system. In such cases, it may not be necessary to have a Subwoofer, or it may be desirable to transfer the lower frequencies to the higher-quality speakers. This function is called "Bass Management." Additionally, since many home systems were previously Pro Logic enabled, it is entirely plausible that not all of the speakers (especially those previously dedicated for the Pro Logic surround information) were designed to have a full-range frequency response. From this consideration, one can easily see the value that Bass Management adds to a Dolby Digital system.

## Mode 0 (Bass Management Off)

Mode 0 is the default mode, and Bass Management is off. All the Gain Block coefficients  $(a0 \sim a5) = 1$ , as does (c3). This results in each of the audio signals passing through unchanged. This mode is recommended for systems that have full-range speakers on each of the primary five channels, plus a Subwoofer for LFE information.

Figure 15 Bass Management Configuration Mode 0: Recommended Room Setup

Figure 16 Bass Management Configuration Mode 0: Signal Block Diagram

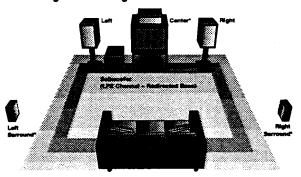

## Bass Management Mode 1 (AC-3 Mode)

Mode 1 adds all of the five main channels to the output of the Low Frequency Effects (LFE) channel. This summation is then filtered to allow only the low frequencies to pass, and the gain is increased by 6dB. Other than using a High-Pass filter, no other processing is done on the main five channels. This mode is recommended for systems that have limited low-frequency response on the primary five channels, but have a Subwoofer.

Figure 17 Bass Management Configuration Mode 1: Recommended Room Setup

\* Indicates Reduced Frequency Response

Figure 18 Bass Management Configuration Mode 1: Signal Block Diagram<sup>1</sup>

Table 2 Default Coefficient Set for Bass Management Configuration Mode 1

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decima<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|-----------------|

| a0          | 7FFF         | 1                | b0          | 16C2         | 0.177            | α0          | XXXX         | X               |

| <b>a</b> 1  | 7FFF         | 1                | <b>b</b> 1  | 16C2         | 0.177            | c1          | XXXX         | X               |

| a2          | 7FFF         | 1                | b2          | 16C2         | 0.177            | 62          | XXXX         | X               |

| <b>a</b> 3  | 7FFF         | 1                | b3          | 16C2         | 0.177            | ය           | XXXX         | X               |

| a4          | 7FFF         | 1                | b4          | 16C2         | 0.177            |             |              |                 |

| a5          | 47FA         | 0.562            |             |              |                  |             |              |                 |

1. "xxxx" indicate that the setting of these coefficients is not applicable.

New Japan Radio Co., Ltd.

Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

## Bass Management Mode 2 (AC-3 Mode)

Mode 2 uses the two Front output channels to augment the bass response of the Subwoofer output by adding the Center and Surround channels to the LFE channel, low-pass filtering it, and adding the filtered response to the two Front channels. This configuration could be used for five-speaker systems where the two front speakers are of extended bass range.

Figure 19 Bass Management Configuration Mode 2: Recommended Room Setup

\*\* Indicates Reduced Frequency Response

Figure 20 Bass Management Configuration Mode 2: Signal Block Diagram<sup>1</sup>

Table 3 Default Coefficient Set for Bass Management Configuration Mode 21

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| a0          | 7FFF         | 1                | b0          | 0000         | 0                | α0          | 0000         | 0                |

| a1          | 7FFF         | 1                | b1          | 0000         | 0                | c1          | 0000         | 0                |

| a2          | 7FFF         | 1                | b2          | 16C2         | 0.177            | 2           | 0000         | 0                |

| <b>a</b> 3  | 7FFF         | 1                | b3          | 16C2         | 0.177            | ය           | 7FFF         | 1                |

| a4          | 7FFF         | 1                | b4          | 16C2         | 0.177            |             |              |                  |

| <b>a</b> 5  | 47FA         | 0.562            |             |              | -                | •           |              |                  |

1. "xxxx" indicate that the setting of these coefficients is not applicable.

New Japan Radio Co., Ltd.

Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

## Bass Management Mode 3 (AC-3 Mode)

Mode 3 uses a different connection diagram than the previous three modes. In this configuration, the Center channel is high-pass filtered and that output goes to the Center speaker. It is also low-pass filtered, and that output goes to the two Front outputs. This configuration could be used for five-speaker systems where the two front speakers are of extended bass range, and the Center speaker is of limited bandwidth.

Figure 21 Bass Management Configuration Mode 3: Recommended Room Setup

\*\* Indicates Reduced Frequency Response

Figure 22 Bass Management Configuration Mode 3: Signal Block Diagram<sup>1</sup>

Table 4 Default Coefficient Set for Bass Management Configuration Mode 31

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| a0          | 50C2         | 0.631            | b0          | XXXX         | X                | 8           | XXXX         | X                |

| a1          | 50C2         | 0.631            | b1          | XXXX         | X                | c1          | XXXX         | X                |

| a2          | 50C2         | 0.631            | b2          | XXXX         | X                | 22          | XXXX         | X                |

| a3          | 50C2         | 0.631            | b3          | XXXX         | X                | ය           | XXXX         | X                |

| a4          | 50C2         | 0.631            | b4          | XXXX         | x                |             |              |                  |

| <b>a</b> 5  | 50C2         | 0.631            |             |              |                  |             |              |                  |

<sup>1. &</sup>quot;xxxx" indicate that the setting of these coefficients is not applicable.

Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

#### Bass Management Mode 4 (AC-3 Mode)

Mode 4 uses a different connection diagram than Modes 1 - 3. In this configuration, the Center channel is high-pass filtered and that output goes to the Center output. It is also low-pass filtered, and that is added to the two Front outputs. In addition, the LFE output is summed with the two Front speakers as well as the Surround channels. This configuration could be used for five-speaker systems where the Front and Surround speaker pairs are of extended bass range.

Figure 23 Bass Management Configuration Mode 4: Recommended Room Setup

™ Indicates Reduced Frequency Response

Figure 24 Bass Management Configuration Mode 4: Signal Block Diagram<sup>1</sup>

Table 5 Default Coefficient Set for Bass Management Configuration Mode 41

|             |              |                  |             |              | •                | _           |              |                  |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

| a0          | 32FA         | 0.398            | ь0          | XXXX         | X                | 8           | XXXX         | X                |

| a1          | 32FA         | 0.398            | b1          | XXXX         | x                | c1          | XXXX         | X                |

| a2          | 32FA         | 0.398            | b2          | XXXX         | X                | 22          | XXXX         | X                |

| a3          | 32FA         | 0.398            | b3          | xxxx         | X                | ය           | XXXX         | X                |

| a4          | 32FA         | 0.398            | b4          | XXXX         | X                |             |              |                  |

| a5          | 32FA         | 0.398            |             |              |                  | -           |              |                  |

1. "xxxx" indicate that the setting of these coefficients is not applicable.

Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

#### Bass Management Mode 5 (Pro Logic Mode)

This is the Pro Logic adaptation of Mode 1. However, there is only one Surround channel produced, and no Low Frequency Effects output. Mode 5 synthesizes all 5.1 channels with filtering and summations. Note that while the Surround channel is high-pass filtered, no contribution is made to the Subwoofer channel. This is due to the phasing of the signals and the reduced low-end frequency response that this channel inherently has. It is a configuration similar to NJRC current Dolby Pro Logic devices.

Figure 25 Bass Management Configuration Mode 5: Recommended Room Setup

\*\* Indicates Reduced Frequency Response

Figure 26 Bass Management Configuration Mode 5: Signal Block Diagram<sup>1</sup>

Table 6 Default Coefficient Set for Bass Management Configuration Mode 51

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| a0          | 7FFF         | 1                | b0          | 16C2         | 0.177            | 80          | XXXX         | X                |

| a1          | 7FFF         | 1                | b1          | 16C2         | 0.177            | c1          | XXXX         | X                |

| a2          | 7FFF         | 1                | b2          | 16C2         | 0.177            | <b>c</b> 2  | XXXX         | ×                |

| a3          | 7FFF         | 1                | b3          | 0000         | 0                | ය           | XXXX         | X                |

| a4          | 0000         | 0                | b4          | 0000         | 0                | <u> </u>    |              |                  |

| a5          | 0000         | 0                |             |              |                  | -           |              |                  |

<sup>1. &</sup>quot;xxxx" indicate that the setting of these coefficients is not applicable.

Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

#### Bass Management Mode 7 (Pro Logic Mode)

This is the Pro Logic adaptation of Mode 2. However, there is only one Surround channel produced, and no Low Frequency Effects output. While similar to Mode 5 or 6, this time there is Subwoofer channel contribution from the Center Channel. Mode 7 synthesizes all 5.1 channels with filtering and summations. Note that while the Surround channel is high-pass filtered, no contribution is made to the Subwoofer channel. This is a configuration for systems with a Subwoofer, and extended bass on all but the Center channel.

Figure 27 Bass Management Configuration Mode 7: Recommended Room Setup

\*\* Indicates Reduced Frequency Response

Figure 28 Bass Management Configuration Mode 7: Signal Block Diagram<sup>1</sup>

Table 7 Default Coefficient Set for Bass Management Configuration Mode 71

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| a0          | 7FFF         | 1                | bO          | 0000         | 0                | 8           | 0000         | 0                |

| a1          | 7FFF         | 1                | b1          | 0000         | 0                | c1          | 0000         | 0                |

| a2          | 7FFF         | 1                | b2          | 16C2         | 0.177            | <b>c</b> 2  | 0000         | 0                |

| a3          | 7FFF         | 1                | b3          | 0000         | 0                | ස           | 7FFF         | 1                |

| a4          | 0000         | 0                | b4          | 0000         | 0                |             |              |                  |

| <b>a</b> 5  | 0000         | 0                |             |              |                  | -           |              |                  |

1. "xxxx" indicate that the setting of these coefficients is not applicable.

New Japan Radio Co., Ltd. .

Arrows and coefficients in grey indicate that there is no fundamental connection or have been grey-out for illustrative purposes.

#### Bass Management Mode 8 (Pro Logic Mode)

This is the Pro Logic adaptation of Mode 10. However, there is only one Surround channel produced, and no Low Frequency Effects output. While similar to Mode 7, this time the low frequency component is summed back into the Front outputs. Mode 8 does not produce a Subwoofer output. Note that while the Surround channel is high-pass filtered, no contribution is made to the Subwoofer channel, it is for systems with extended bass on the front speakers, and no Subwoofer.

Figure 29 Bass Management Configuration Mode 8: Recommended Room Setup

Figure 30 Bass Management Configuration Mode 8: Signal Block Diagram<sup>1</sup>

Ø=2 HP FI Ø<sup>23</sup> HP File

⊗<sup>b2</sup> (8<sup>c0</sup>⊗<sup>c1</sup>⊗ 8 **⊗**t

Table 8 Default Coefficient Set for Bass Management Configuration Mode 81

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| a0          | 7FFF         | 1                | p0          | 0000         | 0                | 8           | 7FFF         | 1                |

| a1          | 7FFF         | 1                | <b>b</b> 1  | 0000         | 0                | c1          | 7FFF         | 1                |

| a2          | 7FFF         | 1                | b2          | 4C3F         | 0.595            | 22          | 0000         | 0                |

| a3          | 7FFF         | 1                | b3          | 0000         | 0                | ය           | 0000         | 0                |

| a4          | 0000         | 0                | b4          | 0000         | 0                |             |              |                  |

| a5          | 0000         | 0                |             |              |                  | •           |              |                  |

<sup>1. &</sup>quot;boox" indicate that the setting of these coefficients is not applicable.

<sup>1.</sup> Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

#### Bass Management Mode 10 (AC-3 Mode)

This is an AC-3 configuration. As such, there is a Low Frequency Effects output. While similar to Mode 2, this time the low frequency component of the Center and Surround channels is summed back into the Front outputs. Mode 10 keeps the LFE separate, going directly to the Subwoofer output. This configuration is used where the Front speakers are of extended range.

Figure 31 Bass Management Configuration Mode 10: Recommended Room Setup

Figure 32 Bass Management Configuration Mode 10: Signal Block Diagram<sup>1</sup>

Table 9 Default Coefficient Set for Bass Management Configuration Mode 101

| Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value | Coefficient | Hex<br>Value | Decimal<br>Value |

|-------------|--------------|------------------|-------------|--------------|------------------|-------------|--------------|------------------|

| a0          | 7FFF         | 1                | ь0          | 0000         | 0                | 8           | XXXX         | X                |

| a1          | 7FFF         | 1                | <b>b</b> 1  | 0000         | 0                | c1          | XXXX         | X                |

| a2          | 7FFF         | 1                | b2          | 4C3E         | 0.595            | 2           | XXXX         | X                |

| a3          | 7FFF         | 1                | b3          | 4C3E         | 0.595            | ස           | XXXX         | x                |

| a4          | 7FFF         | 1                | b4          | 4C3E         | 0.595            |             |              |                  |

| <b>a</b> 5  | 7FFF         | 1                |             |              |                  | •           |              |                  |

<sup>1. &</sup>quot;boox" indicate that the setting of these coefficients is not applicable.

Arrows and coefficients in gray indicate that there is no fundamental connection or have been grayed-out for illustrative purposes.

## NJU25301 Commands

NJU25301 allows for user configuration of the decoder with microcontroller commands entered via the Host I/O interface (I<sup>2</sup>C-bus or SPI bus). The following table summarizes the available user commands.

Table 10 NJU25301 Command Table

| No. | Command                       | Mnemonic          | Description                                                                                  |

|-----|-------------------------------|-------------------|----------------------------------------------------------------------------------------------|

| 1.  | Set Task                      | SET_TASK_CMD      | Sets primary decoding mode: AC-3, Dolby Pro Logic, or Linear PCM                             |

| 2.  | AC-3 Decode                   | AC3_CMD           | Sets AC-3 compression and dialog normalization modes                                         |

| 3.  | Pro Logic Decode              | PRO_LOGIC_CMD     | Sets the variables for Pro Logic decoding                                                    |

| 4.  | Bass Management Configuration | BASS_MGMT_CFG_CMD | Sets Bass Management Configuration Mode                                                      |

| 5.  | Delay Configuration           | DELAY_CFG_CMD     | Sets amount of delay in Center channel and Surround channels                                 |

| 6.  | Pink Noise Generator          | PINK_NOISE_CMD    | Sets variables for the noise generator (used for system setup)                               |

| 7.  | Play                          | PLAY_CMD          | Resumes playing after a stop command                                                         |

| 8.  | Stop                          | STOP_CMD          | Stops operation and mutes the output                                                         |

| 9.  | Mute                          | MUTE_CMD          | Mutes the output without interrupting internal operation                                     |

| 10. | Unmute                        | UNMUTE_CMD        | Restores output after a mute command                                                         |

| 11. | Status                        | STAT_CMD          | Reads the AC-3 bitstream commands (status register)                                          |

| 12  | Version number                | VERSION_NUM_CMD   | Reads the version number                                                                     |

| 13. | Audio Interface               | AUDIOIF_CFG_CMD   | Configures serial audio interface format, ADSCK, divider ratios, LR & BCK Master/Slave, etc. |

| 14. | Set I/O                       | SETIO_CMD         | Sets and reads the device general purpose I/O (GPIO) pins                                    |

| 15. | Input Select                  | INPUT_SEL_CMD     | Selects serial audio source connected at input SDI0 or SDI1                                  |

## NJU25301 Command Details1

#### Command 1: Set Task

| No. | Mnemonic     | OpCode+ | Bytes Written | Bytes Read |

|-----|--------------|---------|---------------|------------|

| 1,  | SET_TASK_CMD | 0xC0    | 6             | 0          |

#### Set Task Command Details

The Set Task command controls the decoder's main operating characteristics. These are: Decode Mode (AC-3 or Linear PCM), Pro Logic decoding (ON/OFF), LFE (ON/OFF), Downmix Mode, PCM Scale Factor and Maximum Frame Repeat Before Muting.

**Table 11 Set Task Parameters**

| Byte | Bit 7 | Bit 6                                           | Bit 5 | Bit 4            | Bit 3           | Bit 2 | BR 1                                    | Bit 0 |  |

|------|-------|-------------------------------------------------|-------|------------------|-----------------|-------|-----------------------------------------|-------|--|

| 1    |       | Decoding Mode                                   |       | Pro Logic        |                 | Res   | erved                                   |       |  |

| 2    |       | Rese                                            | erved |                  | LFE             |       | Downmix Mode                            |       |  |

| 3    |       | PCM Scale Factor (Upper Byte)                   |       |                  |                 |       |                                         |       |  |

| 4    |       |                                                 |       | PCM Scale Fact   | or (Lower Byte) |       |                                         |       |  |

| 5    |       | Maximum Frame Repeat Before Muting (Upper Byte) |       |                  |                 |       |                                         |       |  |

| 6    |       |                                                 |       | n Frame Repeat B |                 |       | *************************************** |       |  |

Reset state default values are indicated by asterisks (\*) or by text (default) in the command descriptions. Italicized text refers

to variables in the AC-3 bitstream.

#### Parameter 1. Decoding Mode (Byte 1: Bits 7, 6, 5)

Sets the primary decoding mode.

Table 12 Set Task: Decoding Mode

| Value | Description                  |  |  |  |  |

|-------|------------------------------|--|--|--|--|

| 000   | AC-3 Decode (Test Only)      |  |  |  |  |

| 001   | Reserved                     |  |  |  |  |

| 010   | Linear PCM Mode (Test Only)  |  |  |  |  |

| 011   | Pink Noise Generator         |  |  |  |  |

| 100   | Reserved (silence)           |  |  |  |  |

| 101   | Reserved (silence)           |  |  |  |  |

| 110   | Reserved (silence)           |  |  |  |  |

| 111"  | Automatic Stream Detection*1 |  |  |  |  |

Automatic Stream Detection mode enables AC-3 decoding if an AC-3 input stream is detected, otherwise processes input as a Linear PCM stream.

#### Parameter 2. Pro Logic (Byte 1: Bit 4)

A value of 1 enables the Pro Logic decoder when the input is either PCM, or 2-channel Surround encoded AC-3. A value of 0 (default) disables the function.

#### Parameter 3. Low Frequency Effects (Byte 2: Bit 3)

A value of 1 (default) enables Dolby Digital LFE processing (subwoofer channel), while a value of 0 disables LFE processing. (It should be noted that only when an AC-3 encoded stream contains LFE information will audio be produced out of the subwoofer).

#### Parameter 4. Downmix Mode (Byte 2: Bits 2, 1, 0)

These bits are used to specify the output channel configurations for AC-3 decoding.

Table 13 Set Task: Downmix Mode

| Value | Description           |                                                       |  |  |  |  |

|-------|-----------------------|-------------------------------------------------------|--|--|--|--|

| 000   | 1+1 (Dual Mono Mode)  | Lo, Ro (Stereo)                                       |  |  |  |  |

| 001   | 1/0 (1 Front, 0 Rear) | С                                                     |  |  |  |  |

| 010*1 | 2/0 (2 Front, 0 Rear) | L <sub>T</sub> , R <sub>T</sub> (Matrixed Surround)*1 |  |  |  |  |

| 011   | 3/0 (3 Front, 0 Rear) | L, C, R                                               |  |  |  |  |

| 100   | 2/1 (2 Front, 1 Rear) | L, R, S (Mono Surround)                               |  |  |  |  |

| 101   | 3/1 (3 Front, 1 Rear) | L, C, R, S (Mono Surround)                            |  |  |  |  |

| 110   | 2/2 (2 Front, 2 Rear) | L, R, SL, SR                                          |  |  |  |  |

| 111-2 | 3/2 (3 Front, 2 Rear) | L, C, R, SL, SR-2                                     |  |  |  |  |

Default if GPIO2=HIGH state during reset sequence.

#### Parameter 5. PCM Scale Factor (Bytes 3, 4)

The PCM scale factor allows for volume control of all output channels. Byte 3 is the upper byte and byte 4 is the lower byte of the 16-bit scale multiplier. This multiplier is a two's complement fraction between zero 0x0000 and 0x7FFF (2<sup>15</sup> -1). Multiplier values from 0x8000 to 0xFFFF are not used. Default parameter is 0x7FFF (0dB).

<sup>2.</sup> Default if GPIO2=LOW state during reset sequence.

#### Parameter 6. Maximum Frame Repeat (Bytes 5, 6)

Byte 5 is the high byte and byte 6 is the low byte for the frame repeat function. In case of CRC error or an invalid bitstream, this command will allow the decoder to repeat the last valid frame until a new valid frame is received. The 16-bit control word indicates the maximum number of frames which will be repeated before the output will be muted. Default is 0x0000 (no repeat).

#### Command 2: AC-3 Decode

| No. | Mnemonic | OpCode + | Bytes Written | Bytes Read |

|-----|----------|----------|---------------|------------|

| 2   | AC3_CMD  | 0xC1     | 5             | 0          |

#### AC-3 Decode Command Details

These parameters are used to control specific aspects of the AC-3 decoding engine. These are: Dynamic Range Boost Factor (Dynsch), Dynamic Range Cut Factor (Dynsch), Compression Mode (Compmod) and Dual Mode (Dualmode).

Table 14 AC-3 Decode Parameters

| Byte | Bit 7                | Bit 6                | Bit 5 | Bit 4      | Bit 3      | Blt 2 | Bit 1 | Bit 0 |

|------|----------------------|----------------------|-------|------------|------------|-------|-------|-------|

| 1    |                      |                      |       | Dynscih (U | pper Byte) |       |       | *     |

| 2    | Dynscih (Lower Byte) |                      |       |            |            |       |       |       |

| 3    |                      | Dynscli (Upper Byte) |       |            |            |       |       |       |

| 4    | Dynsdl (Lower Byte)  |                      |       |            |            |       |       |       |

| 5    | Reserved Comprised   |                      |       |            |            | Dual  | mode  |       |

#### Parameter 1. Dynamic Range Boost Factor (Dynsch) (Bytes 1, 2)

Byte 1 is the high byte and byte 2 is the low byte for dynamic range boost scale factor. The scale factor is a two's complement fraction between zero 0x0000 and 0x7FFF (2<sup>15</sup>-1) which is used to scale the dynamic range. Parameter values from 0x8000 to 0xFFFF are not allowed. Default parameter is 0x0000. A value of zero disables dynamic range boost.

#### Parameter 2. Dynamic Range Cut Factor (Dynscll) (Bytes 3. 4)

Byte 3 is the high byte and byte 4 is the low byte for dynamic range cut scale factor. The parameter is a two's complement fraction between zero 0x0000 and 0x7FFF (2<sup>15</sup> -1). Parameter values from 0x8000 to 0xFFFF are not allowed. Default parameter is 0x0000. A value of zero disables dynamic range cut.

#### Parameter 3. Compression Modes (Compmod) (Byte 5: Bits 3, 2)

Table 15 AC-3 Decode: Compression Modes

| Value | Description                        |  |

|-------|------------------------------------|--|

| 00    | Custom Mode (Analog) <sup>1</sup>  |  |

| 01    | Custom Mode (Digital) <sup>1</sup> |  |

| 10°   | Line Mode*                         |  |

| 11    | RF Mode                            |  |

Both Custom Modes, Analog and Digital, defeat some or all of the features of the Line and RF Modes, thus shifting the burden to the product designer for implementation elsewhere in the audio path. If the Custom Modes are used, dialog normalization, dynamic compression, and downmixing functions must be accomplished external to the decoder IC.

-New Japan Radio Co., Ltd.

#### Parameter 4. Dual Mode (Dualmode) (Byte Bits 1, 0)

Table 16 AC-3 Decode: Dual Mode

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 00*   | Independent Channels*                                    |

| 01    | Left Channel Copied to Both Left and Right Channels      |

| 10    | Right Channel Copied to Both Left and Right Channels     |

| 11    | inputs Scaled by -6dB, Summed, and Sent to Both Channels |

#### Command 3: Pro Logic Decode

|   | No. Mnemonic |               | OpCode + | Bytes Written | Bytes Read |  |

|---|--------------|---------------|----------|---------------|------------|--|

| П | 3.           | PRO_LOGIC_CMD | 0xC4     | 1             | 0          |  |

#### Pro Logic Decode Command Details

This command configures variables for Pro Logic decoding such as: setting the decoding coefficients to match the audio sampling rate, Wide Surround (ON/OFF), Auto Balance (ON/OFF), Stereo 3 (ON/OFF), and Phantom Center (ON/OFF).

**Table 17 Pro Logic Decode Parameters**

|   | Byte | 8tt 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3         | Bit 2        | Bit 1    | Bit 0          |

|---|------|-------|-------|-------|-------|---------------|--------------|----------|----------------|

| Γ | 1    | Rese  | erved | Sampi |       | Wide Surround | Auto Balanca | Stereo 3 | Phantom Center |

#### Parameter 1. Sample Rate (Samprate) (Byte 1: Bits 5, 4)

Sets Pro Logic decoding coefficients to match the system audio sample rate. Note: This command does not cause or determine the sampling rate at the senal audio interface.

Table 18 Pro Logic Decode: Sample Rate

| Value | Description             |

|-------|-------------------------|

| 00*   | Sample Rate = 48 kHz*   |

| 01    | Sample Rate = 44.1 kHz  |

| 10    | Sample Rate = 32 kHz    |

| 11    | Sample Rate = 22.05 kHz |

#### Parameter 2. Wide Surround (Byte 1: Bit 3)

A value of 0 (default) applies a 7 kHz low pass filter and a Dolby B noise reduction on the surround channel. A value of 1 allows for the surround channel to have full audio bandwidth.

#### Parameter 3. Auto Balance (Byte 1: Bit 2)

A value of 1 enables auto balance, while a value of 0 (default) disables the function.

#### Parameter 4. Stereo 3 (Byte 1: Bit 1)

A value of 1 enables the surround channel, while a value of 0 (default) disables the surround channel.

#### Parameter 5. Phantom Center (Byte 1: Bit 0)

A value of 1 disables the center speaker, mixing the left and right to create a phantom center channel, while a value of 0 (default) enables the center channel.

#### Command 4: Bass Management Configuration

| No. | Mnemonic          | OpCode + | Bytes Written | Bytes Read |

|-----|-------------------|----------|---------------|------------|

| 4.  | BASS_MGMT_CFG_CMD | 0xC5     | 1             | 0          |

#### Bass Management Configuration Command Details

This command sets the Bass Management Configuration. Byte 1, Bits 3-0 set which mode the NJU25301 will be set to. Mode 0 disables Bass Management altogether.

Table 19 Bass Management Configuration Parameters<sup>1</sup>

| Byte | Bit 7 | BR 6 | Blt 5 | Bit 4 | Bit 3 | Bit 2        | BR 1            | Bit 0 |

|------|-------|------|-------|-------|-------|--------------|-----------------|-------|

| 1    | 0     | 0    | 0     | 0     |       | s Management | Configuration M | ode   |

<sup>1.</sup> Byte 2, bits 7-4 must be set to zero.

#### Table 20 Bass Management Configuration Modes

| Value <sup>1</sup> | Configuration                                                   | Mode Legal Only When Processing | Configuration Description                                                                                                                                                                                                            |

|--------------------|-----------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000°              | Mode 0*                                                         | Either Class of Stream          | Bass Management Disabled*                                                                                                                                                                                                            |

| 0001               | Mode 1 <sup>2</sup>                                             | AC-3 Discrete Channel Stream    | Bass from all 5 channels is redirected to the Subwoofer. This is in addition to the LFE information the Subwoofer is already receiving.                                                                                              |

| 0010               | Mode 2 <sup>3</sup> AC-3 Discrete Channel Stream Right addition |                                 | Bass from Center and Surround channels is redirected to the Left and<br>Right channels and Subwoofer. For the Left and Right channels, this is<br>additional bass. For the Subwoofer, this is in addition to the LFE<br>information. |

| 0011               | Mode 3                                                          | AC-3 Discrete Channel Stream    | Bass from the Center channel is redirected to the Left and Right channels. For the Left and Right channels, this is additional bass. The Subwoofer only receives LFE information.                                                    |

| 0100               | Mode 4                                                          | AC-3 Discrete Channel Stream    | Bass from Center channel and all LFE information is redirected to the Front and Surround channels. No information is sent to the Subwoofer.                                                                                          |

| 0101               | Mode 5                                                          | Pro Logic Encoded Stream        | Bass from Left, Right and Center channels are redirected to the<br>Subwoofer.                                                                                                                                                        |

| 0111               | Mode 7                                                          | Pro Logic Encoded Stream        | Bass from Center channel is redirected to the Subwoofer.                                                                                                                                                                             |

| 1000               | Mode 8                                                          | Pro Logic Encoded Stream        | Bass from Center channel is redirected to Left and Right channels. No information is sent to the Subwoofer.                                                                                                                          |

| 1010               | Mode 10 <sup>4</sup>                                            | AC-3 Discrete Channel Stream    | Bass from Center and Surround channels is redirected to Left and Right channels. Only LFE information is sent to the Subwoofer.                                                                                                      |

<sup>1.</sup> All other values than those listed here are invalid.

#### Command 5: Delay Configuration

| No. | Mnemonic      | OpCode + | Bytes Written | Bytes Read |

|-----|---------------|----------|---------------|------------|

| 5.  | DELAY_CFG_CMD | 0xC6     | 4             | 0          |

#### **Delay Configuration Command Details**

Delay Configuration sets the time delay applied to surround channels and center channel when AC-3 or Pro Logic decoding is active. Center and surround delays are expressed as 16-bit words that represent delay as a number of audio sample periods. Thus the delay time is a function of the audio sampling rate: Delay(mS)= DELAY/Audio Sample Rate(kHz).

Applies only when NJU25301 is processing an AC-3 discrete channel stream only. Should the NJU25301 be sent a Pro Logic encoded stream, it will automatically switch to Mode 5. Vice Versa scenario applies.

Applies only when NJU25301 is processing an AC-3 discrete channel stream only. Should the NJU25301 be sent a Pro Logic encoded

Applies only when NJU25301 is processing an AC-3 discrete channel stream only. Should the NJU25301 be sent a Pro Logic encoded stream, it will automatically switch to Mode 7. Vice Versa scenario applies.

Applies only when NJU25301 is processing an AC-3 discrete channel stream only. Should the NJU25301 be sent a Pro Logic encoded stream, it will automatically switch to Mode 8. Vice Versa scenario applies.

Maximum allowed delay settings for AC-3 decoding and delay time at 48kHz sample rate:

Center:

DELAY=0x00EF(max)/48 kHz = 5mS

Surround:

DELAY=0x02CF(max)/48 kHz = 15mS

Maximum allowed delays for Dolby ProLogic decoding at 48kHz sample rate:

Center: Surround: DELAY=0x00EF(max)/48 kHz = 5mS

DELAY=0x059F(max)/48 kHz = 30mS

Table 21 Delay Configuration Parameters<sup>1</sup>

| Byte | Bit 7                       | Bit 6                     | Bit 5 | Bit 4         | Bit 3          | BR 2 | Bit 1 | BX 0 |

|------|-----------------------------|---------------------------|-------|---------------|----------------|------|-------|------|

| 1    |                             |                           |       | Surround Dela | y (Upper Byte) |      |       |      |

| 2    | Surround Delay (Lower Byte) |                           |       |               |                |      |       |      |

| 3    |                             | Center Delay (Upper Byte) |       |               |                |      |       |      |

| 4    |                             |                           |       | Center Delay  | (Lower Byte)   |      |       |      |

<sup>1.</sup> Surround Delay default value is 0 ms (0x0000). Center Delay default value is 0 ms (0x0000).

#### Command 6: Pink Noise Generator

| No. | Mnemonic       | OpCode + | Bytes Written | Bytes Read |

|-----|----------------|----------|---------------|------------|

| 6.  | PINK_NOISE_CMD | 0xC7     | 3             | 0          |

#### Pink Noise Generator Command Details

This command sets the global variables for the pink noise generator function.

Table 22 Pink Noise Generator Parameters<sup>1</sup>

| Byte | Bit 7    | BR 6                            | Bit 5 | Bit 4          | Bit 3           | BR 2          | Bit 1          | BR 0      |

|------|----------|---------------------------------|-------|----------------|-----------------|---------------|----------------|-----------|

| 1    | Reserved | Sequence                        | Left  | Right          | Center          | Left Surround | Right surround | Subwoofer |

| 2    |          | Noise Scale Factor (Upper Byte) |       |                |                 |               |                |           |

| 3    |          |                                 |       | Noise Scale Fa | ctor (Lower Byl | ie)           |                |           |

All Bits in Byte1 are mutually exclusive. If more than one are set, the least most significant bit is effective. The default value of Byte 1 is 01000000b.

A value of 1 in bits 6:0 enables pink noise for the selected channel. Bit 6 (sequence) automatically sequences noise as L, C, R, SL, SR, in two second intervals. The Noise Scale Factor (bytes 2 and 3) is a 16-bit word which controls noise amplitude. Scale factor is a two's complement fraction between zero 0x0000 and 0x7FFF (2<sup>15</sup> -1). Values from 0x8000 to 0xFFFF are not used. Default parameter is 0x7FFF (0dB).

#### Command 7: Play

| No. | Mnemonic | OpCode + | Bytes Written | Bytes Read |

|-----|----------|----------|---------------|------------|

| 7.  | PLAY_CMD | 0xC9     | 0             | 0          |

#### Play Command Details

The Play command resumes operation of the selected function and restores the output after a Stop command. Play and Stop commands do not apply to Noise Generator.

#### Command 8: Stop

| ſ | No. | Mnemonic | OpCode+ | Bytes Written | Bytes Reed |

|---|-----|----------|---------|---------------|------------|

| Ì | 8.  | STOP_CMD | 0xCA    | 0             | 0          |

### Stop Command Details

The Stop command stops operation of the selected function and mutes the output. New data is ignored until a new Play command is sent. Play and Stop commands do not apply to Noise Generator.

#### Command 9: Mute

| No. | Mnemonic | OpCode + | Bytes Written | Bytes Read |

|-----|----------|----------|---------------|------------|

| 9.  | MUTE_CMD | 0xC8     | 0             | 0          |

#### **Mute Command Details**

The Mute command mutes the output without interrupting the selected function. Mute and Unmute commands do not apply to Noise Generator.

#### Command 10: Unmute

| No. | Mnemonic   | OpCode+ | Bytes Written | Bytes Read |

|-----|------------|---------|---------------|------------|

| 10. | UNMUTE_CMD | 0xCC    | 0             | 0          |

#### **Unmute Command Details**

The Unmute command restores the output while continuing the selected function. Mute and Unmute commands do not apply to Noise Generator.

## Command 11: Status

|   | No. | Mnemonic | OpCode + | Bytes Written | Bytes Read |

|---|-----|----------|----------|---------------|------------|

| 1 | 11. | STAT_CMD | 0xCD     | 0             | 11         |

#### Status Command Details

The Status command returns for 11 words of the status register to the host.

#### **Table 23 Status Parameters**

| Byte | Bit 7                                       | BR 6       | Bit 5        | Bit 4             | BR 3              | Bit 2               | BR 1              | Bit 0              |

|------|---------------------------------------------|------------|--------------|-------------------|-------------------|---------------------|-------------------|--------------------|

| 1    | run_stat (n                                 | un status) | out_sta      | at (AC-3 decode   | status)           | in_stat (AC         | -3 frame informa  | ition status)      |

| 2    | fscod (sar                                  | npie rate) |              | frmsizo           | od (input data ra | ate in kilobits per | r second)         |                    |

| 3    |                                             | Res        | erved        |                   | Ifeon             | acmo                | d (coding configu | ration)            |

| 4    | bsid (bitstream identification num          |            |              | mber of five bits | )                 | bsn                 | nod (bitstream m  | ode)               |

| 5    | cmixlev (center mix level) smixlev (surroun |            |              |                   |                   |                     |                   | ongos <sup>2</sup> |

| 6    |                                             | Reserved   |              | dialnom           | (dialogue norma   | alization for cha   | nnel 2 in dual mo | no mode)           |

| 7    |                                             | Reserved   |              | dialno            | orm (dialogue no  | rmalization valu    | e for normal ope  | ration)            |

| 8    |                                             | •          | langod2 (lan | nguage code for   | channel 2 in dua  | al mono mode)       |                   |                    |

| 9    |                                             |            | lango        | od (language coo  | le for normal op  | eration)            |                   |                    |

| 10   | audprodie23                                 | roomtyp2   | (room type)4 |                   | mixlevel          | 2 (mix level for a  | hannel 2)4        |                    |

| 11   | audprodie <sup>5</sup> roomtyp <sup>6</sup> |            |              |                   | <u> </u>          | Aixievel (mix lev   | 9i) <sup>6</sup>  |                    |

- 1. copyrightb = copyright information

- 2. origbs = original bitstream information

- 3. audprodie2 = production information in dual mono operation mode

- 4. midevel2, roomtyp2 = mix level and room type in dual mono operation mode

- 5. audprodie = production information in normal operation mode

- 6. mixlevel, roomtyp = mix level and room type in normal operation mode

#### Command 12: Version Number

| No. | Mnemonic        | OpCode + | Bytes Written | Bytes Read |

|-----|-----------------|----------|---------------|------------|

| 12  | VERSION_NUM_CMD | 0xCE     | 0             | 4          |

#### Version Number Command Details

The Version Number command returns four bytes representing version of the ROM-encoded firmware.

**Table 24 Status Parameters**

| Byte | Bit 7 | Bit 6                    | Bit 5 | Bit 4      | Bit 3          | BR 2 | Bit 1 | Bit 0 |

|------|-------|--------------------------|-------|------------|----------------|------|-------|-------|

| 1    |       |                          |       | Firmware V | ersion [31:24] |      |       |       |

| 2    |       | Firmware Version [23:16] |       |            |                |      |       |       |

| 3    |       |                          |       | Firmware 1 | Version [15:8] |      |       |       |

| 4    |       |                          |       | Firmware   | Version [7:0]  |      |       |       |

#### Command 13: Serial Audio Interface Configuration

| No. | Mnemonic      | OpCode+ | Bytes Written | Bytes Read |

|-----|---------------|---------|---------------|------------|

| 13. | AUDIO_CFG_CMD | 0xCF    | 9             | 0          |

#### Serial Audio Interface Configuration Command Details

The Serial Audio Interface Configuration command sets serial audio format and clock configurations. The command also set divide ratios for BCK clock outputs, Serial Audio Word Size, Audio Format, Clocks per Frame, Internal Bit Clock Divider and MASTER/SLAVE mode.

Table 25 Serial Audio Interface Configuration Parameters<sup>1</sup>

| Byte | Bit 7                     | 8 t 6                     | Bit 5               | Bit 4    | Blt 3           | Bit 2                               | Bit 1               | Bit 0                     |

|------|---------------------------|---------------------------|---------------------|----------|-----------------|-------------------------------------|---------------------|---------------------------|

| 1    | 0                         | 0                         | 0                   | 0        | 0               | 0                                   | 0                   | 0                         |

| 2    | 0                         | 1                         | ADSCK <sup>2</sup>  | 1        | 0               | 1                                   | 0                   | 0                         |

| 3    | 1                         | 0                         | 0                   | 0        | 0               | 0                                   | 0                   | 0                         |

| 4    | 0                         | 1                         | 1                   | 1        | 0               | 1                                   | 0                   | 0                         |

| 5    | 0                         | 1                         | 0                   | 0        | S               | Serial Audio Word Size <sup>3</sup> |                     | Audio Format <sup>4</sup> |

| 6    | Audio Format <sup>4</sup> | Clocks/Frame <sup>5</sup> | 0                   | Internal | Bit Clock Divid | er <sup>8</sup> (BCKO)              | MASTER <sup>7</sup> | 0                         |

| 7    | 0                         | 0                         | 0                   | 0        | 0               | 0                                   | 0                   | 0                         |

| 8    | 0                         | 0                         | MASTER <sup>7</sup> | 0        | 0               | MASTER <sup>7</sup>                 | 0                   | 0                         |

| 9    | 1                         | 1                         | 1                   | 0        | 0               | 0                                   | 1                   | 0                         |

1. All fixed bits must be set by the host microcontroller for proper operation.

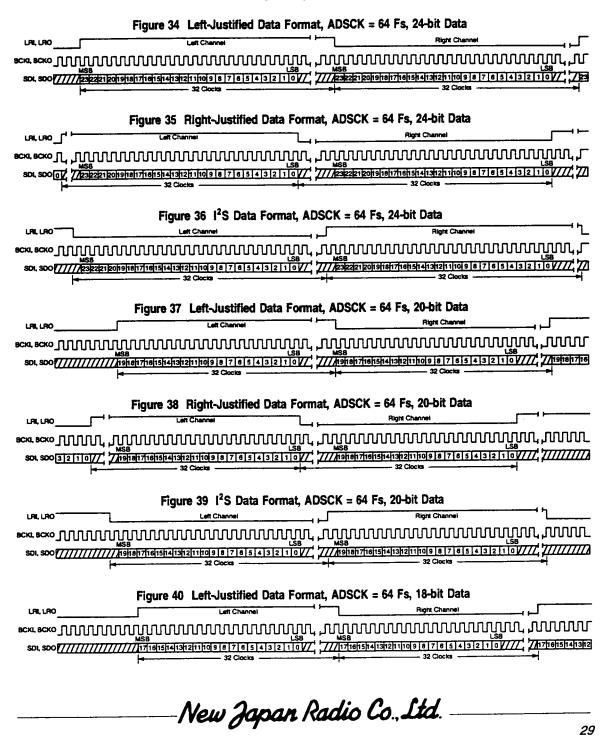

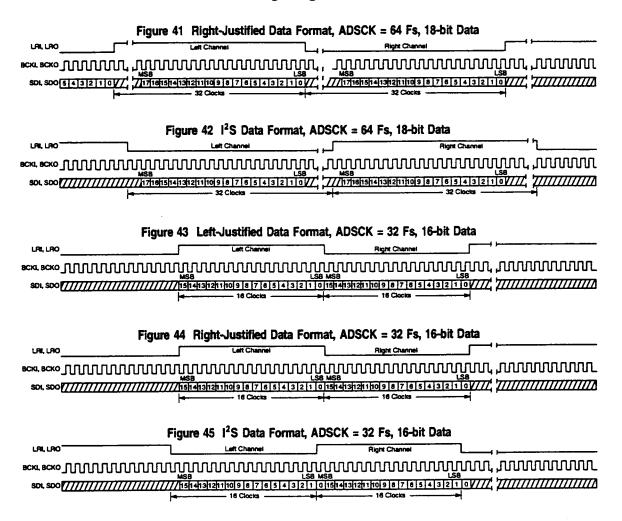

2. Divide ratios for ADSCK are set here. When ADSCK is set HIGH, the system clock rate provided at XI is divided by 64 and output on the ADSCK pin, giving 64Fs. When ADSCK is set LOW (default), the output is the system clock divided by 128, giving 32Fs. This signal is usually used for clocking a system microcontroller, but can drive A/Ds and D/As. BCKO is the signal that is normally connected to A/Ds and D/As.

The Serial Audio Word Size is set here. Bit 3 is the MSB and Bit 1 is the LSB. Set the word size to either: 000 = 16-bits, 001 = 18-bits, 010 = 20-bits, or 011 = 24-bits (default).

The Serial Audio Data Format is set here. Byte 5, Bit 0 is the MSB. Byte 6, Bit 7 is the LSB. Hence, 00 = MSB-First Flight-Justified Format, 01 = MSB-First Left-Justified Format, 10 = 12S Format (default).

Setting Clocks/Frame to HIGH (default) sets the device to expect 64 clocks per LR Frame. Setting Clocks/Frame to LOW set the device to set expect 32 clocks per LR Frame.

6. The divide ratio for the internal bit clock is set here. If the device is in MASTER mode, then this parameter needs to be set to 001 so that the 256Fs source is divided by 4, giving a 64Fs bit clock. If the device is in SLAVE mode, the clock source is BCKI, hence the parameter should be set to 000 (divide ratio of 1). In either case, this signal is output on BCKO. ADSCK and BCKO are independent of each other.

Must be set HIGH if in the INVIESSO is to operate in MASTER mode or set LOW if in SLAVE mode (default). This determines the

generator source for the LRO and BCK pins.

MCK and BCK pins deliver constant frequency clocks generated by dividing the DSP clock at input pin XI. MCK is intended to provide system clock for A/D and D/A converters when NJU25301 operates as the MASTER serial audio clock source. Both MCK and ADSCK halt when RESET input is LOW.

Table 26 Typical Serial Audio Data Format, ADSCK, Clocks/Frame, and Master/Slave Configurations<sup>1</sup>

| 7,                       |           |       | •            | •                          | _                          |

|--------------------------|-----------|-------|--------------|----------------------------|----------------------------|

| Serial Audio Data Format | Word Size | ADSCK | Clocks/Frame | LR & BCK in SLAVE Mode     | LR & BCK in MASTER Mode    |

| <sup>2</sup> S           | 16-bit    | 32Fs  | 32           | 00 54 80 74 41 00 00 00 E2 | 00 54 80 74 41 06 00 24 E2 |

| Left-Justified           | 16-bit    | 32Fs  | 32           | 00 54 80 74 40 80 00 00 E2 | 00 54 80 74 40 86 00 24 E2 |

| Right-Justified          | 16-bit    | 32Fs  | 32           | 00 54 80 74 40 00 00 00 E2 | 00 54 80 74 40 06 00 24 E2 |

| r <sup>2</sup> S         | 18-bit    | 64Fs  | 64           | 00 74 80 74 43 40 00 00 E2 | 00 74 80 74 43 46 00 24 E2 |

| Left-Justified           | 18-bit    | 64Fs  | 64           | 00 74 80 74 42 C0 00 00 E2 | 00 74 80 74 42 C6 00 24 E2 |

| Right-Justified          | 18-bit    | 64Fs  | 64           | 00 74 80 74 42 40 00 00 E2 | 00 74 80 74 42 46 00 24 E2 |

| r²S                      | 24-bit    | 64Fs  | 64           | 00 74 80 74 47 40 00 00 E2 | 00 74 80 74 47 46 00 24 E2 |

| Left-Justified           | 24-bit    | 64Fs  | 64           | 00 74 80 74 46 C0 00 00 E2 | 00 74 80 74 46 C6 00 24 E2 |