# T1 (DS-1 and CEPT-1) Frequency Translator: PLXO

The AT&T T1 Frequency Translator.

#### **Features**

- Translates from:

- —CEPT-1 x 2 (4.096 MHz) to DS-1 (1.544 MHz)

- —CEPT-1 x 2 (4.096 MHz) to DS-1C (3.152 MHz)

- -DS-1 (1.544 MHz) to CÉPT-1 x 2 (4.096 MHz)

- -DS-1C (3.152 MHz) to CEPT-1 x 2 (4.096 MHz)

- 3-state option for board-level testing

- Compact 16-Pin DIP

- Fast acquisition time and low noise output

- Machine insertable

- Free-run mode on loss of input signal

- Surface mountable

- Loss of lock indicator

- Loss of input clock indicator

# **Description**

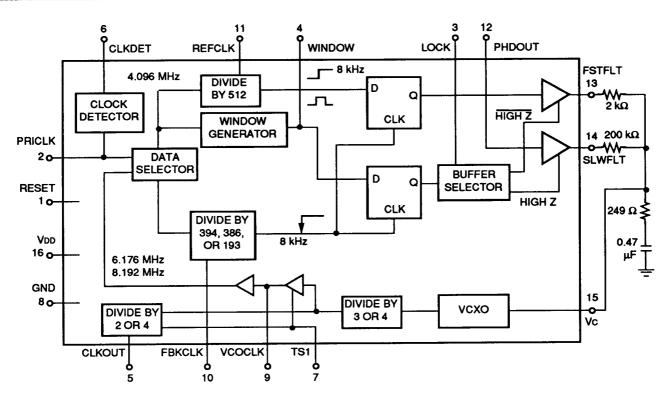

The Phase-locked Crystal Oscillator (PLXO) is a 16-pin, ceramic packaged device that provides frequency translation between telephone standard reference clocks associated with the DS-1, DS-1C, and CEPT-1 transmission rates. Frequency translation is accomplished using an internal, voltage-controlled crystal oscillator (VCXO) based phase-locked loop and user-supplied passive filter elements. The internal phase-locked loop provides two modes of operation. In locked mode, a low-pass filter with a large time constant (narrow bandwidth) is selected to provide a low noise output. In an out of lock mode, a low-pass filter with a small time constant (wide bandwidth) is selected to provide fast acquisition of the inbound clock. By comparing the relative edges of 8 kHz clocks supplied by the input clock and the internal VCXO, the phase detector determines if the loop is in or out of lock. Once lock is achieved, the phase detector switches from wide bandwidth filtering to narrow bandwidth filtering. To achieve this switch, the two outputs of the phase detector (FSTFLT and SLWFLT) are alternately set to a high-impedance state and drive a lead-lag filter created using user-supplied elements.

The PLXO will fully track the long-term stability of an inbound clock to  $\pm 130$  ppm of the nominal value over its full power supply and temperature range (-40 °C to +85 °C). At 25 °C, with VDD equal to 5 V, and no inbound clock present, the free-run frequency of the VCXO (at CLKOUT) will fall within  $\pm 75$  ppm of the nominal value. The CLKOUT frequency will fall within  $\pm 130$  ppm of the nominal value over the VCXO's full voltage and temperature range.

Figure 1. PLXO Functional Block Diagram

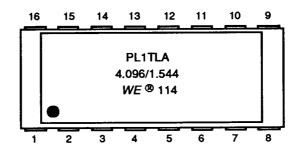

### Pin Information

Figure 2. Pin Diagram

**Table 1. Pin Descriptions**

| Pin# | Type | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 1    | RESET  | TTL logic low sets the output buffers of LOCK, WINDOW, CLKOUT, CLKDET, FBKCLK, REFCLK, PHDOUT, FSTFLT, and SLWFLT to a high-impedance state. If no input clock (PRICLK) is present, VCOCLK and CLKOUT go to a free-run mode. If PRICLK is present, the user may control VCOCLK and CLKOUT by varying Vc from 0 V to 5 V. When set to a logic low, a positive edge applied to both PRICLK and VCOCLK will reset all internal logic except the CLKOUT divider. The positive edge, applied to VCOCLK, may be generated either internally by the VCXO or externally by setting TS1 to a TTL logic low and applying a clock to VCOCLK (pin 9). RESET is internally pulled to TTL logic high during normal operation. |

| 2    | 1    | PRICLK | Primary clock input to which CLKOUT and VCOCLK are locked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3    | 0    | LOCK   | Lock is set to a TTL logic high if the positive edge of the 8 kHz clock derived from VCOCLK is within 244 ns of the positive edge of REFCLK. Otherwise, LOCK is set to a TTL logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4    | 0    | WINDOW | This 488 ns pulse occurs at an 8 kHz rate and is centered about the positive edge of the 8 kHz clock derived from PRICLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5    | 0    | CLKOUT | The output clock derived from VCOCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6    | 0    | CLKDET | Clock detect is a TTL logic high if a clock is present at pin PRICLK. This pin drops to a TTL logic low if no clock is applied to PRICLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7    | i i  | TS1    | A TTL logic low at Test Signal 1 (TS1) disables the output buffer from the VCXO and sets the CLKOUT divider to a divide-by-two mode. The user may then inject a test signal at VCOCLK for external circuit testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8    | ı    | GND    | Circuit and cover ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9    | I/O  | VCOCLK | An output clock derived from the internal on-chip VCXO based phase-locked loop. This pin also serves as an input for test signals with TS1 set to a TTL logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10   | 0    | FBKCLK | 16 kHz clock derived from VCOCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### Pin Information (continued)

Table 1. Pin Descriptions (continued)

| Pin# | Type | Symbol | Function                                                                                                                                                                                                                                                                  |

|------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | 0    | REFCLK | 8 kHz clock derived from the user-supplied PRICLK.                                                                                                                                                                                                                        |

| 12   | 0    | PHDOUT | The phase detector output is a TTL logic high if the positive edge of REFCLK leads the positive edge of the 8 kHz clock derived from VCOCLK. The pin is a TTL logic low if the positive edge of the REFCLK lags the positive edge of the 8 kHz clock derived from VCOCLK. |

| 13   | 0    | FSTFLT | This phase detector output drives a relatively wide bandwidth passive loop filter to provide fast acquisition of PRICLK on start-up. If LOCK is a TTL logic high, this output goes to a high-impedance state.                                                             |

| 14   | 0    | SLWFLT | This phase detector output pin drives a relatively low bandwidth lead-lag passive loop filter. If LOCK is a TTL logic low, this output is set to a high-impedance state until LOCK returns to a TTL logic high.                                                           |

| 15   | ı    | Vc     | Control voltage input to internal VCXO. Both the lead-lag passive filter SLWFLT and the wide-band passive filter FSTFLT are connected to this input.                                                                                                                      |

| 16   |      | VDD    | 5.0 V ± 10% supply voltage.                                                                                                                                                                                                                                               |

### **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. AT&T employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the mode. Although no industry-wide standard has been adopted for the CDM, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and therefore can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters.

**Table 2. ESD Threshold Voltage**

| Model          | ESD Threshold, Minimum | Unit |

|----------------|------------------------|------|

| Human Body     | 2500 <sup>*</sup>      | V    |

| Charged Device | 500                    | V    |

<sup>\*</sup> MIL-STD-1686-8/8/88, Class 2.

# **Electrical Specifications**

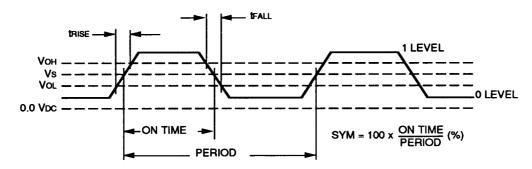

Figure 3. Output Waveform

**Table 3. General Electrical Specifications**

WARNING: Unit will be severely damaged if inserted backwards in a circuit.

| Parameter                                                                                                              | Symbol                | Min                | Max                | Unit                           |

|------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|--------------------|--------------------------------|

| Nominal Primary Clock Input Frequency                                                                                  | PRICLK                | See T              | able 4.            | MHz                            |

| Nominal Output Clock Frequency Nominal Output VCXO Clock Frequency                                                     | CLKOUT<br>VCOCLK      |                    | able 4.<br>able 4. | MHz                            |

| Supply Voltage                                                                                                         | VDD                   | 4.5                | 5.5                | V                              |

| Supply Current (VDD = 5.50 V)                                                                                          | loo                   | 5                  | 30                 | mA                             |

| Input Voltage Levels:<br>Input Logic High*<br>Input Logic Low*                                                         | Vih<br>Vil            | 2.0<br>—           | <br>0.8            | V<br>V                         |

| Output Voltage Levels: Output Logic High* Output Logic Low*                                                            | Vol.                  | 2.5<br>—           | —<br>0.5           | V<br>V                         |

| Transition Times:* Rise Time (0.5 V to 2.5 V) Fall Time (2.5 V to 0.5 V)                                               | trise<br>tfall        | 0.5<br>0.5         | 5.0<br>5.0         | ns<br>ns                       |

| Symmetry or Duty Cycle <sup>†</sup> (options 1 and 2): Output Clock Output VCXO Clock                                  | CLKOUT<br>VCOCLK      | 45<br>45           | 55<br>55           | %<br>%                         |

| Symmetry or Duty Cycle <sup>†</sup> (options 3 and 4): Output Clock Output VCXO Clock                                  | CLKOUT                | 45<br>28           | 55<br>38           | %<br>%                         |

| Nominal Output Frequency on Loss of Signal:<br>Output Clock (VDD = 5 V, 25 °C)<br>Output VCXO Clock (VDD = 5 V, 25 °C) | CLKOUT<br>VCOCLK      | -75 ppm<br>-75 ppm | +75 ppm<br>+75 ppm | ppm from FNOM<br>ppm from FNOM |

| Loss of Lock Indication: <sup>‡</sup> Output Logic High <sup>*</sup> Output Logic Low <sup>*</sup>                     | CLKDET-<br>VOH<br>VOL | 2.5<br>—           | —<br>0.5           | V                              |

| Primary Clock Input Frequency Variation                                                                                | ΔFNOM                 | -130               | 130                | ppm                            |

Figure 3 defines these parameters.

† Symmetry or Duty Cycle is the ON TIME/PERIOD with Vs = 1.4 V for TTL, per Figure 3.

<sup>‡</sup> The loss of signal (CLKDET) indicator is set to a TTL logic high if a clock is present at pin PRICLK. CLKDET is set to a TTL logic low if no clock is detected.

# Electrical Specifications (continued)

**Table 4. Frequency Translation Options**

| Option | Input Clock (PRICLK) | Output Clock (CLKOUT) | VCXO Clock (VCOCLK) |

|--------|----------------------|-----------------------|---------------------|

| 1      | 4.096 MHz            | 1.544 MHz             | 6.176 MHz           |

| 2      | 4.096 MHz            | 3.152 MHz             | 6.304 MHz           |

| 3      | 1.544 MHz            | 4.096 MHz             | 8.192 MHz           |

| 4      | 3.152 MHz            | 4.096 MHz             | 8.192 MHz           |

# **Mechanical Characteristics**

**Table 5. Mechanical and Environmental Conditions**

| Parameter            | Value                      |

|----------------------|----------------------------|

| Mechanical Shock     | MIL-STD-883C 2002.3 Test B |

| Mechanical Vibration | MIL-STD-883C 2007.1 Test C |

| Solderability        | MIL-STD-883C 2003.5        |

| Gross Leak Test      | MIL-STD-883C 1014.7        |

| Fine Leak Test       | MIL-STD-883C 1014.7        |

| Storage Temperature  | -55 °C to +125 °C          |

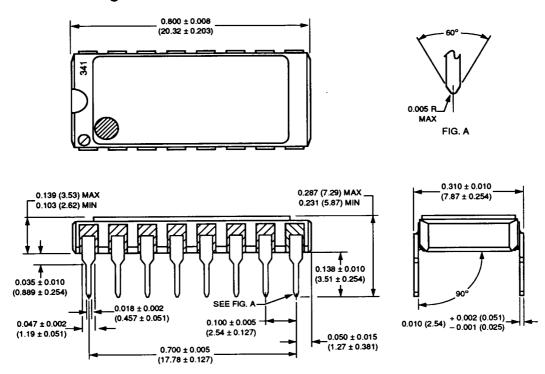

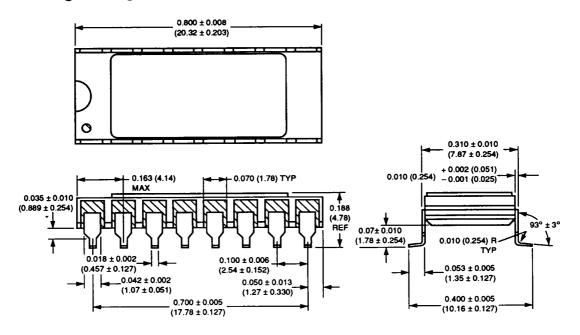

# **Outline Diagrams**

Dimensions are in inches and (millimeters).

#### **PLXO Thru-Hole Package**

### **PLXO Gull-Wing Package**

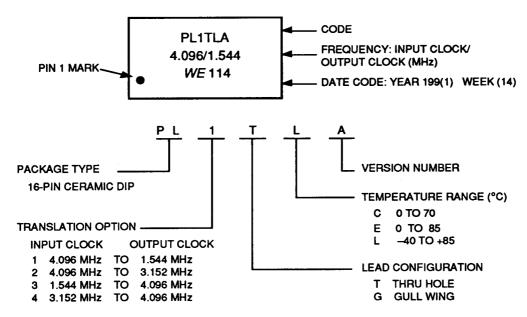

# **Ordering Information**

Figure 4. Part Numbering Information

For additional information, contact your AT&T Account Manager or the following:

U.S.A.: AT&T Microelectronics, Dept. 52AL040420, 555 Union Boulevard, Allentown, PA 18103

1-800-372-2447, FAX 215-778-4106 (In CANADA: 1-800-553-2448, FAX 215-778-4106)

EUROPE: AT&T Microelectronics, AT&T Deutschland GmbH, Bahnhofstr. 27A, D-8043 Unterfoehring, Germany

Tel. 089/950 86-0, Telefax 089/950 86-111

ASIA PACIFIC: AT&T Microelectronics Asia/Pacific, 14 Science Park Drive, #03-02A/04 The Maxwell, Singapore 0511

Tel. (65) 778-8833, FAX (65) 777-7495, Telex RS 42898 ATTM

JAPAN: AT&T Microelectronics, AT&T Japan Ltd., 31-11, Yoyogi 1-chome, Shibuya-ku, Tokyo 151, Japan

Tel. (03) 5371-2700, FAX (03) 5371-3556

SPAIN: AT&T Microelectronica de España, Poligono Industrial de Tres Cantos (Zona Oeste), 28770 Colmenar Viejo, Madrid, Spain

Tel. (34) 1-8071441, FAX (34) 1-8071420

AT&T reserves the right to make changes to the product(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product or circuit. WE is a registered trademark of AT&T.

Copyright © 1991 AT&T All Rights Reserved Printed in U.S.A.