4,194,304 WORD X BIT DYNAMIC RAM

\* This is advanced information and specifications are subject to change without notice.

#### DESCRIPTION

The TC514100J/Z is the new generation dynamic RAM organized 4,194,304 words by 1 bit. The TC514100J/Z utilizes TOSHIBA's CMOS Silicon gate process technology as well as advanced circuit techniques to provide wide operating margins, both internally and to the system user. Multiplexed address inputs permit the TC514100J/Z to be packaged in a standard 26/20 pin plastic SOJ and 20 pin plastic ZIP. The package size provides high system bit densities and is compatible with widely available automated testing and insertion equipment. System oriented features include single power supply of 5V±10% tolerance, direct interfacing capability with high performance logic families such as Schottky TTL.

#### **FEATURES**

- 4,194,304 word by 1 bit organization

- · Fast access time and cycle time

|                  |                               | TC514100J | /Z-80/ <b>-</b> 10 |

|------------------|-------------------------------|-----------|--------------------|

| <sup>t</sup> RAC | RAS Access Time               | `80ns     | 100ns              |

| tAA              | Column Address<br>Access Time | 40ns      | 50ns               |

| <sup>t</sup> CAC | CAS Access Time               | 20ns      | 25ns               |

| <sup>t</sup> RC  | Cycle Time                    | 150ns     | 180ns              |

| <sup>t</sup> PC  | Fast Page Mode<br>Cycle Time  | 50ns      | 60ns               |

· Single power supply of 5V±10% with a built-in V<sub>RR</sub> generator

## PIN COMNECTION (TOP VIEW)

| Pla  | stic S                                                                  | OJ                                                            | Pla                     | stic 2 | ZIP                                                        |

|------|-------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------|--------|------------------------------------------------------------|

| pind | 1 26<br>2 25<br>3 24<br>4 23<br>5 22<br>9 18<br>10 17<br>11 16<br>12 15 | VSS<br>DOUT<br>CAS<br>N.C.<br>DA9<br>DA8<br>DA7<br>DA6<br>DA5 | DOUT DIN RAS N.C. AO A2 |        | CAS<br>VSS<br>WRITE<br>A10<br>N.C.<br>A1<br>A3<br>A4<br>A6 |

| •    |                                                                         |                                                               |                         |        | A8                                                         |

#### PIN NAMES

| A0 ~ A10 | Address Inputs        |

|----------|-----------------------|

| RAS      | Row Address Strobe    |

| DIN      | Data In               |

| DOUT     | Data Out              |

| CAS      | Column Address Strobe |

| WRITE    | Read/Write Input      |

| VCC      | Power (+5V)           |

| VSS      | Ground                |

| N.C.     | No Connection         |

- · Low Power

- 550mW Operating (TC514100J/Z-80) 468mW Operating (TC514100J/Z-10) 5.5mW MAX. Standby

- · Output unlatched at cycle end allows twodimensional chip selection

- Common I/O capability using "EARLY WRITE" operation

- Read-Modify-Write, CAS before RAS refresh, RAS-only refresh, Hidden refresh, Fast Page Mode and Test Mode capability

- · All inputs and output TTL compatible

- 1024 refresh cycles/16ms

- Plastic SOJ: TC514100J Package Plastic ZIP: TC514100Z

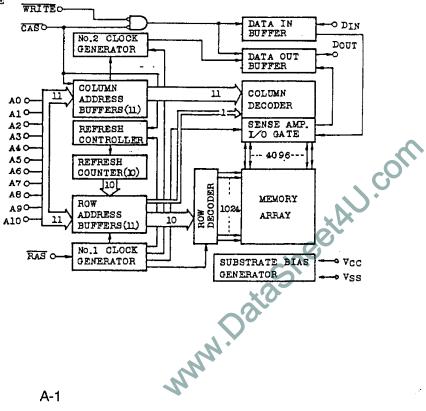

#### **BLOCK DIAGRAM**

### ABSOLUTE MAXIMUM RATINGS

| ITEM                         | SYMBOL           | RATING        | UNITS  | NOTE |

|------------------------------|------------------|---------------|--------|------|

| Input Voltage                | VIN              | -1 ∿ 7        | v      | 1    |

| Output Voltage               | VOUT             | -1 ~ 7        | v      | 1    |

| Power Supply Voltage         | v <sub>CC</sub>  | <b>-1</b> ∿ 7 | v      | 1    |

| Operating Temperature        | T <sub>OPR</sub> | 0 ∿ 70        | °C     | 1    |

| Storage Temperature          | TSTG             | -55 ∿ 150     | °c     | 1    |

| Soldering Temperature · Time | TSOLDER          | 260 • 10      | °C•sec | 1    |

| Power Dissipation            | PD               | 600           | mW     | 1    |

| Short Circuit Output Current | IOUT             | 50            | mA     | 1    |

## RECOMMENDED DC OPERATING CONDITIONS (Ta=0 ~ 70°C)

| SYMBOL | PARAMETER          | MIN. | TYP. | - MAX. | UNIT | NOTE |

|--------|--------------------|------|------|--------|------|------|

| VCC    | Supply Voltage     | 4.5  | 5.0  | 5.5    | V    | 2    |

| AIH    | Input High Voltage | 2.4  | T -  | 6.5    | V    | 2    |

| VIL    | Input Low Voltage  | -1.0 | -    | 0.8    | V    | 2    |

#### DC ELECTRICAL CHARACTERISTICS (Vcc=5V±10%, Ta=0 \ 70°C)

| SYMBOL            |                                                                                                                        |                                       | MIN. | MAX. | UNITS | NOTES |

|-------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|-------|-------|

| I <sub>CC1</sub>  | OPERATING CURRENT Average Power Supply Operating Current                                                               | TC514100J/Z-80                        | -    | 100  | mA    | 3,4,5 |

|                   | (RAS, CAS, Address Cycling: <sup>t</sup> RC≠ <sup>t</sup> RC MIN.)                                                     | TC514100J/Z-10                        | -    | 85   |       |       |

| I <sub>CC2</sub>  | STANDBY CURRENT Power Supply Standby Current (RAS=CAS=V <sub>IH</sub> )                                                |                                       | -    | 2    | mA    |       |

| I <sub>CC3</sub>  | RAS ONLY REFRESH CURRENT Average Power Supply Current, RAS Only Mode                                                   | TC514100J/Z-80                        | -    | 100  |       | 2.5   |

| -663              | (RAS Cycling, CAS=VIH: tRC=tRC MIN.)                                                                                   | TC514100J/Z-10                        | -    | 85   | mA    | 3,5   |

| I <sub>CC4</sub>  | FAST PAGE MODE CURRENT<br>Average Power Supply Current, Fast Page Mode                                                 | TC514100J/Z-80                        | -    | 60   | mА    | 3,4,5 |

|                   | TC514100                                                                                                               |                                       | -    | 50   | шА    | 3,4,5 |

| Icc2              | STANDBY CURRENT Power Supply Standby Current (RAS=CAS=VCC-0.2V)                                                        |                                       | _    | 1    | mA    |       |

| I <sub>CC6</sub>  | CAS BEFORE RAS REFRESH CURRENT Average Power Supply Current, CAS Before                                                | TC514100J/Z-80                        | -    | 100  |       |       |

| -00               | RAS Mode (RAS, CAS Cycling: tRC=tRC MIN.)                                                                              | TC514100J/Z-10                        | _    | : 85 | mA    | 3     |

| I <sub>I(L)</sub> | INPUT LEAKAGE CURRENT Input Leakage Current, any input (0V ≤ V <sub>IN</sub> ≤ 6.5V, All Other Pins Not Under Test=0V) |                                       |      | 10   | μA    |       |

| IO(L)             | OUTPUT LEAKAGE CURRENT (D <sub>OUT</sub> is disabled, OV ≤ V <sub>OUT</sub> ≤ 5.5V)                                    |                                       |      | 10   | μA    |       |

| v <sub>он</sub>   | OUTPUT LEVEL Output "H" Level Voltage (IOUT=-5mA)                                                                      |                                       |      |      | V     |       |

| OL                | OUTPUT LEVEL Output "L" Level Voltage (IOUT=4.2mA)                                                                     | · · · · · · · · · · · · · · · · · · · | -    | 0.4  | V     |       |

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(V_{CC}=5V\pm10\%, Ta=0\sim70^{\circ}C)$  (Notes 6, 7, 8)

|                   |                                                | TC514100J/Z-80 |         | <del>,</del> | 1                 | ., <u>.,</u> |         |

|-------------------|------------------------------------------------|----------------|---------|--------------|-------------------|--------------|---------|

| SYMBOL            | PARAMETER                                      | MIN.           | MAX.    | MIN.         | 100J/Z-10<br>MAX. | UNIT         | NOTES   |

| <sup>t</sup> RC   | Random Read or Write Cycle Time                | 150            | -       | 180          | -                 | ns           |         |

| tRMW              | Read-Modify-Write Cycle Time                   | 175            | _       | 210          | -                 | ns           |         |

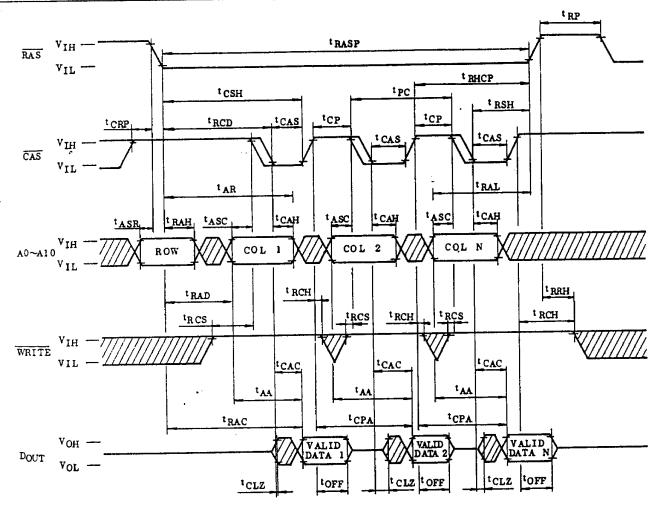

| <sup>t</sup> PC   | Fast Page Mode Cycle Time                      | 50             | _       | 60           | -                 | ns           |         |

| t PRMW            | Fast Page Mode Read-Modify-Write<br>Cycle Time | 75             | -       | 90           | -                 | ns           |         |

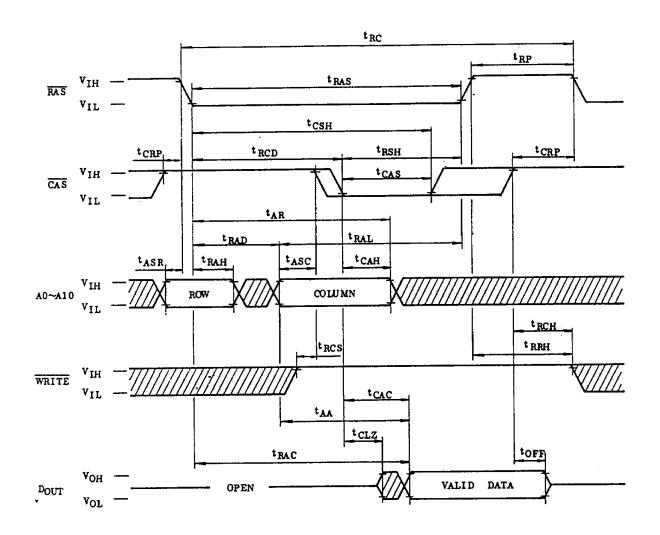

| tRAC              | Access Time from RAS                           | -              | 80      | -            | 100               | ns           | 9,14,15 |

| <sup>t</sup> CAC  | Access Time from CAS                           | -              | 20      | -            | 25                | ns           | 9,14    |

| <sup>t</sup> AA   | Access Time from Column Address                | -              | 40      | -            | 50                | ns           | 9,15    |

| <sup>t</sup> CPA  | Access Time from CAS Precharge                 | _              | 45      | -            | 55                | ns           | 9       |

| <sup>t</sup> CLZ  | CAS to Output in Low-Z                         | 0              | -       | 0            | -                 | ns           | 9       |

| tOFF              | Output Buffer Turn-off Delay                   | 0              | 20      | -0           | 20                | ns           | 10      |

| tΤ                | Transition Time (Rise and Fall)                | 3              | 50      | 3            | 50                | ns           | 8       |

| t <sub>RP</sub>   | RAS Precharge Time                             | 60             | -       | 70           | _                 | ns           |         |

| <sup>t</sup> RAS  | RAS Pulse Width                                | 80             | 10,000  | 100          | 10,000            | ns           |         |

| <sup>t</sup> RASP | RAS Pulse Width (Fast Page Mode)               | 80             | 200,000 | 100          | 200,000           | ns           |         |

| <sup>t</sup> RSH  | RAS Hold Time                                  | 20             | -       | 25           | -                 | ns           |         |

| <sup>t</sup> CSH  | CAS Hold Time                                  | 80             | -       | 100          | -                 | ns           |         |

| <sup>t</sup> RHCP | CAS Precharge to RAS Hold Time                 | 45             | -       | 55           | -                 | ns           |         |

| <sup>t</sup> CAS  | CAS Pulse Width                                | 20             | 10,000  | 25           | 10,000            | ns           |         |

| <sup>t</sup> RCD  | RAS to CAS Delay Time                          | 20             | 60      | 25           | 75                | ns           | 14      |

| <sup>t</sup> RAD  | RAS to Column Address Delay Time               | 15             | 40      | 20           | 50                | ns           | 15      |

| <sup>t</sup> CRP  | CAS to RAS Precharge Time                      | 5              | -       | 10           | -                 | ns           |         |

| <sup>t</sup> CP , | CAS Precharge Time                             | 10             | -       | 10           | -                 | ns           |         |

| <sup>t</sup> ASR  | Row Address Set-Up Time                        | 0              | -       | 0            | -                 | ns           |         |

| t <sub>RAH</sub>  | Row Address Hold Time                          | 10             | -       | 15           | -                 | ns           |         |

| tASC              | Column Address Set-Up Time                     | 0              | -       | 0            | -                 | ns           |         |

| <sup>t</sup> CAH  | Column Address Hold Time                       | 15             | -       | 20           | -                 | ns           |         |

| tar               | Column Address Hold Time referenced to RAS     | 60             | -       | 75           | -                 | ns           |         |

| <sup>t</sup> RAL  | Column Address to RAS Lead Time                | 40             | -       | 50           | -                 | ns           |         |

| tRCS              | Read Command Set-Up Time                       | 0              | -       | 0            | -                 | ns           |         |

| <sup>t</sup> RCH  | Read Command Hold Time                         | 0              | -       | 0            | -                 | ns           | 11      |

| tRRH              | Read Command Hold Time referenced to RAS       | 0              | -       | 0            | -                 | ns           | 11      |

| <sup>t</sup> WCH  | Write Command Hold Time                        | 15             | -       | 20           | -                 | ns           |         |

|                   |                                                |                |         |              |                   |              |         |

# TC514100J/Z-80 TC514100J/Z-10

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

| SYMBOL            | PARAMETER                                                 | TC5141<br>-8 |      | TC5141<br>-1    |      | UNITS | NOTES |

|-------------------|-----------------------------------------------------------|--------------|------|-----------------|------|-------|-------|

|                   |                                                           | MIN.         | MAX. | MIN.            | MAX. |       |       |

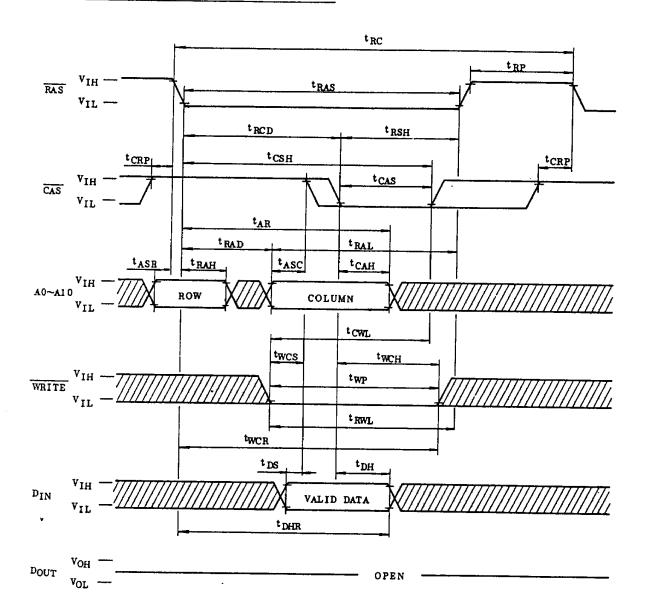

| <sup>t</sup> WCR  | Write Command Hold Time referenced to RAS                 | 60           | ~    | 75              | _    | ns    |       |

| twp               | Write Command Pulse Width                                 | 15           | _    | 20              | -    | ns    |       |

| tRWL              | Write Command to RAS Lead Time                            | 20           | -    | · 25            | -    | ns    |       |

| t CWL             | Write Command to CAS Lead Time                            | 20           | -    | 25              | -    | ns    |       |

| tDS               | Ďata Set-Up Time                                          | 0            | -    | 0               | -    | ns    | 12    |

| tDH               | Data Hold Time                                            | 15           | ı    | 20              | -    | ns    | 12    |

| t <sub>DHR</sub>  | Data Hold Time referenced to RAS                          | 60           | -    | 75              | -    | ns    |       |

| tREF              | Refresh Period                                            | _            | 16   | -               | 16   | ms    |       |

| twcs              | Write Command Set-Up Time                                 | 0            | -    | 0               | -    | ns    | 13    |

| t CWD             | CAS to WRITE Delay Time                                   | 20           | _    | <sup>-</sup> 25 | _    | ns    | 13    |

| tRWD              | RAS to WRITE Delay Time                                   | 80           | -    | 100             | -    | ns    | 13    |

| t <sub>AWD</sub>  | Column Address to WRITE Delay Time                        | 40           | -    | 50              | -    | ns    | 13    |

| <sup>t</sup> CPWD | CAS Precharge to WRITE Delay Time (Fast Page Mode)        | 45           | -    | 55              | _    | ns    | 13    |

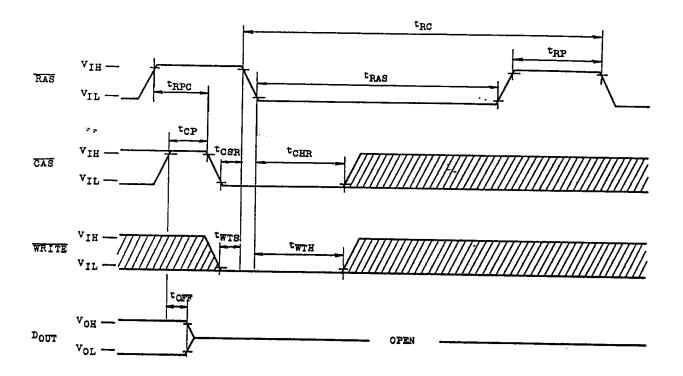

| tcsr              | CAS Set-Up Time (CAS before RAS Cycle)                    | 5            | -    | 5               | -    | ns    |       |

| t <sub>CHR</sub>  | CAS Hold Time (CAS before RAS Cycle)                      | 15           | -    | 20              | _    | ns    |       |

| <sup>t</sup> RPC  | RAS to CAS Precharge Time                                 | 0            | -    | 0               | _    | ns    |       |

| <sup>t</sup> CPT  | CAS Precharge Time<br>(CAS before RAS Counter Test Cycle) | 40           | -    | 50              | -    | ns    |       |

| twis              | Write Command Set-Up Time(Test Mode In)                   | 10           | -    | 10              | _    | ns    |       |

| tWTH              | Write Command Hold Time (Test Mode In)                    | 10           | -    | 10              | _    | ns    |       |

| t <sub>WRP</sub>  | WRITE to RAS Precharge Time (CAS before RAS Cycle)        | 10           | _    | 10              | -    | ns    |       |

| t <sub>WRH</sub>  | WRITE to RAS Hold Time<br>(CAS before RAS Cycle)          | 10           | _    | 10              | -    | ns    |       |

### ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS IN THE TEST MODE

$(V_{CC}=5V\pm10\%, Ta=0~70^{\circ}C)$  (Notes 6, 7, 8)

| SYMBOL            | PARAMETER                        | I    | TC514100J/Z<br>-80 |      | TC514100J/Z<br>-10 |    | NOTES   |

|-------------------|----------------------------------|------|--------------------|------|--------------------|----|---------|

|                   |                                  | MIN. | MAX.               | MIN. | MAX.               |    | 1       |

| <sup>t</sup> RC   | Random Read or Write Cycle Time  | 155  | -                  | 185  | -                  | ns |         |

| t PC              | Fast Page Mode Cycle Time        | 55   | -                  | 65   | -                  | ns |         |

| tRAC              | Access Time from RAS             | -    | 85                 | -    | 105                | ns | 9,14,15 |

| <sup>t</sup> CAC  | Access Time from CAS             | -    | 25                 | -    | 30                 | ns | 9,14    |

| tAA               | Access Time from Column Address  | -    | 45                 | ·-   | 55                 | ns | 9,15    |

| <sup>t</sup> CPA  | Access Time from CAS Precharge   | -    | 50                 | -    | 60                 | ns | 9       |

| <sup>t</sup> RAS  | RAS Pulse Width                  | 85   | 10,000             | 105  | 10,000             | ns |         |

| t <sub>RASP</sub> | RAS Pulse Width (Fast Page Mode) | 85   | 200,000            | 105  | 200,000            | ns |         |

| <sup>t</sup> RSH  | RAS Hold Time                    | 25   | -                  | 30   | -                  | ns |         |

| t <sub>CSH</sub>  | CAS Hold Time                    | 85   | -                  | 105  | -                  | ns |         |

| tRHCP             | CAS Precharge to RAS Hold Time   | 50   | -                  | 60   | -                  | ns |         |

| <sup>t</sup> CAS  | CAS Pulse Width                  | 25   | 10,000             | 30   | 10,000             | ns |         |

| tRAL              | Column Address to RAS Lead Time  | 45   | _                  | 55   | _                  | ns |         |

### CAPACITANCE (V<sub>CC</sub>=5V±10%, f=1MHz, Ta=0~70°C)

| SYMBOL          | PARAMETER                                    | MIN. | MAX. | UNIT |

|-----------------|----------------------------------------------|------|------|------|

| C <sub>I1</sub> | Input Capacitance (AO~A10, D <sub>IN</sub> ) | -    | 5    | pF   |

| C <sub>I2</sub> | Input Capacitance (RAS, CAS, WRITE)          | -    | 7    | pF   |

| С0              | Output Capacitance (D <sub>OUT</sub> )       | -    | 7    | pF   |

#### ·NOTES:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

- 2. All voltages are referenced to VSS.

- 3. ICC1, ICC3, ICC4, ICC6 depend on cycle rate.

- 4.  $I_{\text{CC1}}$ ,  $I_{\text{CC4}}$  depend on output loading. Specified values are obtained with the output open.

- 5. Column address can be changed once or less while RAS=VIL and CAS=VIH.

- 6. An initial pause of 200µs is required after power-up followed by 8 RAS only refresh cycles before proper device operation is achieved. In case of using internal refresh counter, a minimum of 8 CAS before RAS refresh cycles instead of 8 RAS only refresh cycles are required.

- 7. AC measurements assume  $t_T$ =5ns.

- 8.  $V_{\rm IH}({\rm min.})$  and  $V_{\rm IL}({\rm max.})$  are reference levels for measuring timing of input signals. Also, transition times are measured between  $V_{\rm IH}$  and  $V_{\rm IL}$ .

- 9. Measured with a load equivalent to 2 TTL loads and 100pF.

- 10. t<sub>OFF</sub>(max.) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- ll. Either  $t_{\mbox{RCH}}$  or  $t_{\mbox{RRH}}$  must be satisfied for a read cycle.

- 12. These parameters are referenced to CAS leading edge in early write cycles and to WRITE leading edge in read-modify-write.cycles.

- 13. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>CPWD</sub> are not restrictive operating parameters. They are included in the data sheet at electrical characteristics only. If t<sub>WCS</sub>≥t<sub>WCS</sub> (min.), the cycle is an early write cycle and data out pin will remain open circuit (high impedance) through the entire cycle; If t<sub>RWD</sub>≥t<sub>RWD</sub> (min.), t<sub>CWD</sub>≥t<sub>CWD</sub>(min.), t<sub>AWD</sub>≥t<sub>AWD</sub> (min.) and t<sub>CPWD</sub>≥t<sub>CPWD</sub> (min.) (Fast Page Mode), the cycle is a read-modify-write cycle and the data out will contain data read from the selected cell: If neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- 14. Operation within the  $t_{RCD}(max.)$  limit insures that  $t_{RAC}(max.)$  can be met.  $t_{RCD}(max.)$  is specified as a reference point only: If  $t_{RCD}$  is greater than the specified  $t_{RCD}(max.)$  limit, then access time is controlled by  $t_{CAC}$ .

- 15. Operation within the  $t_{RAD}$  (max.) limit insures that  $t_{RAC}$  (max.) can be met.  $t_{RAD}$  (max.) is specified as a reference point only: If  $t_{RAD}$  is greater than the specified  $t_{RAD}$  (max.) limit, then access time is controlled by  $t_{AA}$ .

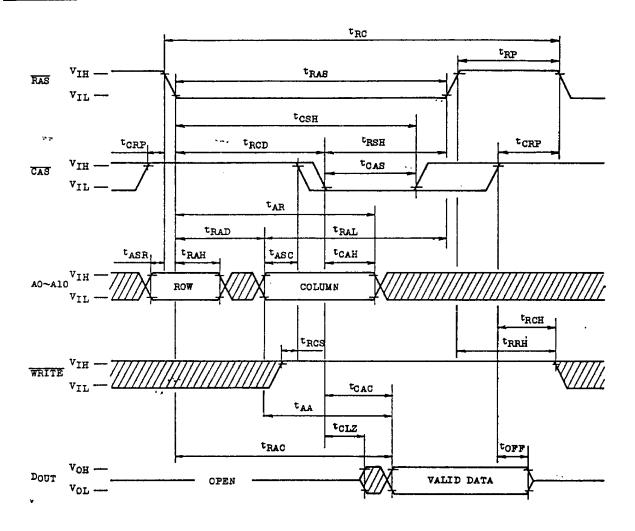

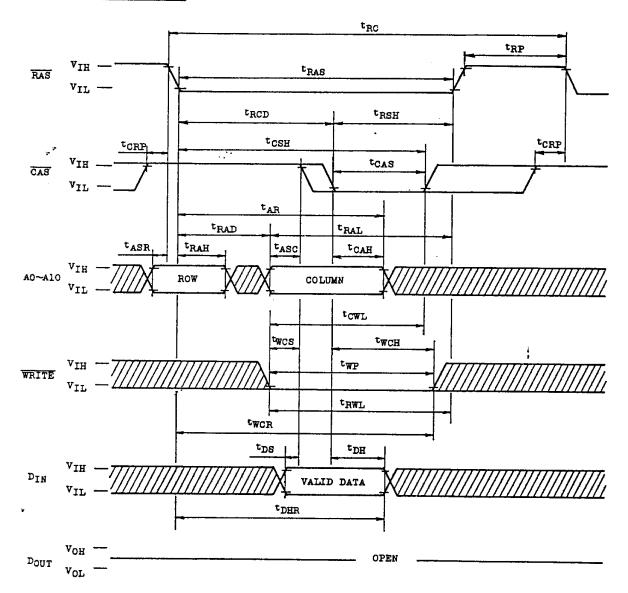

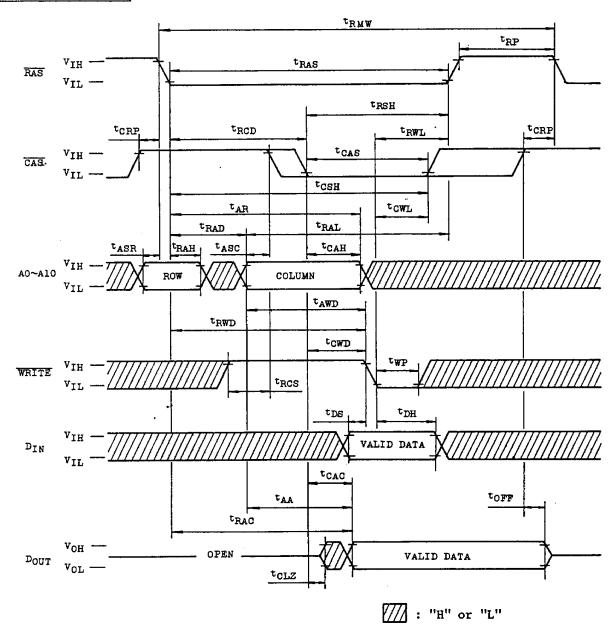

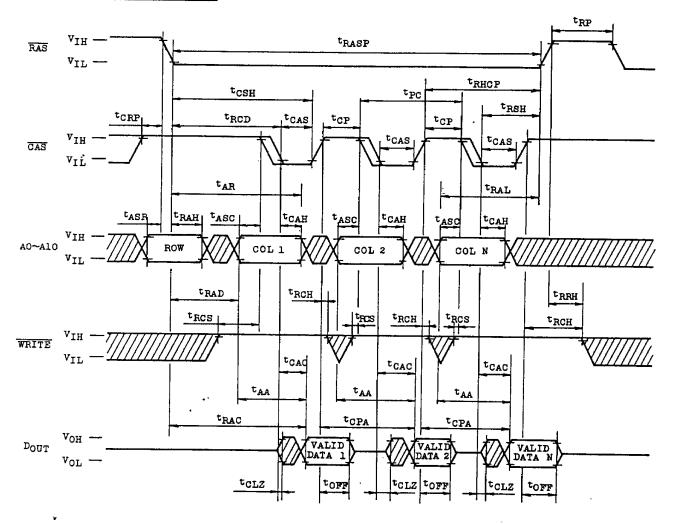

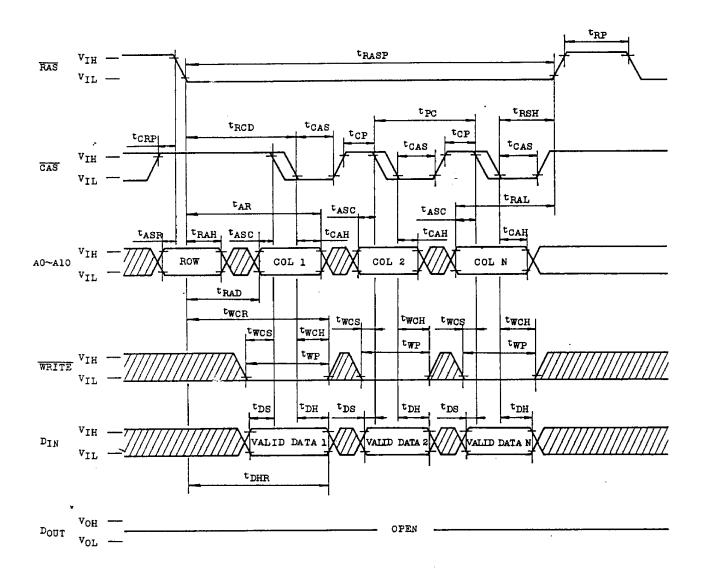

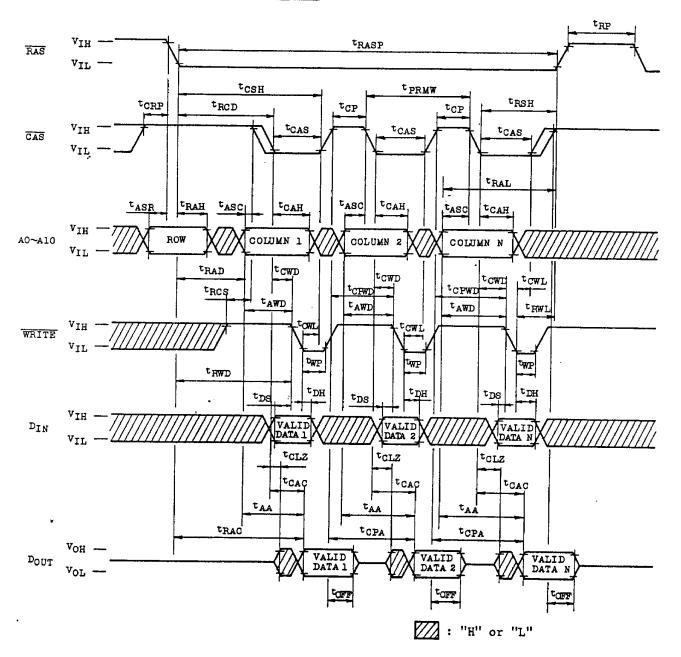

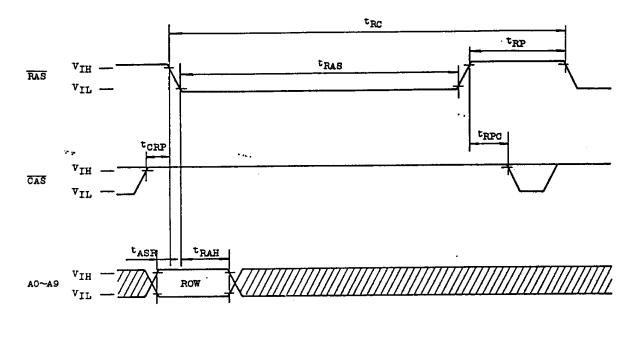

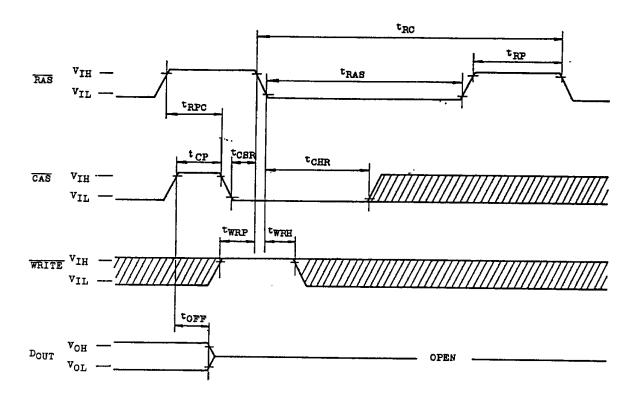

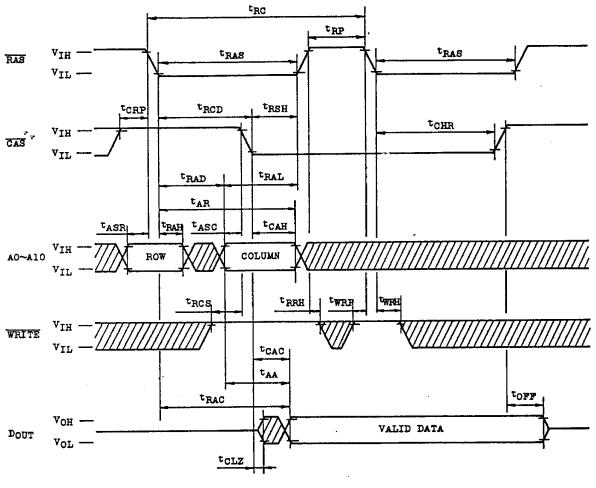

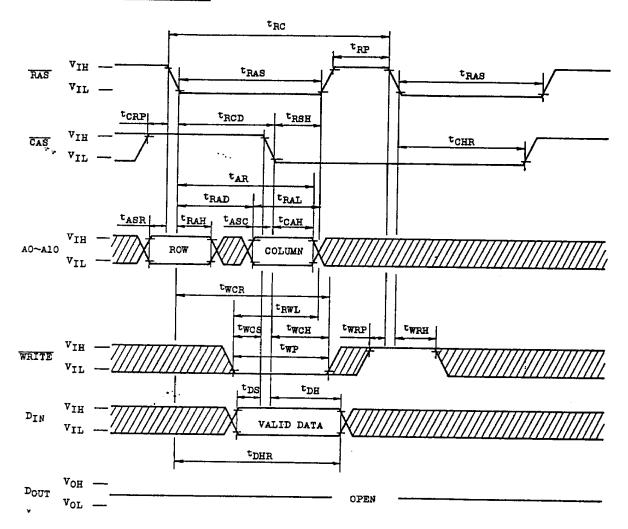

### TIMING WAVEFORMS

## READ CYCLE

## WRITE CYCLE (EARLY WRITE)

### READ-MODIFY-WRITE CYCLE

#### FAST PAGE MODE READ CYCLE

"H" or "L"

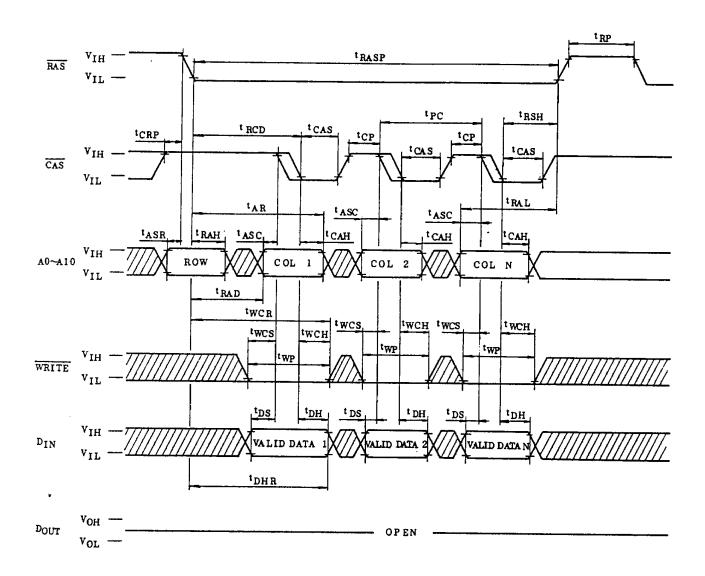

#### FAST PAGE MODE WRITE CYCLE (EARLY WRITE)

## FAST PAGE MODE READ-MODIFY-WRITE CYCLE

## RAS ONLY REFRESH CYCLE

|      | $v_{OH}$ |      |  |

|------|----------|------|--|

| DOUT | Vor      | OPEN |  |

: "H" or "L"

NOTE: WRITE="H" or "L", AlO="H" or "L"

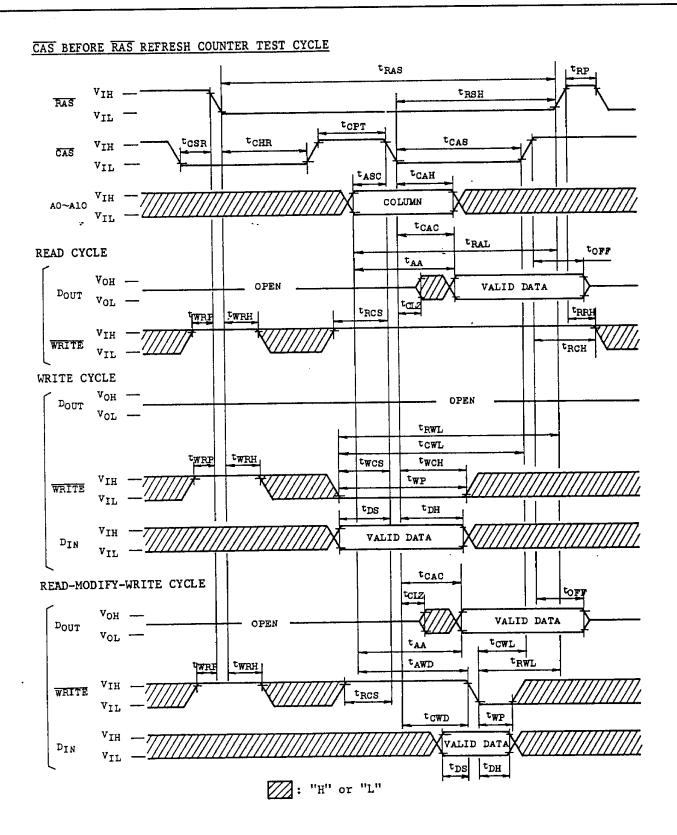

# CAS BEFORE RAS REFRESH CYCLE

NOTE: A0 ~ A10="H" or "L"

## HIDDEN REFRESH CYCLE (READ)

: "H" or "L"

## HIDDEN REFRESH CYCLE (WRITE)

: "H" or "L"

# WRITE, CAS BEFORE RAS REFRESH CYCLE

NOTE: D<sub>IN</sub>, A0 ~ A10: "H" or "L"

## READ CYCLE IN THE TEST MODE

"H" or "L"

# WRITE CYCLE (EARLY WRITE) IN THE TEST MODE

[]]: "H" or "L"

# FAST PAGE MODE READ CYCLE IN THE TEST MODE

: "H" or "L"

# FAST PAGE MODE WRITE CYCLE (EARLY WRITE) IN THE TEST MODE

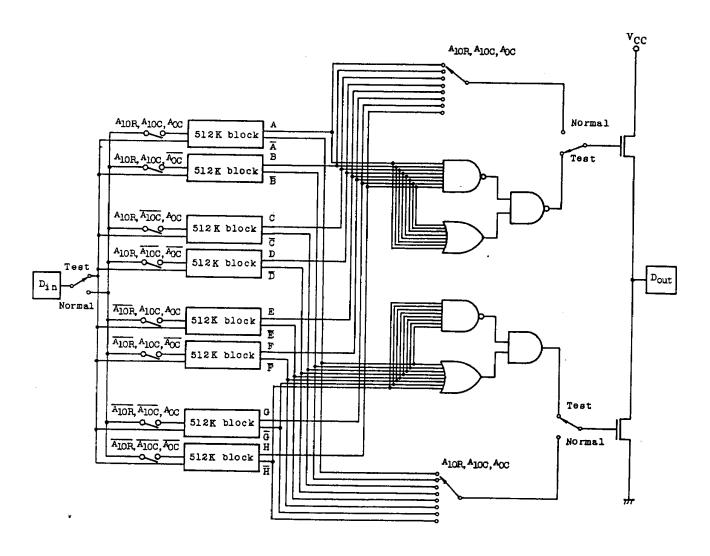

#### TEST MODE

The TC514100J/Z is the RAM organized 4,194,304 words by 1 bit, it is internally organized 524,288 words by 8 bits. In "Test Mode", data are written into 8 secotrs in parallel and retrieved the same way.  $A_{10R}$ ,  $A_{10C}$  and  $A_{0C}$  are not used. If, upon reading, all bits are equal (all "1"s or "0"s), the data output pin indicates a "1". If any of the bits differed, the data output pin would indicate a "0". Fig. 1 shows the block diagram of TC514100J/Z. In "Test Mode", the 4M DRAM can be tested as if it were a 512K DRAM.

"WRITE, CAS Before RAS Refresh Cycle" puts the device into "Test Mode".

And "CAS Before RAS Refresh Cycel" or "RAS Only Refresh Cycle" puts it back into "Normal Mode". In the Test Mode, "WRITE, CAS Before RAS Refresh Cycle" performs the refresh operation with the internal refresh address counter. The "Test Mode" function reduces test times (1/8 in case of N test pattern).

## BLOCK DIAGRAM IN THE TEST MODE

Fig. 1