D2942, OCTOBER 1986-REVISED JUNE 1990

- 2-A Output Current Capability per Full-H Driver

- Wide Range of Output Supply Voltage . . . 5 V to 46 V

- Separate Input-Logic Supply Voltage

- Thermal Shutdown

- Internal Electrostatic Discharge Protection

- High Noise Immunity

- Functional Replacement for SGS L298

#### description

The L298 is a dual high-current full-H driver designed to provide bidirectional drive currents of up to two amperes at voltages from 5 V to 46 V. It is designed to drive inductive loads such as relays, solenoids, dc motors, stepping motors, and other high-current or high-voltage loads in positive-supply applications. All inputs are TTL compatible. Each output (Y) is a complete totempole drive with a Darlington transistor sink and a psuedo-Darlington source. Each full-H driver is enabled separately. Outputs 1Y1 and 1Y2 are enabled by 1EN and outputs 2Y1 and 2Y2 are enabled by 2EN. When an EN input is high, the associated channels are active. When an EN input is low, the associated channels are off (i.e., in the high-impedance state).

Each half of the device forms a full-H reversible driver suitable for solenoid or motor applications. The current in each full-H driver can be monitored by connecting a resistor between the sense output terminal 1E and ground and another resistor between sense output terminal 2E and ground.

External high-speed output-clamp diodes should be used for inductive transient suppression. To minimize device power dissipation, a VCC1 supply voltage, separate from VCC2, is provided for the logic inputs.

The L298 is designed for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

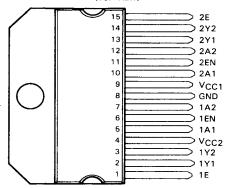

# (TOP VIEW)

The tab is electrically connected to pin 8.

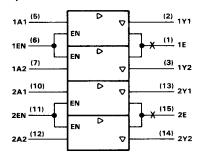

### logic symbol†

$<sup>^\</sup>dagger$  This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

### FUNCTION TABLE (EACH CHANNEL)

| INPL | JTS‡ | OUTPUT |  |  |

|------|------|--------|--|--|

| Α    | EN   | Y      |  |  |

| Н    | Н    | н      |  |  |

| L    | Н    | L      |  |  |

| ×    | Ł    | z      |  |  |

<sup>&</sup>lt;sup>‡</sup>In the thermal shutdown mode, the outputs are in the high-impedance state regardless of the input levels.

H = high-level

L = low-level

X = irrelevant

Z = high-impedance (off)

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1990, Texas Instruments Incorporated

4-15

### logic diagram (positive logic) V<sub>CC2</sub> (2) (3) (4) (13) (14)V<sub>CC1</sub>(9) 1A1<sup>(5)</sup> (12) 2A2 (10) 2A1 1A2<sup>(7)</sup> (11) 2EN 1EN (6) |(1) 1E (8) (15)

### absolute maximum ratings over operating temperature range (unless otherwise noted)

| Logic supply voltage, VCC1, (see Note 1) 7 V                                    |

|---------------------------------------------------------------------------------|

| Output supply voltage, VCC2 50 V                                                |

| Input voltage range at A or EN, VI                                              |

|                                                                                 |

| Output voltage range, VO                                                        |

| Emitter terminal (1E and 2E) voltage range                                      |

| Emitter terminal (1E and 2E) voltage (nonrepetitive, $t_W \le 50 \mu s$ )       |

| Peak output current, IOM, (nonrepetitive, t <sub>W</sub> ≤ 0.1 ms)              |

| (repetitive, t <sub>W</sub> ≤ 10 ms, duty cycle ≤ 80%) ± 2.5 A                  |

| Continuous output current, IO                                                   |

| Peak combined output current for each full-H driver (see Note 2)                |

| (nonrepetitive, $t_W \le 0.1 \text{ ms}$ ) ±3 A                                 |

| (repetitive, $t_W \le 10$ ms, duty cycle $\le 80\%$ ) $\pm 2.5$ A               |

| Continuous combined output current for each full-H driver (see Note 2) 3.575 W  |

| Continuous dissipation at (or below) 25 °C free-air temperature (see Note 3)    |

| Continuous dissipation at (or below) 75 °C case temperature (see Note 3) 25 W   |

| Operating free-air, case, or virtual junction temperature range 40 °C to 150 °C |

| Storage temperature range                                                       |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                    |

2E

NOTES: 1. All voltage values are with respect to the network ground terminal, unless otherwise noted.

- 2. Combined output current applies to each of the two full-H drivers individually. This current is the sum of the currents at outputs 1Y1 and 1Y2 for full-H driver 1 and the sum of the currents at outputs 2Y1 and 2Y2 for full-H driver 2. The full-H drivers may carry the rated combined current simultaneously.

- 3. For operation above 25 °C free-air temperature, derate linearly at the rate of 28.6 mW/ °C. For operation above 75 °C case temperature, derate linearly at the rate of 333 mW/°C. Due to variations in individual device electrical characteristics and thermal resistance, the built-in thermal overload protection may be activated at power levels slightly above or below the rated dissipation.

# recommended operating conditions

|                                                                  |    | MIN               | MAX                    | UNIT |

|------------------------------------------------------------------|----|-------------------|------------------------|------|

| Logic supply voltage, VCC1                                       |    | 4.5               | 7                      | V    |

| Output supply voltage, VCC2                                      |    | 5                 | 46                     | V    |

| Output supply voltage, CC2                                       |    | ~0.5 <sup>†</sup> | 2                      |      |

| Emitter terminal (1E or 2E) voltage, V <sub>E</sub> (see Note 4) |    |                   | V <sub>CC1</sub> - 3.5 | V    |

| Emitter terminal (TE of ZE) voltage, VE (Sec Note 4)             | İ  |                   | V <sub>CC2</sub> - 4   |      |

|                                                                  |    | 2.3               | V <sub>CC1</sub>       |      |

|                                                                  | A  |                   | V <sub>CC2</sub> - 2.5 | V    |

| High-level input voltage, VIH (see Note 4)                       | EN | 2.3               | 7                      |      |

|                                                                  |    |                   | V <sub>CC1</sub>       |      |

| Low-level input voltage at A or EN, VIL                          |    | -0.3 <sup>†</sup> | 1.5                    | V    |

| Output current, IO                                               |    |                   | ± 2                    | Α    |

| Commutation frequency, f <sub>C</sub>                            |    |                   | 40                     | kHz  |

| Operating free-air temperature, TA                               |    | 0                 | 70                     | °C   |

<sup>&</sup>lt;sup>†</sup>The algebraic convention, in which the least positive (most negative) designated minimum, is used in this data sheet for emitter terminal voltage and logic voltage levels.

# electrical characteristics, V<sub>CC1</sub> = 5 V, V<sub>CC2</sub> = 42 V, V<sub>E</sub> = 0, T<sub>J</sub> = 25 °C (unless otherwise noted)

| PARAMETER                                |                         | TEST CONDITIONS                                             |                                                          | MIN                                         | TYP    | MAX                  | UNIT                 |    |  |

|------------------------------------------|-------------------------|-------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------|--------|----------------------|----------------------|----|--|

| VOH High-level output voltage            |                         | 1 <sub>OH</sub> = -1 A                                      |                                                          | V <sub>CC2</sub> -1.8 V <sub>CC</sub>       |        |                      |                      |    |  |

|                                          |                         |                                                             |                                                          | V <sub>CC2</sub> -2.8 V <sub>CC2</sub> -1.8 |        |                      |                      |    |  |

| V <sub>OL</sub> Low-level output voltage |                         | I <sub>OL</sub> = 1 A                                       |                                                          | \                                           | /E+1.2 | V <sub>E</sub> + 1.8 | V                    |    |  |

|                                          |                         |                                                             | I <sub>OL</sub> = 2 A                                    |                                             |        | /E + 1.7             | V <sub>E</sub> + 2.6 |    |  |

| Total source plus sink                   |                         |                                                             |                                                          | 1 A lou = 1 A                               |        | 2.4                  | 3.4                  | V  |  |

| $V_{drop}$                               | output voltage drop     |                                                             | I <sub>OH</sub> = -2 A, I <sub>OL</sub> = 2 A See Note 5 |                                             |        | 3.5                  | 5.2                  |    |  |

| I <sub>IH</sub> High-level input current | ľΑ                      | V <sub>I</sub> = V <sub>I</sub> H                           |                                                          |                                             | 30     | 100                  | μΑ                   |    |  |

|                                          | EN                      | V <sub>I</sub> = V <sub>IH</sub> ≤ V <sub>CC1</sub> - 0.6 V |                                                          |                                             | 30     | 100                  |                      |    |  |

| Iμ                                       | Low-level input current | <del></del>                                                 | V <sub>I</sub> = 0 to 1.5 V                              |                                             |        |                      | 10                   | μΑ |  |

| 'IL                                      | Egw-level input current |                                                             | <del>                                     </del>         | All outputs at high level                   |        | 7 ·                  | 12                   |    |  |

| ICC1 Logic supply curre                  | Logic supply current    | current I <sub>O</sub> = 0                                  | 10 = 0                                                   | All outputs at low level                    |        | 24                   | 32                   | mA |  |

|                                          | Logic supply contain    |                                                             |                                                          | All outputs at high impedance               |        | 4                    | 6                    |    |  |

|                                          |                         |                                                             |                                                          | All outputs at high level                   |        | 38                   | 50                   |    |  |

| loon Ou                                  | Output supply current   | Output supply current                                       |                                                          | All outputs at low level                    |        | 13                   | 20                   | mA |  |

| CC2                                      | Cotpat supply sollions  |                                                             | 10 = 0                                                   | All outputs at high impedance               |        |                      | 2                    | 1  |  |

NOTE 5. The  $V_{drop}$  specification applies for  $I_{OH}$  and  $I_{OL}$  applied simultaneously to different output channels.  $V_{drop} = V_{CC2} - V_{OH} + V_{OL} - V_{E}$

NOTE 4: For optimum device performance, the maximum recommended voltage at any A input is 2.5 V lower than V<sub>CC2</sub>, the maximum recommended voltage at any EN input is V<sub>CC1</sub>, and the maximum recommended voltage at any emitter terminal is 3.5 V lower than V<sub>CC1</sub> and 4 V lower than V<sub>CC2</sub>.

# L298 DUAL FULL-H DRIVER

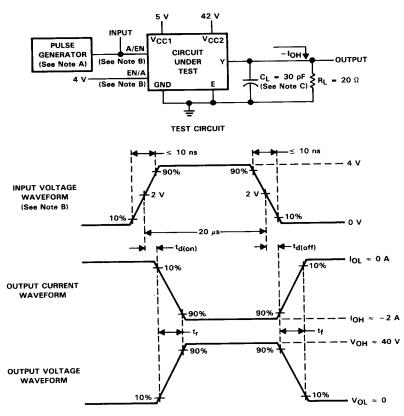

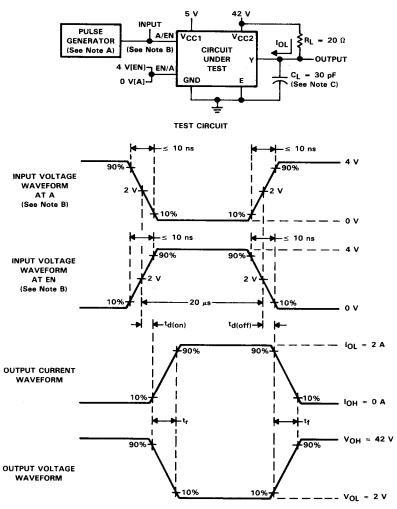

# switching characteristics, $V_{CC1} = 5 \text{ V}$ , $V_{CC2} = 42 \text{ V}$ , $V_E = 0$ , $T_A = 25 ^{\circ}\text{C}$

|                                                                  | PARAMETER                                        | TEST CONDITIONS         | MIN TYP MAX | UNIT |

|------------------------------------------------------------------|--------------------------------------------------|-------------------------|-------------|------|

| td(on)                                                           | Source current turn-on delay time from A input   |                         | 2.5         | μS   |

| td(off)                                                          | Source current turn-off delay time from A input  | <del></del>             | 1.7         | μS   |

| t <sub>r</sub> Source current rise time (turning on)             |                                                  | C <sub>L</sub> = 30 pF, | 0.4         | μS   |

| tf Source current fall time (turning off)                        |                                                  | See Figure 1            | 0.2         | μS   |

| td(on)                                                           | Source current turn-on delay time from EN input  |                         | 2.5         | μS   |

| td(off)                                                          | Source current turn-off delay time from EN input |                         | 1.7         | μs   |

| td(on)                                                           | Sink current turn-on delay time from A input     |                         | 1.5         | μs   |

| td(off)                                                          | Sink current turn-off delay time from A input    |                         | 0.7         | μS   |

| t <sub>r</sub> Sink current rise time (turning on)               |                                                  | C <sub>L</sub> = 30 pF, | 0.2         | μS   |

| t <sub>f</sub> Sink current fall time (turning off)              |                                                  | See Figure 2            | 0.2         | μs   |

| t <sub>d(on)</sub> Sink current turn-on delay time from EN input |                                                  |                         | 1.5         | μs   |

| <sup>t</sup> d(off)                                              | Sink current turn-off delay time from EN input   |                         | 0.7         | μS   |

## PARAMETER MEASUREMENT INFORMATION

**VOLTAGE AND CURRENT WAVEFORMS**

NOTES: A. The pulse generator has the following characteristics: PRR = 2 kHz,  $Z_0 = 50 \Omega$ .

B. EN is at 4 V if A is used as the switching input. A is at 4 V if EN is the switching input.

C. C<sub>L</sub> includes probe and jig capacitance.

FIGURE 1. SOURCE CURRENT SWITCHING TIMES FROM DATA AND ENABLE INPUTS

### PARAMETER MEASUREMENT INFORMATION

**VOLTAGE AND CURRENT WAVEFORMS**

NOTES: A. The pulse generator has the following characteristics: PRR = 2 kHz,  $\rm Z_{O}$  = 50  $\rm \Omega.$

- B. EN is at 4 V if A is used as the switching input. A is at 0 V if EN is the switching input.

- $\text{C.}\ \text{C}_{\text{L}}$  includes probe and jig capacitance.

FIGURE 2. SINK CURRENT SWITCHING TIMES FROM DATA AND ENABLE INPUTS

4-20

POST OFFICE BOX 655303 · DALLAS, TEXAS 75265

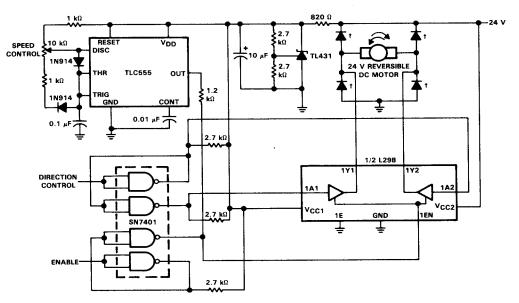

### APPLICATION INFORMATION

This circuit shows one half of an L298 used to provide full-H bridge drive for a 24-V 2-A dc motor. Speed control is achieved with a TLC555 timer. This provides variable duty cycle pulses to the EN input of the L298. In this configuration, the operating frequency is approximately 1.2 kHz. The duty cycle is adjustable from 10% to 90% to provide a wide range of motor speeds. The motor direction is determined by the logic level at the direction control input. The circuit may be enabled or disabled by the logic level at the EN input. A 5-V supply for the logic and timer circuit is provided by a TL431 shunt regulator. For circuit operation, refer to the function table.

#### **FUNCTION TABLE**

| ENABLE | DIRECTION CONTROL | 1Y1      | 1Y2      |  |

|--------|-------------------|----------|----------|--|

| Н      | н                 | source   | sink     |  |

| н      | L                 | sink     | source   |  |

| L      | ×                 | disabled | disabled |  |

X = don't care H = high level L = low level

<sup>†</sup>Diodes are 1N4934 or equivalent.

FIGURE 3. L298 AS BIDIRECTIONAL DC MOTOR DRIVER