## ADuC841 MicroConverter<sup>®</sup>, 12- Bit ADCs and DACs

### with Embedded Hi-Speed 62KB FLASH MCU

# **Preliminary Technical Data**

# ADuC841

#### FEATURES

ANALOG DEVICES

**PIN COMPATABLE** Upgrade to ADuC812/ADuC831 **INCREASED PERFORMANCE** Single Cycle 25MIPS 8052 core High Speed 400kSPS 12-Bit ADC **INCREASED MEMORY** 62Kbytes On-Chip Flash/EE Program Memory 4KBytes On-Chip Flash/EE Data Memory In circuit re-programmable Flash/EE, 100 Yr Retention, 100 Kcycles Endurance 2304 Bytes On-Chip Data RAM SMALLER PACKAGE Available in 8mm x 8mm Chip Scale Package Also available in 52 pin PQFP - pin compatable with ADuC812/ADuC831 ANALOG I/O 8-Channel, 400kSPS High Accuracy, 12-Bit ADC On-Chip, 20 ppm/°C Voltage Reference DMA Controller, High-Speed ADC-to-RAM capture Two 12-Bit Voltage Output DACs Dual Output PWM-ΣΔ DACs **On-Chip Temperature Monitor Function** 8051 Based Core 8051-Compatible Instruction Set (25 MHz Max) High performance Single Cycle Core\* 12 Interrupt Sources, Two Priority Levels Dual Data Pointers, Extended 11-bit Stack Pointer **On-Chip Peripherals** Time Interval Counter (TIC) UART, I2C and SPI® Serial I/O Watchdog Timer (WDT), Power Supply Monitor (PSM) Power Specified for 3 and 5 volt operation Normal: 25mA @ 5 V (Core CLK = 16MHz) Power-Down: 15µA @ 3V **Development Tools** Low Cost, comprehensive development system incorporating non-intrusive single pin emulation IDE based, assembly and C source debug **APPLICATIONS Optical Networking - Laser Power Control Basestation Systems** Precision Instrumentation, Smart Sensors **Transient Capture Systems DAS and Communications Systems** MicroConverter is a registered trademark of Analog Devices, Inc.

SPI is a registered trademark of Motorola Inc.

#### I2C is a registered trademark of Philips Inc.

$^{*}$  68% of insturctions completed in one or two clock cycles

REV. PrB

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### GENERAL DESCRIPTION

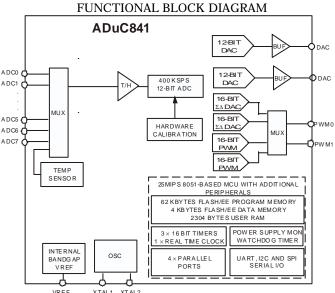

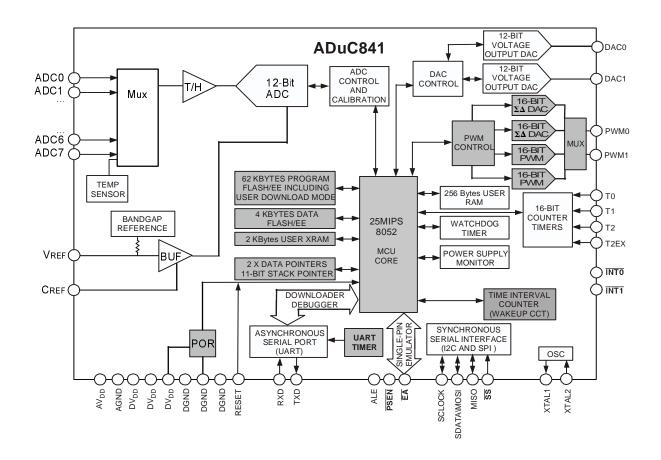

The ADuC841 is a complete smart transducer front-end, integrating a high-performance self calibrating multichannel ADC, dual DAC and an optimized single cycle 25MHz 8-bit MCU(8051 instruction set compatible) on a single chip.

The microcontroller is an optimized 8052 core offering up to 25 MIPS peak performance. 62 Kbytes of nonvolatile Flash/EE program memory are provided on-chip. 4 Kbytes of nonvolatile Flash/EE data memory, 256 bytes RAM and 2 KBytes of extended RAM are also integrated on-chip.

The ADuC841 also incorporates additional analog functionality with two 12-bit DACs, power supply monitor, and a bandgap reference. On-chip digital peripherals include two 16-bit  $\Sigma\Delta$  DACs, dual output 16-bit PWM, watchdog timer, time interval counter, three timers/counters, and three serial I/O ports (SPI, I2C and UART).

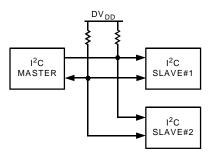

On the ADuC812 and ADuC831 the I2C and SPI interfaces shared some of the same pins. For backwards compatability this is also the case for the ADuC841. However, there is also the option to allow SPI operate separately on P3.3, P3.4 and P3.5 while I2C uses the standard pins. The I2C interface has also been enhanced to offer repeated start, general call and quad addressing.

On-chip factory firmware supports in-circuit serial download and debug modes (via UART), as well as single-pin emulation mode via the EA pin. A functional block diagram of the ADuC841 is shown above.

The part is specified for 3V and 5V operation. When operating from 5V the maximum operating frequency is 25MHz and when operating from 3V the maximum operating frequency is 16MHz.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2003

# $\label{eq:ADUC841-SPECIFICATIONS1} \begin{array}{l} (AV_{DD} = DV_{DD} = 2.7V \mbox{ to } 3.3V \mbox{ or } 4.5V \mbox{ to } 5.5V. \mbox{ } V_{REF} = 2.5 \mbox{ } V \mbox{ Internal Reference, MCLKIN} = 16 \mbox{ } MHz \mbox{ } All \mbox{ specifications } T_A = T_{MIN} \mbox{ to } T_{MAX}, \mbox{ unless otherwise noted.} \end{array}$

| Parameter                                                                                                                                                   | $V_{DD} = 5 V$                                                                            | $V_{DD} = 3 V$                                                                            | Unit                                    | Test Conditions/Comments                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| ADC CHANNEL SPECIFICATIONS                                                                                                                                  |                                                                                           |                                                                                           |                                         |                                                                                                                 |

| DC ACCURACY <sup>2,3</sup>                                                                                                                                  | 10                                                                                        | 10                                                                                        | Dite                                    | $f_{SAMPLE} = 147 \text{ kHz},$                                                                                 |

| Resolution<br>Integral Nonlinearity                                                                                                                         | $ \begin{array}{c c} 12 \\ \pm 1 \\ \pm 0.3 \end{array} $                                 | $     \begin{array}{c}       12 \\       \pm 1 \\       \pm 0.3     \end{array} $         | Bits<br>LSB max<br>LSB typ              | 2.5V Internal Reference                                                                                         |

| Differential Nonlinearity                                                                                                                                   | $\pm 0.3$<br>$\pm 0.9$<br>$\pm 0.25$                                                      | $\pm 0.3$<br>$\pm 0.9$<br>$\pm 0.25$                                                      | LSB typ<br>LSB max<br>LSB typ           | 2.5V Internal Reference                                                                                         |

| Integral Nonlinearity <sup>9</sup><br>Differential Nonlinearity <sup>9</sup><br>Code Distrbution                                                            | ±1.5<br>+1.5/-0.9<br>1                                                                    | ±1.5<br>+1.5/-0.9<br>1                                                                    | LSB max<br>LSB max<br>LSB typ           | 1V External Reference<br>1V External Reference<br>ADC Input is a DC Voltage                                     |

| CALIBRATED ENDPOINT ERRORS <sup>4.5</sup><br>Offset Error<br>Offset Error Match<br>Gain Error<br>Gain Error Match                                           |                                                                                           |                                                                                           | LSB max<br>LSB typ<br>LSB max<br>dB typ |                                                                                                                 |

| DYNAMIC PERFORMANCE                                                                                                                                         |                                                                                           |                                                                                           |                                         | $f_{IN} = 10 \text{ kHz}$ Sine Wave<br>$f_{SAMPLE} = 147 \text{ kHz}$                                           |

| Signal-to-Noise Ratio (SNR) <sup>6</sup><br>Total Harmonic Distortion (THD)<br>Peak Harmonic or Spurious Noise<br>Channel-to-Channel Crosstalk <sup>7</sup> | 71<br>-85<br>-85<br>-80                                                                   | 71<br>-85<br>-85<br>-80                                                                   | dB typ<br>dB typ<br>dB typ<br>dB typ    | $I_{SAMPLE} = 147 \text{ kmz}$                                                                                  |

| ANALOG INPUT<br>Input Voltage Ranges<br>Leakage Current<br>Input Capacitance                                                                                | 0 to V <sub>REF</sub><br>±1<br>32                                                         | 0 to V <sub>REF</sub><br>±1<br>32                                                         | Volts<br>μA max<br>pF typ               |                                                                                                                 |

| TEMPERATURE SENSOR <sup>8</sup><br>Voltage Output at 25°C<br>Voltage TC                                                                                     | 650<br>-2.0                                                                               | 650<br>-2.0                                                                               | mV typ<br>mV/°C typ                     |                                                                                                                 |

| Accuracy<br>Accuracy                                                                                                                                        | $     \pm 3 \\     \pm 1.5 $                                                              | $^{\pm 3}_{\pm 1.5}$                                                                      | °C typ<br>°C typ                        | Internal 2.5V V <sub>REF</sub><br>External 2.5V V <sub>REF</sub>                                                |

| DAC CHANNEL SPECIFICATIONS<br>Internal Buffer Enabled                                                                                                       |                                                                                           |                                                                                           |                                         | DAC Load to AGND<br>$R_L = 10k\Omega$ , $C_L = 100 \text{ pF}$                                                  |

| DC ACCURACY <sup>10</sup><br>Resolution<br>Relative Accuracy                                                                                                | 12<br>±3                                                                                  | 12<br>±3                                                                                  | Bits<br>LSB typ                         |                                                                                                                 |

| Differential Nonlinearity <sup>11</sup><br>Offset Error<br>Gain Error                                                                                       | $-1 \\ \pm 1/2 \\ \pm 50 \\ \pm 1$                                                        | $-1 \\ \pm 1/2 \\ \pm 50 \\ \pm 1$                                                        | LSB max<br>LSB typ<br>mV max<br>% max   | Guaranteed 12-Bit Monotonic<br>$V_{REF}$ Range<br>$AV_{DD}$ Range                                               |

| Gain Error Mismatch                                                                                                                                         | ±1<br>0.5                                                                                 | ±1<br>0.5                                                                                 | % typ<br>% typ                          | VREF Range<br>% of Full-Scale on DAC1                                                                           |

| ANALOG OUTPUTS<br>Voltage Range_0<br>Voltage Range_1<br>Output Impedance<br>I <sub>SINK</sub>                                                               | $\begin{array}{c} 0 \text{ to } V_{REF} \\ 0 \text{ to } V_{DD} \\ 0.5 \\ 50 \end{array}$ | $\begin{array}{c} 0 \text{ to } V_{REF} \\ 0 \text{ to } V_{DD} \\ 0.5 \\ 50 \end{array}$ | V typ<br>V typ<br>Ω typ<br>μA typ       | $\begin{array}{l} \text{DAC } V_{\text{REF}} = 2.5 V \\ \text{DAC } V_{\text{REF}} = V_{\text{DD}} \end{array}$ |

| DAC AC CHARACTERISTICS<br>Voltage Output Settling Time                                                                                                      | 15                                                                                        | 15                                                                                        | µs typ                                  | Full-Scale Settling Time to<br>Within 1/2 LSB of Final Value                                                    |

| Digital-to-Analog Glitch Energy                                                                                                                             | 10                                                                                        | 10                                                                                        | nV sec typ                              | 1 LSB Change at Major Carry                                                                                     |

| Parameter                                                               | $V_{DD} = 5 V$        | <b>V</b> <sub>DD</sub> = <b>3 V</b> | Unit         | Test Conditions/Comments                   |

|-------------------------------------------------------------------------|-----------------------|-------------------------------------|--------------|--------------------------------------------|

| DAC CHANNEL SPECIFICATIONS <sup>12,13</sup><br>Internal Buffer Disabled |                       |                                     |              |                                            |

| DC ACCURACY <sup>10</sup>                                               |                       |                                     |              |                                            |

| Resolution                                                              | 12                    | 12                                  | Bits         |                                            |

| Relative Accuracy                                                       | ±3                    | ±3                                  | LSB typ      |                                            |

| Differential Nonlinearity <sup>11</sup>                                 | -1                    | -1                                  | LSB max      | Guaranteed 12-Bit Monotonic                |

| Differential Politicality                                               | ±1/2                  | $\pm 1/2$                           | LSB typ      | Guaranteeu 12 Bit Wonotonie                |

| Offset Error                                                            | $\pm 1/2$<br>$\pm 10$ | $\pm 1/2$<br>$\pm 10$               | mV max       | V <sub>REF</sub> Range                     |

| Gain Error                                                              | $\pm 10$<br>$\pm 1$   | ±10<br>±1                           | % typ        | VREF Range                                 |

| Gain Error Mismatch                                                     | $ \frac{\pm 1}{0.5} $ | 0.5                                 |              | % of Full-Scale on DAC1                    |

|                                                                         | 0.5                   | 0.5                                 | % typ        | % OF Full-Scale Of DAC1                    |

| ANALOG OUTPUTS                                                          | 0.1 17                |                                     | <b>T</b> 7 / |                                            |

| Voltage Range_0                                                         | 0 to V <sub>REF</sub> | 0 to V <sub>REF</sub>               | V typ        | DAC $V_{REF} = 2.5V$                       |

| REFERENCE INPUT/OUTPUT                                                  |                       |                                     |              |                                            |

| REFERENCE OUPUT <sup>14</sup>                                           |                       |                                     |              |                                            |

| Output Voltage (V <sub>REF</sub> )                                      | 2.5                   | 2.5                                 | V            |                                            |

| Accuracy                                                                | $\pm 2.5$             | $\pm 2.5$                           | % max        | Of $V_{REF}$ measured at the $C_{REF}$ pin |

| Power Supply Rejection                                                  | 47                    | 57                                  | dB typ       | -                                          |

| Reference Temperature Coefficient                                       | $\pm 20$              | ±20                                 | ppm/°C typ   |                                            |

| Internal V <sub>REF</sub> Power-On Time                                 | 80                    | 80                                  | ms typ       |                                            |

| EXTERNAL REFERNCE INPUT <sup>15</sup>                                   |                       |                                     | 51           |                                            |

| Voltage Range $(V_{REF})^9$                                             | 0.1                   | 0.1                                 | V min        |                                            |

| Voltage Range (VREF)                                                    | V <sub>DD</sub>       | V <sub>DD</sub>                     | V max        |                                            |

| Input Impodence                                                         | 20                    | 20                                  |              |                                            |

| Input Impedance                                                         |                       |                                     | kΩ typ       | Internal Band Can Decelected are           |

| Input Leakage                                                           | 10                    | 10                                  | μA max       | Internal Band Gap Deselected via ADCCON1.6 |

|                                                                         |                       |                                     |              | ADCCON1.0                                  |

| POWER SUPPLY MONITOR (PSM)                                              |                       |                                     |              |                                            |

| $DV_{DD}$ Trip Point Selection Range                                    | 2.63                  |                                     | Vmin         | Four Trip Points Selectable in             |

| DVDD THP Tollit Selection Range                                         | 4.37                  |                                     | Vmax         | This Range Programmed via                  |

|                                                                         | 4.57                  |                                     | VIIIdX       | TPD1–0 in PSMCON                           |

| DV Dowen Supply Twin Doint                                              |                       |                                     |              |                                            |

| DV <sub>DD</sub> Power Supply Trip Point                                | 19 5                  |                                     | 0/ may       |                                            |

| Accuracy                                                                | ±3.5                  |                                     | % max        |                                            |

| WATCH DOG TIMER (WDT) <sup>9</sup>                                      |                       |                                     |              |                                            |

| Time-out Period                                                         | 0                     | 0                                   | ms min       | Nine Time-out Periods                      |

|                                                                         | 2000                  | 2000                                | ms max.      | Selectable in This Range                   |

| FLASH/EE MEMORY RELIABILITY                                             |                       |                                     |              |                                            |

| CHARACTERISTICS <sup>16</sup>                                           |                       |                                     |              |                                            |

| Endurance <sup>17</sup>                                                 | 100,000               | 100,000                             | Cycles min   |                                            |

| Data Retention <sup>18</sup>                                            | 100,000               | 100,000                             | Years min    |                                            |

|                                                                         | 100                   | 100                                 |              |                                            |

| DIGITAL INPUTS                                                          |                       |                                     |              |                                            |

| Input High Voltage (V <sub>INH</sub> )                                  | 2.4                   |                                     | V min        |                                            |

| Input Low Voltage (V <sub>INL</sub> )                                   | 0.8                   |                                     | V max        |                                            |

| Input Leakage Current (Port 0,1, EA)                                    | ±10                   |                                     | μA max       | $V_{\rm IN} = 0$ V or $V_{\rm DD}$         |

|                                                                         | ±1                    | ±1                                  | μA typ       | $V_{IN} = 0 V \text{ or } V_{DD}$          |

| Logic 1 Input Current                                                   |                       |                                     |              |                                            |

| (All Digital Inputs)                                                    | ±10                   |                                     | μA max       | $V_{IN} = V_{DD}$                          |

|                                                                         | ±1                    | ±1                                  | μA typ       | $V_{\rm IN} = V_{\rm DD}$                  |

| Logic 0 Input Current (Port 2, 3)                                       | -80                   |                                     | μA max       |                                            |

|                                                                         | -40                   | -40                                 | μA typ       | $V_{IL} = 0 V$                             |

| Logic 1-0 Transition Current (Port 2, 3)                                | -700                  |                                     | μA max       | $V_{IL} = 2 V$                             |

|                                                                         | -400                  | -400                                | μA typ       | $V_{IL} = 2 V$<br>$V_{IL} = 2 V$           |

| CRYSTAL OSCILLATOR                                                      |                       |                                     | , ,,         |                                            |

| Logic Inputs, XTAL1 Only                                                |                       |                                     |              |                                            |

| VINL, Input Low Voltage                                                 | 0.8                   | 0.4                                 | V typ        |                                            |

| VINE, Input High Voltage                                                | 3.5                   | 2.5                                 |              |                                            |

| viivii, iliput riigii voltage                                           | 3.5                   | 2.0                                 | V typ        |                                            |

# ADuC841–SPECIFICATIONS<sup>1</sup>

| Parameter                                                   | V <sub>DD</sub> =5V | V <sub>DD</sub> =3V | Units            | Test Conditions                                                      |

|-------------------------------------------------------------|---------------------|---------------------|------------------|----------------------------------------------------------------------|

| XTAL1 Input Capacitance                                     | 18                  | 18                  | pF typ           |                                                                      |

| XTAL2 Output Capacitance                                    | 18                  | 18                  | pF typ           |                                                                      |

| MCU Clock Rate                                              | 25                  | 16                  | MHz max          |                                                                      |

|                                                             | 20                  | 10                  | IVII IZ IIIdx    |                                                                      |

| DIGITAL OUTPUTS                                             |                     |                     |                  |                                                                      |

| Output High Voltage (V <sub>OH</sub> )                      | 2.4                 | 2.4                 | V min            | $V_{DD} = 4.5 V \text{ to } 5.5 V$                                   |

|                                                             | 1.0                 | 0.0                 | N7 to an         | $I_{\text{SOURCE}} = 80 \mu\text{A}$                                 |

|                                                             | 4.0                 | 2.6                 | V typ            | $V_{DD} = 2.7 \text{ V to } 3.3 \text{ V}$                           |

| Output Low Voltage (V)                                      |                     |                     |                  | $I_{SOURCE} = 20 \ \mu A$                                            |

| Output Low Voltage (V <sub>OL</sub> )<br>ALE, Ports 0 and 2 | 0.4                 | 0.4                 | V max            | $I_{SINK} = 1.6 \text{ mA}$                                          |

| ALE, FOITS 0 and 2                                          | 0.4                 | 0.4                 | V max<br>V typ   | $I_{SINK} = 1.6 \text{ mA}$<br>$I_{SINK} = 1.6 \text{ mA}$           |

| Port 3                                                      | 0.2                 | 0.2                 | Vuyp<br>Vmax     | $I_{SINK} = 4 \text{ mA}$                                            |

| SCLOCK/SDATA                                                | 0.4                 | 0.4                 | Vmax             | $I_{\text{SINK}} = 4 \text{ mA}$<br>$I_{\text{SINK}} = 8 \text{ mA}$ |

| JOLGORISDAIN                                                | 0.4                 | 0.4                 | VIIIdx           | ISINK – O III Y                                                      |

| Floating State Leakage Current                              | ±10                 | ±10                 | μA max           |                                                                      |

| 0                                                           | ±1                  | ±1                  | μA typ           |                                                                      |

| Floating State Output Capacitance                           | 10                  | 10                  | pF typ           |                                                                      |

| 0 <u> </u>                                                  |                     |                     | 1 71             |                                                                      |

| START UP TIME                                               |                     | 1                   |                  | Core CLK = 16MHz                                                     |

| At Power-On                                                 | 500                 | 500                 | ms typ           |                                                                      |

| From Idle Mode                                              | 100                 | 100                 | μs typ           |                                                                      |

| From Power-Down Mode                                        | 100                 | 100                 | μοτγμ            |                                                                      |

| Wakeup with INTO Interrupt                                  | 150                 | 400                 | ms typ           |                                                                      |

| Wakeup with SPI/I <sup>2</sup> C Interrupt                  | 150                 | 400                 | ms typ           |                                                                      |

| Wakeup with External RESET                                  | 150                 | 400                 | ms typ           |                                                                      |

| After External RESET in Normal Mode                         | 3                   | 3                   | ms typ           |                                                                      |

| After WDT Reset in Normal Mode                              | 3                   | 3                   | ms typ           | Controlled via WDCON SFR                                             |

|                                                             |                     | -                   | J F              |                                                                      |

| POWER REQUIREMENTS <sup>19,20</sup>                         |                     |                     |                  |                                                                      |

| Power Supply Voltages                                       |                     | 0.7                 | V                |                                                                      |

| AV <sub>DD</sub> / DV <sub>DD</sub> - AGND                  |                     | 2.7<br>3.3          | V min.<br>V max. | $AV_{DD} / DV_{DD} = 3V$ nom.                                        |

|                                                             | 4.5                 | 3.3                 | V max.<br>V min. | $\Delta V = 5V$ nom                                                  |

|                                                             | 4.5<br>5.5          |                     | V max.           | $AV_{DD} / DV_{DD} = 5V$ nom.                                        |

|                                                             | 0.0                 |                     | v max.           |                                                                      |

| Power Supply Currents Normal Mode                           |                     |                     |                  |                                                                      |

| $D_{VDD}$ Current <sup>9</sup>                              | 12                  | 6                   | mA typ           | Core CLK=8 MHz                                                       |

| A <sub>VDD</sub> Current <sup>9</sup>                       | 1.4                 | 1.4                 | mA max           |                                                                      |

| D <sub>VDD</sub> Current                                    | 25                  | n/a                 | mA max           | Core CLK=16 MHz                                                      |

|                                                             | 21                  | n/a                 | mA typ           |                                                                      |

| A <sub>VDD</sub> Current                                    | 1.4                 | n/a                 | mA max           |                                                                      |

|                                                             |                     |                     |                  |                                                                      |

| Power Supply Currents Idle Mode                             |                     |                     |                  |                                                                      |

| D <sub>VDD</sub> Current <sup>9</sup>                       | 5                   | 2.5                 | mA typ           | Core CLK=8 MHz                                                       |

| A <sub>VDD</sub> Current <sup>9</sup>                       | 0.11                | 0.11                | mA typ           |                                                                      |

| D <sub>VDD</sub> Current <sup>9</sup>                       | 11                  | n/a                 | mA max           | Core CLK=16 MHz                                                      |

| 6                                                           | 10                  | n/a                 | mA typ           |                                                                      |

| A <sub>VDD</sub> Current <sup>9</sup>                       | 0.11                | n/a                 | mA typ           |                                                                      |

|                                                             |                     |                     |                  |                                                                      |

| Power Supply Currents Power Down Mode                       | 0                   | 0.5                 |                  | For any Core CLK                                                     |

| A <sub>VDD</sub> Current                                    | 3                   | 2.5                 | uA typ           | TIMECON 1 0                                                          |

| D <sub>VDD</sub> Current                                    | 35                  | 15                  | uA max           | TIMECON.1=0                                                          |

|                                                             | 25                  | 12                  | uA typ           | TIMECON 1- 1                                                         |

|                                                             | 120                 | 120                 | uA typ           | TIMECON.1=1                                                          |

| Typical Additional Power Supply Currents                    |                     |                     |                  | AVDD = DVDD = 5V                                                     |

| PSM Peripheral                                              | 50                  |                     | uA typ           |                                                                      |

| ADC                                                         | 1.5                 |                     | mA typ           |                                                                      |

| DAC                                                         | 1.5                 |                     | uA typ           |                                                                      |

|                                                             | 100                 |                     | uriyp            |                                                                      |

NOTES

<sup>1</sup> Temperature Range -40°C to +85°C.

- <sup>2</sup> ADC Linearity is guaranteed during normal MicroConverter Core operation.

- <sup>3</sup> ADC LSB Size = Vref / 2^12 i.e for Internal Vref=2.5V, 1LSB = 610uV and for External Vref =1V, 1LSB = 244uV.

- <sup>4</sup> Offset and Gain Error and Offset and Gain Error Match are measured after factory calibration.

- <sup>5</sup> Based on external ADC system components the user may need to execute a system calibration to remove additional external channel errors and achieve these specifications.

- <sup>6</sup> SNR calculation includes distortion and noise components.

- <sup>7</sup> Channel to Channel Crosstalk is measured on adjacent channels.

- <sup>8</sup> The Temperature Monitor will give a measure of the die temperature directly, air temperature can be inferred from this result.

- <sup>9</sup> These numbers are not production tested but are guaranteed by Design and/or Characterization data on production release.

<sup>10</sup> DAC linearity is calculated using :

- reduced code range of 48 to 4095, 0 to Vref range.

- reduced code range of 48 to 3945, 0 to  $V_{\text{DD}}$  range.

- DAC Output Load = 10K Ohms and 100 pF.

- <sup>11</sup> DAC Differential NonLinearity specified on 0 to Vref and 0 to Vdd ranges

- <sup>12</sup> DAC specification for output impedance in the unbuffered case depends on DAC code

- <sup>13</sup> DAC specifications for Isink, voltage output settling time and digital-to-analog glitch engergy depend on external buffer implementation in unbuffered mode.

- <sup>14</sup> Measured with Vref and Cref pins decoupled with 0.1μF capacitors to graound. Power-up time for the Internal Reference will be determined by the value of the decoupling capacitor chosen for both the Vref and Cref pins.

- <sup>15</sup> When using an External Reference device, the internal bandgap reference input can be bypassed by setting the ADCCON1.6 bit. In this mode the Vref and Cref pins need to be shorted together for correct operation.

- <sup>16</sup>Flash/EE Memory Reliability Characteristics apply to both the Flash/EE program memory and the Flash/EE data memory.

- <sup>17</sup> Endurance is qualified to 100 Kcycles as per JEDEC Std. 22 method A117 and measured at -40°C, +25°C, and +85°C, typical endurance at 25°C is 700 Kcycles.

- <sup>18</sup> Retention lifetime equivalent at junction temperature (Tj) = 55°C as per JEDEC Std. 22 method A117. Retention lifetime based on an activation energy of 0.6eV will derate with junction temperature as shown in Figure 27 in the Flash/EE Memory description section of this data sheet.

- <sup>19</sup> Power Supply current consumption is measured in Normal, Idle, and Power-Down Modes under the following conditions: Normal Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Executing internal software loop.

- Idle Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Execution suspended in idle mode.

- Power-Down Mode: Reset = 0.4 V, All Port 0 pins = 0.4 V, All other digital I/O pins and Port 1 are open circuit, OSC off, TIC off.

- <sup>20</sup> D<sub>VDD</sub> power supply current will increase typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

Specifications subject to change without notice.

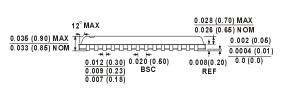

#### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = 25^{\circ}C)$ | C unless | otherwise | noted) |

|-----------------------|----------|-----------|--------|

|-----------------------|----------|-----------|--------|

| $AV_{DD}$ to $DV_{DD}$ $\ \ldots \ \ldots \ \ldots \ -0.3 \ V$ to +0.3 $V$                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| AGND to DGND                                                                                                                              |

| $DV_{DD}$ to DGND, $AV_{DD}$ to AGND $\hdots$ –0.3 V to +7 V                                                                              |

| Digital Input Voltage to DGND $\dots$ -0.3 V, DV <sub>DD</sub> + 0.3 V                                                                    |

| Digital Output Voltage to DGND $\dots$ -0.3 V, DV <sub>DD</sub> + 0.3 V                                                                   |

| $V_{\text{REF}}$ to AGND                                                                                                                  |

| Analog Inputs to AGND $\dots \dots \dots$ |

| Operating Temperature Range Industrial ADuC841BS                                                                                          |

| $-40^{\circ}$ C to $+85^{\circ}$ C                                                                                                        |

|                                                                                                                                           |

| Operating Temperature Range Industrial ADuC841BCP                                                                                         |

| Operating Temperature Range Industrial ADuC841BCP                                                                                         |

|                                                                                                                                           |

| Operating Temperature Range Industrial ADuC841BCP<br>40°C to +85°C                                                                        |

| Operating Temperature Range Industrial ADuC841BCP                                                                                         |

| Operating Temperature Range Industrial ADuC841BCP                                                                                         |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                      |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                      |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                      |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model      | Temperature    | Package                       | Package |

|------------|----------------|-------------------------------|---------|

|            | Range          | Description                   | Option  |

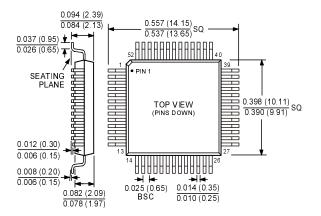

| ADuC841BS  | -40°C to +85°C | 52-Lead Plastic Quad Flatpack | S-52    |

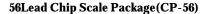

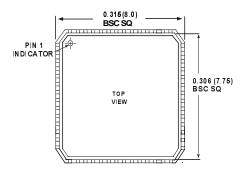

| ADuC841BCP | -40°C to +85°C | 56-Lead Chip Scale Package    | CP-56   |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADuC841 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

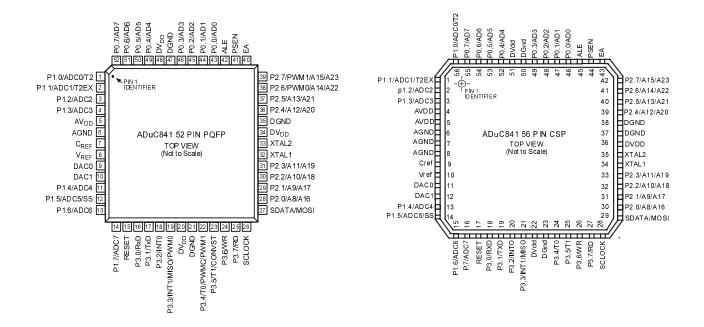

#### **PIN CONFIGURATION**

Figure 1 ADuC841 Block Diagram (Shaded areas are features not present on the ADuC812)

PIN FUNCTION DESCRIPTIONS

| Mnemonic              | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DV <sub>DD</sub>      | Р    | Digital Positive Supply Voltage, 3 V or 5 V Nominal                                                                                                                                                                                                                                                                                                                                                            |

| $AV_{DD}$             | Р    | Analog Positive Supply Voltage, 3 V or 5 V Nominal                                                                                                                                                                                                                                                                                                                                                             |

| C <sub>REF</sub>      | Ι    | Decoupling Input for On-Chip Reference. Connect 0.1 µF between this pin and AGND.                                                                                                                                                                                                                                                                                                                              |

| V <sub>REF</sub>      | I/O  | Reference Input/Output. This pin is connected to the internal reference through a series resistor and is the reference source for the analog-to-digital converter. The nominal internal reference voltage is 2.5 V and this appears at the pin. This pin can be overdriven by an external reference.                                                                                                           |

| AGND                  | G    | Analog Ground. Ground Reference point for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                |

| P1.0-P1.7             | Ι    | Port 1 is an 8-bit Input Port only. Unlike other Ports, Port 1 defaults to Analog Input Mode, to configure any of these Port Pins as a digital input, write a "0" to the port bit. Port 1 pins are multifunction and share the following functionality.                                                                                                                                                        |

| ADC0-ADC7             | Ι    | Analog Inputs. Eight single-ended analog inputs. Channel selection is via ADCCON2 SFR.                                                                                                                                                                                                                                                                                                                         |

| T2                    | Ι    | Timer 2 Digital Input. Input to Timer/Counter 2. When Enabled, Counter 2 is incremented in response to a 1 to 0 transition of the T2 input.                                                                                                                                                                                                                                                                    |

| T2EX                  | Ι    | Digital Input. Capture/Reload trigger for Counter 2 and also functions as an Up/Down control input for Counter 2.                                                                                                                                                                                                                                                                                              |

| SS                    | Ι    | Slave Select Input for the SPI Interface                                                                                                                                                                                                                                                                                                                                                                       |

| SDATA                 | I/O  | User Selectable, I <sup>2</sup> C-Compatible or SPI Data Input/Output Pin                                                                                                                                                                                                                                                                                                                                      |

| SCLOCK                | I/O  | Serial Clock Pin for I <sup>2</sup> C-Compatible or SPI Serial Interface Clock                                                                                                                                                                                                                                                                                                                                 |

| MOSI                  | I/O  | SPI Master Output/Slave Input Data I/O Pin for SPI Interface                                                                                                                                                                                                                                                                                                                                                   |

| MISO                  | I/O  | SPI Master Input/Slave Output Data I/O Pin for SPI Serial Interface                                                                                                                                                                                                                                                                                                                                            |

| DAC0                  | 0    | Voltage Output from DAC0                                                                                                                                                                                                                                                                                                                                                                                       |

| DAC1                  | 0    | Voltage Output from DAC1                                                                                                                                                                                                                                                                                                                                                                                       |

| RESET                 | Ι    | Digital Input. A high level on this pin for 24 master clock cycles while the oscillator is running resets the device.                                                                                                                                                                                                                                                                                          |

| P3.0-P3.7             | I/O  | Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state they can be used as inputs. As inputs Port 3 pins being pulled externally low will source current because of the internal pull-up resistors. Port 3 pins also contain various secondary functions which are described below.     |

| PWMC                  | Ι    | PWM Clock Input                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM0                  | 0    | PMW0 Voltage Output. PWM outputs can be configured to use ports 2.6 & 2.7 or 3.4 and 3.3                                                                                                                                                                                                                                                                                                                       |

| PWM1                  | 0    | PMW1 Voltage Ouput. See CFG831 Register for further Information.                                                                                                                                                                                                                                                                                                                                               |

| RxD                   | I/O  | Receiver Data Input (Asynchronous) or Data Input/Output (Synchronous) of Serial (UART) Port                                                                                                                                                                                                                                                                                                                    |

| TxD                   | 0    | Transmitter Data Output (Asynchronous) or Clock Output (Synchronous) of Serial (UART) Port                                                                                                                                                                                                                                                                                                                     |

| INT0                  | Ι    | Interrupt 0, programmable edge or level triggered Interrupt input, which can be programmed to one of two priority levels. This pin can also be used as a gate control input to Timer 0.                                                                                                                                                                                                                        |

| INT1                  | Ι    | Interrupt 1, programmable edge or level triggered Interrupt input, which can be programmed to one of two priority levels. This pin can also be used as a gate control input to Timer 1.                                                                                                                                                                                                                        |

| Т0                    | Ι    | Timer/Counter 0 Input                                                                                                                                                                                                                                                                                                                                                                                          |

| T1                    | Ι    | Timer/Counter 1 Input                                                                                                                                                                                                                                                                                                                                                                                          |

| CONVST                | Ι    | Active low Convert Start Logic input for the ADC block when the external Convert start function is enabled.<br>A low-to-high transition on this input puts the track/hold into its hold mode and starts conversion.                                                                                                                                                                                            |

| WR                    | 0    | Write Control Signal, Logic Output. Latches the data byte from Port 0 into the external data memory.                                                                                                                                                                                                                                                                                                           |

| RD                    | 0    | Read Control Signal, Logic Output. Enables the external data memory to Port 0.                                                                                                                                                                                                                                                                                                                                 |

| XTAL2                 | 0    | Output of the Inverting Oscillator Amplifier                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL1                 | Ι    | Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                |

| DGND                  | G    | Digital Ground. Ground reference point for the digital circuitry.                                                                                                                                                                                                                                                                                                                                              |

| P2.0-P2.7             | I/O  | Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that have 1s written to them are                                                                                                                                                                                                                                                                                                   |

| (A8–A15)<br>(A16–A23) |      | pulled high by the internal pull-up resistors, and in that state they can be used as inputs. As inputs Port 2 pins being pulled externally low will source current because of the internal pull-up resistors. Port 2 emits the high order address bytes during fetches from external program memory and middle and high order address bytes during accesses to the external 24-bit external data memory space. |

| PIN FUNCTION DESCRIPTION (continued) |      |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mnemonic                             | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PSEN                                 | 0    | Program Store Enable, Logic Output. This output is a control signal that enables the external program memory to the bus during external fetch operations. It is active every six oscillator periods except during external data memory accesses. This pin remains high during internal program execution. PSEN can also be used to enable serial download mode when pulled low through a resistor on power-up or RESET. |  |

| ALE                                  | 0    | Address Latch Enable, Logic Output. This output is used to latch the low byte (and page byte for 24-bit address space accesses) of the address into external memory during normal operation.                                                                                                                                                                                                                            |  |

| EA                                   | Ι    | External Access Enable, Logic Input. When held high, this input enables the device to fetch code from internal program memory locations 0000H to 1FFFH. When held low this input enables the device to fetch all instructions from external program memory. This pin should not be left float.                                                                                                                          |  |

| P0.7–P0.0<br>(A0–A7)                 | I/O  | Port 0 is an 8-Bit Open Drain Bidirectional I/O port. Port 0 pins that have 1s written to them float and in that state can be used as high impedance inputs. Port 0 is also the multiplexed low order address and data bus during accesses to external program or data memory. In this application it uses strong internal pull-ups when emitting 1s.                                                                   |  |

#### TERMINOLOGY ADC SPECIFICATIONS Integral Nonlinearity

This is the maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point 1/2 LSB below the first code transition and full scale, a point 1/2 LSB above the last code transition.

#### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Offset Error**

This is the deviation of the first code transition  $(0000 \dots 000)$  to  $(0000 \dots 001)$  from the ideal, i.e., +1/2 LSB.

#### **Gain Error**

This is the deviation of the last code transition from the ideal AIN voltage (Full Scale – 1.5 LSB) after the offset error has been adjusted out.

#### Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_S/2$ ), excluding dc.

The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise +distortion) ratio for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) = (6.02N + 1.76) dB

Thus for a 12-bit converter, this is 74 dB.

#### **Total Harmonic Distortion**

Total Harmonic Distortion is the ratio of the rms sum of the harmonics to the fundamental.

#### DAC SPECIFICATIONS

#### **Relative Accuracy**

Relative accuracy or endpoint linearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and full-scale error.

#### **Voltage Output Settling Time**

This is the amount of time it takes for the output to settle to a specified level for a full-scale input change.

#### Digital-to-Analog Glitch Impulse

This is the amount of charge injected into the analog output when the inputs change state. It is specified as the area of the glitch in nV sec.

#### INTRODUCTION

The ADuC841 is a 25MIPs 8052 core upgrade to the ADuC831. It has all the same features as the ADuC831 but the standard 12-cycle 8052 core has been replaced with a 25MIPs single cycle core.

Since the ADuC841 and ADuC831 share the same feature set only the differneces bettween the two chips are documented here. For full documentation on the ADuC831 please consult the datasheet available at http://www.analog.com/microconverter

#### 8052 Instruction Set

The following pages document the number of clock cycles required for each instruction. Most instructions are executed in one or two clock cycles resulting in a 25MIPs peak peformance when operating from a 25MHz crystal.

#### **Timer Operation**

Timers on a standard 8052 increment by one with each machine cycle. On the ADuC841 one machine cycle is equal to one clock cycle hence the timers will increment at the same rate as the core clock.

#### ALE

The output on the ALE pin on the ADuC831 was a clock at 1/ 6th of the core operating frequency. On the ADuC841 the ALE pin operates as follows.

For a single machine cycle instruction: ALE is high for the first half of the machine cycle and low for the second half. The ALE output is at the core operating frequency.

For a two or more machine cycle instruction: ALE is high for the first half of the first machine cycle and then low for the rest of the machine cycles.

#### **External Memory Access**

There is no support for external program memory access on the ADuC841. When accessing external RAM the EWAIT register may need to be programmed in order to give extra machine cycles to MOVX commands. This is to account for differing external RAM access speeds.

#### **Baud Rate Generation**

There is an addition divide by two in the fractional divider of the ADuC841 this means that any values calculated for T3CON for the ADuC831 need to be incremented by one in order to give the same baud rate on the ADuC841.

# INSTRUCTION TABLE

| Mnemonic      | Description                                 | Bytes | Cycles |

|---------------|---------------------------------------------|-------|--------|

| Arithmetic    |                                             |       |        |

| ADD A,Rn      | Add register to A                           | 1     | 1      |

| ADD A,@Ri     | Add indirect memory to A                    | 1     | 2      |

| ADD A,dir     | Add direct byte to A                        | 2     | 2      |

| ADD A,#data   | Add immediate to A                          | 2     | 2      |

| ADDC A,Rn     | Add register to A with carry                | 1     | 1      |

| ADDC A,@Ri    | Add indirect memory to A with carry         | 1     | 2      |

| ADDC A,dir    | Add direct byte to A with carray            | 2     | 2      |

| ADD A,#data   | Add immediate to A with carry               | 2     | 2      |

| SUBB A,Rn     | Subtract register from A with borrow        | 1     | 1      |

| SUBB A,@Ri    | Subtract indirect memory from A with borrow | 1     | 2      |

| SUBB A,dir    | Subtract direct from A with borrow          | 2     | 2      |

| SUBB A,#data  | Subtract immediate from A with borrow       | 2     | 2      |

| INC A         | Increment A                                 | 1     | 1      |

| INC Rn        | Increment register                          | 1     | 1      |

| INC @Ri       | Increment indirect memory                   | 1     | 2      |

| INC dir       | Increment direct byte                       | 2     | 2      |

| INC DPTR      | Increment data pointer                      | 1     | 3      |

| DEC A         | Decrement A                                 | 1     | 1      |

| DEC Rn        | Decrement Register                          | 1     | 1      |

| DEC @Ri       | Decrement indirect memory                   | 1     | 2      |

| DEC dir       | Decrement direct byte                       | 2     | 2      |

| MUL AB        | Multiply A by B                             | 1     | 9      |

| DIV AB        | Divide A by B                               | 1     | 9      |

| DA A          | Decimal Adjust A                            | 1     | 2      |

| Logic         |                                             |       |        |

| ANL A,Rn      | AND register to A                           | 1     | 1      |

| ANL A,@Ri     | AND indirect memory to A                    | 1     | 2      |

| ANL A, dir    | AND direct byte to A                        | 2     | 2      |

| ANL A,#data   | AND immediate to A                          | 2     | 2      |

| ANL dir,A     | AND A to direct byte                        | 2     | 2      |

| ANL dir,#data | AND immediate data to direct byte           | 3     | 3      |

| ORL A,Rn      | OR register to A                            | 1     | 1      |

| ORL A,@Ri     | OR indirect memory to A                     | 1     | 2      |

| ORL A,dir     | OR direct byte to A                         | 2     | 2      |

| ORL A,#data   | OR immediate to A                           | 2     | 2      |

| ORL dir,A     | OR A to direct byte                         | 2     | 2      |

| ORL dir,#data | OR immediate data to direct byte            | 3     | 3      |

|               |                                             |       |        |

| XRL A,Rn       | Exclusive-OR register to A            | 1 | 1 |  |

|----------------|---------------------------------------|---|---|--|

| XRL A,@Ri      | Exclusive-OR indirect memory to A     | 2 | 2 |  |

| XRL A,#data    | Exclusive-OR immediate to A           | 2 | 2 |  |

| XRL dir,A      | Exclusive-OR A to direct byte         | 2 | 2 |  |

| XRL A,dir      | Exclusive-OR indirect memory to A     | 2 | 2 |  |

| XRL dir,#data  | Exclusive-OR immediate data to direct | 3 | 3 |  |

| CLR A          | Clear A                               | 1 | 1 |  |

| CPL A          | Complement A                          | 1 | 1 |  |

| SWAP A         | Swap Nibbles of A                     | 1 | 1 |  |

| RL A           | Rotate A left                         | 1 | 1 |  |

| RLC A          | Rotate A left through carry           | 1 | 1 |  |

| RR A           | Rotate A right                        | 1 | 1 |  |

| RRC A          | Rotate A right through carry          | 1 | 1 |  |

| Data Transfer  | 0                                     |   |   |  |

| MOV A,Rn       | Move register to A                    | 1 | 1 |  |

| MOV A,@Ri      | Move indirect memory to A             | 1 | 2 |  |

| MOV Rn,A       | Move A to register                    | 1 | 1 |  |

| MOV @Ri,A      | Move A to indirect memory             | 1 | 2 |  |

| MOV A,dir      | Move direct byte to A                 | 2 | 2 |  |

| MOV A,#data    | Move immediate to A                   | 2 | 2 |  |

| MOV Rn,#data   | Move register to immediate            | 2 | 2 |  |

| MOV dir,A      | Move A to direct byte                 | 2 | 2 |  |

| MOV Rn, dir    | Mov register to direct byte           | 2 | 2 |  |

| MOV dir, Rn    | Move direct to register               | 2 | 2 |  |

| MOV @Ri,#data  | Move immediate to indirect memory     | 2 | 2 |  |

| MOV dir,dir    | Move direct byte to direct byte       | 3 | 3 |  |

| MOV dir,#data  | Move immediate to direct byte         | 3 | 3 |  |

| MOV DPTR,#data | Move immediate to data pointer        | 3 | 3 |  |

| MOVC A,@A+DPTR | Move code byte relative DPTR to A     | 1 | 4 |  |

| MOVC A,@A+PC   | Move code byte relative PC to A       | 1 | 4 |  |

| MOVX A,@Ri     | Move external (A8) data to A          | 1 | 4 |  |

| MOVX A,@DPTR   | Move external (A16) data to A         | 1 | 4 |  |

| MOVX @Ri,A     | Move A to external data (A8)          | 1 | 4 |  |

| MOVX @DPTR,A   | Move A to external data (A16)         | 1 | 4 |  |

| PUSH dir       | Push direct byte onto stack           | 2 | 2 |  |

| POP dir        | Pop direct byte from stack            | 2 | 2 |  |

| XCH A,Rn       | Exchange A and register               | 1 | 1 |  |

| XCH A,@Ri      | Exchange A and indirect memory        | 1 | 2 |  |

| XCHD A,@Ri     | Exchange A and indirect memory nibble | 1 | 2 |  |

| XCH A,dir      | Exchange A and direct byte            | 2 | 2 |  |

| Boolean        |                                       |   |   |  |

| CLR C              | Clear carry                              | 1 | 1 |  |

|--------------------|------------------------------------------|---|---|--|

| CLR bit            | Clear direct bit                         | 2 | 2 |  |

| SETB C             | Set Carry                                | 1 | 1 |  |

| SETB bit           | Set direct bit                           | 2 | 2 |  |

| CPL C              | Complement carry                         | 1 | 1 |  |

| CPL bit            | Complement direct bit                    | 2 | 2 |  |

| ANL C,bit          | AND direct bit and carry                 | 2 | 2 |  |

| ANL C,/bit         | AND direct bit inverse to carry          | 2 | 2 |  |

| ORL C,bit          | OR direct bit and carry                  | 2 | 2 |  |

| ORL C,/bit         | OR direct bit inverse to carry           | 2 | 2 |  |

| MOV C,bit          | Move direct bit to carry                 | 2 | 2 |  |

| MOV bit,C          | Move carry to direct bit                 | 2 | 2 |  |

| Branching          |                                          |   |   |  |

| JMP @A+DPTR        | Jump indirect relative to DPTR           | 1 | 3 |  |

| RET                | Return from subroutine                   | 1 | 4 |  |

| RETI               | Return from interrupt                    | 1 | 4 |  |

| ACALL addr11       | Absolute jump to subroutine              | 2 | 3 |  |

| AJMP addr11        | Absolute jump unconditional              | 2 | 3 |  |

| SJMP rel           | Short jump (relative address)            | 2 | 3 |  |

| JC rel             | Jump on carry = 1                        | 2 | 3 |  |

| JNC rel            | Jump on carry = 0                        | 2 | 3 |  |

| JZ rel             | Jump on accumulator = 0                  | 2 | 3 |  |

| JNZ rel            | Jump on accumulator != 0                 | 2 | 3 |  |

| DJNZ Rn,rel        | Decrement register, jnz relative         | 2 | 3 |  |

| LJMP               | Long jump unconditional                  | 3 | 4 |  |

| LCALL addr16       | Long jump to subroutine                  | 3 | 4 |  |