# TECHNICAL MANUAL

# 1394 Node Controller Core

August 2001 Preliminary

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications using production parts.

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000075-02, Third Edition (August 2001) This document describes the LSI Logic Corporation 1394 Node Controller Core and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, CoreWare, G10, GigaBlaze, FlexStream, and Right-First-Time are trademarks or registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

EΗ

To receive product literature, visit us at http://www.lsilogic.com.

For a current list of our distributors, sales offices, and design resource centers, view our web page located at

http://www.lsilogic.com/contacts/na\_salesoffices.html

## Preface

This book is the primary reference and technical manual for the 1394 Node Controller core. It contains preliminary information regarding the functional description of the 1394 Node Controller core.

#### Audience

This document assumes that you have some familiarity with the IEEE 1394 high-performance serial bus and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the 1394 Node Controller core for possible use in a system

- Engineers who are designing the 1394 Node Controller core into a system

#### Organization

This document has the following chapters:

- Chapter 1, Introduction, summarizes the key features and applications of the 1394 Node Controller core.

- Chapter 2, Data Formats, describes the different data formats that the 1394 Node Controller core sends and receives.

- Chapter 3, Signal Descriptions, describes the signals that comprise the external interface of the 1394 Node Controller core.

- Chapter 4, **Registers**, describes the internal registers of the 1394 Node Controller core.

- Chapter 5, **Operation Overview**, provides functional waveforms, which show the operation of the core.

• Chapter 6, Application Operation, describes transmit and receive operations from the viewpoint of the application.

#### **Related Publications**

1394 Physical Layer (PHY) Core Technical Manual, Document No. DB14-000036-01

IEEE Standard for a High Performance Serial Bus (IEEE Standard 1394-1995)

P1394a Draft Standard for a High Performance Serial Bus (Supplement)

#### **Conventions Used in This Manual**

- All signals have the module name as prefix. For example: LLC\_Lreq: This signal is part of the LLC module.

- All signals ending with 'N' are LOW-asserted signals. For example: APP\_RstN: Reset is an active-LOW signal.

#### Abbreviations:

| ABUF  | Asynchronous Buffer Block                    |

|-------|----------------------------------------------|

| APPIF | Application Interface Module                 |

| AV/C  | Audio Video Control (IEC-61883)              |

| CHF   | CIP Header Field (IEC-61883)                 |

| CIP   | Common Isochronous Packet (IEC-61883)        |

| СМР   | Connection Management Procedures (IEC-61883) |

| CSR   | Command and Status Register (ISO/IEC-13213)  |

| CSU   | Control and Status Unit                      |

| CRC   | Cyclic Redundancy Check code                 |

| DBUF  | DMA Buffer Block                             |

| DVCR  | Digital Video Cassette Recorder              |

| EOH   | End Of CIP Header (IEC-61883)                |

| FCP       | Function Control Protocol (IEC-61883)                 |

|-----------|-------------------------------------------------------|

| IEC-61883 | Standard for consumer digital AV equipment using 1394 |

| IMPR      | Input Master Plug Register                            |

| IPCR      | Input Plug Control Register (IEC-61883)               |

| LLC       | Link Layer Controller                                 |

| MPEG      | Motion Picture Experts Group                          |

| OPCR      | Output Plug Control Register                          |

| OMPR      | Output Master Plug Register                           |

| ORB       | Operation Request Block                               |

| PCR       | Plug Control Register                                 |

| PHT       | Packet Header Transformation                          |

| SBP-2     | Serial Bus Protocol 2                                 |

| SPH       | Source Packet Header (IEC-61883)                      |

| UBUF      | Universal Asynchronous Buffer                         |

| URF       | Universal Receive FIFO                                |

| UTF       | Universal Transmit FIFO                               |

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

## Contents

| Chapter 1 | Intro | duction  |                                    |      |

|-----------|-------|----------|------------------------------------|------|

|           | 1.1   |          | gic CoreWare <sup>®</sup> Program  | 1-2  |

|           | 1.2   |          | lode Controller Core Overview      | 1-3  |

|           | 1.3   |          | Diagram Description                | 1-4  |

|           | 1.4   | Feature  | -                                  | 1-5  |

|           |       | 1.4.1    | General                            | 1-5  |

|           |       | 1.4.2    | Application Interface              | 1-6  |

|           |       | 1.4.3    | Asynchronous Operation             | 1-6  |

|           |       | 1.4.4    | Isochronous Operation              | 1-6  |

|           |       | 1.4.5    | Bus Management                     | 1-7  |

|           | 1.5   | Applica  | tions                              | 1-7  |

| Chapter 2 | Data  | Formate  | 5                                  |      |

|           | 2.1   | Asynch   | ronous Data Formats                | 2-1  |

|           |       | 2.1.1    | Asynchronous Transmit Data Formats | 2-1  |

|           |       | 2.1.2    | Asynchronous Receive Data Formats  | 2-9  |

|           | 2.2   | Isochro  | nous DMA Data Formats              | 2-17 |

|           |       | 2.2.1    | Isochronous Transmit Data Formats  | 2-17 |

|           |       | 2.2.2    | Isochronous Receive Data Formats   | 2-20 |

|           | 2.3   | PHY P    | acket Data Formats                 | 2-21 |

|           |       | 2.3.1    | PHY Packet Transmit Data Format    | 2-21 |

|           |       | 2.3.2    | PHY Packet Receive Data Format     | 2-22 |

|           | 2.4   | Miscella | aneous Packet Data Formats         | 2-22 |

|           |       | 2.4.1    | Self-ID Packet Receive Data Format | 2-22 |

|           |       | 2.4.2    | Unformatted Data Transmit Format   | 2-23 |

| Chapter 3 | Sign  | al Descr | iptions                            |      |

|           | 3.1   | Applica  | tion Interface                     | 3-3  |

|           | 3.2   | Univers  | al Buffer FIFO Interface           | 3-4  |

|           |       |          |                                    |      |

|           | 3.3  | PHY In   | terface                                   | 3-6  |

|-----------|------|----------|-------------------------------------------|------|

|           | 3.4  | DMA 0    | Interface                                 | 3-8  |

|           | 3.5  | DMA 1    | Interface                                 | 3-10 |

|           | 3.6  | DMA 0    | FIFO Interface                            | 3-12 |

|           | 3.7  | DMA 1    | FIFO Interface                            | 3-14 |

|           | 3.8  | Miscella | aneous                                    | 3-15 |

| Chapter 4 | Regi | sters    |                                           |      |

|           | 4.1  | Orderin  | g Conventions                             | 4-1  |

|           | 4.2  | Control  | and Status Registers (CSRs)               | 4-2  |

|           |      | 4.2.1    | Node ID Register (0x000)                  | 4-2  |

|           |      | 4.2.2    | Cycle Time Register (0x004)               | 4-3  |

|           | 4.3  | 1394 R   | egisters                                  | 4-5  |

|           |      | 4.3.1    | Control 0 Register (0x008)                | 4-7  |

|           |      | 4.3.2    | Control 1 Register (0x00C)                | 4-11 |

|           |      | 4.3.3    | Control 2 Register (0x010)                | 4-12 |

|           |      | 4.3.4    | PHY Access Register (0x014)               | 4-13 |

|           |      | 4.3.5    | Interrupt 0 Register (0x020)              | 4-14 |

|           |      | 4.3.6    | Interrupt 0 Mask Register (0x024)         | 4-19 |

|           |      | 4.3.7    | Interrupt 1 Register (0x028)              | 4-21 |

|           |      | 4.3.8    | Interrupt 1 Mask Register (0x02C)         | 4-22 |

|           |      | 4.3.9    | Interrupt 2 Register (0x030)              | 4-23 |

|           |      | 4.3.10   | Interrupt 2 Mask Register (0x034)         | 4-23 |

|           |      | 4.3.11   | DMA Space Register (0x038)                | 4-24 |

|           |      | 4.3.12   | Acknowledge Status Register (0x03C)       | 4-25 |

|           |      | 4.3.13   | UBUF Transmit Next (0x040)                | 4-25 |

|           |      | 4.3.14   | UBUF Transmit Last (0x044)                | 4-25 |

|           |      | 4.3.15   | UBUF Transmit Clear (0x048)               | 4-26 |

|           |      | 4.3.16   | UBUF Receive Clear (0x04C)                | 4-26 |

|           |      | 4.3.17   | UBUF Receive (0x050)                      | 4-26 |

|           |      | 4.3.18   | UBUF Receive Level (0x054)                | 4-26 |

|           |      | 4.3.19   | Encoded Interrupt Priority (0x058)        | 4-26 |

|           |      | 4.3.20   | PHT Control and Status Register 0 (0x080) | 4-28 |

|           |      | 4.3.21   | PHT Split Time-out/Empty CIP Interval     |      |

|           |      |          | Register 0 (0x084)                        | 4-35 |

|           |      | 4.3.22   | PHT Request/Response/CIP Receive          |      |

|           |      |          | Header 0 Register 0 (0x088)               | 4-37 |

| 4.3.23 | PHT Request/Response/CIP Receive<br>Header 1 Register 0 (0x08C) | 4-39 |

|--------|-----------------------------------------------------------------|------|

| 4.3.24 | PHT Request Header 2/Stream SPH Receive                         | 4-55 |

| 4.3.24 | Register 0 (0x090)                                              | 4-42 |

| 4.3.25 | Stream Receive Channel/NodeID Selection 0                       |      |

|        | Register 0 (0x094)                                              | 4-43 |

| 4.3.26 | Stream Receive Channel/NodeID Selection 1                       |      |

|        | Register 0 (0x098)                                              | 4-44 |

| 4.3.27 | Stream Receive Channel Header                                   |      |

|        | Register 0 (0x09C)                                              | 4-44 |

| 4.3.28 | Stream Transmit Channel Header                                  |      |

|        | Register 0 (0x0A0)                                              | 4-45 |

| 4.3.29 | Data Transfer Control Register 0 (0x0A4)                        | 4-47 |

| 4.3.30 | CIP Header Transmit 0 Register 0 (0x0A8)                        | 4-48 |

| 4.3.31 | CIP Header Transmit 1 Register 0 (0x0AC)                        | 4-49 |

| 4.3.32 | Stream Transmit Time Stamp Offset                               |      |

|        | Register 0 (0x0B4)                                              | 4-50 |

| 4.3.33 | DMA Control and Status Register 0 (0x0B8)                       | 4-52 |

| 4.3.34 | DMA Transfer Threshold Register 0 (0x0BC)                       | 4-53 |

| 4.3.35 | DBUF FIFOs Level Register 0 (0x0C0)                             | 4-54 |

| 4.3.36 | DBUF Tx Data Register 0 (0x0C4)                                 | 4-54 |

| 4.3.37 | DBUF Rx Data Register 0 (0x0C8)                                 | 4-55 |

| 4.3.38 | DBUF FIFOs Watermark Level                                      |      |

|        | Register 0 (0x0CC)                                              | 4-56 |

| 4.3.39 | DBUF FIFOs Size Register 0 (0x0D0)                              | 4-57 |

| 4.3.40 | PHT Control and Status Register 1 (0x100)                       | 4-57 |

| 4.3.41 | PHT Split Time-Out/Empty CIP Interval                           |      |

|        | Register 1 (0x104)                                              | 4-64 |

| 4.3.42 | PHT Request/Response/CIP Receive                                |      |

|        | Header 0 Register 1 (0x108)                                     | 4-66 |

| 4.3.43 | PHT Request/Response/CIP Receive                                |      |

|        | Header 1 Register 1 (0x10C)                                     | 4-68 |

| 4.3.44 | PHT Request Header 2/Stream SPH Receive                         | 4 74 |

| 4 9 45 | Register 1 (0x110)                                              | 4-71 |

| 4.3.45 | Stream Receive Channel/NodeID Selection 0                       | 4 70 |

| 4 0 40 | Register 1 (0x114)                                              | 4-73 |

| 4.3.46 | Stream Receive Channel/NodeID Selection 1                       | 4-73 |

|        | Register 1 (0x118)                                              | 4-13 |

|           | 4.3.47    | Stream Receive Channel Header                 |              |

|-----------|-----------|-----------------------------------------------|--------------|

|           |           | Register 1 (0x11C)                            | 4-74         |

|           | 4.3.48    | Stream Transmit Channel Header                |              |

|           |           | Register 1 (0x120)                            | 4-75         |

|           | 4.3.49    | Data Transfer Control Register 1 (0x124)      | 4-76         |

|           | 4.3.50    | CIP Header Transmit 0 Register 1 (0x128)      | 4-77         |

|           | 4.3.51    | CIP Header Transmit 1 Register 1 (0x12C)      | 4-78         |

|           | 4.3.52    | Stream Transmit Time Stamp Offset             |              |

|           |           | Register 1 (0x134)                            | 4-79         |

|           | 4.3.53    | DMA Control and Status Register 1 (0x138)     | 4-81         |

|           | 4.3.54    | DMA Transfer Threshold Register 1 (0x13C)     | 4-82         |

|           | 4.3.55    | DBUF FIFOs Level Register 1 (0x140)           | 4-83         |

|           | 4.3.56    | DBUF Tx Data Register 1 (0x144)               | <b>4-8</b> 4 |

|           | 4.3.57    | DBUF Rx Data Register 1 (0x148)               | <b>4-84</b>  |

|           | 4.3.58    | DBUF FIFOs Watermark Level Register 1 (0x14C) | 4-85         |

|           | 4.3.59    | DBUF FIFOs Size Register 1 (0x150)            | 4-86         |

| <br>Opera | ation Ove | rview                                         |              |

| 5.1       | Link Lay  | er Controller                                 | 5-1          |

|           | 5.1.1     | Transmitter                                   | 5-1          |

|           | 5.1.2     | Receiver                                      | 5-2          |

|           | 5.1.3     | PHY Interface                                 | 5-4          |

|           | 5.1.4     | Single-Phase Retry Mechanism                  | 5-8          |

| 5.2       | Applicati | on Interface Module                           | 5-9          |

|           | 5.2.1     | Read Accesses                                 | 5-9          |

|           | 5.2.2     | Write Accesses                                | 5-10         |

| 5.3       | Packet H  | leader Transformation Modules (PHTs)          | 5-11         |

|           | 5.3.1     | Isochronous Transmission                      | 5-11         |

|           | 5.3.2     | Isochronous Reception                         | 5-12         |

|           | 5.3.3     | Tight Isochronous Cycles                      | 5-12         |

|           | 5.3.4     | Loose Isochronous Packets                     | 5-12         |

|           | 5.3.5     | Asynchronous Request Transmission             | 5-13         |

|           | 5.3.6     | Asynchronous Request Reception                | 5-13         |

|           | 5.3.7     | Scheduling of Packets for Transmission        | 5-13         |

| 5.4       | Interrupt | Mechanism                                     | 5-14         |

|           | 5.4.1     | Setting Up the Interrupt Mask Registers       | 5-14         |

|           |           |                                               |              |

5.4.2 Determining and Clearing the Interrupt 5-15

Chapter 5

| Chapter 6 | App | lication C | Dperation                                   |      |

|-----------|-----|------------|---------------------------------------------|------|

|           | 6.1 | Asynch     | ronous Packet Reception                     | 6-1  |

|           | 6.2 | Asynch     | ronous Packet Transmission                  | 6-2  |

|           | 6.3 | Asynch     | ronous Stream Packet Transmission           | 6-3  |

|           | 6.4 | Examp      | le Register Configurations                  | 6-3  |

|           |     | 6.4.1      | Automatic Asynchronous Write Request        |      |

|           |     |            | Packet Generation                           | 6-3  |

|           |     | 6.4.2      | Automatic Asynchronous Read Request         |      |

|           |     |            | Packet Generation                           | 6-4  |

|           |     | 6.4.3      | CIP Format Isochronous Packet Reception     | 6-5  |

|           |     | 6.4.4      | Simultaneous CIP Format Isochronous Packet  |      |

|           |     |            | Reception and Transmission                  | 6-6  |

|           |     | 6.4.5      | Automatic Asynchronous Request Packet       |      |

|           |     |            | Processing                                  | 6-7  |

|           |     | 6.4.6      | Asynchronous Write Request Packet           |      |

|           |     |            | Generation Writing DMA Transmit FIFO        |      |

|           |     |            | Through The Application Interface           | 6-8  |

|           |     | 6.4.7      | Asynchronous Read Request Packet            |      |

|           |     |            | Generation Reading DMA Receive FIFO         |      |

|           |     |            | Through The Application Interface           | 6-9  |

|           |     | 6.4.8      | CIP Format Isochronous Packet Transmission  |      |

|           |     |            | with SYT Time Stamps Using Programmable Fra | ıme  |

|           |     |            | Synchronization                             | 6-10 |

|           |     |            |                                             |      |

## **Customer Feedback**

## Figures

| 1.1 | 1394 Node Controller Core Block Diagram               | 1-4 |

|-----|-------------------------------------------------------|-----|

| 2.1 | Read Request for Data Quadlet Packet Transmit Format  | 2-2 |

| 2.2 | Write Response Packet Transmit Format                 | 2-2 |

| 2.3 | Write Request for Data Quadlet Packet Transmit Format | 2-4 |

| 2.4 | Read Response for Quadlet Data Packet Transmit Format | 2-4 |

| 2.5 | Read Request for Block Data Packet Transmit Format    | 2-4 |

| 2.6 | Lock/Write Request for Data Block Packet Transmit     |     |

|     | Format                                                | 2-6 |

| 2.7 | Lock/Read Response for Block Data Packet Transmit     |     |

|     | Format                                                | 2-6 |

| 2.8  | Read Request Receive Format for Data Quadlet     | 2-9  |

|------|--------------------------------------------------|------|

| 2.9  | Write Response Packet Receive Format             | 2-9  |

| 2.10 | Write Quadlet Request Receive Format             | 2-11 |

| 2.11 | Read Quadlet Response Packet Receive Format      | 2-11 |

| 2.12 | Read Block Request Packet Receive Format         | 2-12 |

| 2.13 | Lock/Write Request for Data Block Receive Format | 2-14 |

| 2.14 | Lock/Read Response for Block Data Receive Format | 2-15 |

| 2.15 | Isochronous Transmit Format 1                    | 2-17 |

| 2.16 | Isochronous Transmit Format 2                    | 2-17 |

| 2.17 | Isochronous Transmit Format 3                    | 2-19 |

| 2.18 | Isochronous Receive Format 1                     | 2-20 |

| 2.19 | Isochronous Receive Format 2                     | 2-21 |

| 2.20 | PHY Packet Transmit Data Format                  | 2-22 |

| 2.21 | PHY Packet Receive Data Format                   | 2-22 |

| 2.22 | Self-ID Receive Format                           | 2-23 |

| 2.23 | Unformatted Data Transmit Format                 | 2-23 |

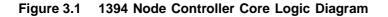

| 3.1  | 1394 Node Controller Core Logic Diagram          | 3-2  |

| 4.1  | Interior Bit Significance                        | 4-1  |

| 4.2  | Interior Byte Significance                       | 4-2  |

| 4.3  | Internal Quadlet Order                           | 4-2  |

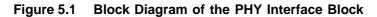

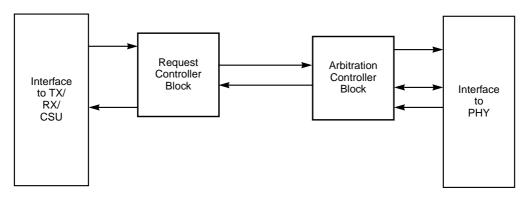

| 5.1  | Block Diagram of the PHY Interface Block         | 5-5  |

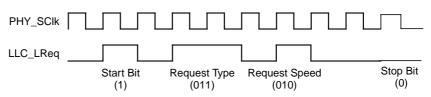

| 5.2  | Bus Request using LLC_LReq                       | 5-5  |

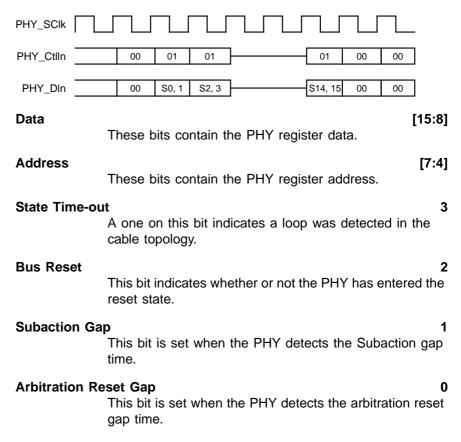

| 5.3  | Status Timing                                    | 5-6  |

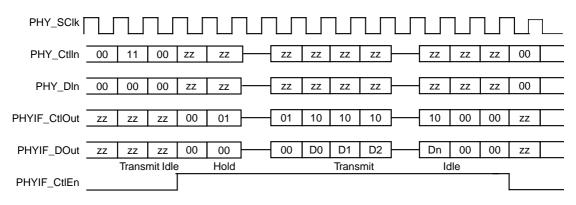

| 5.4  | Transmit Timing                                  | 5-7  |

| 5.5  | Receive Timing                                   | 5-8  |

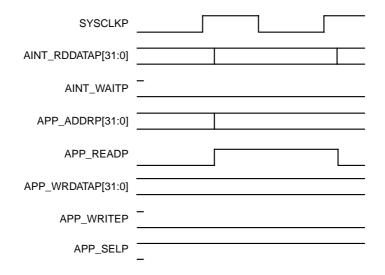

| 5.6  | Read from the Application                        | 5-10 |

| 5.7  | Write from Application                           | 5-11 |

| 6.1  | Write Quadlet Request Receive Format             | 6-1  |

| 6.2  | Write Quadlet Response Packet Transmit Format    | 6-2  |

|      |                                                  |      |

## Tables

| 4.1 | CSR Registers         | 4-2 |

|-----|-----------------------|-----|

| 4.2 | 1394 Register Summary | 4-5 |

| 5.1 | Tcodes                | 5-2 |

| 5.2 | Speed Codes           | 5-8 |

## Chapter 1 Introduction

This chapter contains the following sections:

- Section 1.1, "LSI Logic CoreWare® Program"

- Section 1.2, "1394 Node Controller Core Overview"

- Section 1.3, "Block Diagram Description"

- Section 1.4, "Features"

- Section 1.5, "Applications"

The 1394 Node Controller core conforms with the requirements of the IEEE 1394-1995 Standard for High Performance Serial Bus and the 1394a supplement. It provides full link layer functionality and easily interfaces to the LSI Logic 1394 Physical Layer Core or any other standard 1394a-compliant PHY device.

The core uses a DMA interface to reduce CPU utilization for large data transfers. The core can process incoming 1394 read/write requests to a programmable 4 Gbyte range without CPU intervention using DMA transfers. This feature is useful when the core is used in SBP-2 (serial bus protocol) initiator applications or DPP (Direct Print Protocol) receiver mode. The core can generate automatic and sequential 1394 read/write requests. This feature is useful when the core is used in SBP-2 target applications or DPP sender mode.

Isochronous transfers use the DMA interface. CIP (common isochronous packet) headers can be generated automatically when transmitting. The core supports hardware-assisted transmit data flow control (for example, DV empty CIP packet generation). The core also supports simultaneous transmission and reception of one IEC-61883 format talk stream and two listen streams.

For unformatted streams (1394 tag equals zero), the core supports any combination of simultaneous talk and listen channels.

When the core is a 1394 cycle master, it supports external 1394 cycle timer control by using the cycle clock input signal. The core provides a clock output signal that is based on a 1394 cycle timer for application synchronization when the core is a 1394 cycle slave.

## 1.1 LSI Logic CoreWare<sup>®</sup> Program

An LSI Logic core is a fully defined, optimized, and reusable block of logic. It supports industry-standard functions and has predefined timing and layout. The core is also an encrypted RTL simulation model for a wide range of VHDL and Verilog simulators.

The CoreWare library contains an extensive set of complex cores for the communications, consumer, and computer markets. The library consists of high-speed interconnect functions such as the GigaBlaze<sup>®</sup> G10<sup>®</sup> core, MIPS embedded microprocessors, a USB core, a PCI core, and many more.

The library also includes megafunctions or *building blocks*, which provide useful functions for developing a system on a chip. Through the CoreWare program, you can create a system on a chip uniquely suited to your applications.

Each core has an associated set of deliverables, including:

- RTL simulation models for both Verilog and VHDL environments

- A System Verification Environment (SVE) for RTL-based simulation

- Synthesis and timing shells

- Netlists for full timing simulation

- Complete documentation

- LSI Logic FlexStream software support

The LSI Logic FlexStream software provides seamless connectivity between products from leading electronic design automation (EDA) vendors and LSI Logic manufacturing environment. Standard interfaces for formats and languages such as VHDL, Verilog, Waveform Generation Language (WGL), Physical Design Exchange Format (PDEF), and Standard Delay Format (SDF) allow a wide range of tools to interoperate within the LSI Logic FlexStream environment. In addition to design capabilities, full scan Automatic Test Pattern Generation (ATPG) tools and LSI Logic specialized test solutions can be combined to provide high-fault coverage test programs that assure a fully functional design.

Because your design requirements are unique, LSI Logic is flexible in working with you to develop your system-on-a-chip CoreWare design. Three different work relationships are available:

- You provide LSI Logic with a detailed specification and LSI Logic performs all design work.

- You design some functions while LSI Logic provides you with the cores and megafunctions, and LSI Logic completes the integration.

- You perform the entire design and integration, and LSI Logic provides the core and associated deliverables.

Whatever the work relationship, the LSI Logic advanced CoreWare methodology and ASIC process technologies consistently produce Right-First-Time<sup>™</sup> silicon.

## 1.2 1394 Node Controller Core Overview

The 1394 Node Controller core is targeted for embedded ASIC designs using the IEEE 1394 serial bus. The core provides full link layer functionality. The link layer provides a one-way data transfer with confirmation of request to the transaction layer. The link layer also provides addressing, data checking, and data framing for transmitting and receiving of packets.

The 1394 Node Controller core supports asynchronous and isochronous transfers. You can configure a wide range of isochronous support capabilities, including transmission and reception of several isochronous channels in parallel. The 1394 Node Controller core seamlessly connects to the LSI Logic 1394 Physical Layer core or any other PHY device that conforms to the 1394a specification.

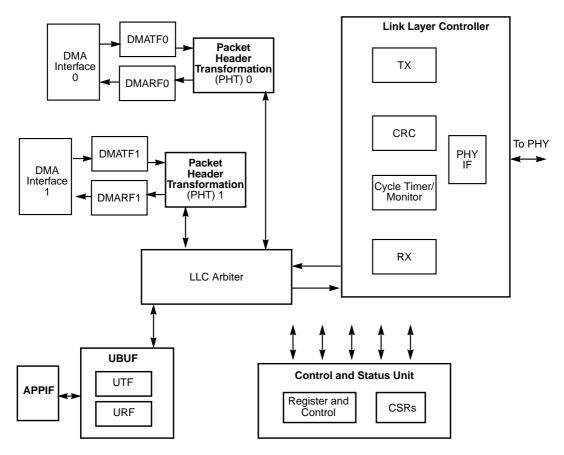

The configurable core design is ideal for a wide range of embedded applications, from basic low-cost devices to sophisticated highperformance ASICs. The core design consists of the Link Layer Controller (LLC), Control and Status Unit, LLC Arbiter, UBUF, APPIF, two PHTs, and two DMATF, DMARF, and DMA interfaces. The Packet Header Transformation (PHT) module is capable of large isochronous or asynchronous DMA transfers. The universal asynchronous buffer is primarily intended for protocol (SBP-2, DPP, AV/C, IICP, etc.) command and status transfers.

## 1.3 Block Diagram Description

Figure 1.1 shows a block diagram of the 1394 Node Controller core.

Figure 1.1 1394 Node Controller Core Block Diagram

The Link Layer Controller (LLC) implements the complete functionality of the Link Layer in the 1394 Node Controller core. This block interfaces

to the PHY, the Arbiter, the Packet Header Transformation module (PHT), and the Control and Status Unit.

The **PHY Interface (PHYIF)** handles all the protocols between the PHY and the LLC.

The **Universal Asynchronous Buffer (UBUF)** block contains a set of FIFOs for transmitting and receiving asynchronous packets. Only one packet is allowed in each of the UBUF Transmit FIFO (UTF).

The **Packet Header Transformation (PHT)** modules handle the communication between the LLC and the DMA interfaces.

The **Application Interface (APPIF)** module connects the application with the 1394 for nonautomated asynchronous packet transfers. The application uses this interface to access the 1394 register space.

The **Control and Status Unit (CSU)** implements the Node Controller registers.

The **DMA Buffer Block (DBUF)** contains a set of FIFOs for isochronous data transmission and reception for different channels or automated asynchronous transfers.

## 1.4 Features

The features of the 1394 Node Controller core are summarized in the following subsections.

## 1.4.1 General

- Supports IEEE Standard 1394-1995 and the 1394a supplement

- Implements full link layer

- Reduces CPU utilization by use of DMA transfers

- Provides automatic asynchronous request packet generation for sequential data buffer accesses

- Generates response to received requests in a designated 4 Gbyte address range without CPU involvement

- Supports 1394 cycle time synchronization with application modules

- Generates IEC-61883 CIP header for isochronous transmission

- Provides hardware-assisted isochronous data flow control

- Provides full packet handling, and packing and unpacking for asynchronous and isochronous packet transmission and reception

- Supports 100/200/400 Mbits/s bus speeds

- Contains a standard PHY interface with up to eight data lines for 400 Mbits/s operation

- Provides 32-bit CRC generation and error detection

- Is configurable to application requirements by optional module selection, compilation parameters (FIFO sizes), and programmable configuration registers

- Connects to the LSI Logic 1394 PHY Core or any other standard 1394a-compliant PHY device

## 1.4.2 Application Interface

- Application interface for both control and data transfers to be used with a microcontroller or a hardwired controller

- Application interface module with 32-bit wide bus (1394 Node Controller core is bus slave) in burst mode as well as nonburst mode

- Controller interface provides access to all CSRs and control register set

- Extensive maskable interrupt register set provides status reporting

## 1.4.3 Asynchronous Operation

- Supports full link layer for asynchronous transmission and reception

- Provides configurable asynchronous buffer bank size during compilation; size allocation among the asynchronous FIFOs configurable by the end-user

- Supports single-phase retry sequence

## 1.4.4 Isochronous Operation

- Supports isochronous bandwidth of the IEEE-1394 bus (up to 400 Mbits/s implementation)

- Transmits and receives multiple isochronous channels

- Provides programmable isochronous data routing with header insertion for transmission and separation for reception

- Supports external DMA controller for isochronous data transmit or receive

- Provides DMA transmit and/or receive FIFO units whose total size is configured during compilation. Size allocation among the FIFOs is configurable by the end-user.

- Provides a byte pack/unpack module for DMA interface

## 1.4.5 Bus Management

- Transaction and isochronous capable node

- Cycle master capable node

- Bus Manager capable node

## 1.5 Applications

Some applications for the 1394 Node Controller core include:

- Digital still cameras

- Video conferencing cameras

- Printers

- Storage devices

- Scanners

- Digital audio devices (consumer and professional)

- Digital VCR/TV

- Digital set-top box

## Chapter 2 Data Formats

This chapter describes the data formats that the 1394 Node Controller core accepts for transmission and reception over the 1394 bus. This chapter contains the following sections:

- Section 2.1, "Asynchronous Data Formats"

- Section 2.2, "Isochronous DMA Data Formats"

- Section 2.3, "PHY Packet Data Formats"

- Section 2.4, "Miscellaneous Packet Data Formats"

In this chapter, the term quadlet refers to a 32-bit data size.

## 2.1 Asynchronous Data Formats

This section describes the asynchronous data formats for the transmit and receive FIFO operations.

### 2.1.1 Asynchronous Transmit Data Formats

Asynchronous data is transmitted in one of three basic formats:

- 1. 3 Quadlet (used for quadlet read requests and quadlet/block write responses)

- 2. 4 Quadlet (used for block read requests, quadlet write requests, and quadlet read responses)

- 3. N Quadlet (used for block write requests, lock requests and responses, and block read responses)

#### 2.1.1.1 3-Quadlet Transmit Format

The 3-quadlet data format is shown in Figures 2.1 and 2.2. The first quadlet contains the packet control information. The second and third quadlets contain the 16-bit destination ID and either the 48-bit quadlet aligned destination offset (used for read requests) or the response code (used for write responses).

#### Figure 2.1 Read Request for Data Quadlet Packet Transmit Format

| Reserved             | spd | tl                    | rt | tcode | pri |  |

|----------------------|-----|-----------------------|----|-------|-----|--|

| destinationID        |     | destinationOffsetHigh |    |       |     |  |

| destinationOffsetLow |     |                       |    |       |     |  |

#### Figure 2.2 Write Response Packet Transmit Format

| RcvdBusID     | Res   | spd  | tl       | rt | tcode | pri |

|---------------|-------|------|----------|----|-------|-----|

| destinationID | rcode |      | Reserved |    |       |     |

|               |       | Rese | erved    |    |       |     |

The field names and their descriptions are described below.

|       | field is the priority level for the current field should always be zero.                                                                                            |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | field is the transaction code for the current following table lists valid encoding for this                                                                         |

| tcode | Description                                                                                                                                                         |

| 0100  | Read Request for Data Quadlet                                                                                                                                       |

| 0010  | Write Response                                                                                                                                                      |

|       | field contains the valid retry code for the<br>et as listed in the following table.                                                                                 |

| rt    | Retry Code                                                                                                                                                          |

| 01    | retry_X                                                                                                                                                             |

|       | This four-bit<br>packet. This<br>Transaction<br>This four-bit<br>packet. The<br>field.<br>tcode<br>0100<br>0010<br>Retry Code<br>This two-bit<br>current pack<br>rt |

| tl        | <b>Transaction Label</b><br>These six bits indicate the transaction label for the<br>packet. They are used for tracking requests with<br>responses. UBUF transmitted requests should never use<br>0x3F, 0x3E (reserved for use by the PHT modules). |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RcvdBusID | Received Bus ID                                                                                                                                                                                                                                     |

This 10-bit field contains the Destination Bus ID used in the write request. This value is used as the Source Bus ID in the write response.

#### spd Speed

This three-bit field indicates the speed at which the current packet is to be sent.

| spd        | Speed       |

|------------|-------------|

| 000        | 100 Mbits/s |

| 010        | 200 Mbits/s |

| 100        | 400 Mbits/s |

| all others | Reserved    |

#### destinationID Destination ID

This 16-bit field specifies the destination ID, which is the concatenation of the 10-bit destination bus ID with the 6-bit destination node ID.

#### destinationOffset

#### **Destination Offset**

The 48-bit destination offset field is the quadlet-aligned destination address.

#### rcode Response Code

This field contains the four-bit response code to an earlier corresponding request.

#### 2.1.1.2 4-Quadlet Transmit Format

This data format is shown in Figures 2.3 through 2.5. The first quadlet contains the packet control information. The second and third quadlets contain the 16-bit destination ID and either the 48-bit quadlet aligned destination offset (used for read/write requests) or the response code (used for read responses). The fourth quadlet contains the quadlet data for read responses and quadlet write requests or the data length for the block read request.

| Reserved             | spd | tl                    | rt | tcode | pri |  |

|----------------------|-----|-----------------------|----|-------|-----|--|

| destinationID        |     | destinationOffsetHigh |    |       |     |  |

| destinationOffsetLow |     |                       |    |       |     |  |

| quadlet_data         |     |                       |    |       |     |  |

#### Figure 2.3 Write Request for Data Quadlet Packet Transmit Format

#### Figure 2.4 Read Response for Quadlet Data Packet Transmit Format

| RcvdBusID     | Res | spd | tl    |          | rt | tcode | pri |

|---------------|-----|-----|-------|----------|----|-------|-----|

| destinationID |     |     | rcode | Reserved |    |       |     |

| Reserved      |     |     |       |          |    |       |     |

| quadlet_data  |     |     |       |          |    |       |     |

#### Figure 2.5 Read Request for Block Data Packet Transmit Format

| Reserved spd tl rt tcode pr |  | pri                   |  |  |  |  |

|-----------------------------|--|-----------------------|--|--|--|--|

| destinationID               |  | destinationOffsetHigh |  |  |  |  |

| destinationOffsetLow        |  |                       |  |  |  |  |

| data_length Reserved        |  |                       |  |  |  |  |

The field names and descriptions are described below.

| pri   |                                | <b>Priority</b><br>This four-bit field is the priority level for the current<br>packet. This field should always be zero. |  |  |  |  |  |

|-------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| tcode |                                | bit field is the transaction code for the current ne following table lists the valid encoding for this                    |  |  |  |  |  |

|       | tcode                          | Description                                                                                                               |  |  |  |  |  |

|       | Write Request for Data Quadlet |                                                                                                                           |  |  |  |  |  |

|       | 0110                           | Read Response for Data Quadlet                                                                                            |  |  |  |  |  |

|       | 0101                           | Read Request for Data Block                                                                                               |  |  |  |  |  |

| rt            | <b>Retry Code</b><br>This two-bit field contains the valid retry code for the<br>current packet as listed in the following table.                                         |                                                                                                                                                           |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|               | rt F                                                                                                                                                                      | etry Code                                                                                                                                                 |  |  |  |  |

|               | 01 r                                                                                                                                                                      | try_X                                                                                                                                                     |  |  |  |  |

| ti            | packet. They are responses. UBUF                                                                                                                                          | el<br>icate the transaction label for the<br>used for tracking requests with<br>transmitted requests should never use<br>ved for use by the PHT modules). |  |  |  |  |

| RcvdBusID     | <b>Received Bus ID</b><br>This 10-bit field contains the Destination Bus ID used in<br>the read request. This value is used as the Source Bus<br>ID in the read response. |                                                                                                                                                           |  |  |  |  |

| spd           | <b>Speed</b><br>This three-bit field indicates the speed at which the<br>current packet is to be sent.                                                                    |                                                                                                                                                           |  |  |  |  |

|               | spd                                                                                                                                                                       | Speed                                                                                                                                                     |  |  |  |  |

|               | 000                                                                                                                                                                       | 100 Mbits/s                                                                                                                                               |  |  |  |  |

|               | 010                                                                                                                                                                       | 200 Mbits/s                                                                                                                                               |  |  |  |  |

|               | 100                                                                                                                                                                       | 400 Mbits/s                                                                                                                                               |  |  |  |  |

|               | all others                                                                                                                                                                | Reserved                                                                                                                                                  |  |  |  |  |

| destinationID | Destination ID<br>This 16-bit field specifies the destination ID, which is the<br>concatenation of the 10-bit destination bus ID with the<br>6-bit destination node ID.   |                                                                                                                                                           |  |  |  |  |

| DestinationOf | fset                                                                                                                                                                      |                                                                                                                                                           |  |  |  |  |

|               | <b>Destination Offset</b><br>The 48-bit destination offset field is the quadlet-aligned<br>destination address.                                                           |                                                                                                                                                           |  |  |  |  |

| rcode         | <b>Response Code</b><br>This field contains the four-bit response code to an earlier<br>corresponding request.                                                            |                                                                                                                                                           |  |  |  |  |

| quadlet_data  |                                                                                                                                                                           | ontains the quadlet data to be<br>her a read response or a write request.                                                                                 |  |  |  |  |

#### data\_length Data Length

The 16-bit data length field specifies the length of the data block size in bytes for block-data read requests.

#### 2.1.1.3 N-Quadlet Transmit Format

The N-Quadlet data format is shown in Figures 2.6 through 2.7. The first quadlet contains the packet control information. The second and third quadlets contain the 16-bit destination ID and either the 48-bit quadlet aligned destination offset (used for read/write requests) or the response code (used for read/lock responses). The fourth quadlet contains the data length and the extended transaction code for the block write/read/lock.

The block data, if any, follows the extended code. Block data must be quadlet aligned; that is, you might have to append zeros to the block data for the last quadlet.

Figure 2.6 Lock/Write Request for Data Block Packet Transmit Format

| Reserved               | spd | tl                    | rt      | tcode   | pri |  |

|------------------------|-----|-----------------------|---------|---------|-----|--|

| destinationID          |     | destinationOffsetHigh |         |         |     |  |

| destinationOffsetLow   |     |                       |         |         |     |  |

| data_length            |     | e                     | extende | d_tcode |     |  |

| data_field             |     |                       |         |         |     |  |

| padding (if necessary) |     |                       |         |         |     |  |

### Figure 2.7 Lock/Read Response for Block Data Packet Transmit Format

| RcvdBusID     | Res | spd   | tl       |     | rt       | tcode      | pri |

|---------------|-----|-------|----------|-----|----------|------------|-----|

| destinationID |     | rcode | Reserved |     |          |            |     |

| Reserved      |     |       |          |     |          |            |     |

| data_length   |     |       |          | e   | extende  | d_tcode    |     |

| data_field    |     |       |          |     |          |            |     |

|               |     |       |          | pad | ding (if | necessary) |     |

#### The field names and their descriptions are described below.

| pri       | <b>Priority</b><br>This four-bit field is the priority level for the current<br>packet. This field should always be zero.                                                                                                                           |                              |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| tcode     | <b>Transaction Code</b><br>This four-bit field is the transaction code for the current<br>packet. The following table lists valid encoding for this<br>field.                                                                                       |                              |  |  |  |  |

|           | tcode                                                                                                                                                                                                                                               | Description                  |  |  |  |  |

|           | 0001                                                                                                                                                                                                                                                | Write Request for Data Block |  |  |  |  |

|           | 1001                                                                                                                                                                                                                                                | Lock Request                 |  |  |  |  |

|           | 1011                                                                                                                                                                                                                                                | Lock Response                |  |  |  |  |

|           | 0111                                                                                                                                                                                                                                                | Read Response for Data Block |  |  |  |  |

| rt        | <b>Retry Code</b><br>This two-bit field contains the valid retry code for the<br>current packet as listed in the following table.                                                                                                                   |                              |  |  |  |  |

|           | rt                                                                                                                                                                                                                                                  | Retry Code                   |  |  |  |  |

|           | 01                                                                                                                                                                                                                                                  | retry_X                      |  |  |  |  |

| tl        | <b>Transaction Label</b><br>These six bits indicate the transaction label for the<br>packet. They are used for tracking requests with<br>responses. UBUF transmitted requests should never use<br>0x3F, 0x3E (reserved for use by the PHT modules). |                              |  |  |  |  |

| RcvdBusID | <b>Received Bus ID</b><br>This 10-bit field contains the Destination Bus ID used in<br>the read request. This value is used as the Source Bus<br>ID in the read response.                                                                           |                              |  |  |  |  |

| spd       | <b>Speed</b><br>This three-bit field indicates the speed at which the<br>current packet is to be sent.                                                                                                                                              |                              |  |  |  |  |

|           | spd Speed                                                                                                                                                                                                                                           |                              |  |  |  |  |

|           | 000                                                                                                                                                                                                                                                 | 100 Mbits/s                  |  |  |  |  |

|           | 010                                                                                                                                                                                                                                                 | 200 Mbits/s                  |  |  |  |  |

|           | 100 400 Mbits/s                                                                                                                                                                                                                                     |                              |  |  |  |  |

|           | all others                                                                                                                                                                                                                                          | Reserved                     |  |  |  |  |

#### destinationID Destination ID

This 16-bit field specifies the destination ID, which is the concatenation of the 10-bit destination bus ID with the 6-bit destination node ID.

#### DestinationOffset

#### **Destination Offset**

The 48-bit destination offset field is the quadlet-aligned destination address.

#### rcode Response Code

This field contains the four-bit response code to an earlier corresponding request.

#### data\_length Data Length

The 16-bit data length field specifies the length of the data block size in bytes for block-data read requests.

#### data\_field Data Field

This field contains block data that needs to be transmitted. Its length is specified by the data\_length field. If data\_length is zero, there is no data\_field. If the value in the data\_length field is not a multiple of four, the data field must be padded with zeros to make it quadlet aligned.

#### extended\_tcode

#### Extended Transaction Code

The extended transaction code is used only for lock transactions. The following table lists the encoding of this field. Refer to the IEEE-1394 document for detailed explanations of this decoding.

| extended_tcode | Description                 |

|----------------|-----------------------------|

| 0x0            | Reserved (reads and writes) |

| 0x1            | mask_swap                   |

| 0x2            | compare_swap                |

| 0x3            | fetch_add                   |

| 0x4            | little_add                  |

| 0x5            | bounded_add                 |

| 0x6            | wrap_add                    |

| 0x7            | vendor_dependent            |

| 0x8–0xF        | Reserved                    |

## 2.1.2 Asynchronous Receive Data Formats

Asynchronous data is received in the receive FIFO in one of four basic formats:

- 1. 4 Quadlet (used for read requests for data quadlets and write responses)

- 2. 5 Quadlet (used for read requests for block data, write requests for data quadlets, and read responses for data quadlets)

- 3. N Quadlet (used for write requests for data blocks, lock requests and responses, and read responses for data blocks)

- 4. Self-ID Data Packets

#### 2.1.2.1 4-Quadlet Receive Format

These data formats are shown in Figures 2.8 and 2.9. The first quadlet contains the destination node ID and the rest of the packet header information. The second and third quadlets contain the 16-bit source ID and either the 48-bit quadlet-aligned destination offset (used for read requests) or the response code (used for write responses).

#### Figure 2.8 Read Request Receive Format for Data Quadlet

| destinationID        |     | tl rt tcode p         |      |       |  |

|----------------------|-----|-----------------------|------|-------|--|

| sourceID             |     | destinationOffsetHigh |      |       |  |

| destinationOffsetLow |     |                       |      |       |  |

| Reserved             | spd |                       | Rese | erved |  |

#### Figure 2.9 Write Response Packet Receive Format

| destinationID |     | tl          |          | rt | tcode | pri |

|---------------|-----|-------------|----------|----|-------|-----|

| sourceID      |     | rcode       | Reserved |    |       |     |

| Reserved      |     |             |          |    |       |     |

| Reserved      | spd | pd Reserved |          |    |       |     |

The field names and their descriptions are described below.

| pri           |                                                                                                                                                                           | <b>Priority</b><br>This four-bit field is the priority level for the current<br>packet. This field should always be zero.                                         |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| tcode         | This four-bit                                                                                                                                                             | <b>Transaction Code</b><br>This four-bit field is the transaction code for the current<br>packet. The following table lists the valid encoding for this<br>field. |  |  |  |

|               | tcode                                                                                                                                                                     | Description                                                                                                                                                       |  |  |  |

|               | 0100                                                                                                                                                                      | Read Request for Data Quadlet                                                                                                                                     |  |  |  |

|               | 0010                                                                                                                                                                      | Write Response                                                                                                                                                    |  |  |  |

| rt            |                                                                                                                                                                           | field contains the retry code for the current sted in the following table.                                                                                        |  |  |  |

|               | rt                                                                                                                                                                        | Retry Code                                                                                                                                                        |  |  |  |

|               | 01                                                                                                                                                                        | retry_X                                                                                                                                                           |  |  |  |

| tl            |                                                                                                                                                                           | <b>Label</b><br>ts indicate the transaction label for the<br>y are used for tracking requests with                                                                |  |  |  |

| spd           |                                                                                                                                                                           | it field indicates the speed at which the<br>tet was received.                                                                                                    |  |  |  |

|               | spd                                                                                                                                                                       | Speed                                                                                                                                                             |  |  |  |

|               | 000                                                                                                                                                                       | 100 Mbits/s                                                                                                                                                       |  |  |  |

|               | 010                                                                                                                                                                       | 200 Mbits/s                                                                                                                                                       |  |  |  |

|               | 100                                                                                                                                                                       | 400 Mbits/s                                                                                                                                                       |  |  |  |

|               | all others                                                                                                                                                                | Reserved                                                                                                                                                          |  |  |  |

| destinationID | D Destination ID<br>This 16-bit field specifies the destination ID, which is the<br>concatenation of the 10-bit destination bus ID with the<br>6-bit destination node ID. |                                                                                                                                                                   |  |  |  |

| DestinationO  | Destination                                                                                                                                                               | Offset                                                                                                                                                            |  |  |  |

The 48-bit destination offset field is the quadlet-aligned destination address.

| rcode    | <b>Response Code</b><br>This field contains the four-bit response code to an earlier<br>corresponding request. |

|----------|----------------------------------------------------------------------------------------------------------------|

| sourceID | <b>Source ID</b><br>This 16-bit field indicates the node ID and bus ID of the sender.                          |

#### 2.1.2.2 5-Quadlet Receive Format

These data formats are shown in Figures 2.10 through 2.12. The first quadlet contains the destination ID and the rest of the packet header information. The second and third quadlets contain the 16-bit source ID and either the 48-bit quadlet-aligned destination offset (used for read/write requests) or the response code (used for read responses). The fourth quadlet contains either the quadlet data for read responses and quadlet write requests or the data length for the block read request. The last quadlet contains the packet reception status.

#### Figure 2.10 Write Quadlet Request Receive Format

| destinationID        |     | tl                    | rt | tcode | pri |

|----------------------|-----|-----------------------|----|-------|-----|

| sourceID             |     | destinationOffsetHigh |    |       |     |

| destinationOffsetLow |     |                       |    |       |     |

| quadlet_data         |     |                       |    |       |     |

| Reserved             | spd | Reserved              |    |       |     |

#### Figure 2.11 Read Quadlet Response Packet Receive Format

| destinationID th |        | tl      | rt   | tcode    | pri |

|------------------|--------|---------|------|----------|-----|

| sourceID         |        | rcode   |      | Reserved |     |

|                  | Rese   | erved   |      |          |     |

|                  | quadle | et_data |      |          |     |

| Reserved         | spd    |         | Rese | erved    |     |

| destinationID        |  | tl                    | rt   | tcode | pri |  |

|----------------------|--|-----------------------|------|-------|-----|--|

| sourceID             |  | destinationOffsetHigh |      |       |     |  |

| destinationOffsetLow |  |                       |      |       |     |  |

| data_length          |  | Reserved              |      |       |     |  |

| Reserved spd         |  |                       | Rese | erved |     |  |

#### Figure 2.12 Read Block Request Packet Receive Format

The field names and their descriptions are described below.

| pri   | <b>Priority</b><br>This four-bit field is the priority level for the current<br>packet. This field should always be zero. |                                                                                                                                                                   |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| tcode | This four-bi                                                                                                              | <b>Transaction Code</b><br>This four-bit field is the transaction code for the current<br>packet. The following table lists the valid encoding for this<br>field. |  |  |  |

|       | tcode                                                                                                                     | Description                                                                                                                                                       |  |  |  |

|       | 0100                                                                                                                      | Read Request for Data Quadlet                                                                                                                                     |  |  |  |

|       | 0010                                                                                                                      | Write Response                                                                                                                                                    |  |  |  |

| rt    |                                                                                                                           | e<br>t field contains the retry code for the current<br>sted in the following table.                                                                              |  |  |  |

|       | rt                                                                                                                        | Retry Code                                                                                                                                                        |  |  |  |

|       | 01                                                                                                                        | retry_X                                                                                                                                                           |  |  |  |

| tl    |                                                                                                                           | n Label<br>bits indicate the transaction label for the<br>by are used for tracking requests with                                                                  |  |  |  |

Speed

spd

This three-bit field indicates the speed at which the current packet was received.

| spd        | Speed       |

|------------|-------------|

| 000        | 100 Mbits/s |

| 010        | 200 Mbits/s |

| 100        | 400 Mbits/s |

| all others | Reserved    |

#### destinationID Destination ID

This 16-bit field specifies the destination ID, which is the concatenation of the 10-bit destination bus ID with the 6-bit destination node ID.

#### DestinationOffset

#### **Destination Offset**

The 48-bit destination offset field is the quadlet-aligned destination address.

## rcode Response Code

This field contains the four-bit response code to an earlier corresponding request.

#### sourceID Source ID This 16-bit field indicates the no

This 16-bit field indicates the node ID and bus ID of the sender.

#### quadlet\_data Quadlet Data This 32-bit field contains the quadlet data to be transmitted for either a read response or a write request.

### data\_length Data Length

The 16-bit data length field specifies the length of the data block size in bytes for block-data read requests.

#### 2.1.2.3 N-Quadlet Receive Format

These data formats are shown in Figures 2.13 and 2.14. The first quadlet contains the destination ID and the rest of the packet header information. The second and third quadlets contain the 16-bit source ID and either the 48-bit quadlet-aligned destination offset (used for read/write requests) or the response code (used for read/lock responses). The

fourth quadlet contains the data length and the extended transaction code for the block write/read/lock.

The block data, if any, follows the extended code. Block data must be quadlet aligned; that is, there may be appended zeros to the block data for the last quadlet of the data field.

> The EHdr and IHdr bits in the PHT Control and Status Register 0 affect the format of the data written to the DBuf Transmit and Receive FIFOs when EnDMAS is asserted. If IHdr is not set, only the data field portion of the incoming request is written to the DBuf Receive FIFO. If IHdr is set and EHdr is not set, the 1394 header is written to the DBuf Receive FIFO in addition to the data field. If IHdr and EHdr are set, in addition to the 1394 header and data field, a quadlet containing the speed of the received request is written to the DBuf Receive FIFO.

<u>Note:</u> If IHdr and EHdr are set, the format of the data in the DBuf is as shown in Figure 2.13 (Write Request for Data Block Receive Format). The maximum data field size that can be received is the DBuf Receive FIFO size less 20 bytes.

If EHdr is not set, the DBuf Transmit FIFO must contain only the data field for read response packets to be sent in response to received read requests. If EHdr is set, the format followed is that of Figure 2.4 or Figure 2.7.

An appropriate setting for EHdr and IHdr depends on the capability of the external DMA controller.

#### Figure 2.13 Lock/Write Request for Data Block Receive Format

| destinationID        |     | tl                    | rt       | tcode      | pri |

|----------------------|-----|-----------------------|----------|------------|-----|

| sourceID             |     | destinationOffsetHigh |          |            |     |

| destinationOffsetLow |     |                       |          |            |     |

| data_length          |     | extended_tcode        |          |            |     |

| data_field           |     |                       |          |            |     |

|                      |     | pad                   | ding (if | necessary) |     |

| Reserved             | spd |                       | Rese     | erved      |     |

| destinationID | ID tl |                |  | rt | tcode | pri |

|---------------|-------|----------------|--|----|-------|-----|

| sourceID      |       | rcode Reserved |  |    |       |     |

| Reserved      |       |                |  |    |       |     |

| data_length   |       | extended_tcode |  |    |       |     |

| Reserved spd  |       | Reserved       |  |    |       |     |

#### Figure 2.14 Lock/Read Response for Block Data Receive Format

The field names and their descriptions are described below.

| pri   | <b>Priority</b><br>This four-bit field is the priority level for the current<br>packet. This field should always be zero.                                     |                                                                                                                                                   |  |  |

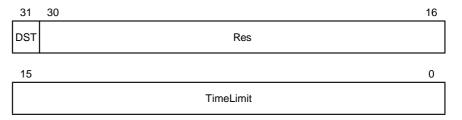

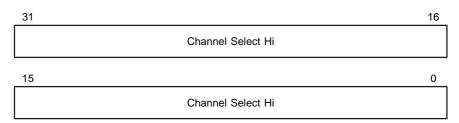

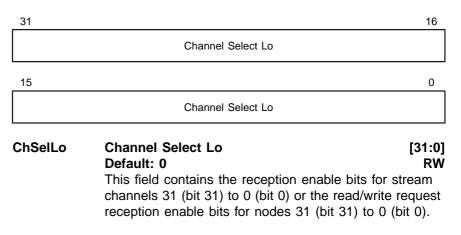

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|