ITD

# 10486

# WHETSTONE®

90 MHz, 32 Bit Microprocessor

- 32 Bit, 30 MIPS MPU

- 33 Ns memory cycle time

- On-chip memory mapping; directly supports up to 1 MB of memory

- Dual data buses for fast RAM access

- ECL internal logic, TTL I/O

- Single +5 volt power supply

- 149 PGA with integral heatsink

- Mature development tools and O.S.

- MIL-STD-883C, Class B and Class S versions can be fabricated as required

## **High Performance**

The 10486 microprocessor provides an unprecedented 90 MHz performance as the result of its ECL implementation. It is designed to directly drive up to one megabyte of high-speed static RAM, providing up to 60 megabytes per second of available memory bandwidth.

## **Applications**

10486 is the solution for power-demanding applications including; CAD, CAM, CAE, ATE, high resolution graphics, optical/voice recognition, AI, imbedded controllers, robotics, realtime synthesis and micromainframes.

# Long Term Solution

Unlike traditional microprocessors, the performance of the 10486 is limited by the speed of memory. As RAM speeds increase, MPU execution speed tracks with it up to 30 million instructions per second (MIPS). Memory cycle time can be as short as RAM access time plus 13 nanoseconds. Designs using the 10486 can be upgraded by the substitution of faster memories.

## **Development Support**

Mature software tools, development systems and a multi-user, multi-tasking O.S. which is optimized for the microprocessor's architecture and written in a compiled high-level development language to ensure efficient, maintainable structured programming. The 10486 supports BASIC, C, COBOL, FORTH, FORTRAN and PASCAL.

# Convenient Packaging

The cavity-down pin grid array (PGA) with integral heat sink provides the shortest thermal path to cool the chip. Because of the low thermal resistance, only conventional air-cooling is necessary. An on-chip thermal diode is externally accessable to allow junction temperature measurement.

Preliminary Specification 5/89

8003-3239 Editor\_\_\_**SA**

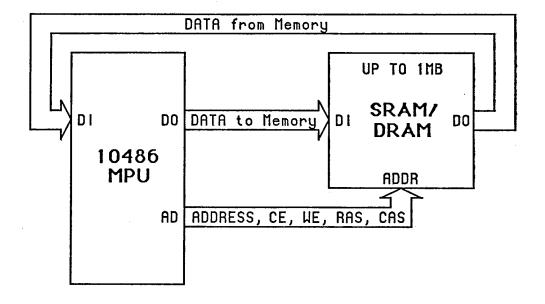

Unique Three-Bus Architecture Directly Drives Memory Chips

## **Absolute Maximum Ratings**

PARAMETER

Supply Voltage

TTL Input Voltage

Power Consumption

MAXIMUM

7.0 V (Vcc-VEE)

5.5 V (Input-VEE)

10 Watts

Operating Temperature -55 °C (ambient) to +125 °C (case)

Operating Junction Temp. +150 °C

Storage Temperature -65 °C to +150 °C

# **Recommended Operating Conditions**

| <u>PARAMETER</u>         | <u>MIN</u> | <u>TYP</u> | <u>MAX</u> | <u>UNIT</u> |

|--------------------------|------------|------------|------------|-------------|

| VCC (VEE=0)              | 4,5        | 5,0        | 5,5        | V           |

| TTL Output Current       | -          | -          | 20         | mΑ          |

| Operating Junction Temp. | -55        | 130        | 150        | °C          |

#### Thermal Characteristics

| PARAME.           | <u>TER</u>   | <u>SYM</u> | <u>TYP</u> | <u>MAX</u> | <u>UNIT</u>                  |

|-------------------|--------------|------------|------------|------------|------------------------------|

| Power Dissipation |              | Pd         | 6,8        | 10         | Watts                        |

| Junction 7        | Temperature  | Tj         | 130        | 150        | °C                           |

| Propagati         | ion Derating | ΔTpd       | -          | 0,37       | % of Max. Tpd/°C of Tj≥130°C |

|                   | Resistance   | Øjc        | 3          | 5          | °C/W (to case only)          |

| #                 | 11.          | Øja        | 21         | 23         | °C/W in still air.           |

| **                | Ħ            | Øja        | 17         | 19         | °C/W @ 100 LFPM              |

| **                | 11           | Øja        | 14         | 16         | °C/W @ 200 LFPM              |

| 11                | 11           | Øja        | 12         | 14         | °C/W @ 300 LFPM              |

| **                | н            | Øja        | 10         | 12         | _                            |

| Ħ                 | #            | Øja        | 8          | 10         | °C/W @ 600 LFPM              |

|                   |              |            | TYP        | W/C        |                              |

| Ambient 7         | Temperature  | Ta         | 14         | -40        | °C @ 100 LFPM                |

| #                 | H            | Ta         | 35         | -10        | °C @ 200 LFPM                |

| **                | **           | Ta         | 48         | +10        | °C @ 300 LFPM                |

| **                | 11           | Ta         | 62         | 30         |                              |

| #                 | н - ·        | Ta         | 76         | 50         | °C @ 600 LFPM                |

|                   |              |            |            |            |                              |

# TTL Input/Output DC Characteristics

| <u>SYM</u> | PARAMETER            | DC TEST CONDITIONS    | <u>MIN</u> | <b>NOM</b> | <u>MAX</u> | <u>UNIT</u> |

|------------|----------------------|-----------------------|------------|------------|------------|-------------|

| VIH        | Input HIGH voltage   | Guaranteed HIGH       | 2,0        | -          | -          | V           |

| VIL        | Input LOW voltage    | Guaranteed LOW        | -          | -          | 0,8        | V           |

| VIK        | Input clamp voltage  | Vcc=Min, IIN = -18mA  | -          | -,8        | 1,2        | ٧           |

| Vон        | Output HIGH voltage  | Vcc=Min, IoH= -1mA    | 2,7        | 3,4        |            | ٧           |

| Vol        | Output LOW voltage   | Vcc=Min, loL=4mA      | -          | -          | 0,4        | V           |

|            |                      | Vcc=Min, loL =20mA    | -          | -          | 0,5        | ٧           |

| loz        | Output OFF current   | Vcc=Max, 0.4≤Vouт≤2.4 | -50        | -          | 50         | μΑ          |

| 11H        | Input HIGH current   | Vcc=Max, Vin=2.7V     | -          | -          | 50         | μΑ          |

| lı         | Input HIGH current   | Vcc=Max, Vin =5.5V    | -          | •-         | 1,0        | mA          |

| liL        | Input LOW current    | Vcc=Max, Vin =0.5V    | -          | -          | -0,4       | mΑ          |

| los        | Output short current | Vcc≟Max, Vouт=0V      | -25        | -          | -100       | mΑ          |

| lα         | Supply current       | Vcc=Max               | -          | 1355       | 1900       | mΑ          |

50E D

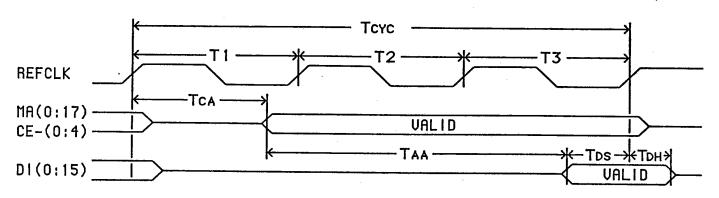

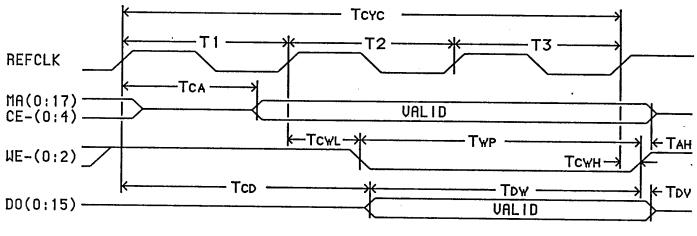

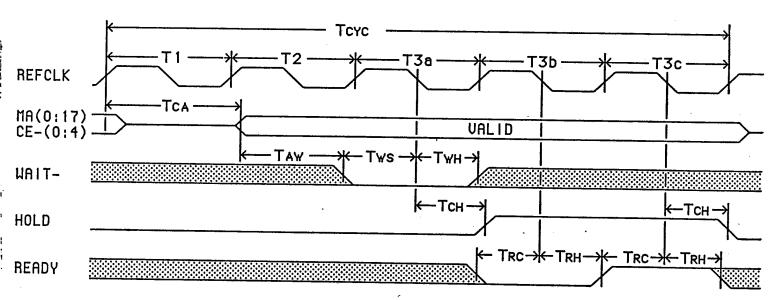

AC Characteristics: MEMORY CYCLE TIMING (0°C≤Ta≤70°C; Tj≤130°C)

| <u>SYM</u>  | <u>PARAMETER</u>                               | <u>MIN</u> | <u>TYP</u> | <u>MAX</u> | <u>UNIT</u> |

|-------------|------------------------------------------------|------------|------------|------------|-------------|

| <b>fMAX</b> | Maximum Clock frequency                        | 90         | -          | -          | MHz         |

| Tclk        | Clock Cycle                                    | 11         | -          | -          | ns          |

| Tcyc        | Memory Cycle (limited by TAA)                  | 33         | -          | -          | ns          |

| TCA         | Clock high to valid Address                    | -          | 8          | 11         | ns          |

| TAA*        | Memory Access Time from Address                | 20         | -          | -          | ns          |

|             | TAA=TCYC-TCAmax-TDSmin=TCYC-10ns               |            |            |            |             |

| Tcwl.       | Clock to Write Enable low                      | -          | -          | 7          | ns          |

| Town        | Clock to Write Enable high                     | 5          | -          | . •        | ns          |

| Twp*        | Write Enable pulse width                       | . 20       | -          | -          | ns          |

|             | TWP=2TCLK-TCWLmax+TCWHmin                      |            |            | ٠          |             |

| Too         | Clock to Data Out valid                        | -          | 15         | 20         | ns          |

| Tow*        | Data Out valid to end of Write Enable          | 10         | -          | -          | ns          |

|             | TDW=TCYC-TCDmax+TCWHmin                        |            |            |            |             |

| Tov         | Data Out valid after end of Write Enable       | 0          | -          | -          | ns          |

| Tos         | Data Input setup to Clock                      | 2          | -          | -          | ns          |

| Тон         | Data Input hold after Clock                    | . 0        | -          | -          | ns          |

| Tah         | Address hold after end of Write Enable         | 0          | -          | -          | ns          |

| Taw*        | Valid Address to Wait- Low                     | -          | -          | 10         | ns          |

|             | TAW=2.5TCLK-TCAmax-TWSmin                      |            |            |            | ,           |

| Tws         | Wait- Setup to Clock                           | 2          | _          | -          | ns          |

| Twn         | Wait- Hold time after Clock                    | 0          | -          | -          | ns          |

| Тан         | Clock Low to Hold                              | -          | _          | 9          | ns          |

| TRC         | Ready Setup to Clock <sup>†</sup>              | 2          | -          | -          | ns          |

| TRH         | Ready Hold time after Clock <sup>†</sup>       | Ò          | _          | -          | ns          |

| ΔTCL        | Derating of all outputs for capacitive loading | -          | 72         | -          | ps/pf       |

|             |                                                |            |            |            |             |

†Note: Ready can be asynchronous.

\*Note: Assumes Tcyc=25 ns.

Note: Refclk is an internal clock that is for reference only.

# Memory Read Timing

# Memory Write Timing

Delayed Memory Cycle Timing

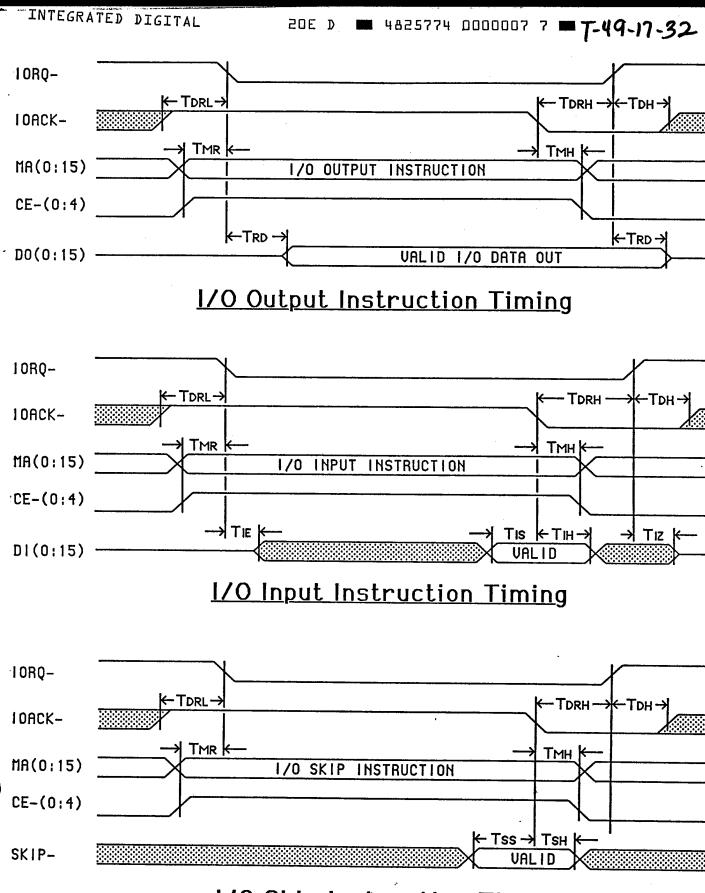

# AC Characteristics: PROGRAMMED I/O INSTRUCTIONS (0°C≤Ta≤70°C; Tj≤130°C)

| SYM  | PARAMETER                                   | MIN | <u>TYP</u> | <u>MAX</u> | <u>UNIT</u> |

|------|---------------------------------------------|-----|------------|------------|-------------|

| TDRL | I/O Acknowledge to I/O Request (Min=Tcyc)   | 33  | -          | -          | ns          |

| TORH | I/O Acknowledge to I/O Request              | 33  | -          | 80         | ns          |

| TMR  | Instruction valid prior to I/O Request      | 15  | 33         | -          | ns          |

| Тмн  | Instruction valid after I/O Acknowledge     | 10  | 33         | -          | ns          |

| TDH  | I/O Acknowledge Hold time after I/O Request | 0   | -          | -          | ns          |

| TRD  | I/O Request to Data Out                     | 0   | 6          | 10         | ns          |

| TIE  | I/O Request to Data In Enabled              | 0   | -          | -          | ns          |

| Tis  | Data In setup to I/O Acknowledge Low        | 10  |            | -          | ns          |

| TIH  | Data In hold after I/O Acknowledge Low      | 40  | -          | -          | ns          |

| Tız  | I/O Request to Data In Disabled             | 0   | -          | 10         | ns          |

| Tss  | I/O Skip setup to I/O Acknowledge High      | 10  | . **       | -          | ns          |

| Тѕн  | I/O Skip hold after I/O Acknowledge High    | 40  |            | -          | ns          |

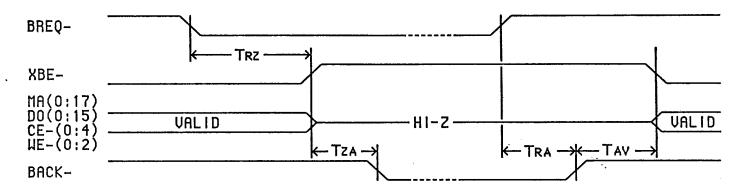

AC Characteristics: <u>DIRECT MEMORY ACCESS</u> (0°C≤Ta≤70°C; Tj≤130°C)

| <u>SYM</u> | PARAMETER PARAMETER                 | <u>MIN</u> | <u>TYP</u> | <u>MAX</u> | <u>UNIT</u> |

|------------|-------------------------------------|------------|------------|------------|-------------|

| TRZ        | Bus Request to High Impedance Buses | 33         | -          | 80         | ns          |

| Tza        | Buses released to Bus Acknowledge   | 10         | -          | 33         | ns          |

| TRA        | Bus Request to Bus Acknowledge      | 75         | -          | 105        | ns          |

| TAV        | Bus Acknowledge to Buses Active     | 33         | -          | 80         | ns          |

# Signal Descriptions: PROCESSOR INTERFACE

| FIGUESSON COMMON AND CLARC CHANGS | Processor | Control | and | State | Signals |

|-----------------------------------|-----------|---------|-----|-------|---------|

|-----------------------------------|-----------|---------|-----|-------|---------|

| RST-        | ı | 1B    | Processor power-up reset                                 |

|-------------|---|-------|----------------------------------------------------------|

| STOP-       | 1 | 2C    | Switch input to force execution into shadow memory       |

| HALT-       | 1 | 2D    | Forces execution into shadow memory for Halt instruction |

| TRAP        | 1 | 1H    | Extended instruction set trap enable                     |

| CLKI, CLKI- | 1 | 1E,2E | ECL level balanced clock inputs                          |

| RUN-        | 0 | 10B   | Processor run indicator (not executing in shadow)        |

| VBB         | Ó | 1G    | External ECL reference voltage                           |

| CARRY       | Ŏ | 2N    | Carry flip-flop state                                    |

|             |   |       | •                                                        |

External Programmed I/O Handshake

| IORQ-  | Ω   | 9B | External programmed I/O instruction   |

|--------|-----|----|---------------------------------------|

|        | ·   |    | Programmed I/O instruction completed  |

| IOACK- | 1   | 8A | · · · · · · · · · · · · · · · · · · · |

| SKIP-  | - [ | 9A | Programmed I/O skip condition         |

Processor Interrupt

| INT-  | l | 13C | Interrupt request (asynchronous) |

|-------|---|-----|----------------------------------|

| DINT- | 1 | 14E | Disable interrupt strobe         |

| INTD- | 0 | 10A | Interrupt disable strobe         |

1/0 Skip Instruction Timing

# Signal Descriptions: MEMORY INTERFACE

| Memory Driving | <u>ıa Siar</u> | nals             | •                                                       |

|----------------|----------------|------------------|---------------------------------------------------------|

| DI(0:15)       | . 1            |                  | Data input from memory                                  |

| DO(0:15)       | 0              |                  | Data output to memory                                   |

| MA(0:17)       | 0              |                  | Memory, I/O address output                              |

| CEÒ-, CÉ1-     | 0              | 14C,K            | 64K SRAM chip enable, page 0, 1                         |

| CE2-, CE3-     | 0              | 14L,M            | 256K SRAM chip enable, page 0, 1                        |

| CE4-           | 0              | 14N              | Shadow RAM/ROM chip enable                              |

| WE0-, WE1-     | 0              | 14G,H            | Write enable, RAM page 0, 1                             |

| WE2-           | 0              | 14J <sup>′</sup> | Shadow RAM write enable                                 |

| RAS-           | O              | 1K               | DRAM row address strobe                                 |

| CAS-           | Ö              | 3C               | DRAM column address strobe                              |

| XBE-           | Ö              | 2F               | External buffer enable (memory drivers)                 |

|                | _              |                  |                                                         |

| Memory Mapp    | ina            |                  |                                                         |

| MAP(0:7)       | ī              |                  | Mapped page selects (0:3, 4:7)                          |

| MAPE-          | i              | 10R              | Mapping enable strobe                                   |

| MAPD-          | i              | 10P              | Mapping disable strobe                                  |

| LA15           | Ö              | 13L              | Unmapped address bit 15                                 |

|                | _              | , , , _          |                                                         |

| Asynchronous   | Mem            | orv Hands        | sha <u>ke</u>                                           |

| WAIT-          | ı              | 8B               | Delayed memory cycle request                            |

| HOLD           | 0              | 7A               | Memory cycle suspended                                  |

| READY          | Ī              | 7B               | Continue suspended memory cycle (asynchronous)          |

| .,_,           |                |                  |                                                         |

| Direct Memory  | Acce           | ss Hands         | <u>hake</u>                                             |

| BREQ-          | 1              | 6A               | DMA request (asynchronous)                              |

| BACK-          | Ö              | 6B               | DMA acknowlege (outputs disabled)                       |

|                |                |                  |                                                         |

| Miscellaneous  | Sign           | als              |                                                         |

| TP(0:3)        | O              |                  | Internal test points - do not use                       |

| ANOD'          | X              | 1 N              | Anode of thermal diode                                  |

| CATH           | X              | 1P               | Cathode of thermal diode                                |

| GND            | X              |                  | System ground                                           |

| +5V            | X              |                  | System +5 volt power supply                             |

| N/C            | X              |                  | Not internally connected pins - reserved for future use |

DMA Handshake Timing

#### 10486 PINOUTS

|     | A      | В     | С             | D     | E     | F    | G    | H    | J    | K    | L    | M    | N     | P     | R     |    |

|-----|--------|-------|---------------|-------|-------|------|------|------|------|------|------|------|-------|-------|-------|----|

| 15  |        | MA17  | MA0           | MA1   | MA2   | МАЗ  | N/C  | MA4  | MA5  | MA6  | MA7  | GND  | N/C   | GND   |       | 15 |

| 1.4 | DO0    | N/C   | CE0-/<br>MA16 | GND   | DINT- | GND  | WE0- | WE1- | WE2- | CE1- | CE2- | CE3- | CE4-  | DI4   | DO4   | 14 |

| 13  | DO1    | DI0   | INT-          | N/C   | N/C   | +5V  | +5V  | GND  | GND  | +5V  | LA15 | NC   | GND   | DI5   | DO5   | 13 |

| 1 2 | DO2    | DI1   | N/C           |       | GND   |      |      |      |      |      | +5 V |      | N/C   | N/C   | DO6   | 12 |

| 11  | DO3    | DI3   | DI2           | GND   |       |      |      |      |      |      |      | GND  | DI6   | DI7   | DO7   | 11 |

| 10  | INTD-  | RUN-  | +5V           |       |       |      |      |      | ٠    |      |      | •    | GND   | MAPD- | MAPE- | 10 |

| 9   | SKIP-  | IORQ- | GND           |       |       |      |      |      |      |      |      |      | +5V   | MAP0  | MAP1  | 9  |

| 8   | IOACK- | WAIT- | GND           |       |       |      |      |      |      |      |      |      | GND   | MAP2  | МАРЗ  | 8  |

| 7   | HOLD   | READY | + 5 V         |       |       |      |      |      |      |      |      |      | GND   | MAP4  | MAP5  | 7  |

| 6   | BREQ-  | BACK- | GND           |       |       |      |      |      |      |      |      |      | +5V   | MAP6  | MAP7  | 6  |

| 5   | DO8    | DI8   | N/C           | GND   |       |      |      |      |      |      |      | GND  | N/C   | DI12  | DO12  | 5  |

| . 4 | DO9    | DI9   | N/C           | N/C   | +5V   |      |      |      |      |      | GND  |      | N/C   | DI13  | DO13  | 4  |

| 3   | DO10   | DI10  | CAS-          | TP0   | TP1   | +5V  | GND  | GND  | +5V  | +5V  | TP2  | TP3  | GND   | DI14  | DO14  | 3  |

| 2   | DO11   | DI11  | STOP-         | HALT- | CLKI- | XBE- | MA10 | MA8  | MA12 | MA13 | MA14 | MA15 | CARRY | DI15  | DO15  | 2  |

| 1   |        | RST-  | MA11          | MA9   | CLKI  | GND  | VBB  | TRAP | GND  | RAS- | GND  | GND  | ANOD  |       |       | 1  |

|     | A      | В     | С             | D     | E     | F    | G    | Н    | J    | K .  | L    | M    | N     | P     | R     |    |

# PC BOARD COMPONENT-SIDE VIEW

#### 10486 Instruction Set

The 10486 microprocessor is a 32 bit machine; instructions are 16 or 32 bits long and data is addressed on 16-bit "word" boundaries. There is no native byte addressing, only word addressing. Arithmetic instructions provide a "byte swap" function for byte manipulation. The processor has four programmable registers (R0-R3), a carry flip-flop (CY) and a program counter (PC). These registers comprise all of the processor context other than external memory mapping.

The logical address space is 64K words (2<sup>16</sup>), or 128K bytes. The physical address space can be expanded to one megabyte using the on-chip memory mapping logic, or to any size using external mapping logic. The MPU has a Von Neumann architecture permitting instructions and data to be intermixed freely within memory under software control.

The 10486 is designed to support an I/O bus that is separate from the memory bus. This was implemented because of the significant speed disparity between very-high-speed memory and slow I/O devices. The MPU does not actually execute I/O instructions by itself, but rather hands them off to an external automaton which can control an I/O bus at the prescribed speed. As a result of having a separate I/O automaton the I/O execution time can often parallel other MPU instruction execution. This allows the MPU to continue further program execution during relatively slow I/O bus transfers.

The 10486 instruction set is designed for maximum performance and simplicity. There are three basic instruction types; memory reference, arithmetic-logic and PIO (programmed input and output). The instructions are described below by type.

# 1.1 Memory Reference Instructions

The eight memory reference instructions provide the only program access to main memory. They function as follows:

- JMP Directs program execution to the specified address, which changes PC.

- JSR Same as JMP, but also saves the return address in R3. The return address is the location after the JSR instruction.

- INC Adds one to the value stored at the specified absolute address. No registers are altered by this instruction.

- ISZ Increment and Skip if Zero; adds one to the value stored at the specified address and skips the next instruction if the resulting value is zero. No registers are altered by this instruction.

- DEC Subtracts one from the value stored at the specified absolute address. No registers are altered by this instruction.

- DSZ Decrement and Skip if Zero; subtracts one from the value stored at the specified address and skips the following instruction if the resulting value is zero. No registers are altered by this instruction.

- LDA Loads the specified register (R0-R3) with the value stored at the specified address in memory.

## 1.1 Memory Reference Instructions (cont.)

STA Stores the value of the specified register (R0-R3) into the specified address in memory.

#### PRIMARY ADDRESSING

In all memory reference instructions, the primary address is specified by the mode bits 6 and 7, plus the displacement field, as explained below:

- ZP Zero-page addressing; the 8 bit address field specifies an address between zero and 255<sub>10</sub> (377<sub>8</sub>).

- REL Relative addressing; the displacement field specifies a signed value from -128<sub>10</sub> to +127<sub>10</sub> (-200<sub>8</sub> to +177<sub>8</sub>) which is added to the value in PC to produce an effective address.

- R2 Indexed addressing; adds the signed displacement (-128 to +127) to the value in register 2 to produce an effective address.

- R3 Indexed addressing; adds the signed displacement (-128 to +127) to the value in register 3 to produce an effective address.

#### **INDIRECT ADDRESSING**

In memory reference instructions the indirect bit (5) indicates that the primary address points to an indirect address rather than directly to the data. The indirect address in turn points to the actual data to be accessed. All indirect addresses are 16 bit absolute.

#### <u>AUTO-INCREMENT & DECREMENT CELLS</u>

The processor provides automatic increment cells at Zero-page locations 20-27, and automatic decrement cells at locations 30-37. These cells are incremented or decremented by one when specified as an indirect address in a memory reference instruction. When accessed, the value in an "automatic" cell is read and modified, then used as an indirect address. These cells are only recognized when accessed using absolute (base page) indirect addressing. Relative and indexed indirect addressing of these cells does <u>not</u> modify them.

#### SELF-MODIFYING CODE

Supporting self-modifying code in a pipelined MPU provides important compatibility to the Von Neumann philosophy. The 10486 supports software that modifies itself using any addressing mode (e.g. relative addressing of PC+1). When the program modifies an instruction that is already loaded in the pipeline, the processor recognizes the instruction address and reloads the pipe at the same time as the memory location is changed. This can occur with STA, ISZ and DSZ instructions because they modify memory.

#### 1.2 Arithmetic Instructions

Arithmetic instructions combine functions of one or two registers with shifting, carry control and test branching. The functions are:

- ADC Adds the compliment of the value in the source register to the value in the destination register and stores the result into the destination register.

- ADD Adds the value in the source register to the value in the destination register and stores the sum into the destination register.

- AND Performs a logical AND (bit by bit) between the value in the source register and the value in the destination register and stores the result into the destination register.

- INC Increments the value of the source register and stores it into the destination register.

- MOV Moves the value from the source register into the destination register.

- NEG Negates the value of the source register and stores it into the destination register.

- NOT Logical inverse of the value of the source register and stores it into the destination register (logical invert).

- SUB Subtracts the value in the source register from the value in the destination register and stores the difference into the destination register.

#### SHIFT

The shift field, bits 8 and 9, allows the result of any arithmetic function to be shifted before it is stored into the destination register and the carry flip/flop. The choices are:

- No shift.

- L Shift left one bit through carry.

- R Shift right one bit through carry.

- S Swap bytes within the word, no effect on carry.

#### CARRY

The carry field (bits 10 and 11) controls the *next state* of the carry flip-flop during an arithmetic function. In addition, if an arithmetic function causes a carry-out, it will complement the carry state specified by this field. The resulting value will then be stored into the carry flip-flop, unless a shift or no-load option is specified. The four choices are:

- Leave carry as it is.

- Z Clear carry to zero.

- O Set carry to one.

- C Complement carry's present value.

# 1.2 Arithmetic Instructions (cont.)

#### NO LOAD

The no-load bit (12) prevents the result of any arithmetic instruction from being stored into the destination register or the carry flip-flop. It is often used to perform non-destructive tests in conjunction with the skip function below.

#### SKIP

The skip field (bits 13-15) permits skipping the next instruction based on the resulting data or carry; after the arithmetic function, shifting and carry control have been performed. The eight options include:

-- Do not skip. SKP Always skip.

SZC Skip if the carry result is zero.

SNC Skip if the carry result is one.

SZR Skip if the data result is zero.

SNR Skip if the data result is not zero.

SEZ Skip if either the data or carry result is zero.

SBN Skip if both the data and carry results are not zero.

# 1.3 Programmed Input/Output

The eight PIO instructions provide the only program access to the I/O devices. The MPU provides 256 I/O device addresses from the eight least-significant bits of the instruction. In addition, the instructions imply the selection of a register within any I/O device. Bits 9 and 10 can be used as an extension of the I/O address if required, with the exception of the SKP instruction. Bit 8 generally determines whether it is an input or output instruction (except SKP which does not alter any register).

The MPU does not actually execute I/O instructions by itself, it expects an external automaton to control the interface and timing to any I/O devices. The MPU puts the actual instruction onto the MA bus and asserts IORQ to initiate the external I/O logic control of the I/O transfer. When completed external logic must assert IOACK.

The I/O instructions are as follows:

- DOA Transfers data from the specified register to the A register of the specified I/O device.

- DIA Transfers data from the A register on the specified I/O device to the specified register.

- DOB Transfers data from the specified register to the B register of the specified I/O device.

- DIB Transfers data from the B register on the specified I/O device to the specified register.

# 1.3 Programmed Input/Output (cont.)

- DOC Transfers data from the specified register to the C register of the specified I/O device.

- DIC Transfers data from the C register on the specified I/O device to the specified register.

- DOD Transfers data from the specified register to the C register of the specified I/O device.

- SKP Selectively skips the following instruction depending on the SKIP input to the MPU. No registers are modified.

Note: It is the responsibility of external logic to assert the SKIP input only during PIO instructions in which you want a skip function. It will cause an instruction skip when asserted during any PIO.

# 1.4 Programmed MPU Control

We recommend that a an I/O address be reserved for MPU control. The following list provides an overview of useful MPU control functions. They may be implemented in a variety of ways using I/O instructions that are convenient to your application.

Halt, branch into shadow memory.

Software interrupt.

Read/write the interrupt mask.

Enable/disable interrupts.

Read/write the map word.

Clear all I/O devices.

Skip if interrupts are enabled/disabled.

Skip if a power failure is detected.

# 2.0 Memory Mapping

The 10486 provides an extremely fast internal memory map to allow access to up to one megabyte of memory without external logic. This method can be externally extended to provide fast access to a larger memory area. Alternately any other memory mapping method can be implemented externally as required by the application.

## 2.1 Internal Memory Mapping

The 10486 provides onchip memory mapping that provides program access to any size main memory. Memory is divided into 64 KB physical pages. The MPU can access any two 64 KB pages of memory at a time. Because of the memory mapping provided on the 10486 there is no speed penalty to directly access up to 1 MB (one megabyte) of main memory. The 10486 provides the chip enable strobes (CE-), write enable strobes (WE-) and addresses (MA) to access up to 1 MB of 64K or 256K static RAMs. It also provides the RAS- and CAS- strobes to access dynamic RAMs.

## 2.2 External Memory Mapping

The LA15 output signal can be used as a selector to extend the internal memory mapping scheme to access over one megabyte of memory. There is a speed penalty when accessing over one megabyte of static RAM. There is generally no penalty when accessing slower dymanic RAM.

When a PIO instruction changes the external map register so that it maps-out the executing memory page (the page that the PIO instruction was fetched from), the very-next instruction is already in the pipe, and will be executed next. That instruction's memory reference and all subsequent instructions will be read from the newly mapped-in page. Example: the I/O instruction (which changes the map) followed by a JMP @60 will change the map, then jump to the address stored in location 60 of the newly selected page. If the MPU map is disabled (following an interrupt) the program can change the map word, but mapping will not take effect again until after it is reenabled.

# 3.1 Processor Interrupts

The INT- input to the 10486 is a non-maskable interrupt to the MPU, but may be masked externally as required. Traditionally this is done using PIO instructions.

When an interrupt occurs the MPU map is internally disabled, forcing the MPU to access physical pages zero and one. The address of the next instruction that would have been executed is stored at location zero in physical page zero in memory. The interrupt vector is read from location one in physical page zero. Program execution resumes at the location specified by the interrupt vector and further interrupts are ignored until interrupts are reenabled, typically by a specific PIO instruction.

The external map register can be read and saved or rewritten at any time whether mapping is enabled or disabled. If the MPU map selects other than page zero & one when mapping is reenabled, the next instruction will be executed; but its memory reference and any subsequent instructions will reference the newly mapped-in page(s).

**DEFINITIONS:**

#### **10486 INSTRUCTION SET**

| R<br>I<br>AA<br>±AA<br>AAAA<br>XX | CPU register 0, 1, 2, or 3 CPU register 2 or 3; used as ar an 8 bit memory address or I/O an 8 bit signed displacement (a 16 bit absolute memory addressed don't care | address<br>-128 to +127)                                    |                                                             |                                          |                  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------|------------------|

| ADC                               | Add logical compliment<br>ADDRESSING MODE<br>REGISTER-TO-REGISTER                                                                                                     | MNEMONIC<br>ADC R,R                                         | OP CODE<br>84XX                                             | BYTES<br>2                               | CYCLES<br>1      |

| ADD                               | Binary Addition<br>ADDRESSING MODE<br>REGISTER-TO-REGISTER                                                                                                            | MNEMONIC<br>ADD R,R                                         | <i>OP CODE</i><br>86XX                                      | BYTES<br>2                               | CYCLES<br>1      |

| AND                               | Logical AND<br>ADDRESSING MODE<br>REGISTER-TO-REGISTER                                                                                                                | MNEMONIC<br>AND R,R                                         | <i>OP CODE</i><br>87XX                                      | BYTES<br>2                               | CYCLES<br>1      |

| DEC                               | Decrement memory ADDRESSING MODE MEMORY ABSOLUTE                                                                                                                      | MNEMONIC<br>DEC AAAA                                        | OP CODE<br>1D01                                             | BYTES<br>4                               | CYCLES<br>4      |

| DI-                               | Input from I/O device ADDRESSING MODE I/O ADDRESS I/O ADDRESS I/O ADDRESS *Note: Number of cycles for I/O                                                             | MNEMONIC DIA R,AA DIB R,AA DIC R,AA D depends upon          | OP CODE<br>61XX<br>63XX<br>65XX<br>external I/O tim         | BYTES<br>2<br>2<br>2<br>2<br>sing.       | CYCLES           |

| DO-                               | Output to I/O device ADDRESSING MODE I/O ADDRESS I/O ADDRESS I/O ADDRESS I/O ADDRESS *Note: Number of cycles for I/O                                                  | MNEMONIC DOA R,AA DOB R,AA DOC R,AA DOD R,AA D depends upon | OP CODE<br>60XX<br>62XX<br>64XX<br>66XX<br>external I/O tim | BYTES<br>2<br>2<br>2<br>2<br>2<br>iing.  | CYCLES           |

| DSZ                               | Decrement and Skip if Zero res<br>ADDRESSING MODE<br>BASE PAGE<br>PROGRAM RELATIVE<br>INDEXED RELATIVE<br>BASE PAGE INDIRECT<br>RELATIVE INDIRECT<br>INDEXED INDIRECT | MNEMONIC DSZ AA DSZ .±AA DSZ ±AA,I DSZ @AA DSZ @.±AA        | OP CODE<br>18XX<br>19XX<br>1AXX<br>1CXX<br>1DXX             | BYTES<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | CYCLES 3 3 4 4 4 |

## **10486 INSTRUCTION SET**

| INC | Add one (Increment)  ADDRESSING MODE  REGISTER-TO-REGISTER  MEMORY ABSOLUTE                                                                          | MNEMONIC<br>INC R,R<br>INC AAAA                                                         | <i>OP CODE</i><br>83XX<br>1501                                  | BYTES<br>2<br>4                               | CYCLES<br>1<br>4       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------|------------------------|

| ISZ | Increment and Skip if Zero result ADDRESSING MODE BASE PAGE PROGRAM RELATIVE INDEXED RELATIVE BASE PAGE INDIRECT RELATIVE INDIRECT INDEXED INDIRECT  | IIIT MNEMONIC<br>ISZ AA<br>ISZ .±AA<br>ISZ ±AA,I<br>ISZ @AA<br>ISZ @.±AA<br>ISZ @±AA,I  | OP CODE<br>10XX<br>11XX<br>12XX<br>14XX<br>15XX<br>16XX         | BYTES<br>2<br>2<br>2<br>2<br>2<br>2<br>2      | CYCLES 3 3 4 4 4       |

| JMP | Jump (program branch) ADDRESSING MODE BASE PAGE PROGRAM RELATIVE INDEXED RELATIVE BASE PAGE INDIRECT RELATIVE INDIRECT INDEXED INDIRECT ABSOLUTE     | MNEMONIC JMP AA JMP .±AA JMP ±AA,I JMP @AA JMP @.±AA JMP @±AA,I JMP @AA                 | OP CODE<br>00XX<br>01XX<br>02XX<br>04XX<br>05XX<br>06XX<br>0501 | BYTES 2 2 2 2 2 2 4                           | CYCLES 2 2 2 3 3 3     |

| JSR | Jump to Subroutine (save reture ADDRESSING MODE BASE PAGE PROGRAM RELATIVE INDEXED RELATIVE BASE PAGE INDIRECT RELATIVE INDIRECT INDEXED INDIRECT    | n address in R3)  MNEMONIC  JSR AA  JSR .±AA  JSR ±AA,I  JSR @AA  JSR @.±AA  JSR @±AA,I | OP CODE 08XX 09XX 0AXX 0CXX 0DXX 0EXX                           | BYTES<br>2<br>2<br>2<br>2<br>2<br>2<br>2      | CYCLES 2 2 2 3 3 3 3 3 |

| LDA | Load register from memory ADDRESSING MODE BASE PAGE PROGRAM RELATIVE INDEXED RELATIVE BASE PAGE INDIRECT RELATIVE INDIRECT INDEXED INDIRECT ABSOLUTE | MNEMONIC LDA R,AA LDA R,±AA LDA R,#AA,I LDA R,@AA LDA R,@.±AA LDA R,@±AA,I LDA R,AAAA   | OP CODE<br>20XX<br>21XX<br>22XX<br>24XX<br>25XX<br>26XX<br>2501 | BYTES<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>4 | CYCLES 2 2 2 3 3 3 3   |

| MOV | Move word  ADDRESSING MODE  REGISTER-TO-REGISTER                                                                                                     | <i>MNEMONIC</i><br>MOV R,R                                                              | OP CODE<br>82XX                                                 | BYTES<br>2                                    | CYCLES<br>1            |

#### 10486 INSTRUCTION SET

| NEG                                        | Negate (twos compliment)  ADDRESSING MODE  REGISTER-TO-REGISTER                                                                                                                                                                                   | MNEMONIC<br>NEG R,R                                                                           | OP CODE<br>81XX                                                         | BYTES<br>2                                         | CYCLES<br>1                                                                                                                          |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| NOT                                        | Logical invert<br>ADDRESSING MODE<br>REGISTER-TO-REGISTER                                                                                                                                                                                         | MNEMONIC<br>NOT R,R                                                                           | OP CODE<br>80XX                                                         | BYTES<br>2                                         | CYCLES<br>1                                                                                                                          |  |

| SKP                                        | Skip on I/O condition  ADDRESSING MODE I/O ADDRESS *Note: Number of cycles for I/O                                                                                                                                                                | <i>MNEMONIC</i><br>SKP AA<br>depends upon e                                                   | <i>OP CODE</i><br>67XX<br>xternal I/O tim                               | BYTES<br>2<br>ning.                                | CYCLES                                                                                                                               |  |

| STA                                        | Store register into memory ADDRESSING MODE BASE PAGE PROGRAM RELATIVE INDEXED RELATIVE BASE PAGE INDIRECT RELATIVE INDIRECT INDEXED INDIRECT ABSOLUTE                                                                                             | MNEMONIC<br>STA R,AA<br>STA R,±AA,I<br>STA R,@AA<br>STA R,@.±AA<br>STA R,@±AA,I<br>STA R,AAAA | OP CODE<br>40XX<br>41XX<br>42XX<br>42XX<br>44XX<br>45XX<br>46XX<br>4501 | BYTES<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>4 | CYCLES 2 2 2 3 3 3                                                                                                                   |  |

| SUB                                        | Subtract ADDRESSING MODE REGISTER-TO-REGISTER                                                                                                                                                                                                     | MNEMONIC<br>SUB R,R                                                                           | OP CODE<br>85XX                                                         | BYTES<br>2                                         | CYCLES<br>1                                                                                                                          |  |

| REGISTER-TO-REGISTER INSTRUCTION MODIFIERS |                                                                                                                                                                                                                                                   |                                                                                               |                                                                         |                                                    |                                                                                                                                      |  |

| SKIP                                       | FUNCTION SKIP NEXT INSTRUCTION SKIP IF CARRY IS ZERO SKIP IF CARRY IS ONE SKIP IF RESULT IS ZERO SKIP IF RESULT IS NOT ZERO SKIP IF RESULT OR CARRY=0 SKIP IF RESULT & CARRY=0 TEST ONLY - without modifying the registers or the carry flip-flop | SBN<br>#                                                                                      | OP CODE XXX1 XXX2 XXX3 XXX4 XXX5 XXX6 XXX7 XXX8                         | (XXXX)<br>(XXXX)<br>(XXXX)<br>(XXXX)<br>(XXXX)     | ARY OP CODE)  XXXX.XXXX.X001)  XXXX.XXXX.X010)  XXXX.XXXX.X100)  XXXX.XXXX.X101)  XXXX.XXXX.X111)  XXXX.XXXX.X111)  XXXX.XXXXX.X111) |  |

| CARRY                                      | FUNCTION PRE-ZERO CARRY PRESET CARRY PRE-COMPLIMENT CARRY                                                                                                                                                                                         | MNEMONIC<br>Z<br>O<br>C                                                                       | OP CODE<br>XX1X<br>XX2X<br>XX3X                                         | (XXXX.                                             | ARY OP CODE)<br>XXXX.XX01.XXXX)<br>XXXX.XX10.XXXX)<br>XXXX.XX11.XXXX)                                                                |  |

| ROTATE                                     | FUNCTION<br>ROTATE LEFT THRU CARRY<br>ROTATE RIGHT THRU CARRY<br>SWAP TWO BYTES IN WORD                                                                                                                                                           | MNEMONIC<br>L<br>R<br>S                                                                       | OP CODE<br>XX4X<br>XX8X<br>XXCX                                         | (XXXX.<br>(XXXX.                                   | ARY OP CODE)<br>XXXX.01XX.XXXX)<br>XXXX.10XX.XXXX)<br>XXXX.11XX.XXXX)                                                                |  |