# Preliminary DATA SHEET

# 439C Sub-Band Decoder

#### **FEATURES**

- 64 x 8-bit input FIFO memory buffer

- 64 x 8-bit output FIFO memory buffer

- Decodes 16 kb/s or 24 kb/s

- 1.67 MHz maximum parallel input data rate

- Input FIFO and output FIFO flags

- Serial data access to DSP, bypassing input FIFO

- TTL-compatible inputs and outputs

- FCC part 68.308 protection circuitry

- Multichannel operation under host control

- μ-law 64 kb/s PCM speech output

- Supports AT&T Voice Store and Forward Standards

#### DESCRIPTION

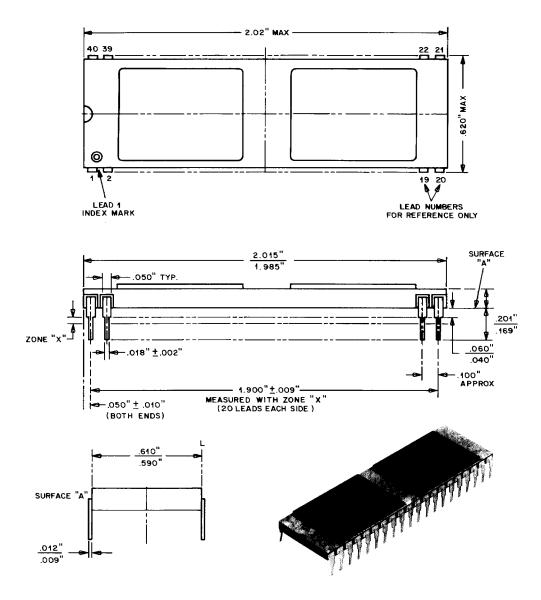

The 439C Sub-Band Decoder is a single-package integrated circuit. The device combines a CMOS memory buffer and a WE® DSP20 Digital Signal Processor (DSP) in a single dual-cavity ceramic 40-pin DIP. It is capable of producing high quality speech at either 16 kb/s or 24 kb/s under the control of a channel-encoded token. The 439C Sub-Band Decoder requires a single 5 V supply.

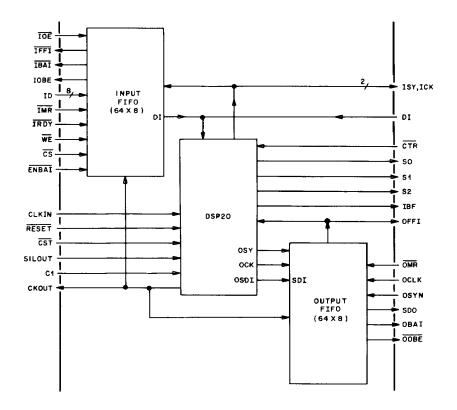

Figure 1. 439C Sub-Band Decoder Block Diagram

The information contained herein is preliminary and subject to change.

#### **USER INFORMATION**

# **Pin Descriptions**

| Symbols                  |     |      |     |                        |     |  |

|--------------------------|-----|------|-----|------------------------|-----|--|

| Sym                      | Pin | Sym  | Pin | Sym                    | Pin |  |

| CKOUT                    | 2   | ID4  | 24  | OMR                    | 14  |  |

| CLKIN                    | 1   | ID5  | 23  | OOBE                   | 16  |  |

| $\overline{\mathrm{CS}}$ | 32  | ID6  | 22  | OSYN                   | 18  |  |

| CST                      | 4   | ID7  | 21  | RESET                  | 3   |  |

| CTR                      | 38  | ĪFFĪ | 33  | SDO                    | 19  |  |

| DI                       | 39  | ĪMR  | 29  | SILOUT                 | 5   |  |

| ENBAI                    | 34  | IOBE | 36  | S0                     | 7   |  |

| <b>IBAI</b>              | 35  | IOE  | 37  | S1                     | 8   |  |

| IBF                      | 11  | IRDY | 30  | S2                     | 9   |  |

| ICK                      | 13  | ISY  | 12  | Vdd                    | 40  |  |

| ID0                      | 28  | C1   | 6   | Vss                    | 20  |  |

| ID1                      | 27  | OBAI | 15  | $\overline{\text{WE}}$ | 31  |  |

| ID2                      | 26  | OCLK | 17  |                        |     |  |

| ID3                      | 25  | OFFI | 10  |                        |     |  |

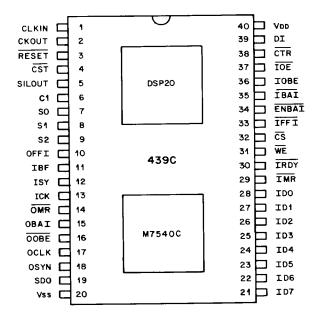

Figure 2. 439C Pin Function Diagram and Alphabetical Listing of Symbols

|                               | Table 1. 439C Pin Descriptions |   |                                                                                                                                                                                                    |  |  |  |

|-------------------------------|--------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Symbol Type Name/Function |                                |   |                                                                                                                                                                                                    |  |  |  |

| 1                             | CLKIN                          | I | Clock Input.                                                                                                                                                                                       |  |  |  |

| 2                             | CKOUT                          | 0 | Clock Output. System clock.                                                                                                                                                                        |  |  |  |

| 3                             | RESET                          | I | Reset (Active Low). Suspends all DSP operations. After rising edge, DSP responds to new speech instructions, disregarding inputs prior to RESET.                                                   |  |  |  |

| 4                             | CST                            | I | Control Strobe (Active Low). When low, SILOUT (pin 5) and C1 (pin 6) are transparent to the DSP. When high, the values of SILOUT and C1 at the time of CST's rising edge are latched into the DSP. |  |  |  |

| 5                             | SILOUT                         | I | Silence Output. When tied to OBAI (pin 15), permits automatic output of silence when input FIFO is empty. When tied low, output is unpredictable when OOBE goes low.                               |  |  |  |

| 6                             | C1                             | I | FCC Part 68 Select. When C1 is high, the FCC part 68 protection circuit is active; when C1 is low, it is inactive.                                                                                 |  |  |  |

| 7                             | S0                             |   |                                                                                                                                                                                                    |  |  |  |

| 8                             | S1                             | О | Status Register Outputs, Bits 0, 1, and 2. No connection.                                                                                                                                          |  |  |  |

| 9                             | S2                             |   |                                                                                                                                                                                                    |  |  |  |

|       | Table 1. 439C Pin Descriptions (Continued) |   |                                                                                                                                                                                                                                            |  |  |  |

|-------|--------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin   | Pin Symbol Type Name/Function              |   |                                                                                                                                                                                                                                            |  |  |  |

| 10    | OFFI                                       | 0 | Output FIFO Full Indicator. When high, indicates output FIFO contains 64 bytes of data (full). If high for more than 500 $\mu$ s, DSP could be in an indeterminate state.                                                                  |  |  |  |

| 11    | IBF                                        | 0 | Input Buffer Full. Indicates state of DSP input buffer. Set after 8 bits have been written into the DSP input buffer; cleared after the DSP has read the buffer.                                                                           |  |  |  |

| 12    | ISY                                        | O | Input Sync. Indicates start of data transfer to input buffer. Generated by DSP. ISY has a weak pull-down (50 k $\Omega$ nominal) to ground to prevent ISY from floating when $\overline{CTR}$ is high.                                     |  |  |  |

| 13    | ICK                                        | О | Input Clock. One-half CLKIN. Data shifted into the input buffer is latched on rising edge of ICK. Generated by DSP. ICK has a weak pull-down (50 k $\Omega$ nominal) to ground to prevent ICK from floating when $\overline{CTR}$ is high. |  |  |  |

| 14    | OMR                                        | I | Output FIFO Master Reset (Active Low). Resets all of the counters and pointers in the output FIFO.                                                                                                                                         |  |  |  |

| 15    | OBAI                                       | 0 | Output FIFO Bytes Available Indicator. High when less than 8 bytes are in output FIFO.                                                                                                                                                     |  |  |  |

| 16    | OOBE                                       | О | Output FIFO Output Buffer Empty (Active Low). Low when last bit of last byte has been shifted out of output FIFO.                                                                                                                          |  |  |  |

| 17    | OCLK                                       | I | Output Clock. Output FIFO serial data output clock. Must be continuous.                                                                                                                                                                    |  |  |  |

| 18    | OSYN                                       | I | Output FIFO Serial Data Output Sync Pulse. Initiates transfer of data out of output FIFO.                                                                                                                                                  |  |  |  |

| 19    | SDO                                        | 0 | Serial Data Output. Data is shifted out of the output FIFO on the negative edge of OCLK.                                                                                                                                                   |  |  |  |

| 20    | Vss                                        | _ | Ground.                                                                                                                                                                                                                                    |  |  |  |

| 21    | ID7                                        |   |                                                                                                                                                                                                                                            |  |  |  |

| 22    | ID6                                        |   |                                                                                                                                                                                                                                            |  |  |  |

| 23    | ID5                                        |   | T I D I D                                                                                                                                                                                                                                  |  |  |  |

| 24    | ID4                                        | I | Input Data Bus.                                                                                                                                                                                                                            |  |  |  |

| 25    | ID3                                        |   |                                                                                                                                                                                                                                            |  |  |  |

| 26    | ID2                                        |   |                                                                                                                                                                                                                                            |  |  |  |

| 27 28 | ID1<br>ID0                                 |   |                                                                                                                                                                                                                                            |  |  |  |

| 29    | IMR                                        | I | Input FIFO Master Reset (Active Low). Resets all counters and pointers in the input FIFO.                                                                                                                                                  |  |  |  |

| 30    | ĪRDY                                       | I | Input Ready (Active Low). Verifies that data on the input data bus is valid. Used with slower microprocessors. Can be tied low if it is not needed.                                                                                        |  |  |  |

|     | Table 1. 439C Pin Descriptions (Continued) |      |                                                                                                                                                                                                                                                                                                    |  |  |  |

|-----|--------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin | Symbol                                     | Туре | Name/Function                                                                                                                                                                                                                                                                                      |  |  |  |

| 31  | WE                                         | I    | Write Enable (Active Low). When low, input data is transferred from the input data bus to the input FIFO if CS and IRDY are low and IFFI is high.                                                                                                                                                  |  |  |  |

| 32  | CS                                         | I    | Chip Select (Active Low). When low, input FIFO is selected.                                                                                                                                                                                                                                        |  |  |  |

| 33  | ĪFFI                                       | 0    | Input FIFO Full Indicator (Active Low). Indicates input FIFO is full (contains 64 bytes of data). When low, further writes to input FIFO are ignored.                                                                                                                                              |  |  |  |

| 34  | ENBAI                                      | I    | Enable Bytes Available Indicator (Active Low). Disables IBAI until the next data write.                                                                                                                                                                                                            |  |  |  |

| 35  | ĪBAĪ                                       | 0    | Input FIFO Bytes Available Indicator (Active Low). Goes low when there are less than 32 bytes in the input FIFO.                                                                                                                                                                                   |  |  |  |

| 36  | IOBE                                       | 0    | Input FIFO Output Buffer Empty. Indicates when the last bit of the last byte has been shifted out of the input FIFO.                                                                                                                                                                               |  |  |  |

| 37  | <u>IOE</u>                                 | I    | Input FIFO Output Enable (Active Low). When low, input FIFO serial data output is input to the DSP. When high, serial data of input FIFO is in high-impedance state, allowing external hardware to provide data, via pin 39, coordinated with DSP-generated sync and clock lines (pins 12 and 13). |  |  |  |

| 38  | CTR                                        | I    | Clear to Read (Active Low). Enables data reception by the DSP.                                                                                                                                                                                                                                     |  |  |  |

| 39  | DI                                         | I    | Data Input. Receives serial data for DSP from input FIFO or external input.                                                                                                                                                                                                                        |  |  |  |

| 40  | VDD                                        |      | 5 V Supply.                                                                                                                                                                                                                                                                                        |  |  |  |

#### **Operation**

The 439C Sub-Band Decoder corresponds to the sub-band code (SBC) standard, Voice Store and Forward Standards, authorized by the AT&T Chief Architect's Division.

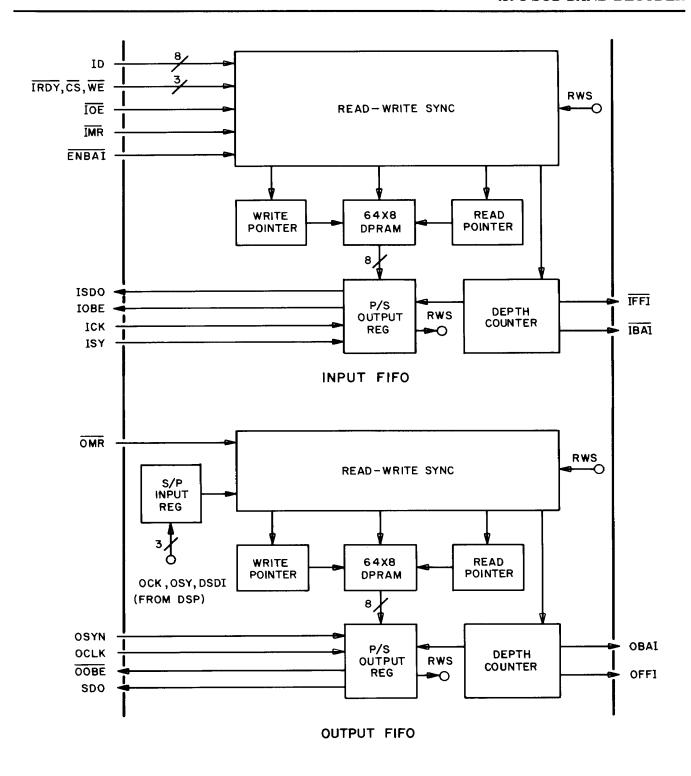

The 439C device can provide high quality speech at either 16 kb/s or 24 kb/s, corresponding to the AT&T standard. As shown on Figure 1, the device consists of an input and output FIFO and a WE DSP20 Digital Signal Processor (DSP). Figure 3 shows a simplified block diagram of the input and output FIFOs.

Parallel data is entered via the input FIFO input data bus (ID0—ID7) and written to the dual-port RAM. The RAM can buffer up to sixty-four 8-bit words. At the same time, the DSP can read the RAM through the parallel-to-serial shift register of the input FIFO. The output of the shift register is the input data to the DSP. The dual-port RAM used for the FIFO implementation facilitates simultaneous reading and writing of the memory.

To reset the counter and pointers in the input and output FIFOs, IMR, and OMR are brought low. The RAM data is then overwritten with the new input data. All DSP operations are suspended by bringing RESET low.

Figure 3. Input and Output FIFOs Simplified Block Diagram

Data can be entered either in parallel form through the input FIFO or in serial form directly to the DSP. To write to the input FIFO,  $\overline{CS}$ ,  $\overline{IRDY}$ , and  $\overline{WE}$  must be active.  $\overline{IOE}$  must be active for serial data to be output to the DSP from the input FIFO (see **Timing Characteristics**).

To enter serial data into the DSP, bypassing the input FIFO, DSP-generated ISY and ICK provide the timing to input data through DI (see **Timing Characteristics**). During parallel data input, DI should not be driven.

The 439C has six flags or indicators. IBAI goes low when there are less than 32 bytes in the input FIFO.

A pulse signal on ENBAI disables this function. As long as ENBAI remains active, IBAI remains disabled.

IBAI starts to function normally upon the next completed write.

IFFI goes low (active) when the input FIFO contains 64 bytes of data in memory. When active, IFFI indicates that the input FIFO is full. Further writes are ignored until IFFI goes high as a result of a DSP read or an IMR going low.

When the last bit of the last byte has been shifted out of the output shift register of the input FIFO, IOBE goes high (active).

OFFI goes high when the output FIFO contains 64 bytes of data in memory. The DSP could be in an indeterminate state if OFFI is high for more than 500  $\mu$ s.

OBAI goes high when there are less than eight bytes in the output FIFO. When the last bit of the last byte is shifted out of the output shift register, OOBE goes low.

As an added feature, if OBAI is tied to SILOUT, the DSP starts writing data to the output FIFO when the output FIFO is nearly empty. It writes silence until more data is entered into the input FIFO.

Data transfer from the input FIFO to the DSP is controlled by connecting IOBE to CTR.

#### **CHARACTERISTICS**

#### Clocks

Clock Input: 6-10 MHz ( $50\% \pm 2\%$  duty cycle).

Input serial clock provided by DSP is 1/2 system clock.

Output serial clock provided by external hardware, maximum is 1/2 system clock (50% ± 2% duty cycle).

## **Electrical Characteristics**

$TA = 0 \text{ to } 70 \, ^{\circ}\text{C}, \ VDD = 5 \pm 0.25 \, \text{V}, \ VSS = 0 \, \text{V}$

| Parameter                                               | Symbol     | Min      | Max         | Unit     | Test<br>Conditions          |

|---------------------------------------------------------|------------|----------|-------------|----------|-----------------------------|

| Supply Current                                          | IDD        | _        | 225         | mA       | _                           |

| Input Current High Level (Logic 1) Low Level (Logic 0)  | IIH<br>IIL | _<br>_   | 20<br>-20   | μΑ<br>μΑ | VIH = 5.25 V<br>VIL = 0.4 V |

| Output Current High Level (Logic 1) Low Level (Logic 0) | Iон<br>Iol | _<br>_   | -400<br>1.6 | μA<br>mA | VOH = 2.7 V<br>VOL = 0.5 V  |

| Input Voltage High Level (Logic 1) Low Level (Logic 0)  | VIH<br>VIL | 2.4<br>— | _<br>0.7    | V<br>V   | 1 1                         |

| Output Voltage High Level (Logic 1) Low Level (Logic 0) | Voh<br>Vol | 2.7      | _<br>0.5    | V<br>V   | <u>-</u><br>-               |

| Power Dissipation                                       | PD         |          | 1.5         | W        | $V_{DD} = 5.0 \text{ V}$    |

# **Absolute Maximum Ratings**

| DC Supply Voltage Range (VDD)            | VSS = 0.5  to VSS + 6  V |

|------------------------------------------|--------------------------|

| Input Voltage Range (VI)                 |                          |

| Power Dissipation (PD)                   |                          |

| Ambient Operating Temperature Range (TA) |                          |

| Storage Temperature Range (Tstg)         |                          |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

# **Timing Characteristics**

Timing characteristics refer to the behavior of the device under specified conditions and to the requirements imposed on the user for proper operation of the device. All timing data is valid for the following conditions:

TA = 0 to 70 °C;  $VDD = 5 \pm 0.25 \text{ V}$ ; VSS = 0 V; capacitive load on outputs = 50 pF.

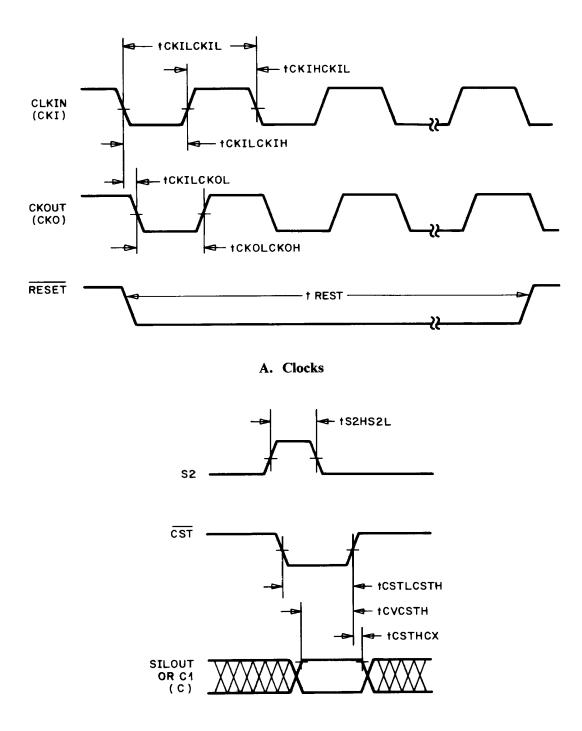

| Timing Characteristics for Clocks and Control (See Figure 4) |                          |              |                |      |  |  |

|--------------------------------------------------------------|--------------------------|--------------|----------------|------|--|--|

| Symbol                                                       | Description              | Min          | Max            | Unit |  |  |

| tCKILCKIL                                                    | CLKIN Period             | 100          | 170            | ns   |  |  |

| tCKILCKIH                                                    | CLKIN Low Time           | 46           | <del>-</del> . | ns   |  |  |

| tCKIHCKIL                                                    | CLKIN High Time          | 46           | _              | ns   |  |  |

| tCKILCKOL                                                    | CKOUT Delay              | -            | 40             | ns   |  |  |

| tCKOLCKOH                                                    | CKOUT Low Time           | tCKILCKIH-2  | tCKILCKIH+2    | ns   |  |  |

| tS2HS2L                                                      | S2 Pulse Width           | tCKILCKIL-10 | tCKILCKIL+30   | ns   |  |  |

| tCSTLCSTH                                                    | CST Pulse Width          | 25           | <u></u>        | ns   |  |  |

| tCVCSTH                                                      | SILOUT or C1 Set-Up Time | 25           | _              | ns   |  |  |

| tCSTHCX                                                      | SILOUT or C1 Hold Time   | 0            | _              | ns   |  |  |

| tREST                                                        | RESET Pulse Width        | 6tCKILCKIL   | _              | ns   |  |  |

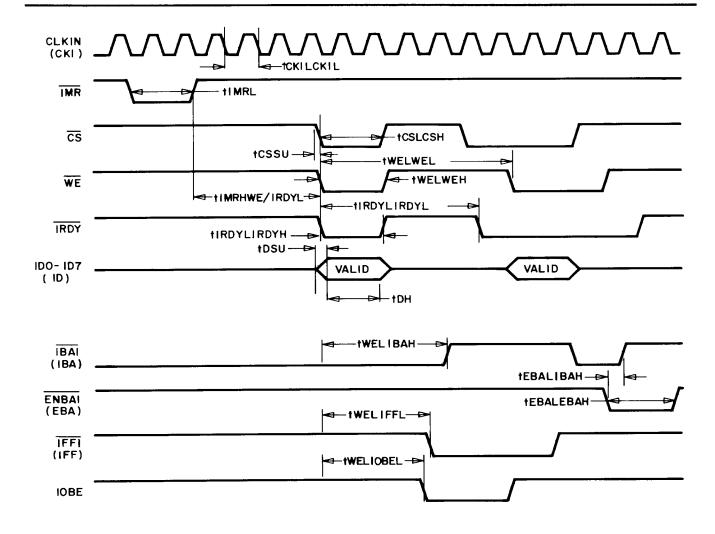

| Timing Characteristics for Parallel Data Input (See Figure 5) |                         |             |            |      |  |  |

|---------------------------------------------------------------|-------------------------|-------------|------------|------|--|--|

| Symbol                                                        | Description             | Min         | Max        | Unit |  |  |

| tIMRL                                                         | IMR Pulse Width         | 2tCKILCKIL  | _          | ns   |  |  |

| tIMRHWE/IRDYL                                                 | IMR High to WE/IRDY Low | 2tCKILCKIL  | _          | ns   |  |  |

| tCSSU                                                         | CS Set-Up Time          | 20          |            | ns   |  |  |

| tCSLCSH                                                       | CS Pulse Width          | 2tCKILCKIL  | _          | ns   |  |  |

| tWELWEH                                                       | WE Pulse Width          | 2tCKILCKIL  | -          | ns   |  |  |

| tWELWEL                                                       | WE Low to WE Low        | 6tCKILCKIL  | _          | ns   |  |  |

| tIRDYLIRDYH                                                   | IRDY Pulse Width        | 2tCKILCKIL  | _          | ns   |  |  |

| tIRDYLIRDYL                                                   | IRDY Low to IRDY Low    | 6tCKILCKIL5 | _          | ns   |  |  |

| tDSU                                                          | Data Set-Up Time        | 0           | _          | ns   |  |  |

| tDH                                                           | Data Hold Time          | 2tCKILCKIL  | _          | ns   |  |  |

| tEBALEBAH                                                     | ENBAI Pulse Width       | 2tCKILCKIL  | _          | ns   |  |  |

| tEBALIBAH                                                     | ENBAI Low to IBAI High  | _           | 2tCKILCKIL | ns   |  |  |

| tWELIBAH                                                      | WE Low to IBAI High     | _           | 5tCKILCKIL | ns   |  |  |

| tWELIFFL                                                      | WE Low to IFFI Low      | _           | 4tCKILCKIL | ns   |  |  |

| tWELIOBEL                                                     | WE Low to IOBE Low      | _           | 9tCKILCKIL | ns   |  |  |

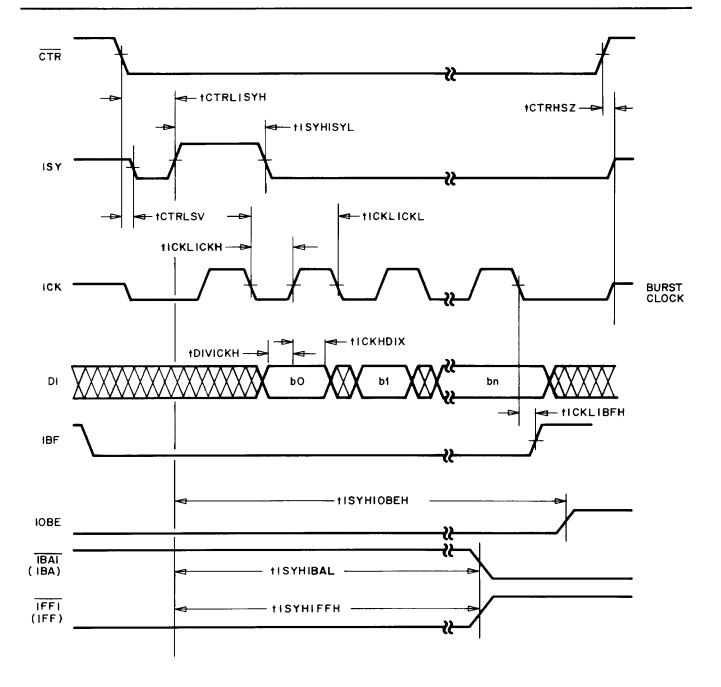

|            | Timing Characteristics f | or Serial Data Input (See | Figure 6)                    |      |

|------------|--------------------------|---------------------------|------------------------------|------|

| Symbols    | Description              | Min                       | Max                          | Unit |

| tICKLICKL  | ICK Period               | 2tCKILCKIL                | _                            | ns   |

| tICKLICKH  | ICK Low Time             | 0.5tICKLICKL-10           | .5tICKLICKL+10               | ns   |

| tISYHISYL  | ISY Pulse Width          | 0.75tICKLICKL             | 1.1tICKLICKL                 | ns   |

| tCTRLISYH  | Delay to SYNC            | 20                        | tCKILCKIL+50                 | ns   |

| tDIVICKH   | DI Set-Up Time           | 20                        | _                            | ns   |

| tICKHDIX   | DI Hold Time             | 15                        | _                            | ns   |

| tICKLIBFH  | Delay of IBF             | 0                         | 60                           | ns   |

| tCTRLSV    | Input Enable Delay       | _                         | 90                           | ns   |

| tCTRHSZ    | Input Disable Delay      | -                         | 70                           | ns   |

| tISYHIBAL  | ISY High to IBAI Low     | _                         | 6.5tICKLICKL<br>+ 5tCKILCKIL | ns   |

| tISYHIFFH  | ISY High to IFFI High    | <del>-</del>              | 6.5tICKLICKL<br>+ 5tCKILCKIL | ns   |

| tISYHIOBEH | ISY High to IOBE High    | _                         | 8.5tICKLICKL<br>+ 3tCKILCKIL | ns   |

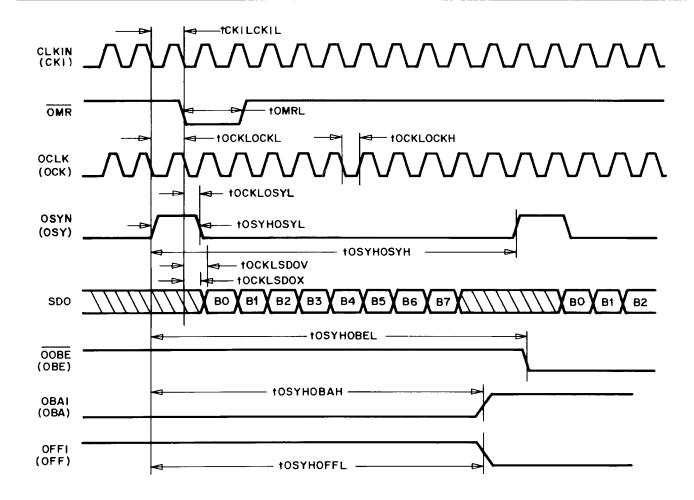

|            | Timing Characteristics for Serial Data Output (See Figure 7) |                 |                              |      |  |  |  |

|------------|--------------------------------------------------------------|-----------------|------------------------------|------|--|--|--|

| Symbols    | Description                                                  | Min             | Max                          | Unit |  |  |  |

| tOMRL      | OMR Pulse Width                                              | 2tOCKLOCKL      | _                            | ns   |  |  |  |

| tOCKLOCKL  | OCLK Period                                                  | 2tCKILCKIL      |                              | ns   |  |  |  |

| tOCKLOCKH  | OCLK Low                                                     | 0.5tOCKLOCKL-10 | 0.5tOCKLOCKL+10              | ns   |  |  |  |

| tOSYHOSYL  | OSYN Pulse Width                                             | tOCKLOCKL       | 5tOCKLOCKL                   | ns   |  |  |  |

| tOSYHOSYH  | OSYN High                                                    | 11tOCKLOCKL     |                              | ns   |  |  |  |

| tOCKLOSYL* | OCLK Low to OSYN Low                                         | 10              | -                            | ns   |  |  |  |

| tOCKLSDOX  | SDO Hold Time                                                | 0               | _                            | ns   |  |  |  |

| tOCKLSDOV  | SDO Delay                                                    | -               | 100                          | ns   |  |  |  |

| tOSYHOBEL  | OSYN High to OOBE Low                                        | _               | 9tOCKLOCKL                   | ns   |  |  |  |

| tOSYHOBAH  | OSYN High to OBAI High                                       | -               | 6.5tOCKLOCKL<br>+ 5tCKILCKIL | ns   |  |  |  |

| tOSYHOFFL  | OSYN High to OFFI Low                                        | -               | 6.5tOCKLOCKL<br>+ 5tCKILCKIL | ns   |  |  |  |

<sup>\*</sup>Clock under sync.

## **Timing Diagrams**

**B.** Control Timing

Figure 4. Clocks and Control Timing

Figure 5. Parallel Data Input Timing

Figure 6. Serial Data Input Timing

Figure 7. Serial Data Output Timing

# **Outline Diagram**

NOTE: MEASUREMENTS ARE IN INCHES.

#### ORDERING INFORMATION

| <b>Device Code</b> | Package                               | Temperature | COMCODE   |

|--------------------|---------------------------------------|-------------|-----------|

| 439C               | 40-pin dual-<br>cavity ceramic<br>DIP | 0 to 70 °C  | 104189675 |