## 128K x 32 FLASH MODULE

### PUMA2F4001-15/17/20

Issue 4.0: July 1995

### **Description**

The PUMA 2F4001 is a 4Mbit CMOS 5.0V only FLASH memory in a 66 pin ceramic PGA package, which is configerable as 8, 16, 32 bit wide output using Chip Select 1-4. Access times of 150ns, 170ns and 200ns are available. The device utilises Sector Erase / Program architecture (128 bytes / sector) with Sector program times of 10ms. Data Polling / Toggle bit indication of end of write. The device incorporates Hardware and Software Data protection which disables any program / erase operations. The package includes onboard decoupling capacitors and is suitable for thermal ladder operations.

# 4,194,304 bit CMOS FLASH Memory Module

- Features

- FastAccessTime of 150/170/200ns.

- Output Configurable as 32 / 16 / 8 bit wide.

- Operating Power 380/693/1320 mW(max.)

Low power standby 6.6 mW(max.)

- JEDEC 66 pin PGA

- · Hardware and Software Data Protection

- Page Write (128 Bytes) in 10ms typ.

- Data retention time of 10 years

- Can be screened in accordance with MIL-STD-883.

# **Pin Definition** (23) D15 (4) D31 (67) 1 25 (2) 29 (3) 11 (4) (4) (6) A1 (5) A1 (7) A2 (4) X2 (6) 25 (7) 25 (7) 4) 24 (3) 25 (4) 26 (3) A (3) A (3) E (4) A (4) 25 (4) 27 (4) (2) | H (2) | H (2) | H (3) | (3) 14 (8) 13 (7) 18 (8) 29 (9) WE (8) 15 (5) 25 (3) 25 (3) D30 **VIEW** FROM **ABOVE** • D21 •

#### **Pin Functions**

A0-A16 Address Inputs D0-D31 DataInput/Output CS1-4 Chip Selects WE1-4 Write Enable OE Output Enable NC No Connect V<sub>cc</sub> Power(+5V) **GND** Ground

**■** 6353379 0002449 067 **■**

#### DC OPERATING CONDITIONS

| Absolute Maximum Ratings (1)                             |                  |              |    |  |

|----------------------------------------------------------|------------------|--------------|----|--|

| Operating Temperature                                    | Tope             | -55 to +125  | .c |  |

| StorageTemperature                                       | T <sub>STG</sub> | -65 to+150   | .c |  |

| Input voltages (including N.C. pins) with Respect to GND | V <sub>IN</sub>  | -0.5 to +7.0 | ٧  |  |

| Output voltages with respect to GND                      | $V_{out}^{"`}$   | -0.5 to +7.0 | V  |  |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Recommended Operating Conditions |                 |      |     |                      |                                  |

|----------------------------------|-----------------|------|-----|----------------------|----------------------------------|

|                                  |                 | min  | typ | max                  |                                  |

| DC Power Supply Voltage          | V <sub>cc</sub> | 4.5  | 5.0 | 5.5                  | V                                |

| Input Low Voltage                | V <sub>IL</sub> | -0.3 | 0.8 | -                    | V                                |

| Input High Voltage               | V <sub>iH</sub> | 2.0  |     | V <sub>cc</sub> +0.3 | V                                |

| Operating Temp Range             | TA              | 0    | -   | 70                   | .c                               |

|                                  | T               | -40  | -   | 85                   | 'C(I Suffix)                     |

|                                  | T <sub>AM</sub> | -55  |     | 125                  | *C( <b>M</b> , <b>MB</b> Suffix) |

| DC Electrical Characteristics ( $T_A$ =-55°C to +125°C, $V_{cc}$ =5V ± 10%) |                        |                                                                                                                                                                 |     |                |      |  |

|-----------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|------|--|

| Parameter                                                                   | Sy                     | mbol Test Condition                                                                                                                                             | min | max            | Unit |  |

| Input Leakage Current                                                       | l <sub>u</sub>         | V <sub>IN</sub> = GND to V <sub>CC</sub>                                                                                                                        | •   | 10             | μA   |  |

| Output Leakage Current 3                                                    | 32 bit I <sub>LC</sub> | $V_{IN} = GND \text{ to } V_{CC}, \overline{CS}^{(1)} = V_{IH}$                                                                                                 | •   | 40             | μΑ   |  |

| Operating Supply Current 3                                                  | 32bit I <sub>co</sub>  | $\overline{\text{CS}}^{(1)} = \overline{\text{OE}} = V_{\text{IL}}, \overline{\text{WE}} = V_{\text{IH}}, I_{\text{OUT}} = 0 \text{mA}, f = 5 \text{MHz}^{(2)}$ | •   | 240            | mA   |  |

| 1                                                                           | l6bit I <sub>co</sub>  | As above                                                                                                                                                        | -   | 126            | mA   |  |

|                                                                             | 8bit I <sub>cc</sub>   | <sub>B</sub> As above                                                                                                                                           | •   | 6 <del>9</del> | mA   |  |

| Standby Supply Current TTL Is                                               | evels I <sub>se</sub>  | $\overline{CS^{(1)}} = V_{iH}, I_{I/O} = 0$ mA, Other Inputs $= V_{iH}$                                                                                         |     | 12             | mΑ   |  |

| CMOS I                                                                      | evels I <sub>se</sub>  | <del></del>                                                                                                                                                     | -   | 1.2            | mΑ   |  |

| Output Low Voltage                                                          | V                      | I <sub>oL</sub> =2.1mA.                                                                                                                                         |     | 0.4            | V    |  |

| Output High Voltage                                                         | V                      |                                                                                                                                                                 | 2.4 | •              | V    |  |

Notes (1) CS above are accessed through CS1-4. These inputs must be operated simultaneously for 32 bit operation, in pairs in 16 bit mode and singly for 8 bit mode.

| Capacitance (T <sub>A</sub> =25°C, f=1MHz) Note: These parameters are calculated, not measured. |                       |                      |     |     |      |  |  |  |

|-------------------------------------------------------------------------------------------------|-----------------------|----------------------|-----|-----|------|--|--|--|

| Parameter                                                                                       | Symbol                | Test Condition       | typ | max | Unit |  |  |  |

| Input Capacitance CS1~4, WE1~4                                                                  | $C_{_{\mathrm{IN1}}}$ | V <sub>IN</sub> =0V  | -   | 16  | pF   |  |  |  |

| OtherInputs                                                                                     | C <sub>IN2</sub>      | V <sub>IN</sub> =0V  | -   | 34  | pF   |  |  |  |

| Output Capacitance                                                                              | $C_out$               | V <sub>OUT</sub> =0V | -   | 22  | pF   |  |  |  |

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121

Tel: 619.271.4565 Fax: 619.271.6058

**■ 6353379 0002450 881** ■

## Operating Modes

The table below shows the logic inputs required to control the operating modes of each device on the PUMA 2F4001.

| MODE           | cs | OE | WE | Outputs  |

|----------------|----|----|----|----------|

| Read           | 0  | 0  | 1  | Data Out |

| Write (1)      | 0  | 1  | 0  | Data In  |

| Standby        | 1  | Х  | X  | High Z   |

| Write Inhibit  | X  | Х  | 1  |          |

| Write Inhibit  | Х  | 0  | Х  |          |

| Output Disable | Х  | 1  | Х  | High Z   |

$1 = V_{IH} 0 = V_{IL} X = Don't care$

Note: (1) Refer to AC Programming Waveforms

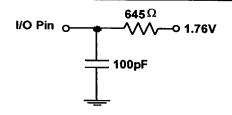

### **AC Test Conditions**

**Output Test Load**

\* Input pulse levels: 0V to 3.0V

\*Input rise and fall times: 10ns

\*Input and Output timing reference levels: 1.5V

\*Output load: 1 TTL gate + 100pF

\*V<sub>cc</sub>=5V±10%

| AC O | PER | ATING | CON | DITIONS |

|------|-----|-------|-----|---------|

|      |     |       |     |         |

| Read Cycle                         |                 |     |     |     |     |     |     |      |       |

|------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|------|-------|

|                                    |                 | - ] | 15  | -17 |     | -20 |     |      |       |

| Parameter                          | Symnbol         | min | max | min | max | min | max | Unit | Notes |

| Read Cycle Time                    | t <sub>RC</sub> | 150 | -   | 170 |     | 200 |     | ns   |       |

| Address Access Time                | t               |     | 150 | •   | 170 |     | 200 | ns   |       |

| Chip Select Access Time            | t <sub>cs</sub> | -   | 150 | •   | 170 |     | 200 | ns   |       |

| Output Enable Access Time          | t <sub>oe</sub> | 0   | 70  | 0   | 80  | 0   | 80  | ns   |       |

| Chip Enable to Output Enable Float | t <sub>DF</sub> | 0   | 40  | 0   | 50  | 0   | 50  | ns   |       |

| Output Hold from Address Change    | t <sub>o⊢</sub> | 0   | -   | 0   | -   | 0   | •   | ns   |       |

| Write Cycle                  |                  |     |     |     |      |  |

|------------------------------|------------------|-----|-----|-----|------|--|

| Parameter                    | Symbol           | min | typ | max | Unit |  |

| Write Cycle Time             | t <sub>wc</sub>  | •   | •   | 10  | ms   |  |

| Address Set-up Time          | t <sub>as</sub>  | 0   | -   | •   | ns   |  |

| Address Hold Time            | t <sub>AH</sub>  | 50  | -   | -   | ns   |  |

| Output Enable Set-up Time    | t <sub>oes</sub> | 0   | •   | -   | ns   |  |

| Output Enable Hold Time      | t <sub>oeh</sub> | 0   | -   | •   | ns   |  |

| Chip Select Set-up Time      | t <sub>cs</sub>  | 0   | -   | •   | ns   |  |

| Chip Select Hold Time        | t <sub>cH</sub>  | 0   | •   | •   | ns   |  |

| Write Pulse Width (WE or CE) | t <sub>we</sub>  | 90  | •   |     | ns   |  |

| Writ Pulse Width High        | t <sub>wpH</sub> | 100 | -   |     | ns   |  |

| Data Set-up Time             | t <sub>os</sub>  | 50  | •   |     | ns   |  |

| Data Hold Time               | t <sub>DH</sub>  | 0   |     |     | ns   |  |

| Byte Cycle Load Time         | t <sub>BLC</sub> | •   |     | 150 | μs   |  |

| Data Polling            |                  |     |     |     |      |  |

|-------------------------|------------------|-----|-----|-----|------|--|

| Parameter               | Symbol           | min | typ | max | Unit |  |

| Data Hold Time          | t <sub>DH</sub>  | 10  | •   | -   | ns   |  |

| Output Enable Hold Time | t <sub>oeh</sub> | 10  | -   |     | ns   |  |

| Write Recovery Time     | $t_wR$           | 0   | -   | -   | ns   |  |

| Toggle Bit               |                             |     |     |     |      |  |

|--------------------------|-----------------------------|-----|-----|-----|------|--|

| Parameter                | Symbol                      | min | typ | max | Unit |  |

| Data Hold Time           | t <sub>DH</sub>             | 10  | -   | -   | ns   |  |

| Output Enable Hold Time  | $t_{\scriptscriptstyleOEH}$ | 10  | •   | -   | ns   |  |

| Output Enable High Pulse | t <sub>oehp</sub>           | 150 | -   | •   | ns   |  |

| Write Recovery Time      | $t_wR$                      | 0   | -   | -   | ns   |  |

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121 Tel: 619.271.4565 Fax: 619.271.6058

**■ 6353379 0002452 654 ■**

ISSUE 4.0: JULY 1995 PUMA 2F4001-15/17/20

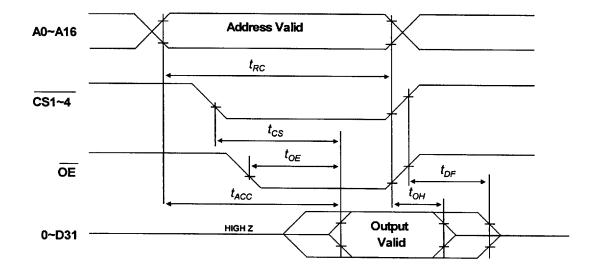

## **Read Cycle Timing Waveform**

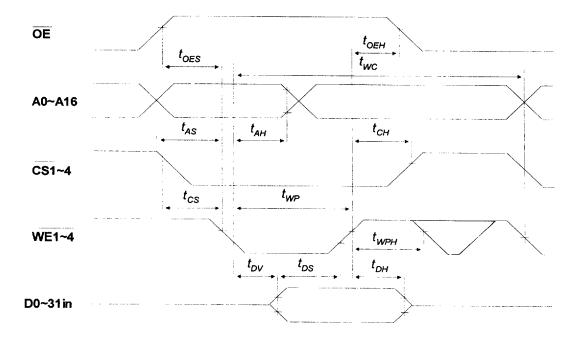

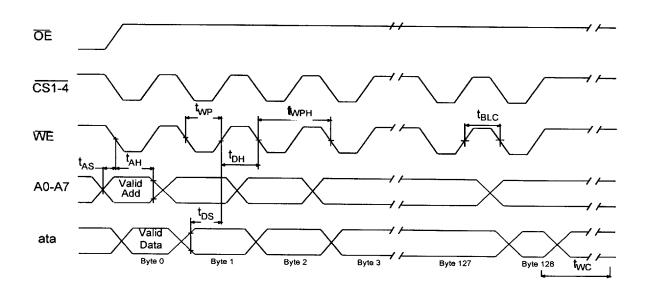

## AC Byte Write Waveform - WE Controlled

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121 5

Tel: 619.271.4565 Fax: 619.271.6058

**=** 6353379 0002453 590 **=**

ISSUE 4.0: JULY 1995 PUMA2F4001-15/17/20

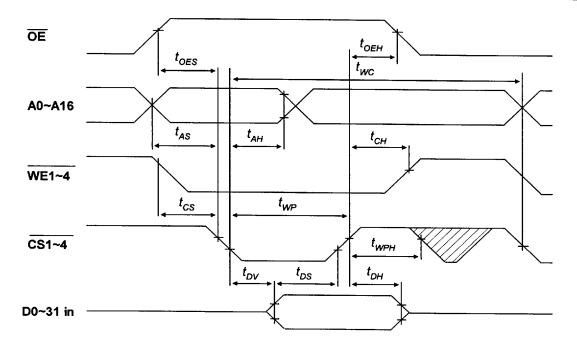

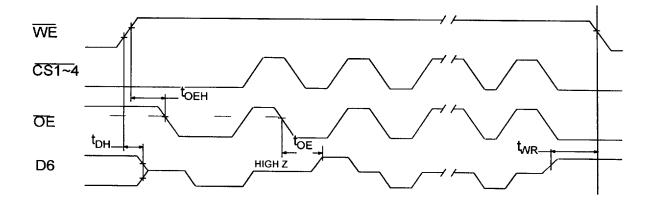

## AC Byte Write Waveform - CS Controlled

## Page Mode Write Waveform

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121 6

Tel: 619.271.4565 Fax: 619.271.6058

**■** 6353379 0002454 427 **■**

ISSUE 4.0: JULY 1995

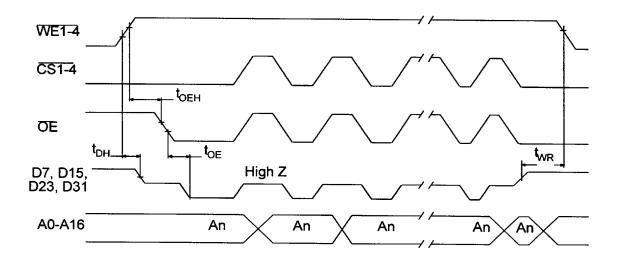

## DATA Polling Waveform

## **Toggle Bit Waveform**

- (1) Toggling either OE or CE or both OE and CE will operate toggle bit.

- (2) Beginning and adding state of D7, D15, D23, D31 may vary.

- (3) Any address location may be used but the address should not vary.

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121

Tel: 619.271.4565 Fax: 619.271.6058

**353379 0002455 363**

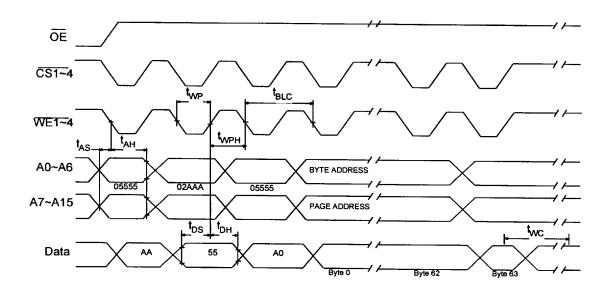

## **Software Protected Write Waveform**

Note: (1) A7 through A16 must specify the page address during each high to low transition of Write Enable (or Chip select).

- (2) Output Enable must be high only when Write Enable and Chip Select are both low.

- (3) All bytes that are not loaded within the sector being programmed will be erased to FF

Tel: 619.271.4565 Fax: 619.271.6058

🖚 6353379 0002456 2TT 🖿

### **Device Operation**

#### Read

The PUMA 2F4001 read operations are initiated when Write Enable is high and both Output Enable and Chip Select are LOW. The read operation is terminated by either Chip Select or Output Enable returning HIGH. This 2-line control architecture elimanates bus connection in a system environment. The data bus will be in a high impendence state when either Output Enable or Chip Select is HIGH.

#### Write

The device is reprogrammed on a sector basis. Byte loads are used to enter the 128 bytes of a sector to be programmed or the software codes for data protection. A byte load is performed by applying a low pulse on the WE or CE input with CE or WE low (respectively) and OE high. The address is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the first rising edge of CE or WE.

If a byte of data within a sector is to be changed, data for the entire sector must be loaded into the device. Any byte that is not loaded during the programming of its sector will be erased to read FFh. Once the bytes of a sector are loaded into the device, they are simulateously programmed during the internal programming period. After the first byte has been loaded into the device, successive bytes are loaded in the same manner.

During a reprogram cycle, the address locations and 128 bytes of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a program cycle, the device will automatically erase the sector and then program the latched data using an internal control timer. The end of a program cycle can be detected by  $\overline{\text{DATA}}$  polling on D7. Once the end of a program cycle has been detected, a new access for a read or program can begin.

Each new byte to be programmed must have its high to low transition on  $\overline{WE}$  (or  $\overline{CE}$ ) within 150  $\mu$ s of the high to low transition of  $\overline{WE}$  (or  $\overline{CE}$ ) of the preceding byte. If a high to low transition is not detected within 150  $\mu$ s of the last low to high transition, the load period will end and the internal programming period will start. A7 to A16 specify the sector address. The sector address must be valid during each high to low transition of  $\overline{WE}$  (or  $\overline{CE}$ ). A0 to A6 specify the byte address within the sector. The bytes may be loaded in any order; sequential loading is not required.

#### **DATA Polling**

In order to detect the end of a write cycle, two methods are provided. During a write operation (Byte or Page) an attempt to read the last byte written will result in the compliment of the written data appearing on D7 (or D15, D23 or D31, depending on the device selected). Once the write cycle is completed, true data appears on the outputs and the next write cycle nay begin. Using this method of indicating the end of a write can effectively reduce the total write time by 50%.

#### **TOGGLE bit**

In addition to DATA polling, another method is provided to determine the end of a Write Cycle. During a write operation successive attempts to read data will result in D6 (D14, D22 or D30, depending on the device selected). toggling between 1 and 0. Once a write is complete, this toggling will stop and valid data will be read as normal, allowing the next write cycle to be performed. This can eliminate the software housekeeping chore and saving and fetching the last address and data written in order to implement DATA polling. This can be especially helpful in an array composed of multiple PUMA 2F4001 modules that are frequently updated.

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121

Tel: 619.271.4565 Fax: 619.271.6058

**=** 6353379 0002457 **1**36 **=**

#### Hardware Data Protection

Both hardware and software protection is provided as described below.

Four types of hardware protection give high security against accidental writes:

- If  $V_m$  < 3.8V, Write is inhibited.

- OE low, CS or WE high inhibits inadvertant Write Cycles during power-on and power-off. Write Cycle timing specifications must be observed concurrently.

- Pulses are less than 15ns on WE do not initiate a Write Cycle.

Software controlled data protection, once enabled by the user, means that a software algorithm must be used before any write can be performed. To enable this feature the algorithm opposite is followed, and must be reused for each subsequent write operation. Once set the data protection remains operational until it is

#### Software Data Protection

Selecting the software data protection mode requires the host system to precede datawrite operations by a series of three write operations to three specfic addresses. The three byte sequence opens the page write window enabling the host to write 128 bytes of data. Once the page load cycle has been completed, the device will automatically be returned to the data protected sate. After the Software data protection is enabled the same three program commands must begin each program cycle inorder for the programs to occur. Once set the Software data protection feature remains active unless the dissable command is issued.

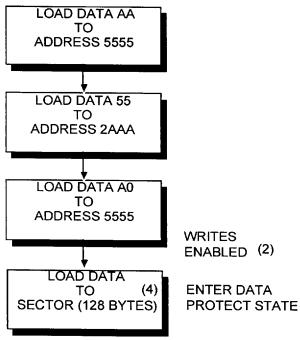

### Software Data Protection Algorithm (1)

Regardless of wheather the device has been protected or not, once the software data protected aglorithm is used and the data is written, the PUMA 2F4001 will automatically disable further writes unless another command is issued to cancel it. If no further commands are issued the PUMA 2F4001 will be write protected during power-down

and any subsequent power-up.

#### Notes:

- (1) Data Format I/O7-I/O0 (Hex);

- Once initiated, this sequence of write operations should not be interrupted.

- (2) Enable Write Protect state will be initiated at end of write even if no other data is loaded.

- (3) Disable Write Protect state will be initiated at end of write period even if no other data is loaded.

- 128 bytes of data must be loaded.

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121

Tel: 619.271.4565 Fax: 619.271.6058

6353379 0002458 072

ISSUE 4.0: JULY 1995 PUMA 2F4001·15/17/20

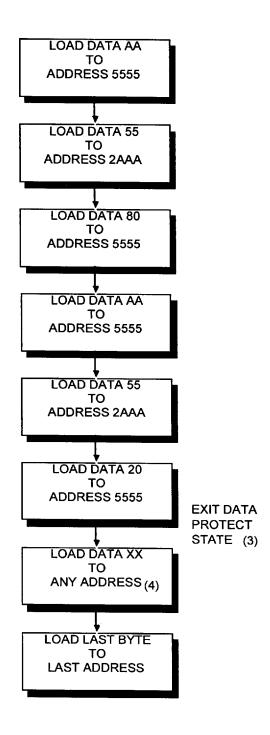

## Software Data Protect Disable Algorithm

In the event the user wants to deactivate the software data protection feature for treprogramming ithe following six step algorithm will reset the internal protection circuit. After  $t_{wc}$ , the PUMA 2F4001 will be in standard operating mode.

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121

Tel: 619.271.4565 Fax: 619.271.6058

**■** 6353379 0002459 **T09 ■**

ISSUE 4.0: JULY 1995

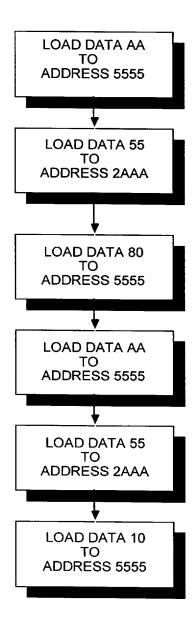

## **Chip Erase Algorithm**

The Puma 2F4001 offers a chip erase function in which the entire device can be erased in 20 ms by a six byte algorithm. Once this code has been entered, the device will set each byte to a high state, (FFh) erasing any stored data. The device will also internally time this operation so that no external clocks are needed.

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121

Tel: 619.271.4565 Fax: 619.271.6058

**■** 6353379 0002460 720 **■**

ISSUE 4.0; JULY 1995

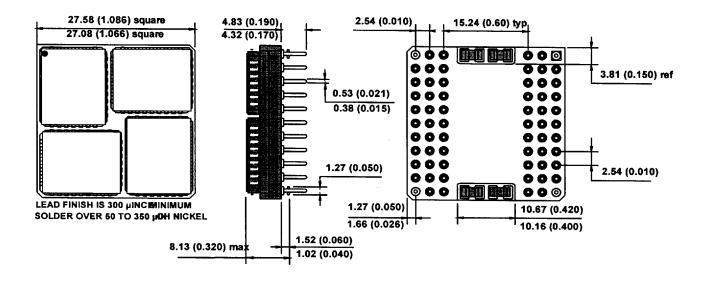

## Package Details (Dimensions in mm (inches))

## Military Screening Procedure

Module Screening Flow for high reliability product is in accordance with Mil-883 method 5004.

| MB MOD                            | ULE SCREENING FLOW                                                                             |              |

|-----------------------------------|------------------------------------------------------------------------------------------------|--------------|

| SCREEN                            | TEST METHOD                                                                                    | LEVEL        |

| Visual and Mechanical             |                                                                                                |              |

| External visual                   | 2017 Condition Bormanufacturers equivalent                                                     | 100%         |

| Temperature cycle                 | 1010 Condition C (10 Cycles, -65°C to +150°C)                                                  | 100%         |

| Burn-In                           |                                                                                                |              |

| Pre-Burn-in electrical            | Per applicable Device Specifications at T <sub>A</sub> =+25°C                                  | 100%         |

| Burn-in                           | T <sub>A</sub> =+125°C,160hrs minimum.                                                         | 100%         |

| Final Electrical Tests            | Per applicable Device Specification                                                            |              |

| Static (DC)                       | a)@T <sub>A</sub> =+25°C and power supply extremes<br>b)@temperature and power supply extremes | 100%<br>100% |

| Functional                        | a)@T <sub>A</sub> =+25°C and power supply extremes<br>b)@temperature and power supply extremes | 100%<br>100% |

| Switching (AC)                    | a)@T <sub>A</sub> =+25°C and power supply extremes<br>b)@temperature and power supply extremes | 100%<br>100% |

| Percent Defective allowable (PDA) | Calculated at Post Burn-in at T <sub>A</sub> =+25℃                                             | 5%           |

| Quality Conformance               | Per applicable Device Specification                                                            | Sample       |

| External Visual                   | 2009 Per vendor or customer specification                                                      | 100%         |

Mosaic Semiconductor, Inc., 7420 Carroll Rd. Suite 300, San Diego, CA 92121 13

Tel: 619.271.4565 Fax: 619.271.6058

**■** 6353379 0002461 667 **■**

### Ordering Information

## PUMA2F4001MB-15 Speed $15 = 150 \, \text{ns}$ $17 = 170 \, \text{ns}$ $20 = 200 \, \text{ns}$ Temp. range/screening Blank = Commercial Temperature | = IndustrialTemperature M = MilitaryTemperature MB = Screened in accordance with MIL-STD-883 Organisation 4001 = 128Kx32, user configurable as 256K x 16 and 512K x 8 Memory Type F = FLASHPackage PUMA 2 = 66 pin Ceramic PGA