# 1/2-INCH 3-MEGAPIXEL CMOS ACTIVE-PIXEL DIGITAL IMAGE SENSOR

PART NUMBER: MT9T001P12STC

#### **Features**

- DigitalClarity<sup>™</sup> Image Sensor Technology

- High frame rate

- Global Reset Release

- · Horizontal and vertical binning

- · Column and row skip modes

- Superior low-light performance

- Low dark current

- Simple two-wire serial interface

- Programmable Controls: Gain, frame rate, frame size, exposure

- Pin-for-Pin Compatible with Micron's 1.3-Megapixel MT9M001 and 2-Megapixel MT9D001

#### **Applications**

- Digital still cameras

- Digital video cameras

- Converged DSCs/camcorders

#### Description

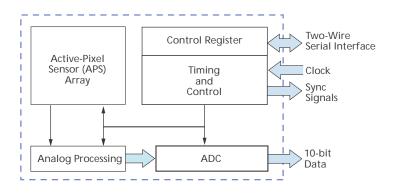

The Micron® Imaging MT9T001 is a QXGA-format 1/2-inch CMOS active-pixel digital image sensor with an active imaging pixel array of 2,048H x 1,536V. It incorporates sophisticated camera functions on-chip such as windowing, column and row skip mode, and snapshot mode. It is programmable through a simple two-wire serial interface.

The 3-megapixel CMOS image sensor features DigitalClarity—Micron's breakthrough low-noise CMOS imaging technology that achieves CCD image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

The sensor can be operated in its default mode or programmed by the user for frame size, exposure, gain setting, and other parameters. The default mode outputs a QXGA image at 12 frames per second (fps). An on-chip analog-to-digital converter (ADC) provides 10 bits per pixel. FRAME\_VALID and LINE\_VALID signals are output on dedicated pins, along with a pixel clock that is synchronous with valid data.

**Table 1: Key Performance Parameters**

| PARAMETER             |                         | TYPICAL VALUE                                          |  |

|-----------------------|-------------------------|--------------------------------------------------------|--|

| Optical Format        |                         | 1/2-inch (4:3)                                         |  |

| Active Ima            | ager Size               | 6.55mm(H) x 4.92mm(V)                                  |  |

|                       |                         | 8.19 (Diagonal)                                        |  |

| Active Pix            | els                     | 2,048H x 1,536V                                        |  |

| Pixel Size            |                         | 3.2um x 3.2um                                          |  |

| Color Filte           | er Array                | RGB Bayer Pattern                                      |  |

| Shutter Ty            | rpe                     | Global Reset Release, Electronic Rolling Shutter (ERS) |  |

| Maximum<br>Master Clo | Data Rate/<br>ock       | 48 MPS/48 MHz                                          |  |

| Frame                 | QXGA<br>(2,048 x 1,536) | Programmable up to 12 fps                              |  |

| Rate                  | UXGA<br>(1,600 x 1,200) | Programmable up to 20 fps                              |  |

|                       | SXGA<br>(1,280 x 1,024) | Programmable up to 27 fps                              |  |

|                       | XGA<br>(1,024 x 768)    | Programmable up to 43 fps                              |  |

|                       | VGA (640 x 480)         | Programmable up to 93 fps                              |  |

| ADC Reso              | lution                  | 10-bit, on-chip                                        |  |

| Responsiv             | ity                     | >1.0 V/lux-sec (550nm)                                 |  |

| Dynamic F             | Range                   | 61dB                                                   |  |

| SNR <sub>MAX</sub>    |                         | 43dB                                                   |  |

| Supply Voltage        |                         | 3.0V-0 3.6V (3.3V nominal)                             |  |

| Power Consumption     |                         | 240mW (nominal);                                       |  |

|                       |                         | 250uW (standby)                                        |  |

|                       | Temperature             | 0°C to +60°C                                           |  |

| Packaging             |                         | 48-pin PLCC                                            |  |

Our MT9T001 produces extraordinarily clear, sharp digital pictures, and its ability to capture both continuous video and single frames makes it the perfect choice for a wide range of consumer and industrial applications, including digital still cameras, digital video cameras, and PC cameras.

#### **Table of Contents**

|                                                           | 4        |

|-----------------------------------------------------------|----------|

| Features                                                  |          |

| Applications                                              |          |

| Description                                               |          |

| Pixel Data Format                                         |          |

| Pixel Array Structure                                     |          |

| Output Data Format                                        |          |

| Output Data Timing                                        |          |

| Frame Timing Formulas                                     |          |

| Register Description                                      |          |

| Feature Description                                       |          |

| Window Control                                            |          |

| Window Size                                               |          |

| Electronic Panning                                        |          |

| Blanking Control.                                         |          |

| Frame Time                                                |          |

| High Frame Rate Readout Modes                             | 20       |

| Pixel Integration Time Control                            |          |

| Snapshot Mode and Flash Control                           | 21       |

| Setting up for Snapshot Mode                              | 21       |

| Triggering A Snapshot                                     | 21       |

| Strobe Pulse Output                                       | 22       |

| Global Shutter Release Snapshot Mode                      | 22       |

| Programmed Exposure Mode                                  |          |

| Bulb Mode                                                 |          |

| Skip and Bin Modes                                        | 23       |

| Smaller Format Resolution                                 |          |

| Line_Valid Formats                                        |          |

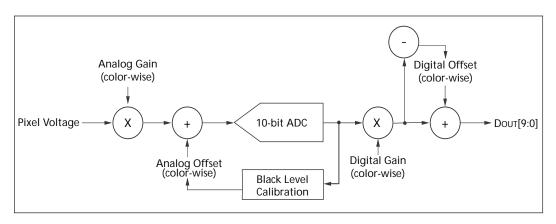

| Signal Path                                               |          |

| Gain Settings                                             |          |

| Black Level Calibration                                   |          |

| Manual Black Level Calibration                            |          |

| Black Level                                               |          |

| Reset                                                     |          |

| Standby Control and Chip Enable                           |          |

| Serial Bus Description                                    |          |

| Protocol                                                  |          |

| Sequence                                                  |          |

| Bus Idle State.                                           |          |

| Start Bit                                                 |          |

| Stop Bit                                                  |          |

| Slave Address.                                            |          |

| Data Bit Transfer.                                        |          |

| Acknowledge Bit                                           |          |

| No-Acknowledge Bit                                        |          |

| Two-Wire Serial Interface Sample Write and Read Sequences |          |

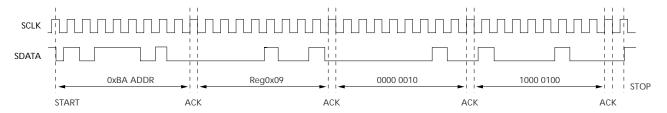

| 16-Bit Write Sequence                                     |          |

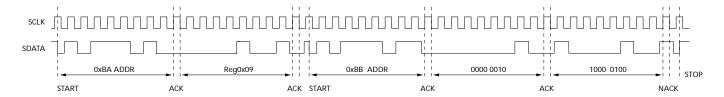

| 16-Bit Read Sequence                                      |          |

| Electrical Specifications.                                |          |

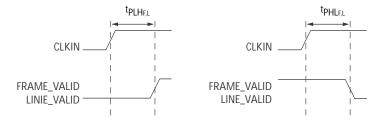

| Propagation Delay for FRAME_VALID and LINE_VALID Signals  |          |

| Two-Wire Serial Bus Timing                                |          |

| Data Shoot Designation                                    | 34<br>36 |

#### **PRELIMINARY**

## MT9T001 3-MEGAPIXEL DIGITAL IMAGE SENSOR

### **List of Figures**

| Figure 1:  | Block Diagram                                                     | .6 |

|------------|-------------------------------------------------------------------|----|

| Figure 2:  | Typical Configuration (Connection)                                | .6 |

| Figure 3:  | Pinout-48-Pin PLCC                                                |    |

| Figure 4:  | Pixel Array Description                                           | .9 |

| Figure 5:  | Pixel Color Pattern Detail (Top Right Corner)                     | .9 |

| Figure 6:  | Spatial Illustration of Image Readout                             |    |

| Figure 7:  | Timing Example of Pixel Data                                      |    |

| Figure 8:  | Row Timing and FRAME_VALID/LINE_VALID Signals                     |    |

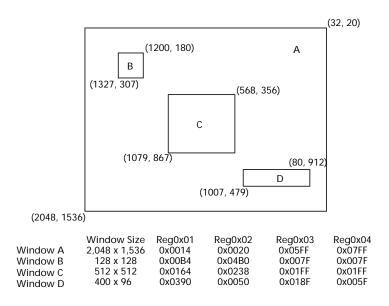

| Figure 9:  | Windowing Capabilities                                            |    |

| Figure 10: | Windowing                                                         |    |

| Figure 11: | Column Skip 2x; Row Skip 2X Enabled                               | 24 |

| Figure 12: | Column Skip 3x; Row Skip 3X Enabled                               |    |

| Figure 13: | Column Skip 4x; Row Skip 4X Enabled                               |    |

| Figure 14: | Column Skip 8x; Row Skip 8X Enabled                               |    |

| Figure 15: | Bin 2-to-1: 2,048H x 1,536V (QXGA) to 1,024H x 768V (XGA)         |    |

| Figure 16: | Bin 3-to-1: 2,048H x 1,536V (QXGA) to 640H x 480V (VGA)           |    |

| Figure 17: | Different LINE_VALID Formats                                      |    |

| Figure 18: | Signal Path                                                       |    |

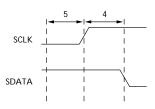

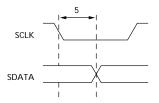

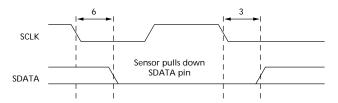

| Figure 19: | Timing Diagram Showing a Write to Reg0x09 with the Value 0x0284   | 31 |

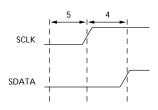

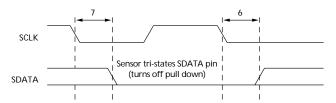

| Figure 20: | Timing Diagram Showing a Read from Reg0x09; Returned Value 0x0284 | 31 |

| Figure 21: | Propagation Delays for FRAME_VALID and LINE_VALID Signals         | 33 |

| Figure 22: | Propagation Delays for PIXCLK and Data Out Signals                |    |

| Figure 23: | Serial Host Interface Start Condition Timing                      | 34 |

| Figure 24: | Serial Host Interface Stop Condition Timing                       | 34 |

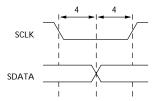

| Figure 25: | Serial Host Interface Data Timing for Write                       | 34 |

| Figure 26: | Serial Host Interface Data Timing for Read                        |    |

| Figure 27: | Acknowledge Signal Timing After an 8-Bit Write to the Sensor      | 34 |

| Figure 28: | Acknowledge Signal Timing After an 8-Bit Read from the Sensor     | 34 |

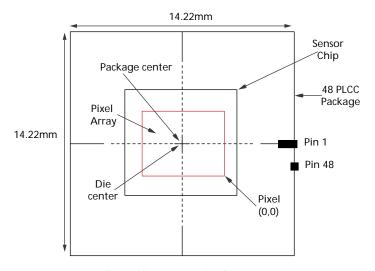

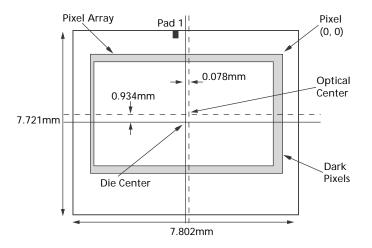

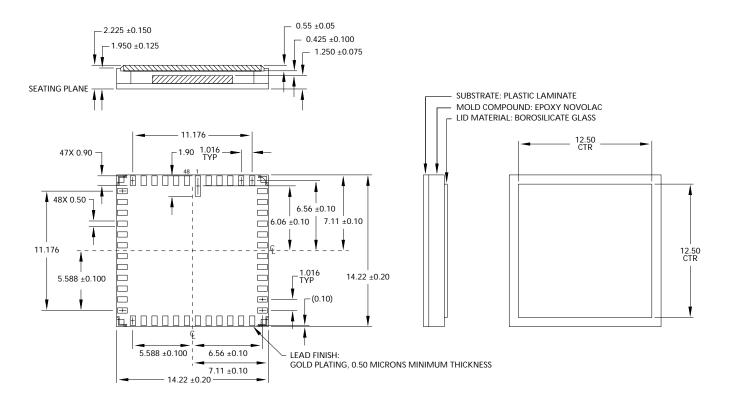

| Figure 29: | Die Placement                                                     | 35 |

| Figure 30: | Image Center Offset                                               | 35 |

| Figure 31: | 48-Pin PLCC                                                       | 36 |

|            |                                                                   |    |

#### **List of Tables**

| Table 1:  | Key Performance Parameters                | 1  |

|-----------|-------------------------------------------|----|

| Table 2:  | Pin Descriptions                          | 7  |

| Table 3:  | Frame Timing                              |    |

| Table 4:  | Register List and Default Values          |    |

| Table 5:  | Reserved Register List and Default Values | 13 |

| Table 6:  | Register Descriptions                     | 15 |

| Table 7:  | Standard Resolutions                      | 19 |

| Table 8:  | Wide Screen (16:9) Resolutions            | 19 |

| Table 9:  | Auto-Focus Modes                          |    |

| Table 10: | STROBE Pulse Output                       |    |

| Table 11: | Bin and Skip Mode Resolution.             | 23 |

| Table 12: | Skip and Bin Modes                        | 23 |

| Table 13: | Gain Increment Settings                   |    |

| Table 14: | DC Electrical Characteristics             |    |

| Table 15: | AC Electrical Characteristics             |    |

## Figure 1: Block Diagram

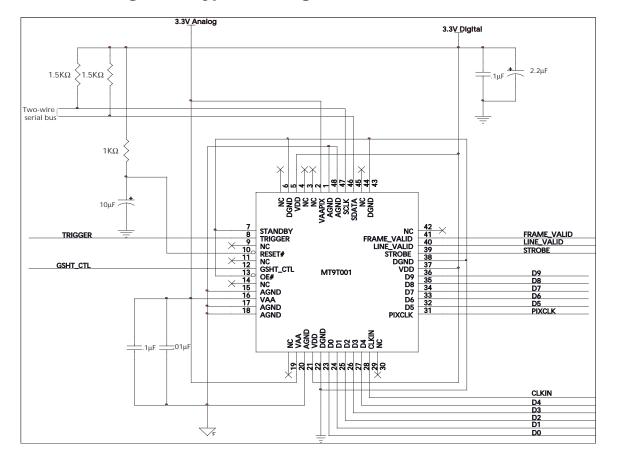

Figure 2: Typical Configuration (Connection)

#### NOTE:

Resistor value  $1.5 \text{K}\Omega$  is recommended, but may be greater for slower two-wire speed.

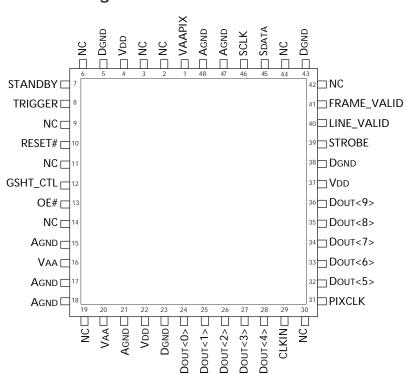

Figure 3: Pinout-48-Pin PLCC

**Table 2: Pin Descriptions**

| PIN<br>NUMBERS                               | SYMBOL      | TYPE   | DESCRIPTION                                                                                                                         |  |

|----------------------------------------------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| 7                                            | STANDBY     | Input  | Standby: Activates (HIGH) standby mode, disables analog bias circuitry for power saving mode.                                       |  |

| 8                                            | TRIGGER     | Input  | Trigger: Activates (HIGH) snapshot sequence.                                                                                        |  |

| 10                                           | RESET#      | Input  | Reset: Activates (LOW) asynchronous reset of sensor. All registers assume factory defaults.                                         |  |

| 13                                           | OE#         | Input  | Output Enable: OE# when HIGH, places outputs Dout<0-9>, FRAME_VALID, LINE_VALID, PIXCLK, and STROBE into a tri-state configuration. |  |

| 29                                           | CLKIN       | Input  | Clock In: Master clock into sensor (48 MHz maximum).                                                                                |  |

| 46                                           | SCLK        | Input  | Serial Clock: Clock for serial interface.                                                                                           |  |

| 12                                           | GSHT_CTL    | Input  | Global shutter control.                                                                                                             |  |

| 45                                           | SDATA       | I/O    | Serial Data: Serial data bus, requires 1.5 $K\Omega$ resistor to 3.3V for pull-up.                                                  |  |

| 24, 25, 26,<br>27, 28, 32,<br>33, 34, 35, 36 | Dout<0-9>   | Output | Data Out: Pixel data output bit 0, Dout<9> (MSB), Dout<0> (LSB).                                                                    |  |

| 31                                           | PIXCLK      | Output | Pixel Clock: Pixel data outputs are valid during falling edge of this clock. Frequency = (master clock).                            |  |

| 39                                           | STROBE      | Output | Strobe: Output is pulsed HIGH to indicate sensor reset operation of pixel array has completed.                                      |  |

| 40                                           | LINE_VALID  | Output | Line Valid: Output is pulsed HIGH during line of selectable valid pixel data (see Reg0x20 for options).                             |  |

| 41                                           | FRAME_VALID | Output | Frame Valid: Output is pulsed HIGH during frame of valid pixel data.                                                                |  |

## **Table 2: Pin Descriptions (continued)**

| PIN<br>NUMBERS                        | SYMBOL | TYPE   | DESCRIPTION                                                              |  |

|---------------------------------------|--------|--------|--------------------------------------------------------------------------|--|

| 1                                     | VAAPIX | Supply | Analog Pixel Power: Provide power supply for pixel array, 3.3V ±0.3V.    |  |

| 4, 22, 37                             | Vdd    | Supply | Digital Power: Provide power supply for digital block, 3.3V ±0.3V.       |  |

| 5, 23, 38, 43                         | DGND   | Supply | Digital Ground: Provide isolated ground for digital block.               |  |

| 16, 20                                | VAA    | Supply | Analog Power: Provide power supply for analog block, 3.3V ±0.3V.         |  |

| 15, 17, 18,<br>21, 47, 48             | AGND   | Supply | Analog Ground: Provide isolated ground for analog block and pixel array. |  |

| 2, 3, 6, 9,<br>11,14,19, 30<br>42, 44 | NC     | _      | No Connect: These pins must be left unconnected.                         |  |

#### **Pixel Data Format**

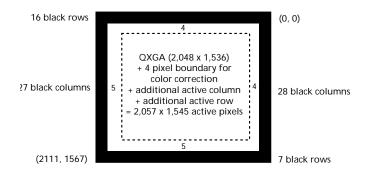

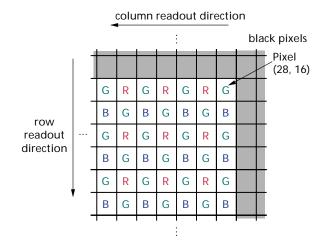

#### Pixel Array Structure

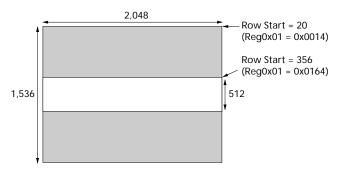

The MT9T001 pixel array is configured as 2,112 columns by 1,568 rows, as shown in Figure 4. Columns from 0 through 27 and from 2,085 through 2,111, and also rows from 0 through 15 and from 1,561 through 1,567 are optically black. These optical black columns and rows can be used to monitor the black level. The black row data is used internally for the automatic black level adjustment. However, the black rows and columns can also be read out by setting Reg0x20 (11) and Reg0x1E (7), respectively. There are 2,057 columns by 1,545 rows of optically active pixels, which provides a four-pixel boundary around the QXGA (2,048 x 1,536) image to avoid boundary effects during color interpolation and correction.

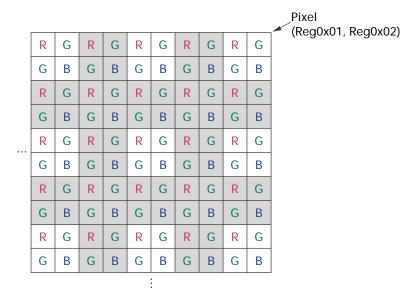

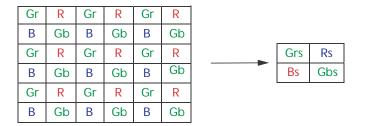

The MT9T001 uses a Bayer color pattern, as shown in Figure 5. The even-numbered rows contain green and red color pixels, and odd-numbered rows contain blue and green color pixels. The even-numbered columns contain green and blue color pixels; odd-numbered columns contain red and green color pixels.

Figure 4: Pixel Array Description

Figure 5: Pixel Color Pattern Detail (Top Right Corner)

#### **Output Data Format**

The MT9T001 image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking and vertical blanking, as shown in Figure 6. The amount of horizontal blanking and vertical blanking is programmable through Reg0x05 and Reg0x06, respectively. LINE\_VALID is HIGH during the shaded region of the figure. FRAME\_VALID timing is described in "Output Data Timing" on page 10.

Figure 6: Spatial Illustration of Image Readout

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                       | 00 00 00 00 00 00 00 00 00 00 00 0 |

|--------------------------------------------------------------------------------------------|------------------------------------|

| VALID IMAGE                                                                                | HORIZONTAL<br>BLANKING             |

|                                                                                            |                                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                       | 00 00 00 00 00 00 00 00 00 00 00   |

|                                                                                            |                                    |

| P <sub>m,0</sub> P <sub>m,1</sub> P <sub>m,n-1</sub> P <sub>m,n</sub> 00 00 00 00 00 00 00 | 00 00 00 00 00 00                  |

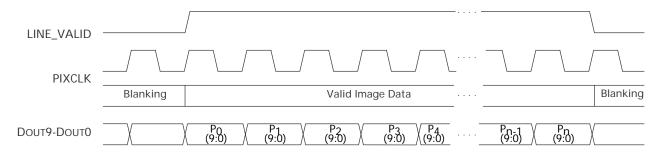

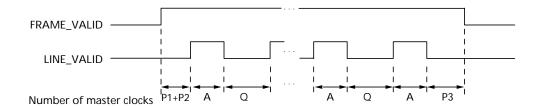

#### **Output Data Timing**

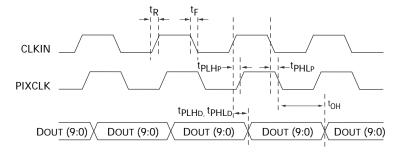

The data output of the MT9T001 is synchronized with the PIXCLK output. When LINE\_VALID is HIGH, one 10-bit pixel datum is output every PIXCLK period.

The PIXCLK can be used as a clock to latch the data. DOUT data is valid on the falling edge of PIXCLK in default mode. The PIXCLK is HIGH while master clock is HIGH and then LOW while master clock is LOW. It is continuously enabled, even during the blanking period. The parameters in P, A, and Q shown in Figure 8 are defined in Table 3.

Figure 7: Timing Example of Pixel Data

Figure 8: Row Timing and FRAME\_VALID/LINE\_VALID Signals

### Frame Timing Formulas

### Table 3: Frame Timing

| PARAMETER          | NAME                   | EQUATION (PIXEL CLOCKS = MASTER CLOCK)                                                                | DEFAULT TIMING                      |

|--------------------|------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------|

| R                  | Active Rows            | ((Reg0x03 + 1)/((Reg0x22[2-0] + 1)))<br>(rounded up to next even number)                              | 1,536 pixel clocks<br>= 32.0µs      |

| А                  | Active Columns         | ((Reg0x04 + 1)/((Reg0x23[2-0] + 1)))<br>(rounded up to next even number)                              | 2,048 pixel clocks<br>= 42.67µs     |

| P1                 | Frame Start Blanking 1 | 331 if Reg0x22[5-4] = 0, normal<br>673 if Reg0x22[5-4] = 1, Bin 2x<br>999 if Reg0x22[5-4] = 2, Bin 3x | 331pixel clocks<br>= 6.89µs         |

| P2                 | Frame Start Blanking 2 | 38 if Reg0x23[5-4] = 0, normal<br>22if Reg0x23[5-4] = 1, Bin 2x<br>14 if Reg0x23[5-4] = 2, Bin 3x     | 38 pixel clocks<br>= 0.79µs         |

| P3                 | Frame End Blanking 3   | Reg0x05 (minimum Reg0x05 value = 21)                                                                  | 142 pixel clocks<br>= 2.96µs        |

| Q                  | Horizontal Blanking    | P1 + P2 + P3                                                                                          | 511 pixel clocks<br>= 10.65µs       |

| P4                 | Shutter Overhead       | Reg0x0C + 316 x (Reg0x23[5-4] +1)                                                                     | 316 pixel clocks<br>= 6.58µs        |

| <sup>t</sup> ROW   | RowTime                | The greater of: (A + Q) or (P1+ P4)                                                                   | 2,559 pixel clocks<br>= 53.31µs     |

| V                  | Vertical Blanking      | (Reg0x06 + 1) x <sup>t</sup> ROW                                                                      | 66,534 pixel clocks<br>= 1.39ms     |

| <sup>t</sup> FV    | Frame Valid Time       | R x <sup>t</sup> row                                                                                  | 3,930,624 pixel clocks<br>= 81.89ms |

| <sup>t</sup> FRAME | Total Frame Time       | The greater of: ((65536 x Reg0x08 + Reg0x09) x $^{t}$ ROW) or ( $^{t}$ FV + V)                        | 3,997,158 pixel clocks<br>= 83.27ms |

**Table 4: Register List and Default Values**

| REGISTER # (HEX) | DESCRIPTION              | DATA FORMAT<br>(BINARY) | DEFAULT VALUE (HEX) |

|------------------|--------------------------|-------------------------|---------------------|

| 0x00             | Chip Version             | 0001 0110 0000 0001     | 0x1611              |

| 0x01             | Row Start                | 0000 00dd dddd ddd0     | 0x0014              |

| 0x02             | Column Start             | 0000 0ddd dddd ddd0     | 0x0020              |

| 0x03             | Row Size (Window Height) | 0000 00dd dddd ddd1     | 0x05FF              |

| 0x04             | Col Size (Window Width)  | 0000 0ddd dddd ddd1     | 0x07FF              |

| 0x05             | Horizontal Blanking      | 0000 00dd dddd dddd     | 0x008E              |

| 0x06             | Vertical Blanking        | 0000 00dd dddd dddd     | 0x0019              |

| 0x07             | Output Control           | 0d00 0000 d0dd 00dd     | 0x0002              |

| 0x08             | Shutter Width Upper      | 0000 0000 0000 dddd     | 0x0000              |

| 0x09             | Shutter Width            | dddd dddd dddd          | 0x0619              |

| 0x0A             | Pixel Clock Control      | dddd dddd dddd          | 0x0000              |

| 0x0B             | Restart                  | 0000 0000 0000 000d     | 0x0000              |

| 0x0C             | Shutter Delay            | 0000 00dd dddd dddd     | 0x0000              |

| 0x0D             | Reset                    | 0000 0000 0000 000d     | 0x0000              |

| 0x1E             | Read Mode 1              | dddd dddd dd00 0000     | 0xC040              |

| 0x20             | Read Mode 2              | ddd0 ddd0 0000 00dd     | 0x0000              |

| 0x21             | Read Mode 3              | 0000 0000 0000 00dd     | 0x0000              |

| 0x22             | Row Address Mode         | Oddd Oddd Oddd Oddd     | 0x0000              |

| 0x23             | Column Address Mode      | 0000 0ddd 00dd 0ddd     | 0x0000              |

| 0x2B             | Green1 Gain              | 0ddd dddd 0d0d dddd     | 0x0008              |

| 0x2C             | Blue Gain                | 0ddd dddd 0d0d dddd     | 0x0008              |

| 0x2D             | Red Gain                 | Oddd dddd OdOd dddd     | 0x0008              |

| 0x2E             | Green2 Gain              | 0ddd dddd 0d0d dddd     | 0x0008              |

| 0x35             | Global Gain              | dddd dddd dddd          | 0x0008              |

| 0x49             | Black Level              | 0000 0ddd dddd dddd     | 0x00A8              |

| 0x4B             | Row Black Default Offset | 0000 0ddd dddd dddd     | 0x0028              |

| 0x5D             | BLC Delta Thresholds     | Oddd dddd Oddd dddd     | 0x2D13              |

| 0x5F             | Cal Threshold            | dddd dddd dddd dddd     | 0x231D              |

| 0x60             | Green1 Offset            | 0000 000d dddd dddd     | 0x0020              |

| 0x61             | Green2 Offset            | 0000 000d dddd dddd     | 0x0020              |

| 0x62             | Black Level Calibration  | dddd d000 0000 00dd     | 0x0000              |

| 0x63             | Red Offset               | 0000 0ddd dddd dddd     | 0x0020              |

| 0x64             | Blue Offset              | 0000 0ddd dddd dddd     | 0x0020              |

| 0xF8             | Chip Enable/Synchronize  | 0000 0000 0000 00dd     | 0x0001              |

| 0xFF             | Chip Version             | 0001 0110 0000 0001     | 0x1611              |

#### NOTE:

1 = always 1

0 = always 0

d = programmable

? = read only

## **Table 5: Reserved Register List and Default Values**

| REGISTER # (HEX) | DESCRIPTION | DEFAULT VALUE (HEX) |

|------------------|-------------|---------------------|

| 0x27             | Reserved    | 0x0001              |

| 0x29             | Reserved    | 0x0401              |

| 0x30             | Reserved    | 0x0000              |

| 0x32             | Reserved    | 0x0008              |

| 0x3C             | Reserved    | 0x0010              |

| 0x3D             | Reserved    | 0x0005              |

| 0x3E             | Reserved    | 0x0003              |

| 0x3F             | Reserved    | 0x0002              |

| 0x40             | Reserved    | 0x0005              |

| 0x41             | Reserved    | 0x0003              |

| 0x42             | Reserved    | 0x0003              |

| 0x43             | Reserved    | 0x0003              |

| 0x44             | Reserved    | 0x0003              |

| 0x45             | Reserved    | 0x0010              |

| 0x46             | Reserved    | 0x0010              |

| 0x47             | Reserved    | 0x0010              |

| 0x48             | Reserved    | 0x0010              |

| 0x4A             | Reserved    | 0x0010              |

| 0x4C             | Reserved    | 0x0030              |

| 0x4D             | Reserved    | 0x0020              |

| 0x4E             | Reserved    | 0x0010              |

| 0x4F             | Reserved    | 0x0028              |

| 0x50             | Reserved    | 0x8004              |

| 0x51             | Reserved    | 0x0002              |

| 0x52             | Reserved    | 0x8004              |

| 0x53             | Reserved    | 0x0002              |

| 0x54             | Reserved    | 0x0010              |

| 0x55             | Reserved    | 0x0010              |

| 0x56             | Reserved    | 0x0020              |

| 0x5B             | Reserved    | 0x0007              |

| 0x5C             | Reserved    | 0x071C              |

| 0x5E             | Reserved    | 0x5364              |

| 0x65             | Reserved    | 0x0000              |

| 0x67             | Reserved    | 0x3FFF              |

| 0x68             | Reserved    | 0x0000              |

| 0x69             | Reserved    | 0x0000              |

| 0x6A             | Reserved    | 0x0000              |

| 0x6B             | Reserved    | 0x0000              |

| 0x6C             | Reserved    | 0x0000              |

| 0x6D             | Reserved    | 0x0000              |

| 0x6E             | Reserved    | 0x0000              |

| 0x70             | Reserved    | 0x00A3              |

| 0x71             | Reserved    | 0xA204              |

| 0x72             | Reserved    | 0xA006              |

| 0x73             | Reserved    | 0x260A              |

| 0x74             | Reserved    | 0x280C              |

## Table 5: Reserved Register List and Default Values (continued)

| REGISTER # (HEX) | DESCRIPTION | DEFAULT VALUE (HEX) |

|------------------|-------------|---------------------|

| 0x75             | Reserved    | 0x520D              |

| 0x76             | Reserved    | 0x7054              |

| 0x77             | Reserved    | 0x0000              |

| 0x78             | Reserved    | 0x9C57              |

| 0x79             | Reserved    | 0x9E02              |

| 0x7A             | Reserved    | 0x9E04              |

| 0x7B             | Reserved    | 0x9E06              |

| 0x7C             | Reserved    | 0xA006              |

| 0x7D             | Reserved    | 0x5308              |

| 0x7E             | Reserved    | 0x3208              |

| 0x7F             | Reserved    | 0x7C52              |

| 0x80             | Reserved    | 0x004E              |

| 0x81             | Reserved    | 0x4E00              |

| 0x82             | Reserved    | 0x4C02              |

| 0x83             | Reserved    | 0x480C              |

| 0x84             | Reserved    | 0x4A0E              |

| 0x86             | Reserved    | 0x2E0C              |

| 0x87             | Reserved    | 0x0000              |

| 0x89             | Reserved    | 0x4C02              |

| 0x8A             | Reserved    | 0x0000              |

| 0x8B             | Reserved    | 0x4F0A              |

| 0x8C             | Reserved    | 0x3A0A              |

| 0x90             | Reserved    | 0x061F              |

| 0x91             | Reserved    | 0x0000              |

| 0x92             | Reserved    | 0x0001              |

| 0xF1             | Reserved    | 0x0000              |

| 0xFA             | Reserved    | 0x0000              |

| 0xFB             | Reserved    | 0x0000              |

| 0xFC             | Reserved    | 0x0000              |

| 0xFD             | Reserved    | 0x0000              |

#### NOTE:

Even reading some of these registers will cause this part to go into an unknown state.

### **Register Description**

### **Table 6: Register Descriptions**

| REGISTER                         | BIT     | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip ID                          |         |                                                                                                                                                                                                                                                                                                                                          |

| 0x00                             | 15:0    | This register is read-only and gives the chip identification number: 0x1611.                                                                                                                                                                                                                                                             |

| Row Start                        |         |                                                                                                                                                                                                                                                                                                                                          |

| 0x01                             | 10:0    | First row to be read out—default = 0x0014 (20), register value must be an even number.                                                                                                                                                                                                                                                   |

| Column Start                     |         |                                                                                                                                                                                                                                                                                                                                          |

| 0x02                             | 11:0    | First column to be read out—default = 0x0020 (32), register value must be an even number.  Note: If column bin is enabled, the value must be a multiple of Reg0x23 [5:4] + 1.                                                                                                                                                            |

| Row Size                         |         |                                                                                                                                                                                                                                                                                                                                          |

| 0x03                             | 10:0    | Window height (number of rows - 1)—default = 0x5FF (1535), register value must be an odd number. Minimum value for 0x03 = 0x0001.                                                                                                                                                                                                        |

| Column Size                      |         |                                                                                                                                                                                                                                                                                                                                          |

| 0x04                             | 10:0    | Window width (number of columns - 1)— $default = 0x7FF$ (2047), register value must be an odd number. Minimum value for $0x04 = 0x0001$ .                                                                                                                                                                                                |

| Horizontal Bla                   | ank     |                                                                                                                                                                                                                                                                                                                                          |

| 0x05                             | 10:0    | Horizontal Blank—default = 0x008E (142 pixels). Minimum value = 0x0015 (21).                                                                                                                                                                                                                                                             |

| Vertical Blank                   | (       |                                                                                                                                                                                                                                                                                                                                          |

| 0x06                             | 10:0    | Vertical Blank—default = 0x0019 (25 rows). Minimum value = 0x0003 (3).                                                                                                                                                                                                                                                                   |

| Output Contr<br>This register co |         | arious features of the output format for the sensor.                                                                                                                                                                                                                                                                                     |

| 0x07                             | 0       | Synchronize changes.  0 = normal operation, update changes to registers that affect image brightness (integration time, shutter delay, gain, horizontal and vertical blank, window size, row/column skip, or row mirror) at the next frame boundary.  1 = do not update any changes to these settings until this bit is returned to "0." |

|                                  | 1       | Chip Enable.  1 = normal operation.  0 = sensor readout is stopped and analog control signals are put in a state which draws minimal power.                                                                                                                                                                                              |

|                                  | 6       | Override pixel data.  0 = normal operation.  1 = output programmed test data (see Reg0x32). First valid columns will output contents of test data register; second columns will output inverted data. Third columns will output non-inverted data, fourth inverted, etc.                                                                 |

| Shutter Width                    | n Upper |                                                                                                                                                                                                                                                                                                                                          |

| 0x08                             | 15:0    | The most significant bits of the shutter width, which are combined with Shutter Width (Reg0x09). The total shutter width is therefore: (((Shutter_Width_Upper) x 65536) + Shutter_Width). This should allow a shutter width from about 50us to about 50s at default row time.                                                            |

| Shutter Width                    | า       |                                                                                                                                                                                                                                                                                                                                          |

| 0x09                             | 15:0    | Number of rows of integration, the exposure time; the time between when the rolling shutter resets a row and that row is read out, in rows.  Default = 0x0619 (1561). Minimum value = 0x0001 (1).                                                                                                                                        |

## **Table 6: Register Descriptions (continued)**

| REGISTER       | BIT    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pixel Clock Co | ontrol |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x0A           | 15     | Invert Pixel Clock—default = 0x00 (0) When set, line_valid, frame_valid, and data10_out will be set up to the rising edge of PIXCLK. When clear, they are set up to the falling edge. This is accomplished by inverting the PIXCLK output.                                                                                                                                                                                                                                                             |

|                | 10:8   | Shift Pixel Clock—default = 0x00 (0) Two's compliment value representing how far to shift the PIXCLK output pin relative to Dout, in CLKIN cycles. Positive values shift PIXCLK later in time relative to Dout (and thus relative to the internal array/datapath clock. No effect unless PIXCLK is divided by Divide Pixel Clock.                                                                                                                                                                      |

|                | 6:0    | Divide Pixel Clock —default = 0x00 (0) Produces a PIXCLK that is divided by the value times two. The value must be a power of 2. This will slow down the internal clock in the array control and datapath blocks, including pixel readout. It will not affect the two-wire serial interface clock. A value of 0 corresponds to a PIXCLK with the same frequency as CLK_IN. A value of 1 means f_PIXCLK = (f_CLK_IN / 2); 2 means f_PIXCLK = (f_CLK_IN / 4); 64 means f_PIXCLK = (f_CLK_IN / 128); etc. |

| Frame Restar   | t      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x0B           | 0      | Setting bit 0 to "1" of Reg0x0B will cause the sensor to abandon the readout of the current frame and restart from the first row. This register automatically resets itself to 0x0000 after the frame restart. The first frame after this event is considered to be a "bad frame" (see description for Reg0x20, bit 0).                                                                                                                                                                                |

| Shutter Delay  | /      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x0C           | 10:0   | Shutter delay—default = 0x0000 (0). This is the number of pixel clocks that the timing and control logic waits before asserting the reset for a given row.                                                                                                                                                                                                                                                                                                                                             |

| Reset          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x0D           | 0      | Setting this bit will put the sensor into reset mode, which will set the sensor to its default power-up state. Clearing this bit will resume normal operation.                                                                                                                                                                                                                                                                                                                                         |

| Read Mode 1    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x1E           | 8      | Snapshot Mode—default is 0 (continuous mode).  1 = enable Snapshot trigger signal can come from outside signal (trigger pin 8 on the sensor) or from serial interface register restart, i.e. programming a "1" to bit 0 of Reg0x0B.                                                                                                                                                                                                                                                                    |

|                | 9      | Strobe Enable—default is 0 (no strobe signal).  1 = enable strobe (signal output from the sensor during the time all rows are integrating). See strobe width for more information.                                                                                                                                                                                                                                                                                                                     |

|                | 10     | Strobe Width—default is 0 (strobe signal width at minimum length, one row of integration time, prior to Line_Valid going high).  1 = extend strobe width (strobe signal width extends to entire time all rows are integrating; shutter width must be >= row size + vertical blanking).                                                                                                                                                                                                                 |

|                | 11     | Strobe Override—default is 0 (strobe signal created by digital logic).  1 = override strobe signal (strobe signal is set high when this bit is set, low when this bit is set low. It is assumed that strobe enable is set to "0" if strobe override is being used).                                                                                                                                                                                                                                    |

| Read Mode 2    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x20           | 0      | No bad frames—1 = output all frames (including bad frames). 0 = default, only output good frames. A bad frame is defined as the first frame following a change to: window size or position, horizontal blanking, row or column skip, or mirroring.                                                                                                                                                                                                                                                     |

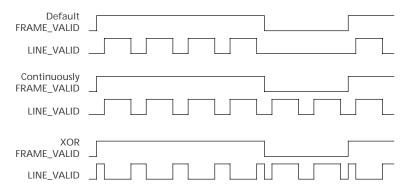

|                | 9      | 1 = "Continuous" LINE_VALID (continue producing Line_Valid during vertical blanking). 0 = Normal Line_Valid (default, no Line_Valid during vertical blank).                                                                                                                                                                                                                                                                                                                                            |

|                | 10     | 1 = LINE_VALID = "Continuous" LINE_VALID XOR FRAME_VALID. 0 = LINE_VALID determined by bit 9 (default).                                                                                                                                                                                                                                                                                                                                                                                                |

## **Table 6: Register Descriptions (continued)**

| REGISTER           | BIT    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Mode 3        | DII    | DESCRIF HOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x21               | 0      | Global Reset—default = 0x0000—when set, snapshot mode will make use of the global reset                                                                                                                                                                                                                                                                                                                                                                                                              |

| UNZ I              |        | — that is, the entire array will be released from reset simultaneously. Ineffective unless                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    |        | Snapshot (Reg0x1E[8]) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | 1      | Use GSHT_CTL—default = 0x0000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    |        | When set, the leading edge of the GSHT_CTL pad signal will be used to start the shutter sequence in snapshot mode, and the trailing edge will start the read sequence. When clear, the leading edge of the TRIGGER pad signal will be used to initiate the shutter sequence, the trailing edge of GSHT_CTL will start the exposure, and the trailing edge of the TRIGGER pad signal will be used to start the strobe and readout. Ineffective unless Snapshot (Reg0x1E[8]) and Global Reset are set. |

| <b>Row Address</b> | Mode   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x22               | 2:0    | Row Skip—the number of row-pairs to skip for every row read. For example, "0" means read every row pair. "1" is skip 2x; 2 is skip 3x, etc. If Row Bin is non-zero, this should be set to the interval between the first rows in each bin. For full binning, Row Skip equals Row Bin.                                                                                                                                                                                                                |

|                    | 5:4    | Row Bin—the number of rows to be read per row output minus one. For normal read out, this should be "0." For Bin 2x, it should be "1"; for Bin 3x, it should be "2."                                                                                                                                                                                                                                                                                                                                 |

| Column Addr        | ess Mo | de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x23               | 2:0    | Column Skip—the number of column-pairs to skip for every pair read. Zero means read every column. "1" means skip one pair for every pair read (Skip 2x); 2 means skip 2 pairs for every pair read (Skip 3x) etc.                                                                                                                                                                                                                                                                                     |

|                    | 5:4    | Column Bin—the number of columns to be addressed per column read out minus one. Zero will produce standard 1:1 read out. A value of "1" will produce Bin 2x; "2" would be Bin 3x. Note: Column start address value must be a multiple of Reg0x23 [5:4] + 1.                                                                                                                                                                                                                                          |

| Green1 Gain        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x2B               | 6:0    | Green1 analog gain—default = 0x08 (8) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | 14:8   | Green1 digital gain—default = 0x00 (0) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Blue Gain          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x2C               | 6:0    | Blue analog gain—default = 0x08 (8) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 14:8   | Blue digital gain—default = 0x00 (0) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Red Gain           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x2D               | 6:0    | Red analog gain—default = 0x08 (8) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | 14:8   | Red digital gain—default = 0x00 (0) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Green2 Gain        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x2E               | 6:0    | Green2 analog gain—default = 0x08 (8) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | 14:8   | Green2 digital gain—default = 0x00 (0) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Global Gain        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x35               | 6:0    | Global analog gain—default = 0x08 (8) = 1x gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | 14:8   | Global digital gain—default = 0x00 (0) = 1x gain. This register can be used to set all four gains at once. When read, it will return the value stored in Reg0x2B.                                                                                                                                                                                                                                                                                                                                    |

| Black Level        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x49               | 11:2   | Desired black level in image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## **Table 6: Register Descriptions (continued)**

| REGISTER BIT DESCRIPTION |            |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|--------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                          |            | on Coarse Thresholds                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 0x5D                     | 6:0        |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| OAJD                     |            | Low Coarse Threshold—default = 0x13. This value should be less than Low Target Threshold. See High Coarse Threshold below.                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                          | 14:8       | High Coarse Threshold—default = 0x2D. If the average black value for a color is higher than this value or lower than Low Coarse Threshold, the coarse mode will be activated (if enabled). Once the black level is between the High Coarse Threshold and the Low Coarse Threshold, the fine method will be used. This value should be set no lower than High Target Threshold.                   |  |  |  |  |  |  |  |

| Black Level C            | alibration | on Target Thresholds                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 0x5F                     | 6:0        | Thres_lo: Lower threshold for black level in units of ADC LSBs—default = 29.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                          | 14:8       | Thres_hi: Upper threshold for black level in units of ADC LSBs—default = 35. When the black value for a color is within these thresholds, it will be considered to be on target.                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Green1 Offse             | t          |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 0x60                     | 8:0        | Cal Green1—Two's compliment representation of analog offset correction value for Green1.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Green2 Offse             |            |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 0x61                     | 8:0        | Cal Green2—Two's compliment representation of analog offset correction value for Green2.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Black Level C            |            |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 0x62                     | 0          | Manual override of black level correction.  1 = override automatic black level correction with programmed values.  0 = normal operation (default).                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                          | 1          | Force/disable black level calibration.  0 = Enable Offset Correction (default).  1 = disable Offset Correction Voltage (Offset Correction Voltage = 0.0V).                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                          | 12         | Recalculate Black Level—1 = start a new running digitally filtered average for the black level (this is internally reset to "0" immediately), and do a rapid sweep to find the new starting point.  0 = normal operation (default).                                                                                                                                                              |  |  |  |  |  |  |  |

|                          | 13         | Lock Red/Blue Calibration—when set, only one calibration value will be used for both red and blue channels. Default is 0, set to "0" at all times.  Note: Gain for Red and Blue channels must be equal for setting to be effective.                                                                                                                                                              |  |  |  |  |  |  |  |

|                          | 14         | Lock Green Calibration—when set, only one calibration value will be used for both Green1 and Green2 channels. Default is 0, set to "0" at all times.  Note: Gain for Green1 and Green2 channels must be equal for setting to be effective.                                                                                                                                                       |  |  |  |  |  |  |  |

| Red Offset               | 1          |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 0x63                     | 8:0        | Cal Red. Two's compliment representation of analog offset correction value for Red.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Blue Offset              |            |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |