# **ICs for Communications**

Analog Front End for Telephone Systems SAM-AFE

**PSB 4851 Version 2.1**

Data Sheet 09.99

| PSB 4851<br>Revision His         | story:                      | Current Version: 09.99                       |

|----------------------------------|-----------------------------|----------------------------------------------|

| Previous Version: none           |                             |                                              |

| Page<br>(in previous<br>Version) | Page<br>(in new<br>Version) | Subjects (major changes since last revision) |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4μC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

#### Edition 09.99

Published by Infineon Technologies AG TR, Balanstraße 73, 81541 München

© Infineon Technologies AG 1999.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| 1        | Overview                                           | 4  |

|----------|----------------------------------------------------|----|

| 1.1      | Features                                           |    |

| 1.2      | Pin Configuration                                  | 6  |

| 1.3      | Pin Definitions and Functions                      |    |

| 1.4      | Logic Symbol                                       | 9  |

| 1.5      | Functional Block Diagram                           |    |

| 1.6      | System Integration                                 | 10 |

| 1.6.1    | Analog Featurephone with Digital Answering Machine | 10 |

| 1.6.2    | DECT Basestation with Full Duplex Featurephone     |    |

| 2        | Functional Description                             | 13 |

| _<br>2.1 | Signal Paths and Functional Units                  |    |

| 2.2      | Line Powered Operation                             |    |

| 2.3      | Attenuation Plan                                   |    |

| 2.4      | Analog Front End Interface                         |    |

| 2.5      | Serial Control Interface                           |    |

| 2.6      | Test Loops                                         |    |

| 2.6.1    | Analog Loops                                       |    |

| 2.6.2    | Digital Loops                                      |    |

| 3        | Register Description                               | 25 |

| 4        | Electrical Characteristics                         | 34 |

| 4.1      | Absolute Maximum Ratings                           |    |

| 4.2      | DC Characteristics                                 |    |

| 4.3      | AC Characteristics                                 |    |

| 5        | Package Outlines                                   | 44 |

### 1 Overview

The PSB 4851 integrates all amplifiers to directly connect the transducers to the chip. It features two completely independent channels. An integrated analog multiplexer allows the connection of three signal sources (handset microphone, speakerphone microphone, analog line) to the two channels.

Furthermore the PSB 4851 supports a sophisticated power management and a loop mode in the analog domain. These features can be used to implement a line powered mode for emergency operation of the phone.

The chip is programmed by a simple four wire serial control interface.

Data Sheet 4 09.99

# **Analog Front End for Telephone Systems SAM-AFE**

**PSB 4851**

Version 2.1 CMOS

#### 1.1 Features

- Direct connection to handset

- Direct connection to microphone

- Direct connection to loudspeaker (50  $\Omega$ )

- Low power emergency operation

- Serial control interface for programming

- 3.3V or 5V operation (full operating mode)

- 3V-5V voltage range (emercency mode)

- 2.4 V reference voltage

- Two differential inputs

- · Support for controlled loudhearing

- Compliant to G.712

| Туре     | Package    |

|----------|------------|

| PSB 4851 | P-TQFP-144 |

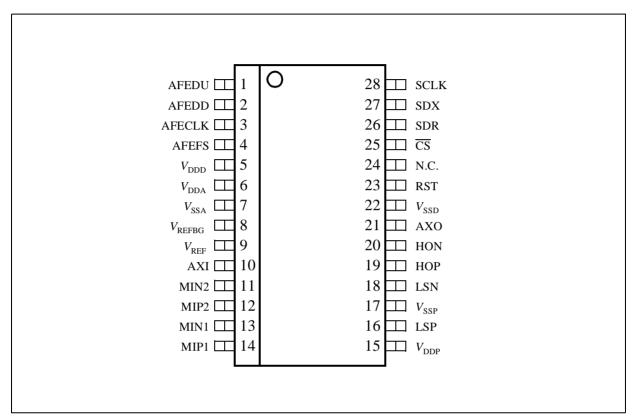

## 1.2 Pin Configuration

(top view)

Figure 1-1 Pin Configuration

## 1.3 Pin Definitions and Functions

Table 1-1 Pin Definitions and Functions

| Pin No.<br>P-DSO-28-1 | Symbol        | Dir. | Reset | Function                                                                                                                                   |

|-----------------------|---------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 5                     | $V_{ m DDD}$  | -    | -     | Power supply (3.0V - 3.6V or 4.75V - 5.25V) Power supply for digital parts. Must be at the same level as $V_{\rm DDA}$ and $V_{\rm DDP}$ . |

| 6                     | $V_{DDA}$     | -    | -     | Power supply (3.0V - 3.6V or 4.75V - 5.25V) Power supply for analog parts. Must be at the same level as $V_{\rm DDD}$ and $V_{\rm DDP}$ .  |

| 15                    | $V_{DDP}$     | -    | -     | Power supply (3.0V - 3.6V or 4.75V - 5.25V) Power supply for amplifiers. Must be at the same level as $V_{\rm DDA}$ and $V_{\rm DDD}$ .    |

| 22                    | $V_{\rm SSD}$ | -    | -     | Power supply (0 V) Ground for digital parts.                                                                                               |

| 7                     | $V_{\rm SSA}$ | -    | -     | Power supply (0 V) Ground for analog parts.                                                                                                |

| 17                    | $V_{\rm SSP}$ | -    | -     | Power supply (0 V) Ground for amplifiers.                                                                                                  |

| 1                     | AFEDU         | 0    | L     | Data Upstream: Data output to PSB 4860.                                                                                                    |

| 2                     | AFEDD         | I    | -     | Data Downstream: Data input from PSB 4860.                                                                                                 |

| 3                     | AFECLK        | I    | -     | Data Clock:<br>6.912 MHz clock.                                                                                                            |

| 4                     | AFEFS         | I    | -     | Frame Synchronization: 8kHz frame synchronization from PSB 4860.                                                                           |

| 28                    | SCLK          | I    | -     | Serial Clock: Clock for serial control interface (SCI).                                                                                    |

| 27                    | SDX           | OD   | Н     | Serial Data Transmit: Data output for serial control interface (SCI).                                                                      |

| 26                    | SDR           | I    | -     | Serial Data Receive: Data input for serial control interface (SCI).                                                                        |

| 25                    | CS            | I    | -     | Chip Select: Select signal for serial control interface (SCI).                                                                             |

Table 1-1 Pin Definitions and Functions

| P-DSO-28-1 | Symbol             | Dir.   | Reset      | Function                                                                                                                                                                                                     |

|------------|--------------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | RST                | I      | -          | Reset: Active high reset signal.                                                                                                                                                                             |

| 10         | AXI                | I      | -          | Auxiliary Input: Single ended analog input (e.g. line in)                                                                                                                                                    |

| 13<br>14   | MIN1<br>MIP1       | I<br>I | -          | Microphone Input 1: This input provides a highly symmetrical differential input for commonly used telephone microphones.                                                                                     |

| 11<br>12   | MIN2<br>MIP2       | I<br>I | -          | Microphone Input 2: This input provides a highly symmetrical differential input for commonly used telephone microphones.                                                                                     |

| 21         | AXO                | 0      | 0 V        | Auxiliary Output: Single ended analog output (e.g line out).                                                                                                                                                 |

| 19<br>20   | HOP<br>HON         | 0      | 0 V<br>0 V | Handset Earpiece Output: Differential outputs which can drive common handset earpiece transducers (200 $\Omega$ ) directly.                                                                                  |

| 16<br>18   | LSP<br>LSN         | 0      | 0 V<br>0 V | Loudspeaker Output: Differential outputs which can drive a $50\Omega$ loudspeaker at 5V or a $25\Omega$ loudspeaker at 3.3V directly. A piezo transducer can be used for ringing instead of the loudspeaker. |

| 8          | V <sub>REFBG</sub> | О      | 0 V        | Reference Bandgap Voltage Connection to external 22 nF capacitor for low pass filtering.                                                                                                                     |

| 9          | $V_{REF}$          | 0      | 0 V        | Reference Voltage (2.4 V): Output for biasing external circuitry, e.g. electret microphone. Connection to external 100 nF capacitor.                                                                         |

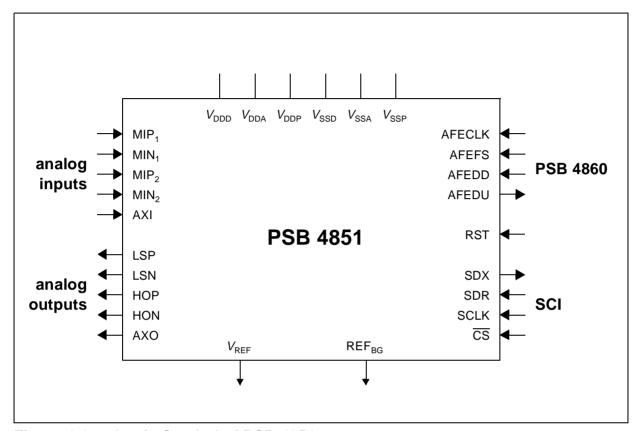

## 1.4 Logic Symbol

Figure 1-2 Logic Symbol of PSB 4851

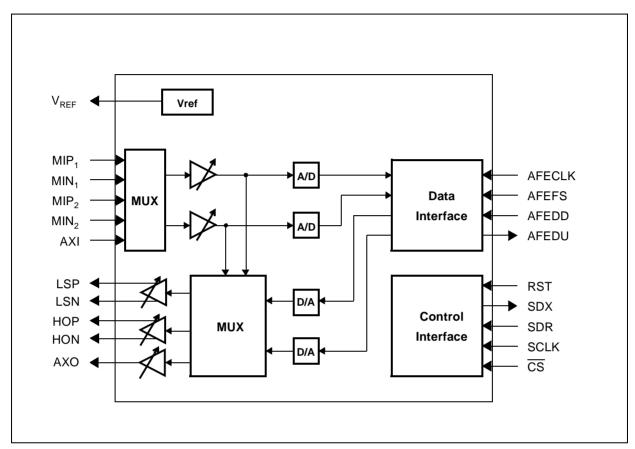

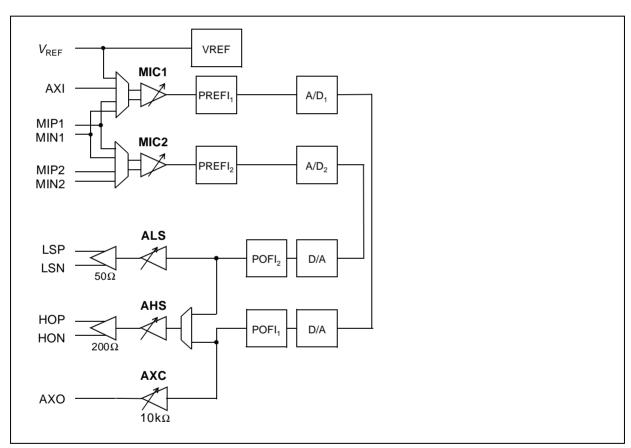

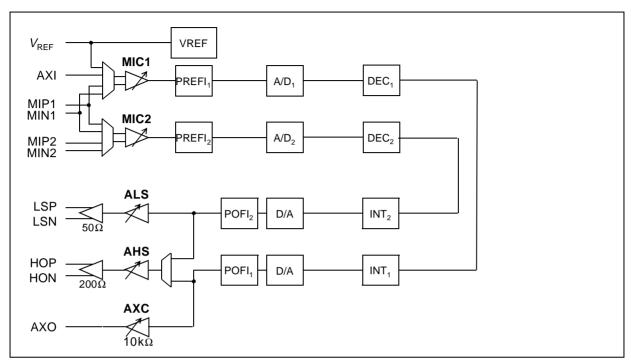

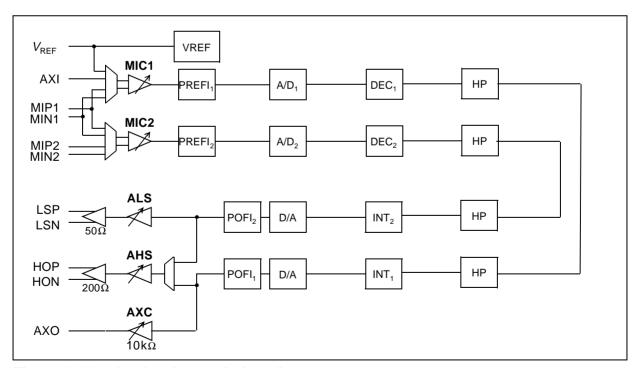

## 1.5 Functional Block Diagram

Figure 1-3 Block Diagram of PSB 4851

## 1.6 System Integration

The PSB 4851 is the standard analog interface for several digital telecommunication ICs such as:

- PSB 4860 (digital answering machine)

- PSB 2170 (acoustic echo canceller)

The PSB 4851 is especially suited for applications that need two independent analog channels where one codec interfaces to a loudspeaker/microphone combination while the other codec serves the line.

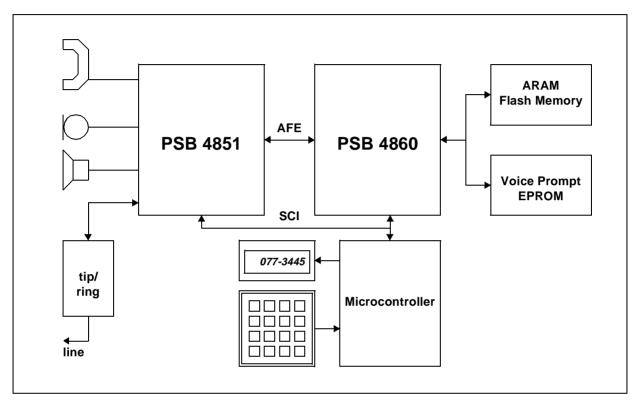

## 1.6.1 Analog Featurephone with Digital Answering Machine

Figure 1-4 shows an example of an analog telephone system. The telephone can operate during power failure by line powering. In this case only the handset is active. All other parts of the chipset are shut down leaving enough power for the external microcontroller to perform basic tasks like keyboard monitoring.

For answering machine operation the voice data is stored in ARAM or Flash Memory devices and voice prompts can be played back from an optional voice prompt EPROM. If Flash Memory is used the functionality of the voice EPROM can be realized by the Flash Memory devices.

Figure 1-4 Analog Full Duplex Speakerphone with Digital Answering Machine

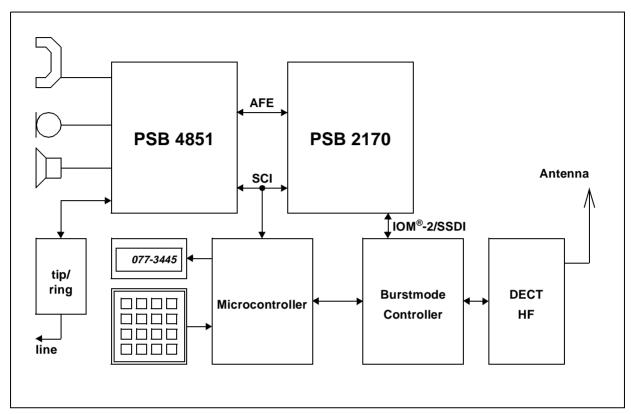

## 1.6.2 DECT Basestation with Full Duplex Featurephone

Figure 1-5 shows a DECT basestation with acoustic echo cancellation based on the PSB 2170. The full duplex featurephone can be switched to the basestation or a mobile handset dynamically. For programming the serial control interface (SCI) is used while voice data is transferred via the strobed serial data interface (SSDI).

Data Sheet 11 09.99

Figure 1-5 DECT Basestation with Full Duplex Speakerphone

## 2 Functional Description

The PSB 4851 provides two bidirectional channels from the analog domain to the digital domain, an internal loopback and a sophisticated power management for line-powered operation. The first section describes the signal paths and functional units of the PSB 4851 while the second section discusses the support of the line powered operation.

## 2.1 Signal Paths and Functional Units

The PSB 4851 supports three analog inputs, three analog outputs and two digital channels (Table 2-1).

Table 2-1

| Analog Inputs         | Pins                           | Comment                                                           |

|-----------------------|--------------------------------|-------------------------------------------------------------------|

| Analog inputs         | 1 1119                         | Comment                                                           |

|                       | AXI                            | line input from tip/ring interface                                |

|                       | MIP1, MIN1                     | mic. 1, e.g. speakerphone microphone                              |

|                       | MIP2, MIN2                     | mic. 2, e.g. handset microphone                                   |

| <b>Analog Outputs</b> | AXO                            | line output to tip/ring interface                                 |

|                       | HOP, HON                       | handset earpiece                                                  |

|                       | LSP, LSN                       | speakerphone loudspeaker                                          |

| Digital Channels      | AFEDD, AFEDU,<br>AFEFS, AFECLK | Channel 1 and 2 of AFE interface (to/<br>from PSB 2170, PSB 4860) |

|                       | / =: 0, / ti = 0=i t           | == =                                                              |

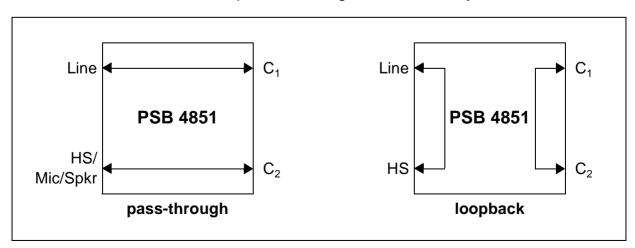

These signals can be routed in either *pass-through* or *loopback* mode (Fig. 2-1). In loopback mode different loops are available for test purposes and line powered operation. In loopback mode the digital part of the PSB 4851 can be completely shut down if it is not needed. The loop on the analog side remains fully functional.

Figure 2-1 Basic Configurations of PSB 4851

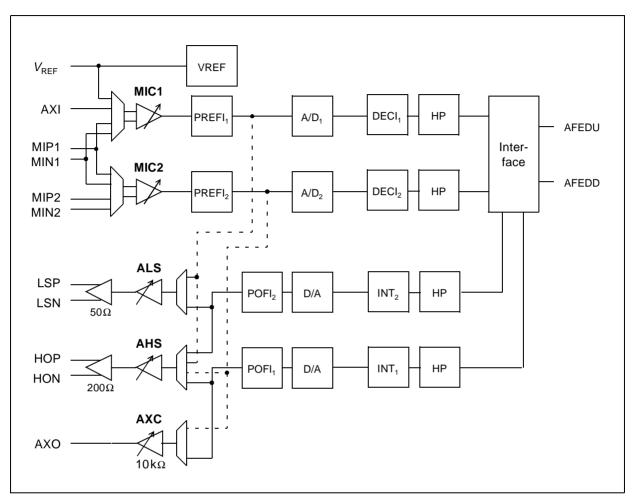

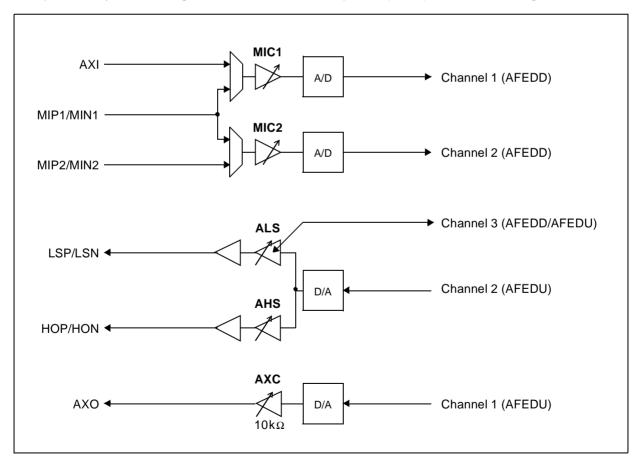

A detailed functional diagram of the PSB 4851 is shown in figure 2-2.

Figure 2-2 Detailed Block Diagram of PSB 4851

Two differential inputs for microphones and one single ended input for the tip/ring interface are fed to two analog input amplifiers (MIC2, MIC1). These amplifiers can be programmed for a gain of up to 42 dB in steps of 6 dB.

For both the loudspeaker and the handset transducer differential amplifiers (ALS, AHS) are provided. These amplifiers can be programmed within a range of 33 (24) dB in steps of 3 dB or muted.

A third programmable amplifier (AXC) is provided for the tip/ring interface.

The high passes (HP) have a cut-off frequency of 150 Hz. These filters can be disabled individually for the receive and transmit direction.

## 2.2 Line Powered Operation

The PSB 4851 supports line powered operation by a flexible power management. The controller can power down all elements that are not needed for the current task. In particular, the following three states are useful in line powered operation:

#### 1. Idle

All elements are powered down. The power consumption is minimal. This state is automatically entered by reset.

#### 2. Ringing

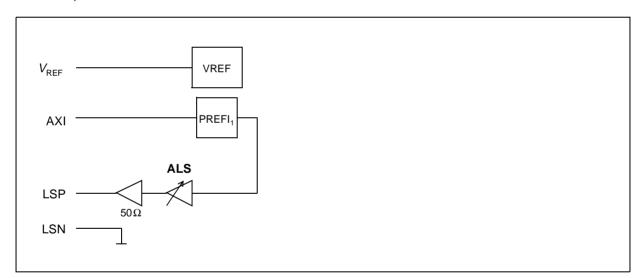

MIC1 is in bypass mode, PREFI1 is powered up and ALS is connected to PREFI1. Therefore a signal fed into AXI is amplified by ALS and output at LSP/LSN. In order to maximize the loudness of the ringing signal one of the output drivers of ALS (either LSP or LSN) can be forced to GND thus providing a single ended output. Figure 2-3 shows the signal routing and the remaining active elements in this mode (single ended mode).

Figure 2-3 Emergency Ringing Mode

#### 3. Speech

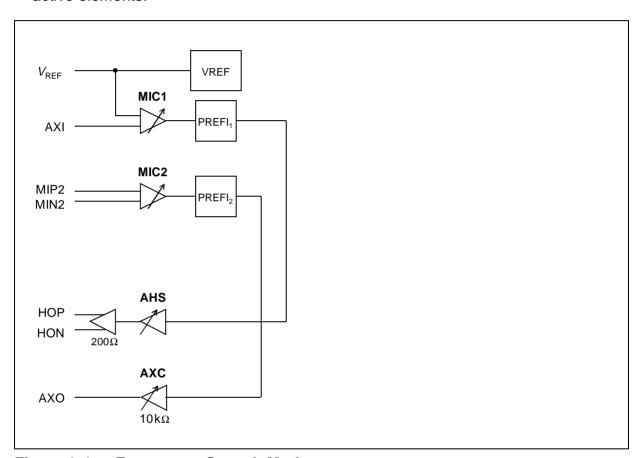

MIC1, PREFI1, MIC2, PREFI2, AHS and AXC are powered up. AHS is connected to PREFI1 and AXC is connected to PREFI2. Therefore the signal fed into MIP2/MIN2 is amplified by MIC2 and AXC and output at AXO. The signal fed into AXI is amplified by MIC1 and AHS and output at HOP/HON. Figure 2-4 shows the signal routing and the active elements.

Figure 2-4 Emergency Speech Mode

Note: An external circuitry should be provided to detect power failure and inform the controller. The controller in turn should reduce the gain of the ALS amplifier if necessary to avoid excessive power consumption.

Note: The serial control interface must remain operational even when some of the connected devices are without power supply. Some devices have clamping diodes at their inputs and might block the bus.

#### 2.3 Attenuation Plan

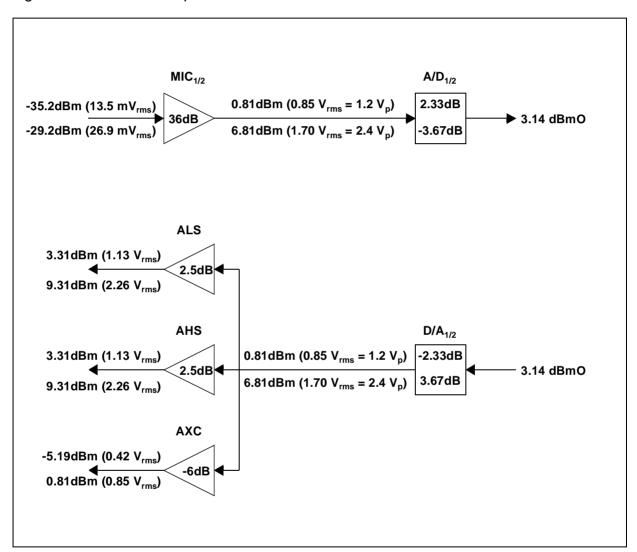

Figure 2-5 shows the attenuation plan for 3.3V and 5V operation. At the digital side the reference signal level is 3.14dBmO (maximum digital signal value). The stated gain settings at the amplifiers are the maximum gains for the guaranteed transmission characteristics. Values above the signal lines refer to 3.3V operation, values below the signal lines refer to 5V operation.

Figure 2-5 Attenuation Plan

## 2.4 Analog Front End Interface

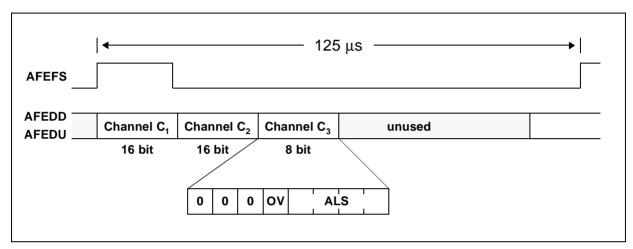

The PSB 4851 uses a four wire interface similar to the IOM<sup>®</sup>-2 interface to exchange information in the digital domain. The main difference is that all timeslots and the channel assignments are fixed as shown in figure 2-6.

Figure 2-6 AFE Interface - Frame Structure

Voice data is transferred in 16 bit linear coding in two bidirectional channels  $C_1$  and  $C_2$ . For controlled loudhearing an auxiliary channel  $C_3$  is used to transfer the current setting of the loudspeaker amplifier ALS to the PSB 4860. The remaining bits are fixed to zero. In the other direction  $C_3$  transfers an override value for ALS from the PSB 4860 to the PSB 4851. An additional override bit OV determines if the currently transmitted value should override the AOAR:LSC setting. The AOAR:LSC setting is not affected by  $C_3$ :ALS override. Table 2-2 shows the source control of the gain for the ALS amplifier.

**Table 2-2** Source control of the gain for the ALS amplifier

| AOPR:OVRE | C <sub>3</sub> :OV | Gain of ALS amplifier |

|-----------|--------------------|-----------------------|

| 0         | -                  | AOAR:LSC              |

| 1         | 0                  | AOAR:LSC              |

| 1         | 1                  | C <sub>3</sub> :ALS   |

Therefore the PSB 4860 can control the gain of the loudspeaker amplifier (ALS) independently from the gain of the handset amplifier (AHS) as shown in figure 2-7.

Figure 2-7 AFE Interface - Signal Routing

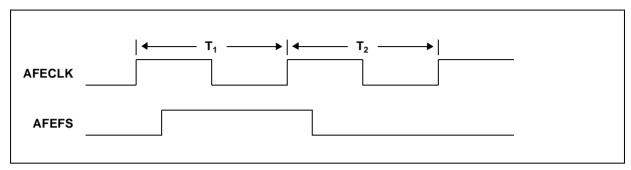

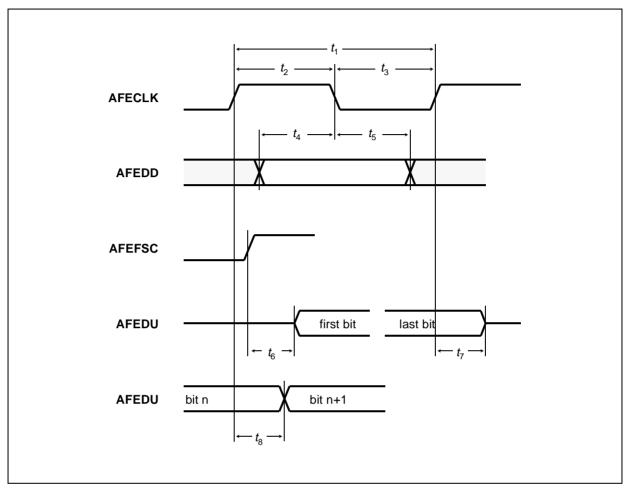

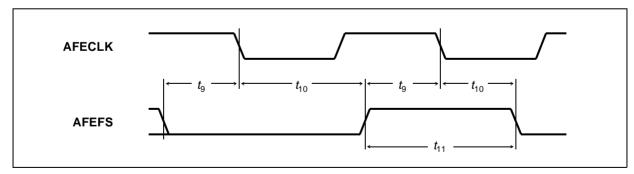

Figure 2-8 shows the synchronization of a frame by AFEFS. The first clock of a new frame ( $T_1$ ) is indicated by AFEFS switching from low to high before the falling edge of  $T_1$ . AFEFS may remain high during subsequent cycles up to  $T_{32}$ .

Figure 2-8 AFE Interface - Frame Start

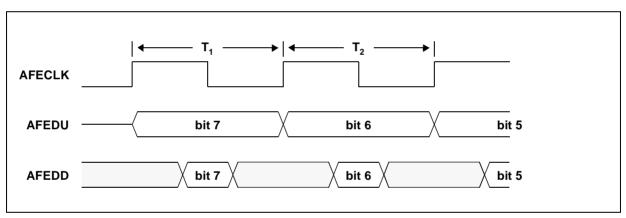

The data is shifted out with the rising edge of AFECLK and sampled at the falling edge of AFECLK (figure 2-9).

Figure 2-9 AFE Interface - Data Transfer

If AOPR:OVRE is not set, the channel  $C_3$  is not used by the PSB 4851. All values ( $C_1$ ,  $C_2$ ,  $C_3$ :ALS) are transferred MSB first. The data clock (AFECLK) rate is fixed at 6.912 MHz. Table 2-3 shows the clock cycles used for the three channels.

Table 2-3 Clock cycles

| Clock Cycles                      | AFEDD (driven by PSB 4860) | AFEDU (driven by PSB 4851) |

|-----------------------------------|----------------------------|----------------------------|

| T <sub>1</sub> -T <sub>16</sub>   | C <sub>1</sub> data        | C₁ data                    |

| T <sub>17</sub> -T <sub>32</sub>  | C <sub>2</sub> data        | C <sub>2</sub> data        |

| T <sub>33</sub> -T <sub>40</sub>  | C <sub>3</sub> data        | C <sub>3</sub> data        |

| T <sub>41</sub> -T <sub>864</sub> | 0                          | tristate                   |

#### 2.5 Serial Control Interface

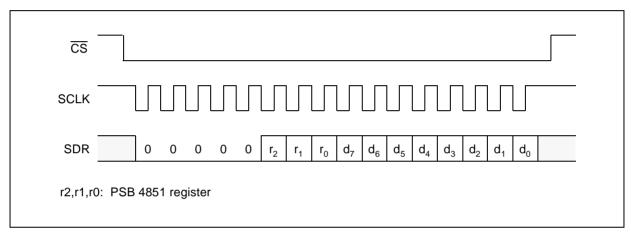

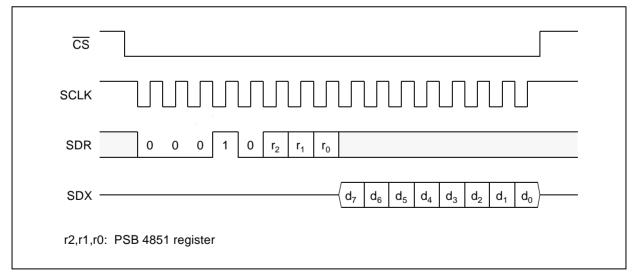

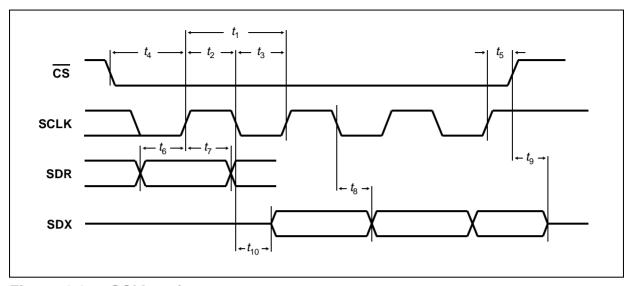

The serial control interface (SCI) uses four lines. Data is transferred by the lines SDR and SDX at the rate given by SCLK. The falling edge of CS indicates the beginning of an access. Data is sampled by the PSB 4851 at the rising edge of SCLK and shifted out at the falling edge of SCLK. Each access must be terminated by a rising edge of CS.

Data is transferred in bytes (8 bits). Data from the controller is latched into a register at the rising edge of  $\overline{CS}$ . Figure 2-10 shows a write access to the PSB 4851 and figure 2-11 shows a read access to the PSB 4851.

Figure 2-10 SCI Interface - Write Access

Figure 2-11 SCI Interface - Read Access

## 2.6 Test Loops

The PSB 4851 supports several internal loops for performance testing. There are two kinds of loops: analog loops and digital loops.

## 2.6.1 Analog Loops

Analog loops connect the analog inputs to the analog outputs within the PSB 4851. Emergency mode is the most basic loop involving a minimal amount of components within the chip. These loops can be programmed by the bit field ALTF of register TFCR. The next figures show the programmable loops besides emergency mode.

Figure 2-12 Analog Loop via Converter

Figure 2-13 Analog Loop via 64 kHz

The loop via 64 kHz incorporates only a part of the interpolation and decimation filters.

Figure 2-14 Analog Loop via Interface

## 2.6.2 Digital Loops

The digital loops can be programmed by bit field DLTF of register TFCR. These loops feed the input from the analog front end interface directly back to the analog front end interface. As no analog parts of the PSB 4851 are involved these loops are only useful for functional tests. The loops are as follows:

- Digital Loop via PCM register

Received data is fed back without modification.

- Digital Loop via 64 kHz

Received data is passed through the interpolation filters (INT<sub>1</sub>, INT<sub>2</sub>), fed back into the decimation filters (DEC<sub>1</sub>, DEC<sub>2</sub>) and then sent back.

# 3 Register Description

A summary of the registers of the PSB 4851 is presented in table 3-1.

Table 3-1

Summary of the registers

| Name | Reg | 7    |                   |    |   |      |      |       | 0    |

|------|-----|------|-------------------|----|---|------|------|-------|------|

| AIAR | 1   |      | MI                | C2 |   |      | MI   | C1    |      |

| AIPR | 2   | 0    | 0 ADC2 ADC1 EVREF |    |   |      | 0    | IS    | SS   |

| AOAR | 3   |      | HC                | OC |   |      | LS   | SC SC |      |

| AOCR | 4   | SEM  | M AXC             |    |   | DHOP | DHON | DLSP  | DLSN |

| AOPR | 5   |      | OSS DAC2          |    |   | DAC1 | PSS  | 0     | OVRE |

| TFCR | 6   | DHPR | DHPX ALTF         |    |   |      | DL   | TF    | 0    |

| TMR  | 7   | -    | _1)               | 0  | 0 | 0    | 0    | 0     | 0    |

<sup>1)</sup> undefined

All registers except TMR are set to 0 after reset.

## **REG 1: AIAR - AFE Input Amplification Register**

| 7    | 0    |

|------|------|

| MIC2 | MIC1 |

## MIC1 MIC1 amplifier control

| 3 | 2 | 1 | 0 | Description                                  |

|---|---|---|---|----------------------------------------------|

| 0 | 0 | 0 | 0 | MIC1and PREFI1 are in power down mode        |

| 0 | 0 | 0 | 1 | 0 dB amplification                           |

| 0 | 0 | 1 | 0 | 6 dB amplification                           |

| 0 | 0 | 1 | 1 | 12 dB amplification                          |

| 0 | 1 | 0 | 0 | 18 dB amplification                          |

| 0 | 1 | 0 | 1 | 24 dB amplification                          |

| 0 | 1 | 1 | 0 | 30 dB amplification                          |

| 0 | 1 | 1 | 1 | 36 dB amplification                          |

| 1 | 0 | 0 | 0 | 42 dB amplification                          |

| 1 | 1 | 1 | 1 | MIC1 is in bypass mode, PREFI1 is powered up |

## MIC2 MIC2 amplifier control

| 7 | 6 | 5 | 4 | Description                                  |

|---|---|---|---|----------------------------------------------|

| 0 | 0 | 0 | 0 | MIC2 and PREFI2 are in power-down mode       |

| 0 | 0 | 0 | 1 | 0 dB amplification                           |

| 0 | 0 | 1 | 0 | 6 dB amplification                           |

| 0 | 0 | 1 | 1 | 12 dB amplification                          |

| 0 | 1 | 0 | 0 | 18 dB amplification                          |

| 0 | 1 | 0 | 1 | 24 dB amplification                          |

| 0 | 1 | 1 | 0 | 30 dB amplification                          |

| 0 | 1 | 1 | 1 | 36 dB amplification                          |

| 1 | 0 | 0 | 0 | 42 dB amplification                          |

| 1 | 1 | 1 | 1 | MIC2 is in bypass mode, PREFI2 is powered up |

## **REG 2: AIPR - AFE Input Path Register**

| 7 |      |      |       |   |   | 0   |

|---|------|------|-------|---|---|-----|

| 0 | ADC2 | ADC1 | EVREF | 0 | 0 | ISS |

### ISS Input Source Selection

| 1 | 0 | Description                                              |

|---|---|----------------------------------------------------------|

| 0 | 0 | reserved                                                 |

| 0 | 1 | AXI connected to A/D1, MIP1/MIN1 connected to A/D2       |

| 1 | 0 | MIP1/MIN1 connected to A/D1, MIP2/MIN2 connected to A/D2 |

| 1 | 1 | AXI connected to A/D1, MIP2/MIN2 connected to A/D2       |

#### **EVREF Enable VREF**

0: VREF module is enabled when any other module needs the reference voltage

1: VREF module always enabled

#### ADC1 A/D Control 1

0:  $A/D_1$  is in power down mode

1: A/D₁ active

#### ADC2 A/D Control 2

0: A/D<sub>2</sub> is in power down mode

1: A/D<sub>2</sub> active

Note: If ADC1 and ADC2 are set to 0 then  $DEC_1$ ,  $DEC_2$ ,  $INT_1$ ,  $INT_2$  and the timing generation are also forced into power down mode.

## **REG 3: AOAR - AFE Output Amplification Register**

| 7   | 0   |

|-----|-----|

| HOC | LSC |

## LSC Loudspeaker Amplifier Control

| 3 | 2 | 1 | 0 | Description               |

|---|---|---|---|---------------------------|

| 0 | 0 | 0 | 0 | ALS is in power-down mode |

| 0 | 0 | 0 | 1 | 11.5 dB amplification     |

| 0 | 0 | 1 | 0 | 8.5 dB amplification      |

| 0 | 0 | 1 | 1 | 5.5 dB amplification      |

| 0 | 1 | 0 | 0 | 2.5 dB amplification      |

| 0 | 1 | 0 | 1 | -0.5 dB amplification     |

| 0 | 1 | 1 | 0 | -3.5 dB amplification     |

| 0 | 1 | 1 | 1 | -6.5 dB amplification     |

| 1 | 0 | 0 | 0 | -9.5 dB amplification     |

| 1 | 0 | 0 | 1 | -12.5 dB amplification    |

| 1 | 0 | 1 | 0 | -15.5 dB amplification    |

| 1 | 0 | 1 | 1 | -18.5 dB amplification    |

| 1 | 1 | 0 | 0 | -21.5 dB amplification    |

| 1 | 1 | 1 | 1 | reserved                  |

## **HOC** Handset Amplifier Control

| 7 | 6 | 5 | 4 | Description               |

|---|---|---|---|---------------------------|

| 0 | 0 | 0 | 0 | AHS is in power-down mode |

| 0 | 0 | 0 | 1 | 2.5 dB amplification      |

| 0 | 0 | 1 | 0 | -0.5 dB amplification     |

| 0 | 0 | 1 | 1 | -3.5 dB amplification     |

| 0 | 1 | 0 | 0 | -6.5 dB amplification     |

| 0 | 1 | 0 | 1 | -9.5 dB amplification     |

| 0 | 1 | 1 | 0 | -12.5 dB amplification    |

| 0 | 1 | 1 | 1 | -15.5 dB amplification    |

| 7 | 6 | 5 | 4 | Description            |

|---|---|---|---|------------------------|

| 1 | 0 | 0 | 0 | -18.5 dB amplification |

| 1 | 0 | 0 | 1 | -21.5 dB amplification |

| 1 | 1 | 1 | 1 | reserved               |

#### **REG 4: AOCR - AFE Output Configuration Register**

| 7   |     |      |      |      | 0    |

|-----|-----|------|------|------|------|

| SEM | AXC | DHOP | DHON | DLSP | DLSN |

### **DLSN** Disable Loudspeaker Amplifier Output N

0: LSN output of ALS amplifier controlled by LSC setting

1: LSN controlled by SEM setting

#### **DLSP** Disable Loudspeaker Amplifier Output P

0: LSP output of ALS amplifier controlled by LSC setting

1: LSP controlled by SEM setting

## **DHON** Disable Handset Amplifier Output N

0: HON output of AHS amplifier controlled by HOC setting

1: HON output of AHS amplifier disabled (power down)

## **DHOP** Disable Handset Amplifier Output P

0: HOP output of AHS amplifier controlled by HOC setting

1: HOP output of AHS amplifier disabled (power down)

### **AXC** Auxiliary Output Control

| 6 | 5 | 4 | Description               |

|---|---|---|---------------------------|

| 0 | 0 | 0 | AXO is in power-down mode |

| 0 | 0 | 1 | -6 dB amplification       |

| 0 | 1 | 0 | -9 dB amplification       |

| 0 | 1 | 1 | -12 dB amplification      |

| 1 | 0 | 0 | -15 dB amplification      |

| 1 | 0 | 1 | -18 dB amplification      |

| 1 | 1 | 0 | -21 dB amplification      |

| 1 | 1 | 1 | -24 dB amplification      |

#### **SEM** Single Ended Mode

0: LSN (LSP) fixed to GND

1: LSN (LSP) tristated

### **REG 5: AOPR - AFE Output Path Register**

| 7   |      |      |     |   | 0    |

|-----|------|------|-----|---|------|

| OSS | DAC2 | DAC1 | PSS | 0 | OVRE |

#### **OVRE Override Enable**

0: Gain for ALS is always defined by LSC

1: Gain for ALS can be overridden by interchip communication

#### DAC1 D/A Control 1

0: POFI<sub>1</sub> and D/A<sub>1</sub> are in power down mode

1: POFI<sub>1</sub> and D/A<sub>1</sub> are active

## **PSS** Power Supply Selection

0: 3.3V power supply

1: 5V power supply

#### DAC2 D/A Control 2

0: POFI<sub>2</sub> and D/A<sub>2</sub> are in power down mode

1: POFI<sub>2</sub> and D/A<sub>2</sub> are active

## **OSS** Output Source Selection

| 7 | 6 | 5 | Description                                                                                                                                                  |

|---|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 0 | ALS and AHS are connected to PREFI <sub>1</sub> , AXC is connected to PREFI <sub>2</sub> , POFI <sub>1</sub> and POFI <sub>2</sub> must be set to power down |

| 0 | 0 | 1 | ALS is connected to PREFI <sub>1</sub> , AHS and AXC are connected to PREFI <sub>2</sub> , POFI <sub>1</sub> and POFI <sub>2</sub> must be set to power down |

| 0 | 1 | - | reserved                                                                                                                                                     |

| 1 | 0 | - | reserved                                                                                                                                                     |

| 1 | 1 | 0 | ALS and AHS are connected to POFI <sub>2</sub> , AXC is connected to POFI <sub>1</sub>                                                                       |

| 1 | 1 | 1 | ALS is connected to POFI <sub>2</sub> , AHS and AXC are connected to POFI <sub>1</sub>                                                                       |

## **REG 6: TFCR - Test Function Configuration Register**

| 7    |      |      |      | 0 |

|------|------|------|------|---|

| DHPR | DHPX | ALTF | DLTF | 0 |

## **DHPR** Disable High-Pass (Receive Direction)

0: High Pass activated (Receive)

1: High Pass disabled (Receive)

## **DHPX** Disable High-Pass (Transmit Direction)

0: High Pass activated (Transmit)

1: High Pass disabled (Transmit)

## **ALTF** Analog Loop Test Function

| 5 | 4 | 3 | Description               |

|---|---|---|---------------------------|

| 0 | 0 | 0 | Normal Mode               |

| 0 | 0 | 1 | Analog Loop via Front End |

| 0 | 1 | 0 | Analog Loop via Converter |

| 0 | 1 | 1 | Analog Loop via 64kHz     |

| 1 | 0 | 0 | Analog Loop via Interface |

## **DLTF** Digital Loop Test Function

| 2 | 1 | Description                   |

|---|---|-------------------------------|

| 0 | 0 | Normal Mode                   |

| 0 | 1 | Digital Loop via PCM register |

| 1 | 0 | Digital Loop via 64kHz        |

| 1 | 1 | reserved                      |

# **REG 7: TMR - Test Mode Register**

| 7   |   |   |   |   |   |   | 0 |

|-----|---|---|---|---|---|---|---|

| _1) | - | 0 | 0 | 0 | 0 | 0 | 0 |

<sup>1)</sup> undefined

This register is reserved for factory tests. Do not write this register.

## 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

| Parameter                                 | Symbol        | Limit Values                 | Unit |

|-------------------------------------------|---------------|------------------------------|------|

| Ambient temperature under bias            | $T_{A}^{1)}$  | - 40 to 85                   | °C   |

| Storage temperature                       | $T_{STG}$     | - 65 to125                   | °C   |

| Voltage on any pin with respect to ground | $V_{S}$       | $-0.3$ to $V_{\rm DD}$ + 0.3 | V    |

| Maximum voltage on any pin                | $V_{\sf max}$ | 7                            | V    |

<sup>1)</sup> Reduced performance e.g. noise and gain tracking

ESD-integrity (according MIL-Std 883D, method 3015.7): 1000 V exception: The pins #16, #18, #19 and #20 are not protected against voltage stress > 630 V

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

### 4.2 DC Characteristics

The performance is guaranteed for 3.0V-3.6V or 4.75V-5.25V only. In emergency mode the supply voltage range is 3.0V-5.25V for  $V_{DDD}/V_{DDA}/V_{DDP}$ .

$V_{\rm DDD}/V_{\rm DDA}/V_{\rm DDP}$  = 3.0V-3.6V or 4.75V-5.25V;  $V_{\rm SSD}/V_{\rm SSA}/V_{\rm SSP}$  = 0 V;  $T_{\rm A}$  = 0 to 70 °C

| Parameter                                     | Symbol                              | Lim                    | it Valı | ues                                          | Unit           | Test Condition                                                                                                                            |  |

|-----------------------------------------------|-------------------------------------|------------------------|---------|----------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                               |                                     | min.                   | typ.    | max.                                         |                |                                                                                                                                           |  |

| Input leakage current                         | $I_{IL}$                            | - 1.0                  |         | 1.0                                          | μΑ             | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DD}}$                                                                                       |  |

| H-input level                                 | $V_{IH}$                            | 2.0                    |         | V <sub>DD</sub> + 0.3                        | V              |                                                                                                                                           |  |

| L-input level                                 | $V_{IL}$                            | - 0.3                  |         | 0.8                                          | V              |                                                                                                                                           |  |

| H-output level                                | $V_{OH}$                            | V <sub>DD</sub> – 0.45 |         |                                              | V              | $I_{\rm O}$ = 2 mA                                                                                                                        |  |

| L-output level                                | $V_{OL}$                            |                        |         | 0.45                                         | V              | $I_{\rm O} = -2 \mathrm{mA}$                                                                                                              |  |

| Input capacitance                             | $C_1$                               |                        |         | 10                                           | pF             |                                                                                                                                           |  |

| Output capacitance                            | $C_{O}$                             |                        |         | 15                                           | pF             |                                                                                                                                           |  |

| $V_{\mathrm{DD}}$ standby supply current      | I <sub>DDS1</sub>                   |                        |         | <ul><li>200</li><li>50</li><li>1.8</li></ul> | μA<br>μA<br>mA | V <sub>dd</sub> =5 V, power down (after reset), no clock on AFECLK, V <sub>dd</sub> =3.3 V, power down (after reset), no clock on AFECLK, |  |

|                                               | $I_{DDS2}$                          |                        |         | -                                            |                | $V_{VREF} = ON$                                                                                                                           |  |

| $V_{\rm DD}$ supply current operating $^{1)}$ | $I_{\text{DDO1}}$ $I_{\text{DDO2}}$ |                        |         | 5.1                                          | mA<br>mA       | emergency ringing via ALS (single ended mode) emergency speech mode (AHS in differential mode)                                            |  |

|                                               | $I_{DDO3}$                          |                        |         | 20.0                                         | mA             | full operation (loudhearing)                                                                                                              |  |

$<sup>\</sup>overline{\ ^{1)}}$  Operating power dissipation is measured with all analog outputs open. All analog inputs are set to  $V_{\rm REF}.$

Data Sheet 35 09.99

#### 4.3 AC Characteristics

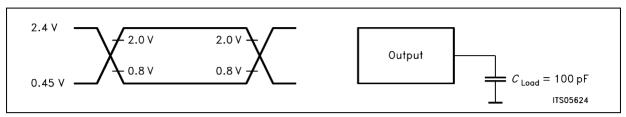

Digital inputs are driven to 2.4 V for a logical "1" and to 0.45 V for a logical "0". Timing reference points are 2V and 0.8 V. The AC-testing waveforms are shown below.

Figure 38 Input/Output Waveforms for AC-Tests

The performance is guaranteed for 3.0V-3.6V aor 4.75V-5.25V only. In emergency mode the supply voltage range is 3.0V-5.25V for  $V_{DDD}/V_{DDA}/V_{DDP}$ .

## Analog Front End Input Characteristics 1)

| Parameter                          | Symbol               | Limit Values |      |      | Unit | <b>Test Condition</b>         |  |

|------------------------------------|----------------------|--------------|------|------|------|-------------------------------|--|

|                                    |                      | min.         | typ. | max. | =    |                               |  |

| AXI-input impedance                | $Z_{AXI}$            | 12.5         | 20.5 |      | kΩ   | 300 – 3400 Hz                 |  |

| AXI-input voltage swing            | $V_{AXI}$            |              |      | 19   | mVpk | 42 dB, V <sub>dd</sub> =5 V   |  |

| AXI-input voltage swing            | $V_{AXI}$            |              |      | 1.67 | Vpk  | 0 dB, V <sub>dd</sub> =5 V    |  |

| AXI-input voltage swing            | $V_{AXI}$            |              |      | 9.53 | mVpk | 42 dB, V <sub>dd</sub> =3.3 V |  |

| AXI-input voltage swing            | $V_{AXI}$            |              |      | 0.75 | Vpk  | 0 dB, V <sub>dd</sub> =3.3 V  |  |

| AXI-gain                           | $G_{AXI}$            |              |      | 42   | dB   | 9.55 mV @ 1 kHz               |  |

| AXI-input impedance in bypass-mode | $Z_{AXI}$            | 160          | 270  |      | kΩ   | 300 – 3400 Hz                 |  |

| AXI-gain in bypass-mode            | $G_{AXI}$            |              |      | 0    | dB   | 1V @ 1 kHz                    |  |

|                                    |                      | •            | •    | •    | •    |                               |  |

| MIP/MIN1,2-input voltage swing     | V <sub>MIP/MIN</sub> |              |      | 19   | mVpk | 42 dB, V <sub>dd</sub> =5 V   |  |

| MIP/MIN1,2-input voltage swing     | V <sub>MIP/MIN</sub> |              |      | 9.53 | mVpk | 42 dB, V <sub>dd</sub> =3.3 V |  |

| MIP/MIN1,2-gain                    | $G_{MIP/MIN}$        |              |      | 42   | dB   | 9.55 mV @ 1 kHz               |  |

Data Sheet 36 09.99

The maximum voltage swing at the internal paths corresponds to the maximum PCM-code ( $\pm$  127).

| Parameter | Symbol     | Lin  | nit Values |      | Unit | Test Condition |

|-----------|------------|------|------------|------|------|----------------|

|           |            | min. | typ.       | max. |      |                |

| RST input | $t_{RSTI}$ | 1    |            |      | μs   |                |

## **Analog Front End Output Characteristics**

| AHO-output impedance        | $Z_{AHO}$         |    | 2   | Ω   | 300 – 3400 Hz                                                   |

|-----------------------------|-------------------|----|-----|-----|-----------------------------------------------------------------|

| AHO-output voltage swing    | V <sub>AHO</sub>  |    | 3.2 | Vpk | V <sub>dd</sub> = 5V, load<br>measured from<br>HOP to HON       |

| AHO-output voltage swing    | V <sub>AHO</sub>  |    | 1.6 | Vpk | V <sub>dd</sub> = 3.3V, load<br>measured from<br>HOP to HON     |

|                             |                   |    |     |     |                                                                 |

| ALS-output impedance        | $Z_{ALS}$         |    | 2   | Ω   | 300 – 3400 Hz                                                   |

| ALS-output voltage swing    | V <sub>ALS</sub>  |    | 3.2 | Vpk | V <sub>dd</sub> = 5V, load<br>measured from<br>LSP to LSN       |

| ALS-output voltage swing    | V <sub>ALS</sub>  |    | 1.6 | Vpk | V <sub>dd</sub> = 3.3V, load<br>measured from<br>LSP to LSN     |

|                             |                   |    |     |     |                                                                 |

| AXO-output impedance        | $Z_{AXO}$         | 15 | 21  | Ω   | 300 – 3400 Hz                                                   |

| AXO-output voltage swing 1) | V <sub>AXO</sub>  |    | 1.2 | Vpk | V <sub>dd</sub> = 5V, load<br>measured from<br>AXO to GND       |

| AXO-output high voltage 1)  | V <sub>AXOH</sub> |    | 3.6 | Vpk | V <sub>dd</sub> = 5V, input load<br>- 0.12 mA<br>reference: GND |

| AXO-output low voltage 1)   | $V_{AXOL}$        |    | 1.2 | Vpk | V <sub>dd</sub> = 5V, input load<br>+ 0.12 mA<br>reference: GND |

| AXO-output voltage swing    | V <sub>AXO</sub>  |    | 0.7 | Vpk | V <sub>dd</sub> = 3.3V, load<br>measured from<br>AXO to GND     |

| Parameter                                      | Symbol       | Limit Values |      |      | Unit | Test Condition                                    |  |

|------------------------------------------------|--------------|--------------|------|------|------|---------------------------------------------------|--|

|                                                |              | min.         | typ. | max. |      |                                                   |  |

| $\overline{V_{\mathrm{REF}}}$ output impedance | $Z_{VREF}$   |              | 3    | 5    | Ω    | Load measured from $V_{\rm REF}$ to $V_{\rm SSA}$ |  |

| $V_{REF}$ output voltage                       | $V_{VREF}$   | 2.3          | 2.4  | 2.5  | V    | input load – 2 mA                                 |  |

| $\overline{V_{REFBG}}$ output voltage          | $V_{VREFBG}$ |              | 1.2  |      | V    | with ext. capacitor                               |  |

### **Transmission Characteristics**

$V_{\rm DDD}/V_{\rm DDA}/V_{\rm DDP}$  = 3.0V-3.6V or 4.75V-5.25V;  $V_{\rm SSD}/V_{\rm SSA}/V_{\rm SSP}$  = 0 V;  $T_{\rm A}$  = 0 to 70 °C

| Parameter                  | Limit ' | Values      | Unit | Test Condition              |  |  |

|----------------------------|---------|-------------|------|-----------------------------|--|--|

|                            | min.    | max.        |      |                             |  |  |

| Attenuation Distortion     | 0       |             | dB   | < 200 Hz                    |  |  |

| @ 0 dBmO                   | - 0.25  |             | dB   | 200 – 300 Hz                |  |  |

|                            | - 0.25  | 0.25        | dB   | 300 – 2400 Hz               |  |  |

|                            | - 0.25  | 0.45        | dB   | 2400 – 3000 Hz              |  |  |

|                            | - 0.25  | 0.9         | dB   | 3000 – 3400 Hz              |  |  |

|                            | 0       |             | dB   | > 3400 Hz                   |  |  |

| Out-of-band signals        |         |             |      | receive signal filtering:   |  |  |

|                            |         | <b>–</b> 35 | dB   | 4.6 kHz                     |  |  |

|                            |         | <b>- 45</b> | dB   | >8.0 kHz                    |  |  |

|                            |         |             |      | transmit:                   |  |  |

|                            |         | - 35        | dB   | 4.6 kHz                     |  |  |

|                            |         | - 40        | dB   | >8.0 kHz                    |  |  |

| Group delay distortion     |         | 750         | μs   | 500 – 600 Hz                |  |  |

| @ 0 dBmO                   |         | 380         | μs   | 600 – 1000 Hz               |  |  |

|                            |         | 130         | μs   | 1000 – 2600 Hz              |  |  |

|                            |         | 750         | μs   | 2600 – 2800 Hz              |  |  |

| Signal-to-total distortion | 50      |             | dB   | 0 to - 20dBm0 <sup>1)</sup> |  |  |

| (sine signal)              | 39      |             | dB   | - 30 dBm0                   |  |  |

|                            | 29      |             | dB   | - 40 dBm0                   |  |  |

|                            | 24      |             |      | - 45 dBm0                   |  |  |

| Gain tracking              | - 0.3   | 0.3         | dB   | 3 to - 40 dB                |  |  |

| (sine signal)              | - 0.6   | 0.6         | dB   | - 40 to - 50 dB             |  |  |

| @ - 10 dBmO                | - 1.6   | 1.6         | dB   | - 50 to - 55 dB             |  |  |

| Idle-channel noise         |         | <b>- 75</b> | dBmO | receive                     |  |  |

| (Psophometric)             |         | - 66        | dBmO | transmit                    |  |  |

| Channel crosstalk          |         | <b>- 75</b> | dB   | Reference: 0 dBmO           |  |  |

| Programmable gain          | - 0.5   | 0.5         | dB   | step accuracy               |  |  |

|                            | - 1.0   | 1.0         | dB   | overall accuracy            |  |  |

For single ended inputs only within gain settings 0 dB to 24 db at  $V_{dd}$  = 5V and within gain settings 0 dB to 18 db at  $V_{dd}$  = 3.3V. For differential inputs 0 dB to 36 dB.

Data Sheet 39 09.99

Figure 4-1 SCI Interface

| Parameter               | Symbol                | Limit v | Unit |    |

|-------------------------|-----------------------|---------|------|----|

| SCI Interface           |                       | Min     | Max  |    |

| SCLK cycle time         | $t_1$                 | 500     |      | ns |

| SCLK high time          | $t_2$                 | 100     |      | ns |

| SCLK low time           | $t_3$                 | 100     |      | ns |

| CS setup time           | $t_4$                 | 0       |      | ns |

| CS hold time            | <i>t</i> <sub>5</sub> | 10      |      | ns |

| SDR setup time          | <i>t</i> <sub>6</sub> | 40      |      | ns |

| SDR hold time           | <i>t</i> <sub>7</sub> | 40      |      | ns |

| SDX data out delay      | <i>t</i> <sub>8</sub> |         | 80   | ns |

| CS high to SDX tristate | $t_9$                 |         | 40   | ns |

| SCLK to SDX active      | t <sub>10</sub>       |         | 80   | ns |

Figure 4-2 AFE Interface - Bit Synchronization Timing

Figure 4-3 AFE Interface - Frame Synchronization Timing

| Parameter                           | Symbol                | Limit v | Unit |                       |

|-------------------------------------|-----------------------|---------|------|-----------------------|

| AFE Interface                       |                       | Min     | Max  |                       |

| AFECLK period                       | <i>t</i> <sub>1</sub> | 125     | 165  | ns                    |

| AFECLK high                         | $t_2$                 | 50      |      | ns                    |

| AFECLK low                          | $t_3$                 | 50      |      | ns                    |

| AFEDD setup                         | $t_4$                 | 20      |      | ns                    |

| AFEDD hold                          | <i>t</i> <sub>5</sub> | 20      |      | ns                    |

| AFEDU high impedance to active      | <i>t</i> <sub>6</sub> |         | 20   | ns                    |

| AFEDU from active to high impedance | <i>t</i> <sub>7</sub> |         | 20   | ns                    |

| AFEDU output delay                  | <i>t</i> <sub>8</sub> |         | 20   | ns                    |

| AFEFS setup                         | t <sub>9</sub>        | 20      |      | ns                    |

| AFEFS hold                          | t <sub>10</sub>       | 20      |      | ns                    |

| AFEFS high                          | t <sub>11</sub>       | 1       |      | <i>t</i> <sub>1</sub> |

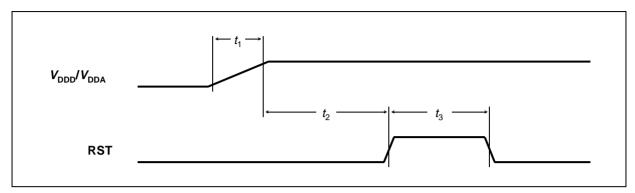

Figure 4-4 Power and Reset Timing

| Parameter Power and Reset Timing           | Symbol                | Limit values |     | Unit |

|--------------------------------------------|-----------------------|--------------|-----|------|

|                                            |                       | Min          | Max |      |

| $V_{\rm DDD}/V_{\rm DDA}$ rise time 5%-95% | <i>t</i> <sub>1</sub> |              | 20  | ms   |

| Supply voltages stable to RST high         | $t_2$                 |              | 100 | ns   |

| RST high                                   | <i>t</i> <sub>3</sub> | 100          |     | ns   |

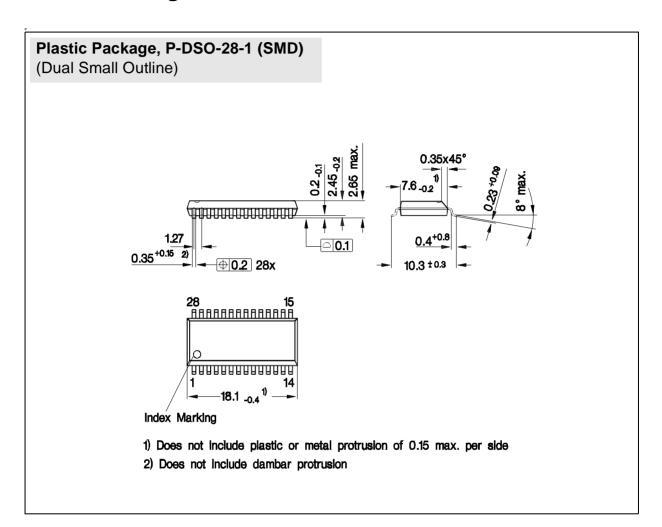

# 5 Package Outlines

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our