# **ADVANCED**

December 1995

**DP8459 All-Code Data Synchronizer**

# **DP8459 All-Code Data Synchronizer**

# **General Description**

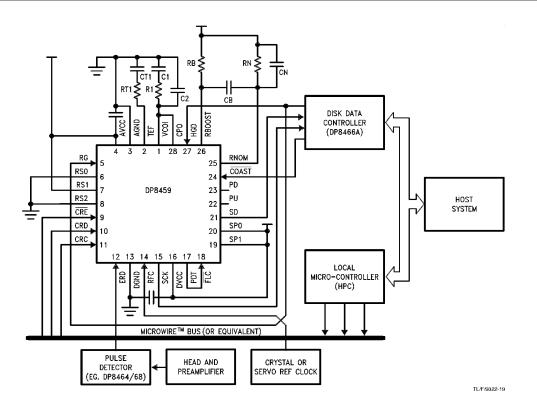

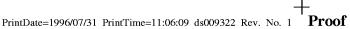

The DP8459 Data Synchronizer is an integrated phase locked loop circuit which has been designed for application in magnetic hard disk, flexible (floppy) disk, optical disk, and tape drive memory systems for data re-synchronization and clock recovery with any standard recording code, operating to 25 Mb/s. The DP8459 is provided in a 28-pin PCC package. Zero phase start is employed during both data and reference clock lock sequences for rapid acquisition. An (Customer-controlled) synchronization frequency-acquisition feature guarantees lock, accommodating the preamble types used with GCR (Group Code Recording), MFM (Modified Frequency Modulation), the [1,N] run length limited (RLL) codes, and either of the standard 2,7 RLL codes. Precise synchronization window generation is achieved via an internal, self-aligning delay line which remains accurate independent of temperature, power supply, external component and IC process variations. The DP8459 also incorporates a digitally controlled (MICROW-IRE™ bus compatible) strobe function with 5-bit resolution which allows for margin testing, error recovery routines, and precise window calibration. The PLL filter resides external to the chip, with two ports provided to allow significant design flexibility. Synchronization pattern detection circuitry issues a

PREAMBLE DETECTED signal when a pre-determined length of the user-selected pattern is encountered. All digital input and output signals are TTL compatible and a single, +5V power supply is required. The DP8459V is offered as a DP8459V-10 (250 Kbit/sec thru 10 Mbits/sec) or DP8459V-25 (250 Kbits/sec thru 25 Mbit/sec), see AC Electrical Characteristics.

### **Features**

- Fully integrated dual-gain PLL

- Zero phase start lock sequence

- 250 Kbit/sec-25 Mbit/sec data rate range

- Frequency lock capability (optional) for all standard recording codes

- Digital window strobe control, 5-bit resolution

- Two-port PLL filter network

- PLL free-run (Coast) control for optical disk defects

- Synchronization pattern (preamble lock) detection

- Non-glitching multiplexed read/write clock output

- +5V supply

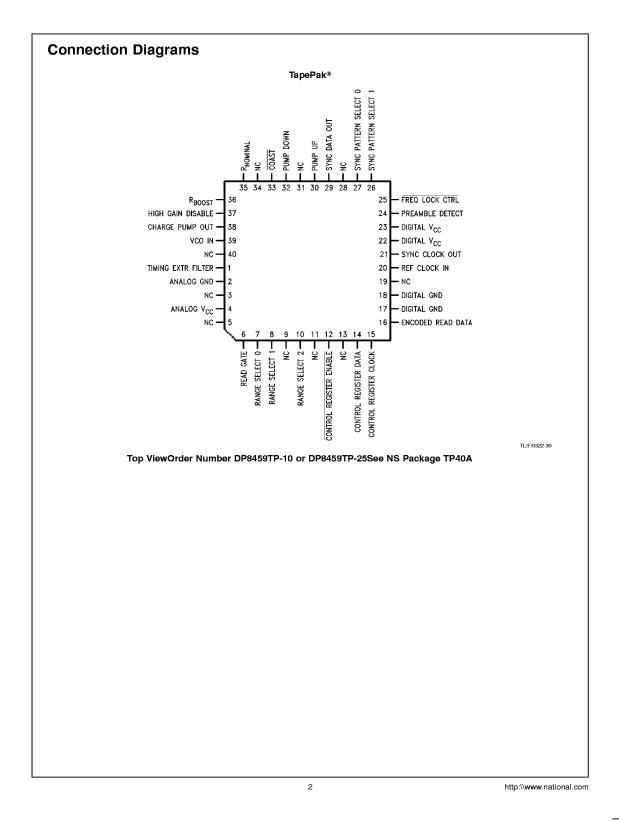

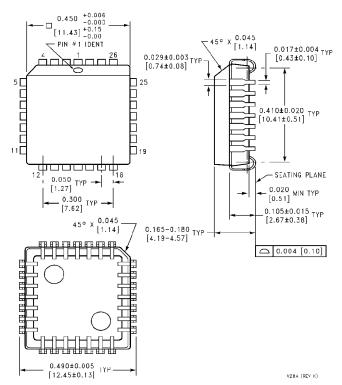

- DP8459 supplied in 28-pin plastic chip carrier (PCC) and 40-pin TapePak packages

# **Connection Diagrams**

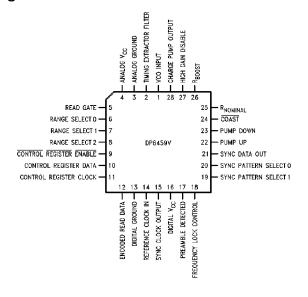

FIGURE 1. DP8459 in 28-Pin Plastic Chip Carrier (PCC) V-Type Package Order Number DP8459V-10 or DP8459V-25

$\label{eq:tageneral} \mbox{TapePak$^0$ is a registered trademark of National Semiconductor Corporation} \\ \mbox{MICROWIRE}^{\mbox{\tiny MIC}} \mbox{ is a trademark of National Semiconductor Corporation}.$

© 1996 National Semiconductor Corporation TL/F/932

http://www.national.com

TL/F/9322-6

PrintDate=1996/07/31 PrintTime=11:05:38 ds009322 Rev. No. 1 **Proo**

PrintDate=1996/07/31 PrintTime=11:05:39 ds009322 Rev. No. 1 **Proo**

+

http://www.national.com

+

PrintDate=1996/07/31 PrintTime=11:05:39 ds009322 Rev. No. 1 **Proo**

# 1.0 Pin Descriptions

DP8459 28-pin PCC package

|             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| POWER SUP   | PLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16          | <b>DIGITAL V<sub>cc</sub>:</b> 5.0V ±5%. (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4           | <b>ANALOG V<sub>CC</sub>:</b> 5.0V ±5%. (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13          | DIGITAL GROUND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3           | ANALOG GROUND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TTL LEVEL L | OGIC INPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5           | READ GATE (RG): Read mode control input, active high (logical-one). Assertion causes the PLL to lock to the ENCODED READ DATA, employing a zero phase start routine. Deassertion causes the PLL to lock the REFERENCE CLOCK input, also employing a zero phase start routine. READ GATE timing is allowed to be fully asynchronous.                                                                                                                                                                                                                                                                                                                                                                                         |

| 6, 7, 8     | RANGE SELECT 0, 1, 2 (RS0, RS1, RS2): Control the operating frequency range of the VCO. A 2:1 continuously variable sub-range is available within each of 6 allowed selections, enabling the VCO to operate at any frequency within a 96:1 range from 500 kHz to 50 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9           | CONTROL REGISTER ENABLE (CRE): A logical Low level allows the CONTROL REGISTER CLOCK to clock data into the Control Register via the CONTROL REGISTER DATA input; a logical HIGH level latches the register data and issues the information to the appropriate circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10          | CONTROL REGISTER DATA (CRD): Control Register data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11          | CONTROL REGISTER CLOCK (CRC): Negative edge triggered Control Register clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12          | ENCODED READ DATA (ERD): Incoming TTL-level data derived from the storage media; issued from a pulse detector circuit. Each positive edge represents a single recorded code bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14          | REFERENCE CLOCK (RFC): A reference frequency input required for DP8459 operation. The RFC frequency must be accurate and highly stable (crystal or servo derived) and equivalent to the 2F frequency for the MFM or [2,7] codes (i.e., equal to, but not derived from the VCO frequency).                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18          | FREQUENCY LOCK CONTROL (FLC): Selects or de-selects the frequency lock function during a READ operation. Has no effect with READ GATE deasserted; frequency lock is automatically employed for the full duration of time READ GATE is deasserted regardless of the level of the FLC input. With READ GATE high and FLC low (logical-zero) the PLL is forced to lock to the pattern frequency selected via the SYNC PATTERN SELECT inputs. When high (logical-one) frequency lock action is terminated and the PLL employs a pulse gate to accommodate random disk data patterns. FLC may be tied to PREAMBLE DETECTED output pin for self-regulated frequency lock control. FLC timing is allowed to be fully asynchronous. |

| 20, 19      | SYNC PATTERN SELECT 0, 1 (SP0, SP1): Control inputs for selection of the preamble type being employed. These inputs determine the pattern to which the PLL will frequency-lock during preamble acquisition (if frequency lock is employed) and for which the PREAMBLE DETECTED circuitry searches.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24          | COAST (CST): Control for Coast function. The Coast function may be activated when READ GATE is either high or low. When the COAST input is low (logical-zero), the phase comparator is disabled and held in a cleared state, allowing the VCO to coast regardless of ENCODED READ DATA input activity (READ GATE high) or REFERENCE CLOCK input activity (READ GATE low). No other circuit functions are disturbed. When high (logical-one), the phase comparator operates normally.                                                                                                                                                                                                                                        |

| 27          | HIGH-GAIN DISABLE (HGD): Charge Pump gain switch control. When low (logical-zero), the charge pump input current is the combined value of the currents at both R <sub>BOOST</sub> and R <sub>NOMINAL</sub> pins. When high (logical-one), charge pump input current is taken from the R <sub>NOMINAL</sub> pin only. HGD may be tied either to READ GATE or PREAMBLE DETECTED for self-regulated gain control.                                                                                                                                                                                                                                                                                                              |

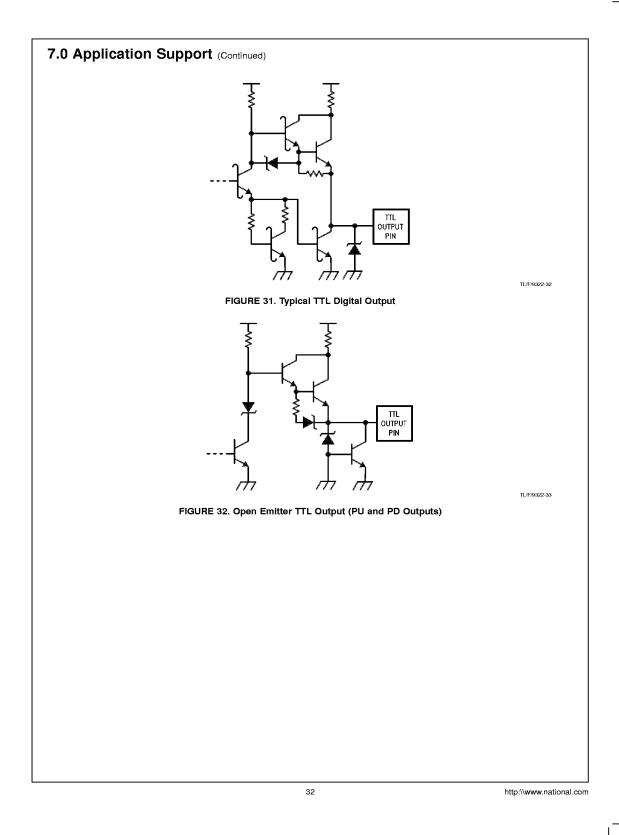

| TTL LEVEL L | OGIC OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15          | SYNCHRONIZED CLOCK (SCK): Issues the VCO signal following READ GATE assertion and completion of zero phase start sequence; issues REFERENCE CLOCK input signal when READ GATE is deasserted. Multiplexer switching is achieved without glitches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17          | PREAMBLE DETECTED (PDT): Issues a high level (logical-one) following assertion of READ GATE, completion of the zero phase start sequence, and the detection of approximately 32 sequential pulses of 1T, 2T or 3T period preamble, or 16 sequential pulses of 4T period preamble, depending on state of SYNC PATTERN SELECT inputs (T = VCO period). Following preamble detection, the output remains latched high until de-assertion of READ GATE. The PDT output will be at a logical zero state whenever READ GATE is inactive.                                                                                                                                                                                          |

http:\\www.national.com

PrintDate=1996/07/31 PrintTime=11:05:40 ds009322 Rev. No. 1 **Proof**

| 1.0 Pin I   | Descriptions (Continued)                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #       |                                                                                                                                                                                                                                                                                                                                                                                             |

| TTL LEVEL I | LOGIC OUTPUTS                                                                                                                                                                                                                                                                                                                                                                               |

| 21          | SYNCHRONIZED DATA (SD): A reconstructed replica of the ENCODED READ DATA signal, time-stabilized and synchronized to the SYNCHRONIZED CLOCK output.                                                                                                                                                                                                                                         |

| 22          | PUMP UP (PU): Active HIGH whenever the phase comparator issues a pump-up signal to the charge pump. The PU pin is an open-emitter output requiring an external passive pull down resistor whenever in active use. The output should be allowed to float when not needed.                                                                                                                    |

| 23          | <b>PUMP DOWN (PD):</b> Active HIGH whenever the phase comparator issues a pump-down signal to the charge pump. The PD pin is an open-emitter output requiring an external passive pull down resistor whenever in active use. The output should be allowed to float when not needed.                                                                                                         |

| ANALOG SIG  | GNAL PINS                                                                                                                                                                                                                                                                                                                                                                                   |

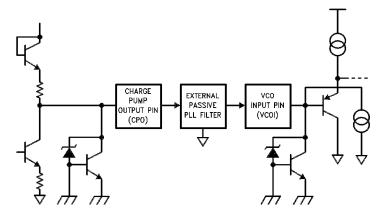

| 28          | CHARGE PUMP OUTPUT: The output of the high-speed, switching bi-directional current source circuitry of the charge pump. The external, passive PLL filter network is established between this pin, the VCO INPUT pin, and ground.                                                                                                                                                            |

| 1           | VCO INPUT: The high-impedance control voltage input to the voltage controlled oscillator (VCO). The external, passive PLL filter network is established between this pin, the CHARGE PUMP OUTPUT pin, and ground.                                                                                                                                                                           |

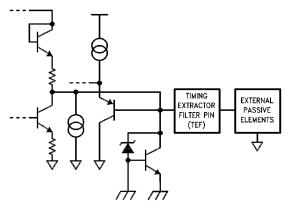

| 2           | TIMING EXTRACTOR FILTER: A pin for the connection of external, passive components employed to stabilize the delay line timing extraction circuitry. Delay accuracy is not a function of external component values or tolerances.                                                                                                                                                            |

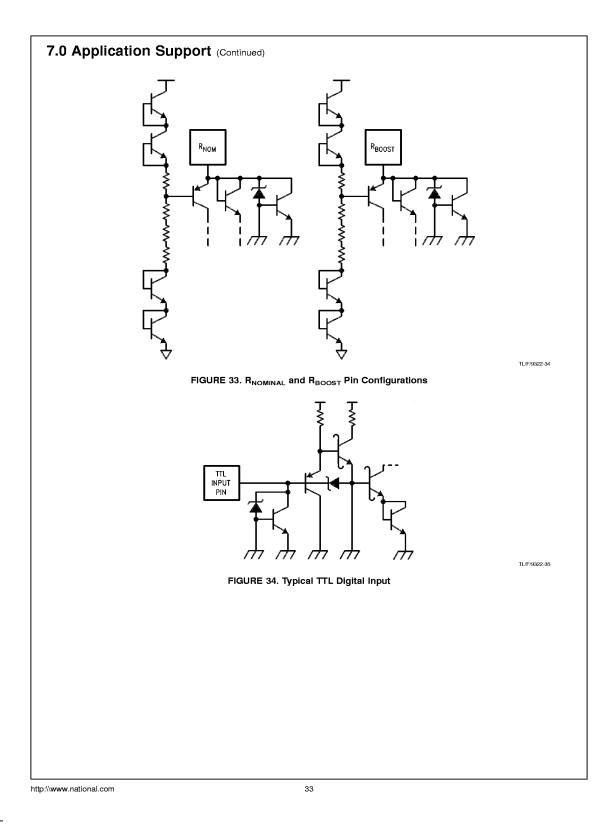

| 25          | R <sub>NOMINAL</sub> : A resistor is tied between this pin and V <sub>CC</sub> to set the charge pump <i>nominal</i> operating current. The current is internally multiplied by 2 for charge pump use.                                                                                                                                                                                      |

| 26          | R <sub>BOOST</sub> : A resistor is tied between this pin and V <sub>CC</sub> to set the charge pump <i>boost</i> (or adder) current. The R <sub>BOOST</sub> resistor is effectively paralleled with the R <sub>NOMINAL</sub> resistor when the HIGH GAIN DISABLE input is inactive (logical-zero); thus the sum of the resistor currents sets the total input current. The input current is |

Note 1: These pins should always be tied together; they are not intended to be used with separate power supplies.

multiplied by 2 within the charge pump circuitry

#### 2.0 Circuit Operation

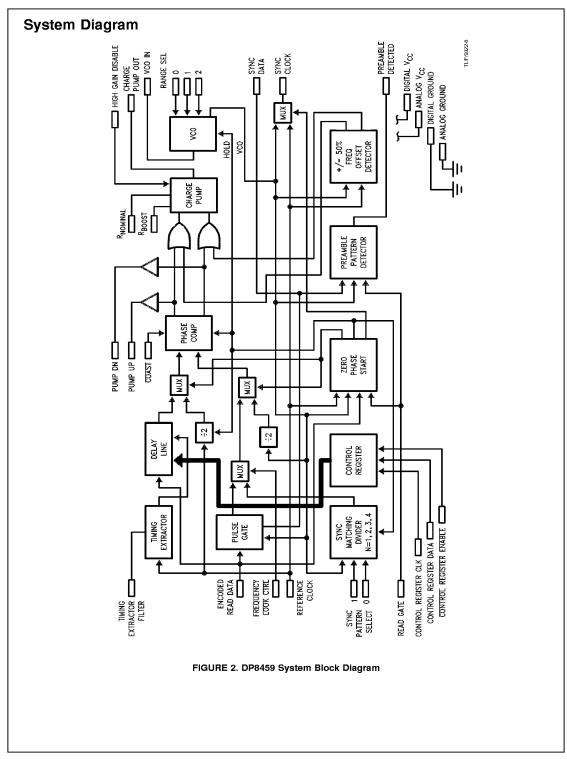

In the non-Read mode, the DP8459 PLL is locked to the REFERENCE CLOCK signal. This permits the VCO to remain at a frequency very close to the encoded data clock rate while the PLL is "idling" and thus will minimize the frequency step and associated lock time encountered at the initiation of lock to ENCODED READ DATA. Frequency acquisition is employed in the non-Read mode to ensure lock.

Note: The REFERENCE CLOCK signal is employed by circuitry which sets the time delay of the internal delay line. This requires the REFERENCE CLOCK signal to be present at all times at a stable and accurate frequency for proper DRASS operation.

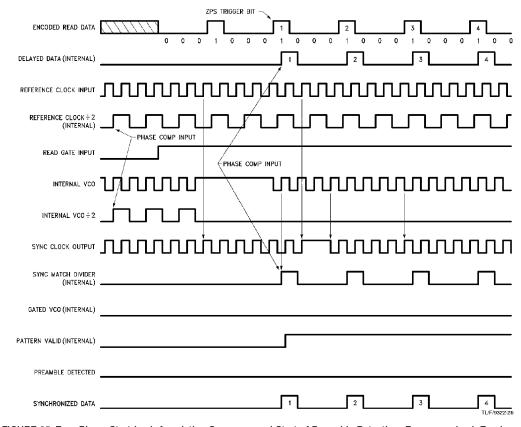

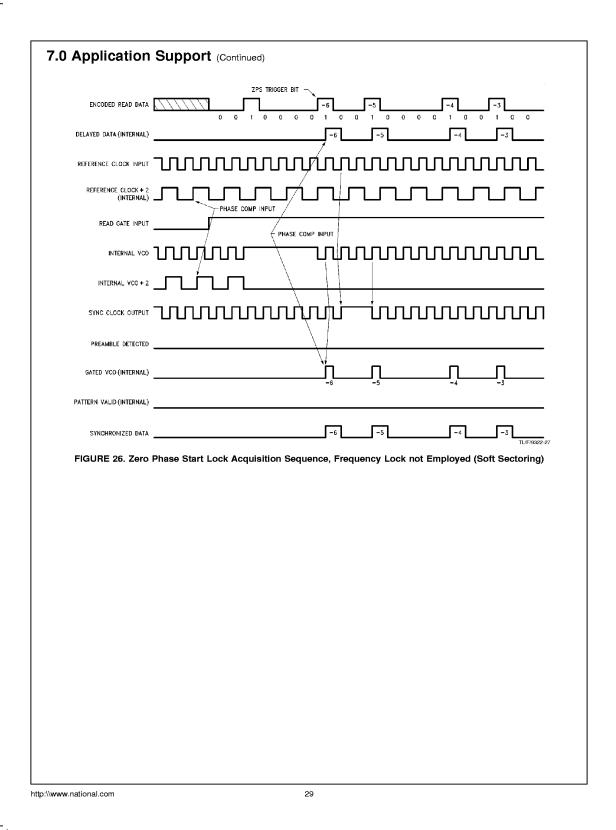

At the assertion of READ GATE, which is allowed to be done asynchronously (no timing requirements), and following the completion of two subsequent VCO cycles, the DP8459 VCO is stopped momentarily and restarted in accurate phase alignment with the second data bit which arrives following the VCO pause. This minimization of phase misalignment between the ENCODED READ DATA and the VCO (referred to as zero phase start, or ZPS) significantly reduces data lock acquisition time.

The DP8459 incorporates a preamble-specific frequency acquisition feature which may be employed at the user's option. The frequency acquisition feature is intended specifically for use within hard or pseudo-hard sectored systems where READ GATE is asserted only within a preamble. With the READ GATE active (logical-one) and the FREQUENCY LOCK CONTROL (FLC) input active (logical-zero), the DP8459 will be forced to lock to the exact preamble frequency selected at the SYNC PATTERN SELECT inputs. The frequency discriminating action of the PLL

provided in this mode produces a lock-in range equivalent to the available VCO operating range and thus eliminates the possibility of fractional-harmonic lock. Windowing (pulse gate action; see Pulse Gate, Section 2.1) is not employed in the frequency acquisition mode and thus quadrature lock is prevented (see National Semiconductor Application Note AN-414, APPS Mass Storage Handbook #1, 1986, for an explanation of typical false lock modes). The DP8459 will remain in the frequency acquisition mode until the  $\overline{\text{FLC}}$  input is deactivated (logical-one). In ordinary hard sectored or pseudo-hard sectored operation, the PREAMBLE DETECTED (PDT) output is tied to the FLC input for automatic switching from frequency acquisition to phase lock following internal detection of the selected preamble by the DP8459. The Customer may choose to intervene in this path and extend the frequency lock period. However, the DP8459 must be placed in the phase lock mode (FLC deactivated-logical-one) prior to encountering the end of the preamble, or loss of lock will result. Switching of the FLC input may be done asynchronously (no set-up or hold timing requirements).

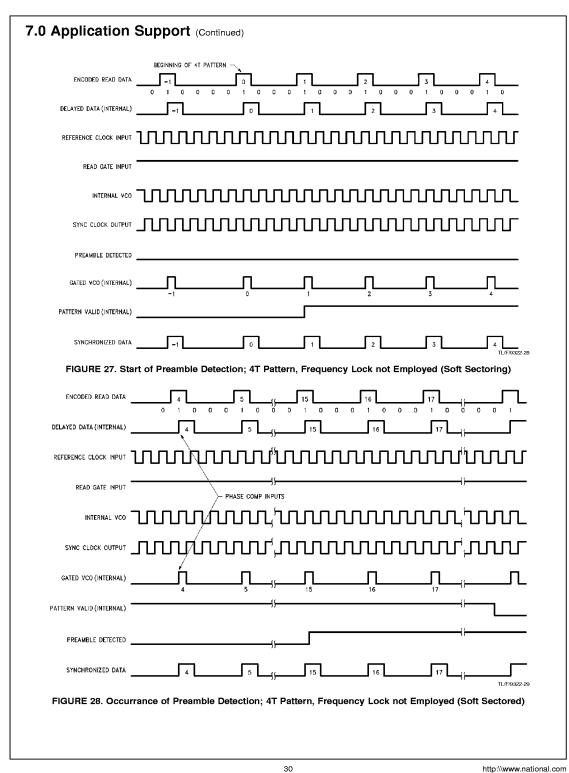

The PREAMBLE DETECTED (PDT) output will become active (logical-one) following READ GATE assertion, completion of the ZPS sequence and the subsequent detection of approximately 32 ENCODED READ DATA (ERD) pulses of the 1T, 2T or 3T preamble types, or 16 ENCODED READ DATA (ERD) pulses of the 4T preamble type (see specification tables), and will remain active (logical-one) until deassertion of READ GATE.

The Customer has the option of employing an elevated PLL bandwidth during preamble acquisition (or at any other time) for an extended capture range. An  $R_{BOOST}$  pin is provided to

http://www.national.com

5

+ Proof

PrintDate=1996/07/31 PrintTime=11:05:41 ds009322 Rev. No. 1

allow for an increase in charge pump gain above the level set by the  $R_{\mathsf{NOMINAL}}$  pin. When the HIGH GAIN DISABLE pin (HGD) is inactive (logical-zero), the  $R_{BOOST}$  resistor is electrically paralleled with the  $R_{NOMINAL}$  for an elevated charge pump gain. When HIGH GAIN DISABLE is active (logical-one), only the  $R_{\text{NOMINAL}}$  resistor is employed to set the pump current. The Charge Pump throughput gain is I<sub>CPO</sub> = 2 x  $I_{\rm Rp}$  where  $I_{\rm Rp}=0.25 V_{\rm CC}/R_{\rm p},~R_{\rm p}=R_{\rm NOM}$  with HGD high, and  $R_{\rm p}=R_{\rm NOM}||R_{\rm BOOST}|$  with HGD low. The Customer may choose to configure the system for high gain prior to DP8459 preamble detection by tying the HGD pin to the PDT output pin, or for high gain only during REFERENCE CLOCK lock by tying the HGD pin to the READ GATE pin. Other configurations may be employed, if desired.

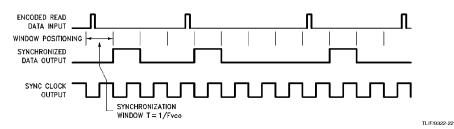

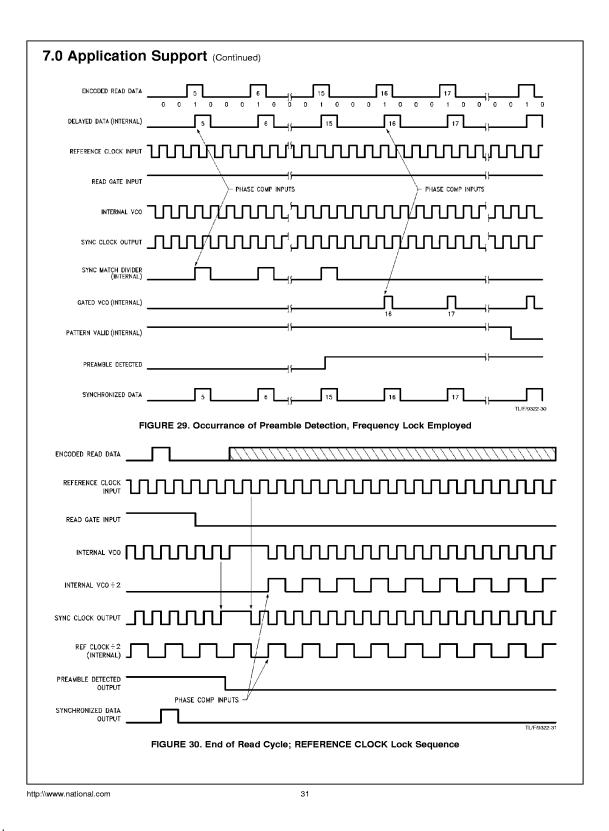

The DP8459 issues a clock waveform from the SYNCHRO-NIZED CLOCK output which is derived from the REFERENCE CLOCK input when the READ GATE is inactive (logical-zero), and from the VCO signal following READ GATE assertion (logical-one) and completion of the zero phase start sequence. The REFERENCE CLOCK signal is issued from the SYNCHRONIZED CLOCK output during non-Read activity and may be used as a write clock, if desired. Once data lock is achieved and the SYNCHRONIZED CLOCK output is issuing VCO, the SYNCHRONIZED DATA output and the SYNCHRO-NIZED CLOCK output are held in a fixed, specified timing relationship for use by decoding/deserializing circuitry. The SYNCHRONIZED CLOCK output multiplexer switching is achieved without glitches, i.e., no pulse is narrower than 50% of the VCO or REFERENCE CLOCK period.

The DP8459 provides a COAST control input which serves to clear the phase comparator and disable charge pump action whenever taken to an active, logical-zero level. This function is made available to allow the PLL to be set to free-run, undisturbed, while a detectable defect is being read from the media in a region where re-initiation of the lock procedure is impractical (e.g., data field). External data controller circuitry is responsible for the detection of the defect and issuance of the COAST command. The primary application of this feature is expected to be optical disk bright-spot avoidance, though it will lend itself to other applications as well.

As in the previous family of National Semiconductor data separators/synchronizers, the DP8459 provides phase comparator activity information to the Customer. The phase comparator's pump-up and pump-down outputs are brought out to separate pins, PUMP UP (PU) and PUMP DOWN (PD). The outputs are of the open-emitter type, requiring an external "pull-down" resistor when in active use. These outputs serve to indicate the relative displacement of the current data bit with respect to the internal VCO phase (window center). When in completely stabilized lock with no bit displacement, the output(s) will issue a pulse of a finite, minimum-valued width for each arriving data pulse. If any data pulse is displaced with respect to the VCO phase, the corresponding output pulse will widen by an amount equivalent to the bit displacement. These output signals may be integrated over time and employed to

determine the average magnitude of media bit shift. Additionally, the pulse widening/narrowing effect bit displacement has on the PU/PD outputs produces an amplitude modulation of the output's waveform. The waveform envelope, when observed with a relatively slow oscilloscope time base, can be employed for observation of PLL dynamics. This is particularly useful if intrusive probing of the PLL filter nodes is

It is strongly recommended that the PU/PD outputs be left "floating" (unconnected to any net or circuit element, including the output pull-down resistor) in any application where they are not specifically needed. This will serve to minimize unnecessary, spurious digital switching transients in the vicinity of the DP8459, and thus improve noise performance.

The DP8459 provides a wide operating data rate range to facilitate use within a broad base of applications, including multiple data rate systems or constant density recording (CDR). In order to achieve the specified 250 kbit /sec to 25 Mbit/sec span, the operation of the VCO has been divided into 6 contiguous frequency sub-ranges, with approximately a 2:1 ratio between adjacent range selections. Three inputs are provided for selecting of the sub-ranges, RANGE SELECT 0, 1 and 2. Some code type restrictions have been placed on the higher ranges of operating VCO frequency. See Figure 3 for the operating data rate truth table and allowed code type versus VCO range selection.

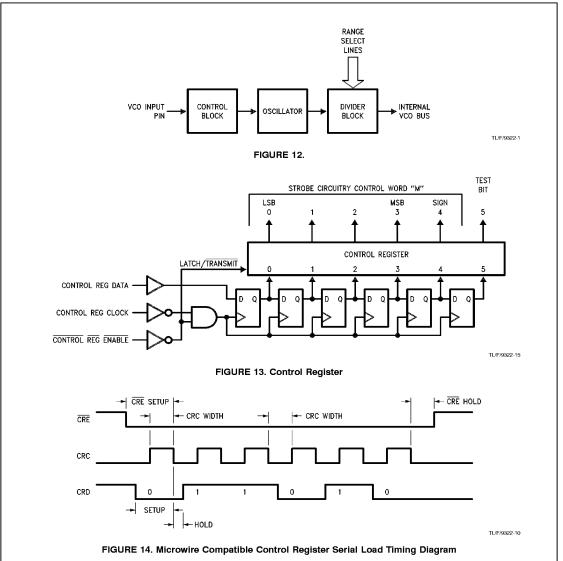

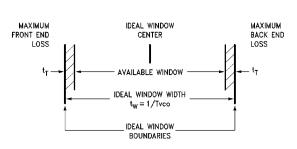

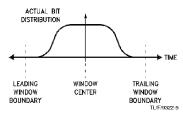

The DP8459 allows for flexible synchronization window strobe control. The inputs CONTROL REGISTER DATA (CRD), CONTROL REGISTER CLOCK (CRC), and CONTROL REGISTER ENABLE (CRE) are configured to permit interfacing of the DP8459 to the MICROWIRE™ (or equivalent) bus for entry of strobe information. Information is serially shifted into the  $\overline{\text{CON}}_{\overline{\text{TROL}}}$  REGISTER via the CRD and CRC pins whenever the CRE pin is active (logical-zero). When the CRE pin is inactive (logical-one), CRD and CRC are ignored. The strobe function allows the Customer to shift the synchronization window in 31 equal steps of magnitude t<sub>S</sub> = M x [1.8% x  $\tau_{VCO}$ ] from approximately 27% early to 27% late with respect to nominal window position. This function may be employed for margin testing (eg., approximately ±12%) or error recovery read re-try operations (eg., approximately ±2% to ±3%). Additionally, this feature allows the Customer to align the center of the synchronization window to within one half strobe step of ideal, regardless of the initial performance or specification of the DP8459. This window centering function may be performed completely within the drive system itself (auto-alignment) given the employment of an intelligent window alignment routine. Such a routine would be configured to determine the maximum error free early and late window positions via the strobe function, and then would fix the DP8459 window in the arithmetic mean position (Section 4.3.3). See Figure 4 for a window strobe truth table.

Note: In all DP8459 applications, provision must be made to load the appropriate information into the Control Register

http://www.national.com

| RANG | GE SELECT<br>( Note 1 ) |   | VCO Range                    | Equivalent<br>NRZ Data Rate | Minimum N (Allowed Code |                  | d Code T   | Гуре)      |

|------|-------------------------|---|------------------------------|-----------------------------|-------------------------|------------------|------------|------------|

| 2    | 1                       | 0 | MHz                          | MFM or 2,7<br>(Mbit/sec)    | 1<br>(GCR)              | 2<br>(MFM; 1, N) | 3<br>(2,7) | 4<br>(2,7) |

| 1    | 1                       | Х | 0.50 ≤ Fvco ≤ 1.25           | 0.250≤ Fnrz ≤ 0.625         | √                       | √                | √          | √          |

| 1    | 0                       | 1 | 1.25 < Fvco ≤ 2.5            | 0.625< Fnrz ≤ 1.25          | √                       | √                | √          | √          |

| 1    | 0                       | 0 | 2.5 < Fvco ≤ 5               | 1.25< Fnrz ≤ 2.5            | √                       | √                | √          | √          |

| 0    | 1                       | 1 | 5 < Fvco ≤ 10                | 2.5< Fnrz ≤ 5               | √                       | √                | √          | √          |

| 0    | 1                       | 0 | 10 < Fvco ≤ 20               | 5< Fnrz ≤ 10                | N/A                     | √                | √          | √          |

| 0    | 0                       | Х | 20 < Fvco ≤ 50<br>( Note 3 ) | 10< Fnrz ≤ 25               | N/A                     | 4                | 1          | √          |

Note 1: N/A-Not Allowed.

Note 2: Operation slightly beyond listed range boundaries may be acceptable in some applications. At or near range boundaries, range selection should be made to place the operating frequency near the UPPER boundary; e.g., use RS2 = 0, RS1 = 1, and RS0 = 0 for 10 Mb/s.

Note 3: 20 MHz < Fvco ≤ 38 MHz for 1, N codes.

FIGURE 3. Code Type Allowance Versus VCO Frequency Range

http://www.national.com

PrintDate=1996/07/31 PrintTime=11:05:45 ds009322 Rev. No. 1 **Proof**

|   | St | robe l | 3it |   | Strobe | Window Strobe             |

|---|----|--------|-----|---|--------|---------------------------|

| 4 | 3  | 2      | 1   | 0 | Word M | T <sub>s</sub> (Typical)  |

| 0 | 1  | 1      | 1   | 1 | -15    | –0.270 x τ <sub>VCO</sub> |

| 0 | 1  | 1      | 1   | 0 | -14    | –0.252 x τ <sub>VCO</sub> |

| 0 | 1  | 1      | 0   | 1 | -13    | -0.234 x τ <sub>VCO</sub> |

| 0 | 1  | 1      | 0   | 0 | -12    | –0.216 x τ <sub>VCO</sub> |

| 0 | 1  | 0      | 1   | 1 | -11    | –0.198 x τ <sub>VCO</sub> |

| 0 | 1  | 0      | 1   | 0 | -10    | –0.180 x τ <sub>VCO</sub> |

| 0 | 1  | 0      | 0   | 1 | -9     | –0.162 x τ <sub>VCO</sub> |

| 0 | 1  | 0      | 0   | 0 | -8     | –0.144 x τ <sub>VCO</sub> |

| 0 | 0  | 1      | 1   | 1 | -7     | –0.126 x τ <sub>VCO</sub> |

| 0 | 0  | 1      | 1   | 0 | -6     | –0.108 x τ <sub>VCO</sub> |

| 0 | 0  | 1      | 0   | 1 | -5     | –0.090 x τ <sub>VCO</sub> |

| 0 | 0  | 1      | 0   | 0 | -4     | -0.072 x τ <sub>VCO</sub> |

| 0 | 0  | 0      | 1   | 1 | -3     | –0.054 x τ <sub>VCO</sub> |

| 0 | 0  | 0      | 1   | 0 | -2     | –0.036 x τ <sub>VCO</sub> |

| 0 | 0  | 0      | 0   | 1 | -1     | –0.018 x τ <sub>VCO</sub> |

| 0 | 0  | 0      | 0   | 0 | 0      | 0                         |

| 1 | 0  | 0      | 0   | 0 | 0      | 0                         |

| 1 | 0  | 0      | 0   | 1 | 1      | 0.018 x τ <sub>VCO</sub>  |

| 1 | 0  | 0      | 1   | 0 | 2      | 0.036 x τ <sub>VCO</sub>  |

| 1 | 0  | 0      | 1   | 1 | 3      | 0.054 x τ <sub>VCO</sub>  |

| 1 | 0  | 1      | 0   | 0 | 4      | 0.072 x τ <sub>VCO</sub>  |

| 1 | 0  | 1      | 0   | 1 | 5      | 0.090 x τ <sub>VCO</sub>  |

| 1 | 0  | 1      | 1   | 0 | 6      | 0.108 x τ <sub>VCO</sub>  |

| 1 | 0  | 1      | 1   | 1 | 7      | 0.126 x τ <sub>VCO</sub>  |

| 1 | 1  | 0      | 0   | 0 | 8      | 0.144 x τ <sub>VCO</sub>  |

| 1 | 1  | 0      | 0   | 1 | 9      | 0.162 x τ <sub>VCO</sub>  |

| 1 | 1  | 0      | 1   | 0 | 10     | 0.180 x τ <sub>VCO</sub>  |

| 1 | 1  | 0      | 1   | 1 | 11     | 0.198 x τ <sub>VCO</sub>  |

| 1 | 1  | 1      | 0   | 0 | 12     | 0.216 x τ <sub>VCO</sub>  |

| 1 | 1  | 1      | 0   | 1 | 13     | 0.234 x τ <sub>VCO</sub>  |

| 1 | 1  | 1      | 1   | 0 | 14     | 0.252 x τ <sub>VCO</sub>  |

| 1 | 1  | 1      | 1   | 1 | 15     | 0.270 x τ <sub>VCO</sub>  |

FIGURE 4. Window Strobe Truth Table

Customers who employ the DP8459 in a system without a MICROWIRETM (or functionally equivalent) bus configuration and who wish to fix the synchronization window in the nominal position while deselecting the test mode need only load all-zero's into the Control Register following power-up; this may be easily achieved in some system configurations (requiring no additional hardware) by tying  $\overline{\text{CRE}}$  to RG, tying CRC to ERD and tying CRD to ground, providing the necessary waveforms are present for register loading prior to the first read operation.

The DP8459 provides two pins for PLL filtering purposes, CHARGE PUMP OUTPUT (CPO) and VCO INPUT (VCOI). These provide the Customer with great flexibility in filter design, permitting high-order filter functions for optimization of PLL lock characteristics and bit jitter rejection. For basic 3rd order applications, CPO and VCOI may be tied together

(single-node) with a simple lead-lag, C||(R+C) filter tied between these pins and ground. More esoteric filter designs may be implemented if the pins are electrically separated and a two-port filter network is established between CPO, VCOI, and ground. National Semiconductor supplies initial PLL filter recommendations for the single-node configuration within this data sheet with the qualifying statement that they are very general in nature, intended primarily for production testing of static window margin, and are NOT optimized for any particular disk system. For optimum performance, the Customer should pursue a filter design which is individualized and tailored to the requirements of the specific system involved. This is particularly true for the two-port filtering technique. See Figure 5 for initial single-node filter design recommendations.

http://www.national.com

+ o. 1 **Proof**

| Code                               | MFM     | MFM  | мғм  | 2,7   | 2,7     | Units       |

|------------------------------------|---------|------|------|-------|---------|-------------|

| Rate                               | 0.500   | 2    | 5    | 10    | 20      | Mbit/sec    |

| VCO freq.                          | 1       | 4    | 10   | 20    | 40      | MHz         |

| Sync bytes                         | 12      | 12   | 12   | 12    | 12      | bytes       |

| pulses/byte                        | 8       | 8    | 8    | 4     | 4       | flux tran's |

| sync length                        | 192     | 48   | 19.2 | 9.6   | 4.8     | μs          |

| sync freq                          | 0.500   | 2    | 5    | 5     | 10      | MHz         |

| N <sub>sync</sub>                  | 2       | 2    | 2    | 4     | 4       | none        |

| N <sub>max</sub> /N <sub>min</sub> | 4/2     | 4/2  | 4/2  | 8/3   | 8/3     | none        |

| $\zeta_{min}$                      | 0.5     | 0.5  | 0.5  | 0.5   | 0.5     | none        |

| $\zeta_{max}$                      | 0.7     | 0.7  | 0.7  | 0.8   | 0.8     | none        |

| ζ <sub>sync</sub>                  | 0.7     | 0.7  | 0.7  | 0.7   | 0.7     | none        |

| ω <sub>sync</sub>                  | 35      | 144  | 353  | 606   | 1230    | Krad/sec    |

| C1                                 | 0.5     | 0.12 | 0.05 | 0.018 | 8200 pF | μF*         |

| R1                                 | 82      | 82   | 82   | 150   | 150     | Ω           |

| C2                                 | 0.01 μF | 2700 | 1000 | 510   | 200     | pF          |

Note 1: Preamble (sync) natural frequency chosen yields phase error ≤ 0.01 radians at sync field end, given a 1% frequency step at READ GATE assertion. Rnom = Rboost = 2.4k for all above loop filter selections. HGD is tied to RG, FLC is tied to PD and CPO is tied to VCOI as well as to the loop filter components.

Note 2: Component values are listed for purposes of window specification testing and correlation. These values do not necessarily yield optimum performance in actual system applications. PLL dynamics and code characteristics are presented for Customer information and convenience only. See Section 3.1.

\*Unless otherwise noted.

#### FIGURE 5. Test Conditions and Component Values for Static Window Truncation Testing

The DP8459 VCO is constrained at all times to operate within a frequency swing of approximately ±50% of the frequency present at the REFERENCE CLOCK input. Internal frequency detector/comparator circuitry senses when the VCO overruns the 50% boundary and forces the charge pump to move the VCO back toward the REFERENCE CLOCK frequency until the 50% constraint is again satisfied—thus preventing VCO cunaway in the event of loss of lock or during extended periods where ENCODED READ DATA is not present. Additionally, this technique causes the filter node voltage to behave as if a voltage clamp were present at the Charge Pump Output, preventing the control voltage, in the event of loss of lock, from drifting outside of its operating range and inadvertently extending lock recovery time.

A special test mode feature has been incorporated into the DP8459 which allows a specific input pin to change function and act as an excitation source (substitute VCO) for clocking internal logic circuitry. When the last bit in the CONTROL REGISTER is taken to a logical ONE, the VCO is stopped, and the HGD input is redirected to act as a clock source for the VCO divider circuitry. Additionally, the Delay Line and Timing Extractor blocks are disabled when the Test Mode is entered, and thus the device will not function normally and should not be operated in this mode for purposes other than internal gate exercising. Further information regarding application of the Test Mode will be furnished at the Customer's request: contact National Semiconductor Logic Marketing Group or Logic Applications Group.

#### 2.1 Functional Block Description

#### **PULSE GATE**

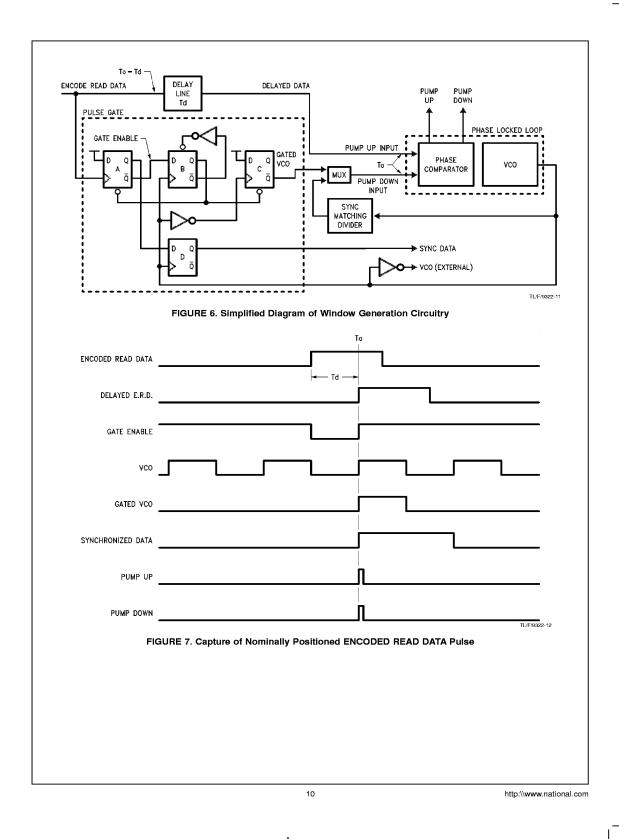

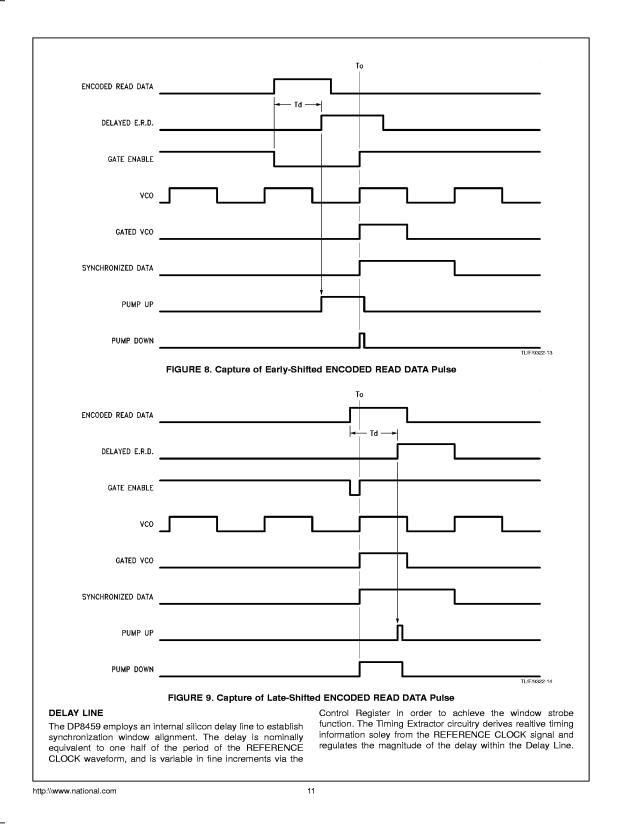

The function of the Pulse Gate within the DP8459 is twofold. First, the block contains the ECL flip-flop which captures each arriving ENCODED READ DATA bit and transmits the bit to the SYNCHRONIZED DATA output. The very high switching speed of the bit-capture ECL flip-flop minimizes the portion of window margin loss caused by flip-flop metastability at window boundaries. Second, the Pulse Gate regulates the transmission of the VCO waveform into the Phase Comparator, allowing only one VCO pulse to pass with each arriving ENCODED READ DATA pulse. See Figure 6 for a simplified logical representation of the Pulse Gate block. The one-to-one data/VCO pulse ratio produced by the Pulse Gate permits the multiple-harmonic nature of encoded data to be accommodated by the phase/frequency comparator. During the non-Read mode or during the portion of the Read mode within which the Customer has set the FREQUENCY LOCK CONTROL pin to a logical-zero (low), the Pulse Gate is inactive (bypassed) and the VCO frequency is divided as appropriate to match the incoming frequency source (ENCODED READ DATA or the REFERENCE CLOCK input).

http://www.national.com

PrintDate=1996/07/31 PrintTime=11:05:48 ds009322 Rev. No. 1

Powered by ICminer.com Electronic-Library Service CopyRight 2003

PrintDate=1996/07/31 PrintTime=11:05:49 ds009322 Rev. No. 1 **Proof**

Powered by ICminer.com Electronic-Library Service CopyRight 2003

The Delay Line thus remains insensitive to the external components associated with the extractor as well as to supply voltage, temperature, and IC process variations.

#### TIMING EXTRACTOR

This block extracts timing information from the REFERENCE CLOCK input for use by the variable silicon delay line. External passive components (tied to the Timing Extractor Filter pin) are associated with this block, although the accuracy of the circuit's function remains independent of the general value and tolerance of the components. The resistor-capacitor net is employed by the Timing Extractor for stabilization purposes-no monostable multivibrator (one-shot) circuitry is employed by the DP8459. Note that the performance of the delay line is directly dependent upon the accuracy of the REFERENCE CLOCK input waveform. Either a crystal reference generator or a stable servo clock source must be applied to this input. Multiplexing of the REFERENCE CLOCK waveform between read operations (within multiple data rate systems) is acceptable, although sufficient Timing Extractor stabilization time must be allowed following any perturbation at this pin before a read operation may be performed (see Figure 10 for timing table).

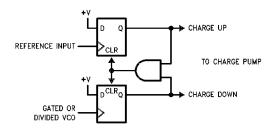

#### PHASE COMPARATOR

The DP8459 employs a digital Phase Comparator (non-harmonic discriminator circuit) which has the capability of forcing the frequency of the PLL VCO toward the frequency of the reference input regardless of the magnitude of the frequency difference. The function of the Phase Comparator circuit can be represented in a diagrammatically simplified form as in Figure 11.

The Phase Comparator's action can be disabled at any time (cleared) via the  $\overline{\text{COAST}}$  input pin, allowing the VCO to free-run.

#### **CHARGE PUMP**

The Charge pump is a high speed, switching, dual-gain, bi-directional current source whose current flow is controlled by the digital Phase Comparator circuit. The current pulses at the CHARGE PUMP OUTPUT (CPO) pin thus reflect the magnitude and sign of the phase error seen at the input of the Phase Comparator. The CPO pin is connected externally to a passive component network whose impedance translates the aggregate current into a voltage for the VCO INPUT while providing a low-pass filter function for the PLL. The matched source and sink current generators' operating currents are set via the  $R_{\text{NOMINAL}}$  and  $R_{\text{BOOST}}$  pins, which are supplied current from  $V_{\text{CC}}$  through external resistors. The bias voltages at the  $R_{\text{NOMINAL}}$  and  $R_{\text{BOOST}}$  pins are set to 0.75 x  $V_{\text{CC}};$  the current into each of these pins is internally multiplied by 2 for Charge Pump use. The CPO current is defined as follows:

> $I_{CPO} = (V_{CC}/2)/R_{NOM}$ HIGH GAIN DISABLE high (logical-one)  $I_{CPO} = (V_{CC}/2)/(R_{NOM}||R_{BOOST})$ HIGH GAIN DISABLE low (logical-zero)

| RFC Frequency | 1    | 4   | 10    | 20    | 40    | MHz |

|---------------|------|-----|-------|-------|-------|-----|

| CT1           | 0.82 | 0.2 | 0.082 | 0.056 | 0.027 | μF  |

| RT1           | 68   | 68  | 68    | 68    | 68    | Ω   |

| Settling Time | 192  | 96  | 19.2  | 9.6   | 4.6   | μs  |

Values may be interpolated for intermediate data rates. Timing Extractor settling times are given which indicate time required for the DP8459 to accommodate a change of Strobe setting from nominal selection to either extreme (early/late), or vice versa, to within approximately 1% of final value

FIGURE 10. TIMING EXTRACTOR FILTER Component Values for Various Data Rates

TL/F/9322-17

FIGURE 11. Simplified Digital Phase-Frequency Comparator

# **VOLTAGE CONTROL OSCILLATOR (VCO)**

The DP8459 VCO is comprised of two portions-a self contained, high frequency oscillator (no external components) whose frequency is regulated by the voltage at the VCO INPUT pin, and a programmable modulus digital divider. The oscillator is only required to operate over approximately a 2:1 frequency range; the divider modulus is programmable in factors of 2. The two blocks work in conjunction to achieve a continuous range of equivalent VCO operating frequencies from 500 kHz to 50 MHz. (See Figure 12.)

# CONTROL REGISTER

Within the DP8459, the Control Register is a MICROWIRE compatible, 6-bit shift register block with bits 0 through 4 employed to control the window strobe function and bit 5 employed to regulate the device test mode (see Figures 13 and 14 ). Information is serially shifted into the Control Register via the CRD and CRC (negative edge clock) pins whenever the CRE pin is active (logical-zero). When the CRE pin is inactive (logical-one), CRD and CRC are ignored. Figure 3 shows the truth table for the VCO range select function; Figure 4 shows the truth table for the window strobe function.

http://www.national.com

PrintDate=1996/07/31 PrintTime=11:05:51 ds009322 Rev. No. 1

# SYNCHRONIZATION FIELD MATCHING DIVIDER

The Synchronization field Matching Divider is a programmable modulus counter employed for implementation of the preamble frequency lock function. It is placed in the VCO feedback path to match the relative frequency of the VCO seen at the Phase Comparator to the frequency of the ENCODED READ DATA (preamble) during the read operation whenever the FREQUENCY LOCK CONTROL input is active (logic-zero). The modulus of the divider, M, is determined by the states of the SYNC PATTERN SELECT 0 and 1 inputs, as defined by the table in Figure 15.

| 1 | Pattern<br>lect | Sync Matching  Divider Modulus | Expected<br>Code<br>Preamble |

|---|-----------------|--------------------------------|------------------------------|

| 1 | 0               | M                              |                              |

| 0 | 0               | 1                              | GCR                          |

| 0 | 1               | 2                              | MFM; 1,N                     |

| 1 | 0               | 3                              | 2,7                          |

| 1 | 1               | 4                              | 2,7                          |

# FIGURE 15. SYNC PATTERN SELECT Input Truth Table

Prior to the assertion of READ GATE, the divider is held in a known count state and is enabled at the end of the zero phase

http://www.national.com

13

PrintDate=1996/07/31 PrintTime=11:05:52 ds009322 Rev. No. 1 **Proc**

start sequence in correct phase relationship with the ENCODED READ DATA. Re-assertion (logical zero) of the FREQUENCY LOCK CONTROL pin within a read operation (following the normal FLC deassertion after lock is achieved) is permissible; however, it should be noted that the initial phase error of the Synchronization Field Matching Divider with respect to the ENCODED READ DATA at FREQUENCY-LOCK CONTROL re-assertion may be as large as M x τ<sub>VCO</sub> in magnitude, possibly resulting in an extended PLL settling

#### ZERO PHASE START

The function of the zero phase start (ZPS) block is to clear the Phase Comparator and freeze the VCO in a known phase when a transition occurs at the READ GATE input (either high or low), and restart the VCO in a precise, controlled phase with respect to the newly selected input (ENCODED READ DATA or REFERENCE CLOCK ÷ 2, respectively). The ZPS circuit also resets the count state of the Synchronization field Matching Divider in anticipation of locking to specific preamble information (when frequency lock is being employed), and controls the operation of the REFERENCE CLOCK multiplexer. ZPS operation at READ GATE assertion is aimed at optimizing initial window alignment and thus minimizing initial phase step and the resulting phase lock acquisition time. ZPS is also employed at deassertion of READ GATE; however, the ZPS phase alignment for the REFERENCE CLOCK signal at READ GATE deassertion has been made less stringent than for ENCODED READ DATA at READ GATE assertion.

#### PREAMBLE PATTERN DETECTOR

The Preamble Pattern Detector block has a pattern-specific recognition circuit keyed to search the ENCODED READ DATA for the pattern selected at the SYNC PATTERN SELECT inputs. The pattern search begins following the assertion of READ GATE and the completion of the zero phase start

# Input Current

systems.

# 2.2 SPECIFICATION TABLES

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage  | 7V         |

|-----------------|------------|

| TTL Inputs      | 7 <b>V</b> |

| Output Voltages | 7V         |

| (R <sub>NOM</sub> , R <sub>BOOST</sub> , CPO, VCOI, TEF) | 2 mA            |

|----------------------------------------------------------|-----------------|

| Storage Temperature                                      | −65°C to +150°C |

| Operating Temperature Range                              | 0°C to +70°C    |

| ESD Susceptibility ( Note 3 )                            | 1500V           |

|                                                          |                 |

sequence, and continues until approximately 32 uninterrupted

ENCODED READ DATA pulses of the 1T, 2T or 3T pattern have been detected, or until 16 uninterrupted ENCODED

READ DATA pulses of the 4T pattern have been detected (see

specification tables). When this event occurs, the PREAMBLE

DETECTED output becomes active high (logical-one). The

output will then remain latched in the high state until READ

GATE is deasserted. The PREAMBLE DETECTED output may be tied to the HIGH GAIN DISABLE input to regulate the gain

of the PLL during the preamble lock sequence, and/or tied to the FREQUENCY LOCK CONTROL input for self-regulation

of frequency acquisition in hard or pseudo-hard sectored

The Frequency Offset Detector is employed to constrain the

VCO frequency swing, preventing VCO runaway associated

with standard, wide-range voltage controlled oscillators. The

circuitry will sense the relative difference between the

REFERENCE CLOCK frequency and the VCO frequency,

sending a "charge-up" signal to the Charge Pump to correct

the VCO should a limit of approximately -50% in frequency

differential (VCO w.r.t. REF CLOCK) be exceeded, and sending a "charge-down" signal to the Charge Pump to correct

the VCO should a limit of approximately +50% in frequency

differential be exceeded. The resulting voltage-clamping action at the filter node(s) also prevents out-of-range control voltage

This block issues the VCO signal following READ GATE

assertion and completion of the zero phase start sequence, and issues the REFERENCE CLOCK input signal when the

READ GATE is deasserted. Multiplexer switching is achieved

without glitches. The output is intended to be used both for read and write clock purposes. (Please note output loading

SYNCHRONIZATION CLOCK OUTPUT MULTIPLEXER

±50% VCO FREQUENCY OFFSET DETECTOR

straying and thus speeds lock recovery.

recommendations for this pin in Section 6.)

# **Operating Conditions**

| Symbol           | Parameter                       | Conditions | Min  | Тур  | Max   | Units |

|------------------|---------------------------------|------------|------|------|-------|-------|

| V <sub>cc</sub>  | Supply Voltage                  |            | 4.75 | 5.00 | 5.25  | V     |

| T <sub>A</sub>   | Ambient Temperature             |            | 0    | 25   | 70    | °C    |

| I <sub>OH</sub>  | High Logic Level Output Current | SYNC CLOCK |      |      | -2000 | μΑ    |

|                  |                                 | Others     |      |      | -400  |       |

| I <sub>OL</sub>  | Low Logic Level Output Current  | SYNC CLOCK |      |      | 20    | mA    |

|                  | ( Note 1 )                      | Others     |      |      | 8     |       |

| V <sub>IH</sub>  | High Logic Level Input Voltage  |            | 2    |      |       | ٧     |

| V <sub>IL</sub>  | Low Logic Level Input Voltage   |            |      |      | 0.8   | V     |

| f <sub>NRZ</sub> | Operating Data Rate Range       |            | 0.25 |      | 25    | Mb/s  |

http://www.national.com

14

PrintDate=1996/07/31 PrintTime=11:05:54 ds009322 Rev. No. 1

| Operat              | ting Conditions (Continued)                                        |            |         |     |     |       |

|---------------------|--------------------------------------------------------------------|------------|---------|-----|-----|-------|

| Symbol              | Parameter                                                          | Conditions | Min     | Тур | Max | Units |

| t <sub>PW-RFC</sub> | Width of REFERENCE CLOCK, High or Low                              |            | 8       |     |     | ns    |

| t <sub>PW-ERD</sub> | Width of ENCODED READ DATA                                         |            | 12 High |     |     | ns    |

|                     |                                                                    |            | 18 Low  |     |     |       |

| t <sub>PW-CRE</sub> | Width of CONTROL REGISTER ENABLE,                                  |            | 40      |     |     | ns    |

|                     | High or Low (Note 2)                                               |            |         |     |     |       |

| t <sub>SU-CRD</sub> | CONTROL REGISTER DATA Set-Up Time                                  |            | 20      |     |     | ns    |

|                     | with Respect to CRC (Note 2)                                       |            |         |     |     |       |

| t <sub>H-CRD</sub>  | CONTROL REGISTER DATA Hold Time                                    |            | 10      |     |     | ns    |

|                     | with Respect to CRC (Note 2)                                       |            |         |     |     |       |

| t <sub>SU-CRE</sub> | CONTROL REGISTER ENABLE Set-Up Time with Respect to CRC ( Note 2 ) |            | 20      |     |     | ns    |

40

ns

μΑ

1000

Note 1: PUMP UP and PUMP DOWN outputs have no current sinking capability and thus are excluded from this specification.

Note 2: Parameter guaranteed by correlation to characterization data. No outgoing test performed.

CONTROL REGISTER ENABLE Hold Time

with Respect to CRC ( Note 2 )

CONTROL REGISTER CLOCK Pulse

Width, Positive or Negative (Note 2)

Combined  $R_{\text{NOM}}$  &  $R_{\text{BOOST}}$  Input Current

Note 3: Human body model; 120 picofarads through 1.5 k $\Omega$ .

t<sub>H-CRE</sub>

I<sub>CPIN</sub>

t<sub>PW-CRC</sub>

# **AC Electrical Characteristics**

Over recommended  $\ensuremath{V_{\text{CC}}}$  and operating temperature range.

| Symbol                              | Parameter                                                                                                 | Min                | Тур                                            | Max                | Units     |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------|--------------------|-----------|

| t <sub>STOP</sub>                   | SYNC CLOCK Negative Transitions following READ GATE until Data Lock ZPS Sequence Begins (VCO Freezes)     |                    | 2                                              | 3                  | _         |

| <sup>†</sup> RESTART                | Positive ENCODED READ DATA Transitions following VCO Freeze until VCO Restarts                            |                    | 2                                              |                    | _         |

| <sup>†</sup> READ ABORT             | Number of REF CLOCK Cycles following READ GATE Deactivation until REF CLOCK Lock ZPS Sequence Begins      |                    |                                                | 4                  | _         |

| t <sub>T</sub>                      | Window Truncation (Half Window Loss);  DP8459V-10 10 Mbit/sec (Note 1 )  DP8459V-25 20 Mbit/sec (Note 2 ) |                    | 3% x τ <sub>νco</sub><br>4% x τ <sub>νco</sub> | 3.0<br>2.5         | ns<br>ns  |

| φ Linearity                         | Phase Range for Charge Pump Linearity (wrt VCO)                                                           |                    | ±π                                             |                    | Radians   |

| K <sub>vco</sub>                    | VCO Gain Constant                                                                                         | 1.0 ω <sub>Ο</sub> | 1.2 ω <sub>O</sub>                             | 1.6 ω <sub>O</sub> | Rad/Sec \ |

| f <sub>MAX</sub> vco                | VCO Maximum Frequency; RS0 = RS1 = RS2 = Logical ZERO                                                     | 70                 |                                                |                    | MHz       |

| t <sub>SD0</sub>                    | Time Skew between SYNC CLOCK Negative Edge and SYNC DATA Negative Edge                                    | 0                  |                                                | 10                 | ns        |

| t <sub>SD1</sub>                    | Time Skew between SYNC CLOCK Negative Edge and SYNC DATA Positive Edge                                    | 0                  |                                                | 10                 | ns        |

| t <sub>ZPSR</sub>                   | Zero Phase Start Trigger Bit Targeting Accuracy,<br>READ GATE Activation (READ) ( Note 4 )                |                    | 2                                              |                    | ns        |

| t <sub>PWPC</sub>                   | Width of PCT, PU or PD Outputs in Fully Stabilized Lock (ERD Free of Jitter); R-Pull-Down = 510Ω          |                    | 10                                             |                    | ns        |

| Δf <sub>VCO</sub> /f <sub>RFC</sub> | Automatic f <sub>VCO</sub> Range Limiting                                                                 |                    | 50                                             |                    |           |

http://www.national.com

15

PrintDate=1996/07/31 PrintTime=11:05:55 ds009322 Rev. No. 1 **Proof**

# AC Electrical Characteristics (Continued)

Over recommended  $V_{\text{CC}}$  and operating temperature range.

| Symbol                | Parameter                                                                                      | Min | Тур                              | Max | Units            |

|-----------------------|------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|------------------|

| t <sub>HOLD</sub>     | SYNC CLOCK Rest Period (Logical One) at Assertion or De-Assertion of READ GATE                 | 1/2 |                                  | 3   | T <sub>vco</sub> |

| t <sub>PDT</sub>      | SCK Negative Edge to PREAMBLE DETECTED Positive Edge at End of Detection Sequence              |     |                                  | 25  | ns               |

| L <sub>PDT1</sub>     | Length of Valid 1T Preamble Pattern Required for<br>Occurrence of PREAMBLE DETECTED            | 33  | 34                               | 35  | ERD<br>Pulses    |

| L <sub>PDT2</sub>     | Length of Valid 2T Preamble Pattern Required for<br>Occurrence of PREAMBLE DETECTED            | 32  | 33                               | 34  | ERD<br>Pulses    |

| L <sub>PDT3</sub>     | Length of Valid 3T Preamble Pattern Required for<br>Occurrence of PREAMBLE DETECTED            | 31  | 32                               | 33  | ERD<br>Pulses    |

| L <sub>PDT4</sub>     | Length of Valid 4T Preamble Pattern Required for<br>Occurrence of PREAMBLE DETECTED            | 15  | 16                               | 17  | ERD<br>Pulses    |

| ts                    | Window Strobe Time Step (M = Hex Value of Bits 0-3 in CONTROL REGISTER; Bit 4 = Sign Bit)      |     | M x (1.8%)<br>x t <sub>RFC</sub> |     | ns               |

| t <sub>RFC-SCK1</sub> | Positive Transition Propagation Delay from REF CLOCK INPUT to SYNC CLOCK OUTPUT, READ GATE Low |     |                                  | 15  | ns               |

| t <sub>RFC-SCK0</sub> | Negative Transition Propagation Delay from REF CLOCK INPUT to SYNC CLOCK OUTPUT, READ GATE Low |     |                                  | 15  | ns               |

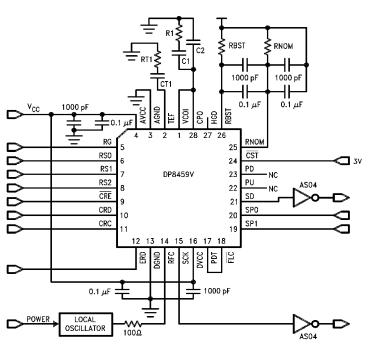

Note 1: The DP8459V-10 static window specification,  $t_T$ , applies only to the factory-tested 2,7-code data rate of 10 Mb/s (with RS0,1,2 = 010) and with the component values as listed in Figures 5 and 10, test configuration as shown in Figure 23, test procedure as shown in Figure 24, and strobe word M = -2. Significant variation in  $t_T$  as a percentage of the VCO period due to the use of other filters and data rates is not expected.

Note 2: The DP8459V-25 static window specification, t<sub>T</sub>, incorporates the DP8459V-10 window specification and, in addition, the factory-tested 2,7-code data rate of 20 Mb/s (with RS0, 1, 2, = 000), with the component values as listed in Figures 5 and 10, test configuration as shown in Figure 23, test procedure as shown in Figure 24, and strobe word M = -3. Significant variation in t<sub>T</sub> as a percentage of the VCO period due to the use of other filters and data rates is not expected.

Note 3: I<sub>IN</sub> = V<sub>CC</sub>/(4 x R<sub>IN</sub>). R<sub>IN</sub> = R<sub>NOM</sub> (HGD High) or R<sub>NOM</sub>||R<sub>BOOST</sub> (HGD Low).

Note 4: t<sub>ZPSR</sub> (ZPS Read) gauges the accuracy with which the ZPS circuitry aligns the VCO to the triggering ERD bit internally (i.e., initial phase step) at the completion of a ZPS operation following READ GATE assertion.

# DC Electrical Characteristics Over recommended operating temperature range.

| Symbol               | Parameter                           | Conditions                                                | Min                 | Тур                   | Max                 | Units |

|----------------------|-------------------------------------|-----------------------------------------------------------|---------------------|-----------------------|---------------------|-------|

| V <sub>IC</sub>      | Input Clamp Voltage                 | $V_{CC} = Min, I_I = -18 \text{ mA}$                      |                     |                       | -1.5                | V     |

| V <sub>OH</sub>      | High Level Output Voltage           | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max              | V <sub>CC</sub> -2V | V <sub>CC</sub> -1.6V |                     | V     |

| V <sub>OL</sub>      | Low Level Output Voltage ( Note 4 ) | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max              |                     |                       | 0.5                 | V     |

| I <sub>IH</sub>      | High Level Input Current            | $V_{CC} = Max, V_1 = 2.7V$                                |                     |                       | 20                  | μA    |

| I <sub>IL</sub>      | Low Level Input Current             | $V_{CC} = Max, V_I = 0.4V$                                |                     |                       | -200                | μA    |

| lo                   | Output Drive Current ( Note 1 )     | $V_{CC} = Max, V_{O} = 2.125V$                            | -12                 |                       | -110                | mA    |

| I <sub>CPO</sub>     | Charge Pump Output Current (K1)     | 100 ≤ I <sub>Rp</sub> ≤ 1000 (Note 2 )                    | 1.7 I <sub>Rp</sub> | 2.0 I <sub>Rp</sub>   | 2.5 I <sub>Rp</sub> | μA    |

| I <sub>CPO-OFF</sub> | Charge Pump Output Inactive Current | 100 ≤ I <sub>Rp</sub> ≤ 1000 (Note 2 )                    | -0.85               |                       | +0.85               | μA    |

| I <sub>vcoi</sub>    | VCOI Offset Current                 | VCOI Voltage 1.5V                                         | -0.25               |                       | +0.25               | μA    |

| V <sub>RNOM</sub>    | Voltage across R-NOM Resistor       | $1.2 \text{ k}\Omega ≤ \text{R-NOM} ≤ 12 \text{ k}\Omega$ | Typ.<br>-18%        | 0.26 V <sub>CC</sub>  | Typ.<br>+18%        | V     |

| V <sub>RBST</sub>    | Voltage across R-BOOST Resistor     | 1.2 k $\Omega$ ≤ R-BOOST ≤ 12 k $\Omega$                  | Typ.<br>–18%        | 0.26 V <sub>CC</sub>  | Typ.<br>+18%        | ٧     |

| I <sub>CC1</sub>     | Supply Current, Nominal Strobe      | V <sub>CC</sub> = Max (Note 3)                            |                     |                       | 190                 | mA    |

Note 1: This value has been chosen to produce a current that closely approximates one-half of the true short-circuit output current, I<sub>OS</sub>.

Note 2: I<sub>Rp</sub> = I<sub>NOM</sub> + I<sub>BOOST</sub>

Note 3: I<sub>CC1</sub> is measured with the window strobe set at nominal timing (Strobe Bits 0 through 5 = 0,0,0,0,0,0); VCO operating at maximum allowed frequency within any given range selection. I<sub>CC</sub> typically increases by 30 mA when the strobe is set at the maximum early position (M = -15). This is not a linear increase per step. Most of the increase occurs as the -15 step is approached. I<sub>CC</sub> decreases as the window is moved late.

Note 4: PUMP UP and PUMP DOWN outputs have no current sinking capability and thus are excluded from this specification.

http://www.national.com

PrintDate=1996/07/31 PrintTime=11:05:57 ds009322 Rev. No. 1 **Proof**

16

# **External Component Selection**

| Symbol             | Parameter                                    | Min  | Тур | Max | Units |

|--------------------|----------------------------------------------|------|-----|-----|-------|

| R <sub>NOM</sub>   | Charge Pump Nominal Operating                | 1.2  |     | 12  | kΩ    |

|                    | Current Setting Resistor ( Note 1 )          |      |     |     |       |

| R <sub>BOOST</sub> | Charge Pump Boost Current                    | 1.2  |     | ∞   | kΩ    |

|                    | Setting Resistor ( Note 1 )                  |      |     |     |       |

| C <sub>NOM</sub>   | R <sub>NOM</sub> Bypass Capacitor (Note 2)   | 0.01 |     |     | μF    |

| C <sub>BOOST</sub> | R <sub>BOOST</sub> Bypass Capacitor (Note 2) | 0.01 |     |     | μF    |

| R <sub>PU</sub>    | PUMP UP Open Emitter Output                  | 510  |     |     | Ω     |

|                    | Pull-Down Resistor                           |      |     |     |       |

| R <sub>PD</sub>    | PUMP DOWN Open Emitter Output                | 510  |     |     | Ω     |

|                    | Pull-Down Resistor                           |      |     |     |       |

Note 1: The minimum allowed value for the parallel combination of  $R_{\mbox{NOM}}$  and  $R_{\mbox{BOOST}}$  is 1.2  $k\Omega$

Note 2:  $C_{\mbox{NOM}}$  and  $C_{\mbox{BOOST}}$  should be high quality, high frequency type.

# 3.0 PLL Applications: Loop Filter Design

In order to maintain greatest design flexibility for the Customer, all PLL filter components and Charge Pump gain setting elements reside external to the DP8459. All PLL dynamics are thus under the control of the system designer. The following is a brief analysis of the DP8459 PLL; Section 3.1 contains a derivation of component values based on projected requirements within an example hard disk drive system.

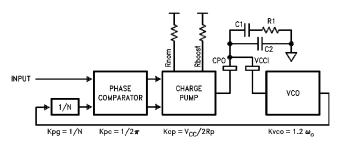

Figure 16 represents the DP8459 PLL in simplified form.

Mathematical gain representations for each block are:

Pulse Gate equivalent gain  $K_{PG} = 1/N$  $K_{PC} = 1/(2\pi)$ Phase Comparator gain

Charge Pump gain where  $R_p = R_{NOM}$ ,

$K_{CP} = V_{CC}/2R_p$  Charge Pump gain w HGD high;  $R_p = R_{NOM}||R_{BOOST}$ , HGD low

$K_{VCO}$  = 1.2  $\omega_{O}$  VCO gain ( $\omega_{O}$  = operating center frequency)

TL/F/9322-18

# FIGURE 16. Basic DP8459 Phase Locked Loop Block Diagram

N is defined as the number VCO cycles per recorded ENCODED READ DATA pulse, or conversely, the ratio of the VCO frequency to the ENCODED READ DATA frequency. The aggregate block gain equation (excluding the loop filter) can be

$$K_B = 1.2 V_{CC} f_O/(2R_pN)$$

The impedance of the loop filter is

$$Z(s) = \frac{1}{sC_2} || \left( \frac{1}{sC_1} + R_1 \right) = \frac{1 + sR_1C_1}{sC_1(1 + C_2/C_1 + sR_1C_2)}$$

The open loop system response G(s) is given by

$$G(s) = \frac{K_B}{s} \times \frac{1 \, + \, sR_1C_1}{sC_1 \, (1 \, + \, C_2/C_1 \, + \, sR_1C_2)}$$

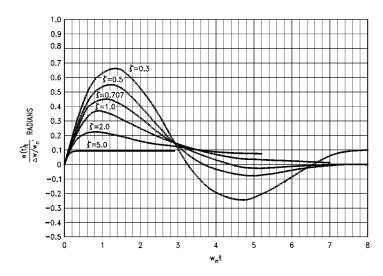

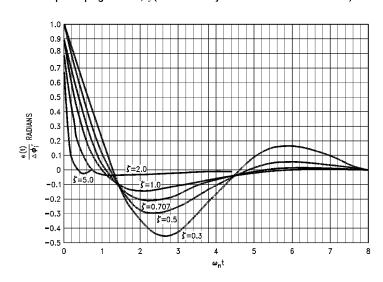

This last equation reveals the PLL with this filter configuration is a third order system, which is typically difficult to analyze. However, if  $C_2 \ll C_1$ , it can be argued that the behavior of the third order loop closely resembles that of a second order system, allowing for a greatly simplified analysis.

If  $C_2 << C_1$ , the impedance Z(s) approximates to

$$\frac{\text{1} + \text{sR}_1\text{C}_1}{\text{sC}_1}$$

The overall open loop gain (including the filter) is then

$$G(s) = \frac{K_B}{s} \times \frac{1 + sR_1C_1}{sC_1}$$

Substituting K<sub>B</sub> into the equation,

$$G(s) = \frac{1.2\,f_o\,V_{CC}}{s2N} \times \frac{1\,+\,sR_1C_1}{sR_pC_1} \label{eq:Gs}$$

$\tau_1 = R_p C_1$  and  $\tau_2 = R_1 C_1$  are the pole and zero, respectively, which govern the system response. The closed loop gain H(s)

$$H(s) = \frac{\phi_{OUT}}{\phi_{IN}} = \frac{G(s)}{1 + G(s)}$$

http://www.national.com

17

PrintDate=1996/07/31 PrintTime=11:06:00 ds009322 Rev. No. 1

Substituting,

$$H(s) = \frac{K_B (sR_1C_1 + 1)}{s^2C_1 + K_B (sR_1C_1 + 1)}$$

$$= \frac{(K_B/C_1)(sR_1C_1\,+\,1)}{s^2\,+\,sK_BR_1\,+\,K_B/C_1}$$

The second order characteristic equation can be written as follows:

$$s^2 + sK_BR_1 + K_B/C_1 = s^2 + s2\zeta\omega_n + \omega_n^2$$

Extracting the component values from these results,

$$C_1 = \frac{K_B}{\omega_n^2} = \frac{1.2 \, V_{CC} \, f_o/(2R_pN)}{\omega_n^2} \label{eq:c1}$$

$$R_1 = \frac{2 \zeta \omega_n}{K_B} = \frac{2 \zeta \omega_n}{1.2 \, V_{CC} \, f_0 / (2 R_p N)}$$

$$C_2 \leq (\frac{1}{10}) C$$

Thus, one is able to select component values in accordance with specific system requirements, i.e., with given VCO center frequency (equivalent to REFERENCE CLOCK frequency),  $R_{\rm p}$  (in either high or low gain mode), N (the ratio of the VCO frequency to the ENCODED READ DATA frequency), the desired natural frequency of the loop, and the desired damping ratio.

The natural frequency and the damping ratio may be extracted from the component values to determine system behavior under various conditions (differing data patterns, i.e., varying N value; high gain or low gain; read or non-read mode):

$$\begin{split} \omega_{n} &= [1.2 \ V_{CC} \ f_{o}/2R_{p}NC_{1})]^{0.5} \\ \text{Natural frequency Damping ratio} \\ \zeta &= \omega_{n} \ R_{1}C_{1}/2 \end{split}$$

# 3.1 2,7 CODE, 10 MBIT/SEC LOOP FILTERDESIGN EXAMPLE

#### Initial Requirements and Definitions