# 3.3 VOLT M13 MULTIPLEXER IDT82V8313

Version 3 June 3, 2004

2975 Stender Way, Santa Clara, California 95054 Telephone: (800) 345-7015 • • FAX: (408) 492-8674 Printed in U.S.A. © 2004 Integrated Device Technology, Inc.

| DISCLAIMER Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIFE SUPPORT POLICY Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.  1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. |

### **Table of Contents**

| FEATURES                                    | 1     |

|---------------------------------------------|-------|

| PACKAGE                                     | 2-4   |

| PIN DESCRIPTIONS                            | 5-12  |

| REGISTER MEMORY MAP                         | 13-16 |

| REGISTER DESCRIPTIONS                       | 17    |

| Master Reset/Lock Status                    |       |

| Revision/Global PMON Update                 | 17    |

| Master Bypass Configuration                 | 18    |

| Master HDLC Configuration                   | 19    |

| Master Loopback Configuration               | 20    |

| Master Interface Configuration              | 21    |

| Master Alarm Enable/Network Requirement Bit | 22    |

| Master Test                                 | 23    |

| Master Interrupt Source #1                  | 24    |

| Master Interrupt Source #2                  | 25    |

| Master Interrupt Source #3                  |       |

| DS3 Transmit Configuration                  |       |

| DS3 Transmit Diagnostic                     |       |

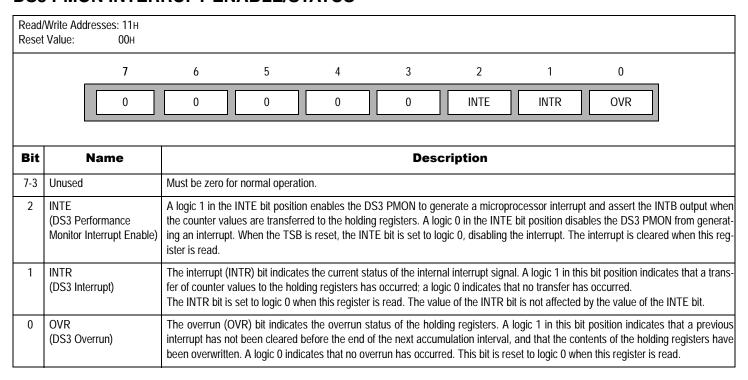

| DS3 PMON Interrupt Enable/Status            |       |

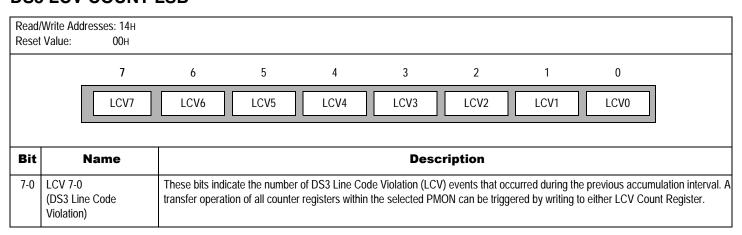

| DS3 LCV Count LSB                           |       |

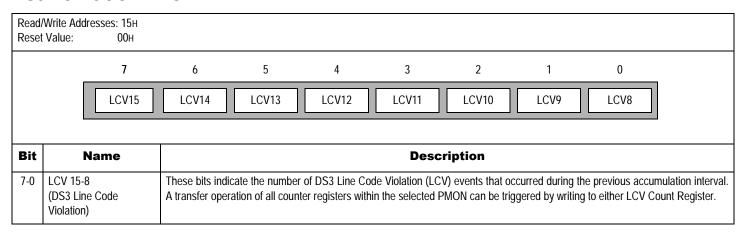

| DS3 LCV Count MSB                           |       |

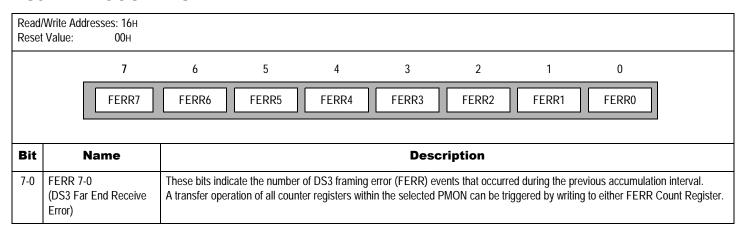

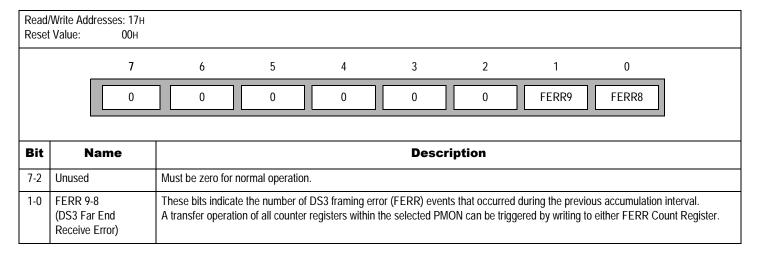

| DS3 FERR Count LSB                          |       |

| DS3 FERR Count MSB                          |       |

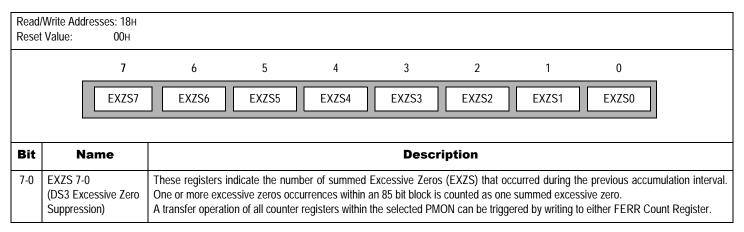

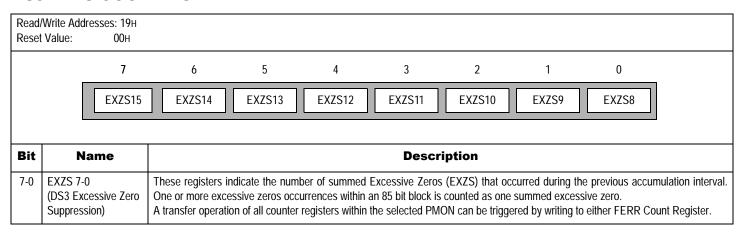

| DS3 EXZS Count LSB                          |       |

| DS3 EXZS Count MSB                          |       |

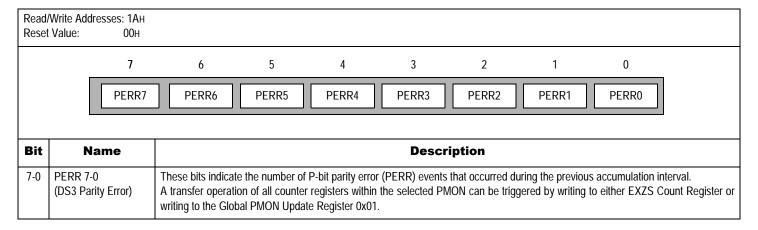

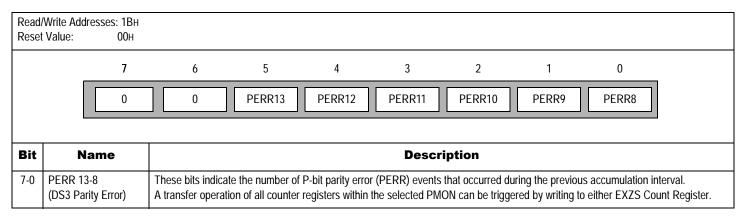

| DS3 PERR Count LSB                          |       |

| DS3 PERR Count MSB                          |       |

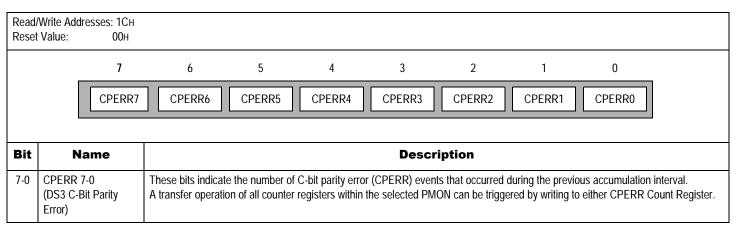

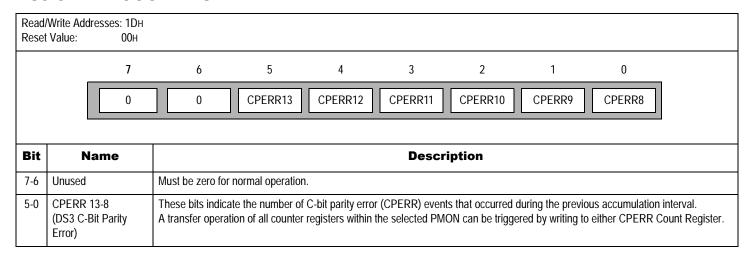

| DS3 CPERR Count LSB                         |       |

| DS3 CPERR Count MSB                         |       |

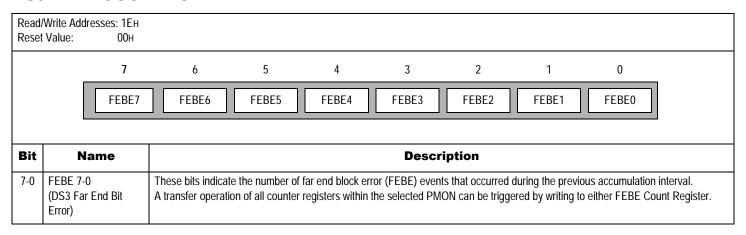

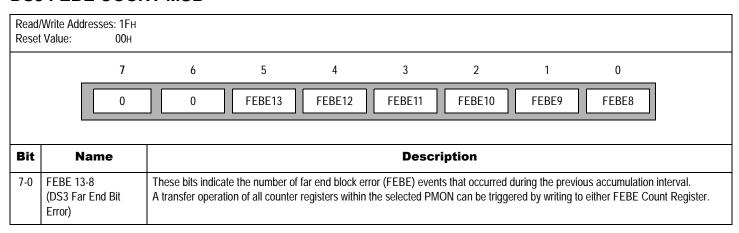

| DS3 FEBE Count LSB                          |       |

| DS3 FEBE Count MSB                          |       |

| XFDL Islammat States                        |       |

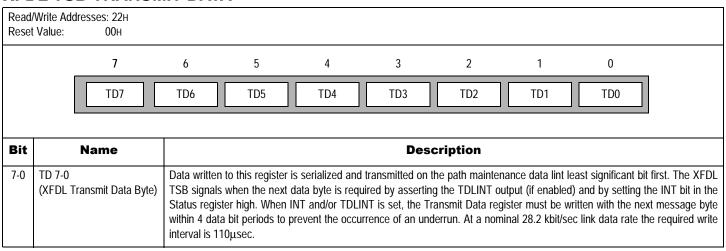

| XFDL TSD Tspromit Data                      |       |

| XFDL TSB Transmit Data                      | 34    |

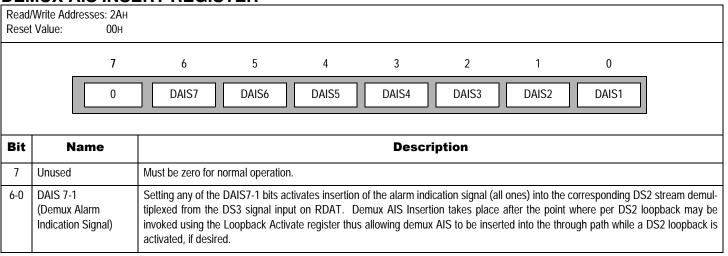

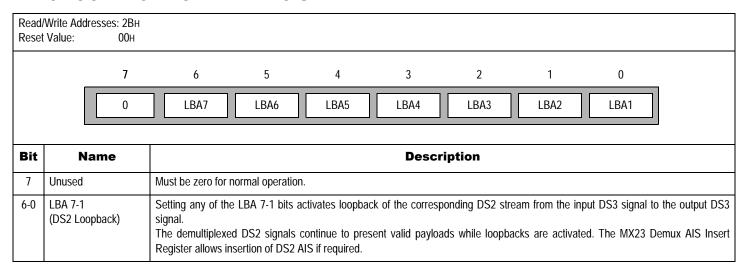

| N.D. 13D COMOUNTAINS                        |       |

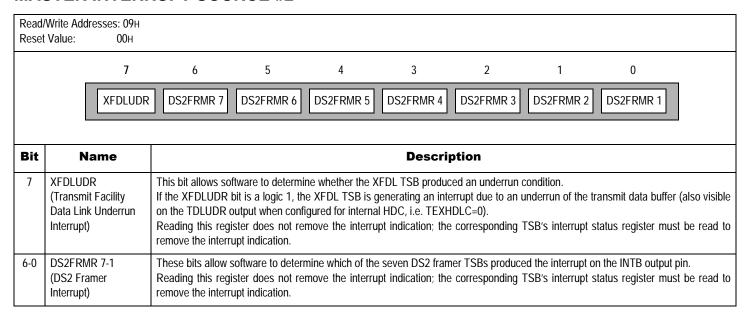

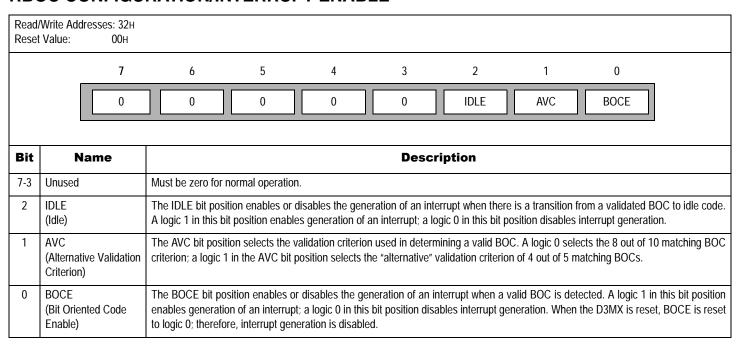

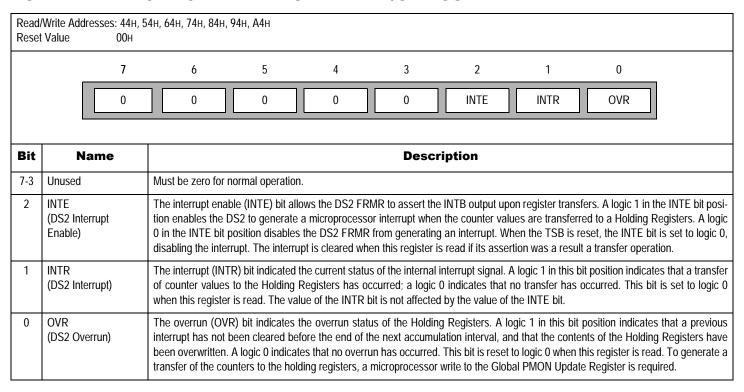

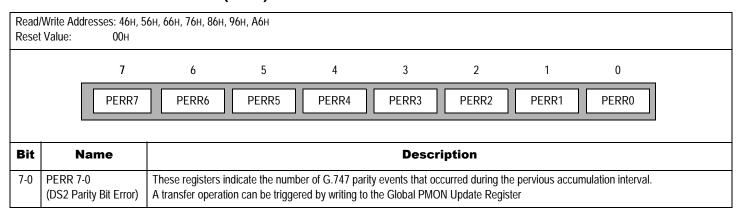

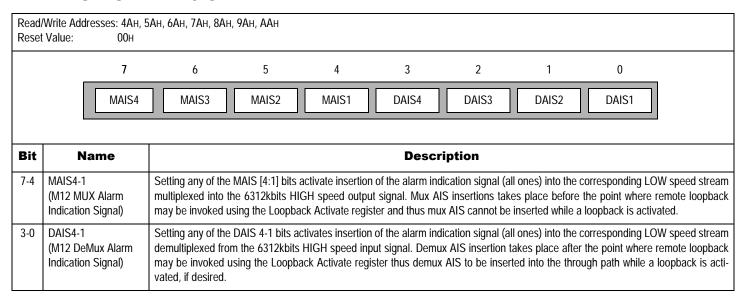

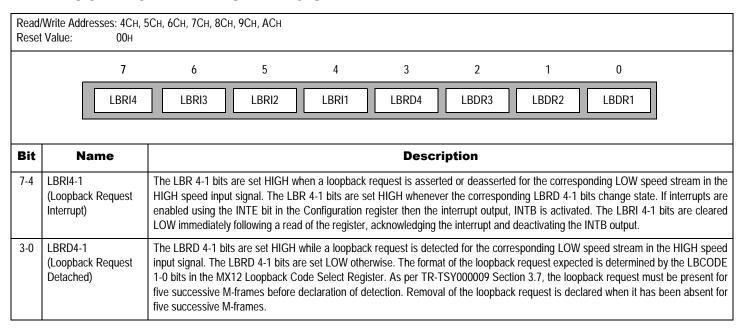

### **3.3 VOLT M13 MULTIPLEXER** IDT82V8313 RFDL TSB Receive Data 36 FEAC XBOC TSB Code.......41 RBOC Configuration/Interrupt Enable.......41 DS2 FRMR Interrupt Enable 49 DS2 Framer Interrupt Status 50 DS2 Framer Status 51 DS2 FRMR PERR Count (LSB) 53 FUNCTIONAL DESCRIPTION 59-78 FUNCTIONAL TIMING 93-94 LOOPBACK MODES 95-100

| AC ELECTRICAL CHARACTERISTICS                                              |     |

|----------------------------------------------------------------------------|-----|

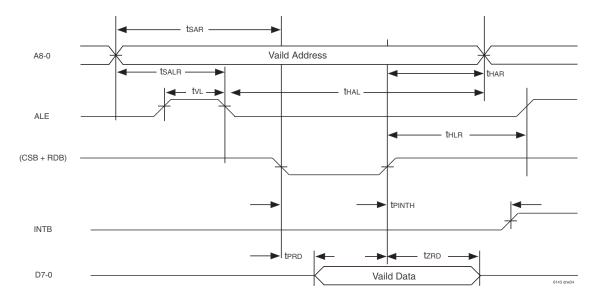

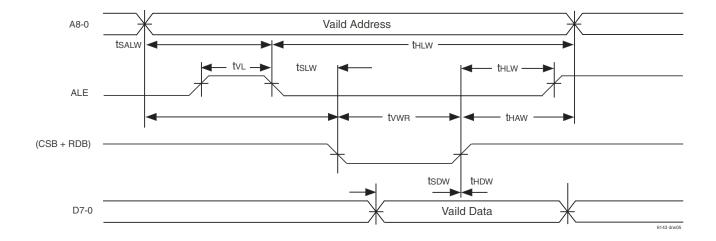

| Microprocesser Interface Timing Characteristics/Microprocessor Read Access | 103 |

| Microprocessor Write Access                                                |     |

| Timing Characteristics                                                     | 105 |

| Transmit DS3 Input                                                         | 106 |

| Transmit Overhead input                                                    | 106 |

| Transmit Tributary Input                                                   | 107 |

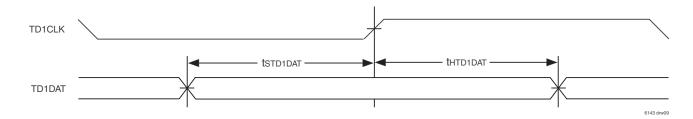

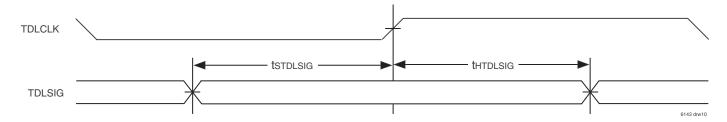

| Transmit Data Link Input                                                   | 107 |

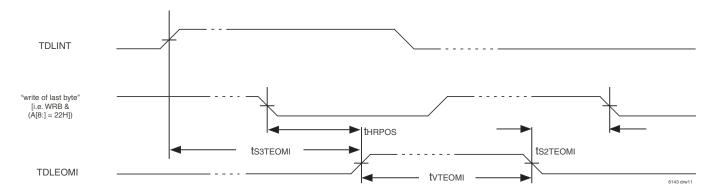

| Transmit Data Link EOM Input                                               | 108 |

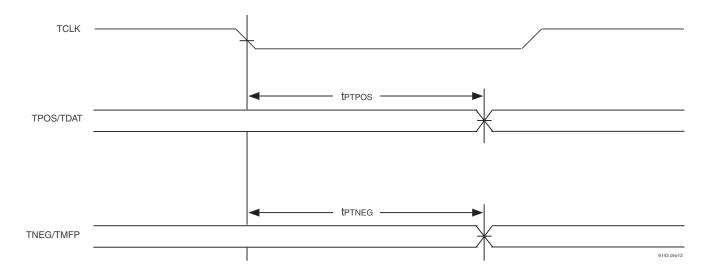

| Transmit DS3 Output                                                        | 109 |

| Receive DS3 Output                                                         | 110 |

| Receive Overhead Output                                                    | 111 |

| Transmit Overhead Output                                                   | 112 |

| Receive Tributary Output                                                   | 112 |

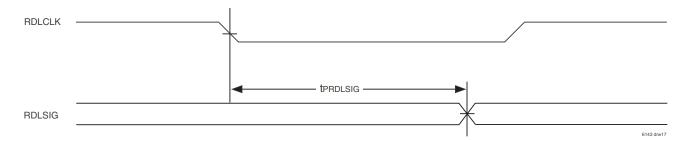

| Receive Data Link Output                                                   | 113 |

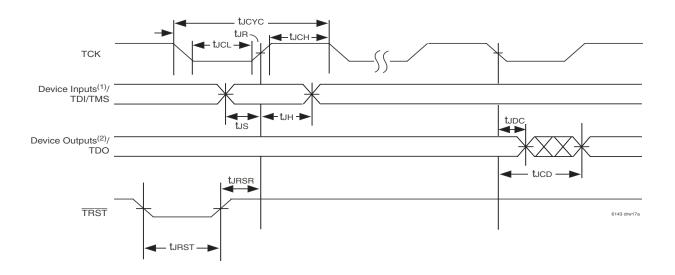

| JTAG                                                                       |     |

| JTAG Timing Solutionsl                                                     |     |

| JTAG AC Electrical Characteristics                                         |     |

| Identification Register Definitions                                        | 116 |

| Scan Register Sizes                                                        | 116 |

| System Interface Parameters                                                | 117 |

| JTAG Scan Order                                                            |     |

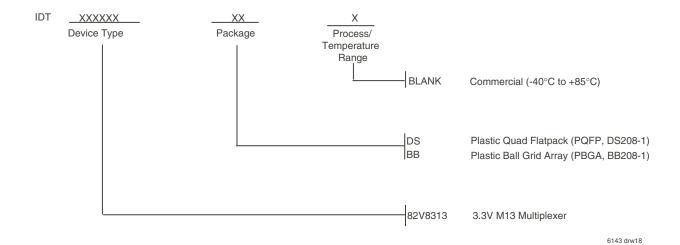

| ORDERING INFORMATION                                                       | 121 |

| GLOSSARY                                                                   |     |

| STANDARDS                                                                  |     |

| INDEX                                                                      |     |

### **List of Tables**

| Table 1 — Pin Descriptions                                    | 5-11  |

|---------------------------------------------------------------|-------|

| Table 2 — Register Memory Map                                 | 13-16 |

| Table 3 — FERF Status (X1 & X2 State)                         | 62    |

| Table 4 — C-Bit Parity Mode DS3 C-Bit Assignments             | 63    |

| Table 5 — DS3 FEAC Loopback Control Message                   | 65    |

| Table 6 — DS3 FEAC Alarm and Status Message                   |       |

| Table 7 — DS1 Bit Oriented Codes Command and Response Message | 67    |

| Table 8 — DS1 Bit Oriented Priority Message                   |       |

| Table 9 — DS1 Bit Oriented Codes Reserved Messages            | 67    |

| Table 10 — Data Link Format                                   | 68    |

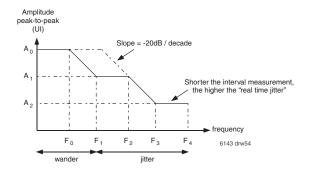

| Table 11 — Max Jitter Tolerance on DS if CAT II               | 70    |

## **List of Figures**

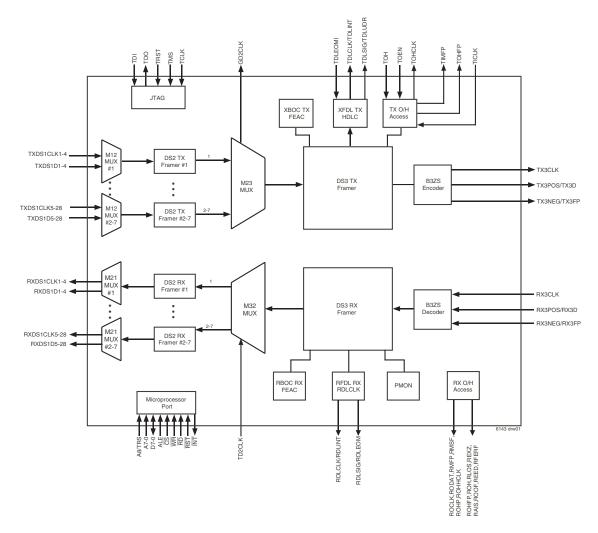

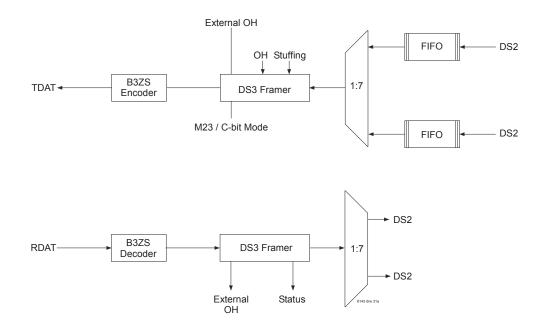

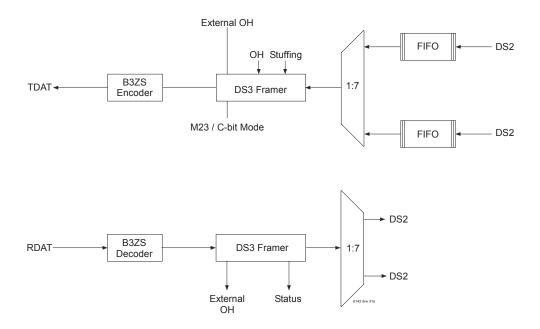

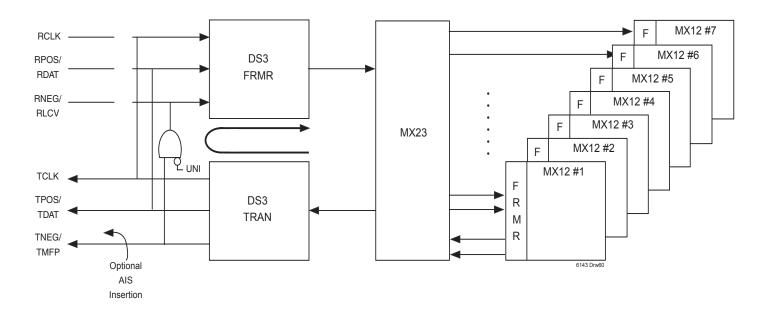

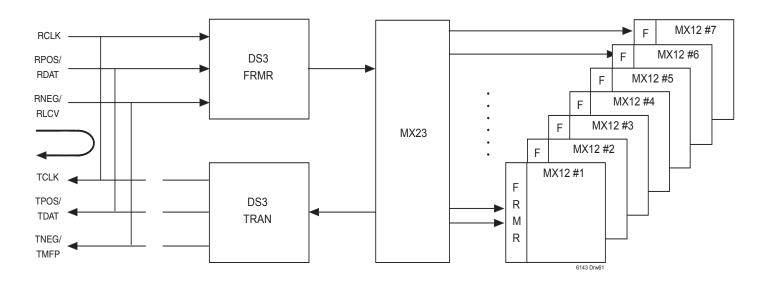

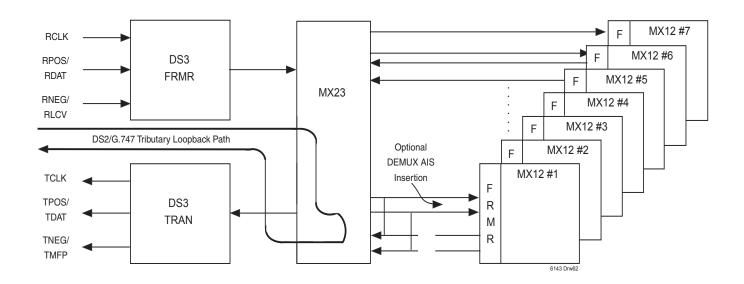

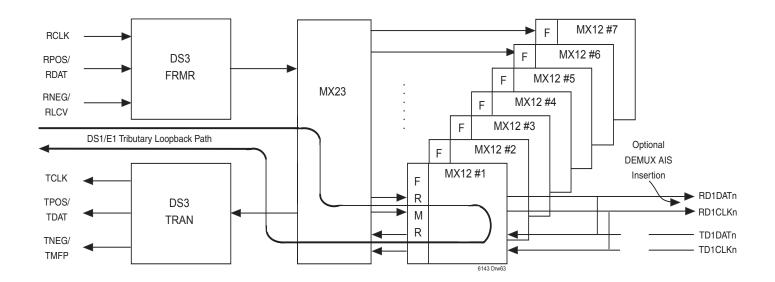

| Figure 1  | DS3 Framer Block                                 | 59  |

|-----------|--------------------------------------------------|-----|

| Figure 2  | DS3 Frame                                        | 59  |

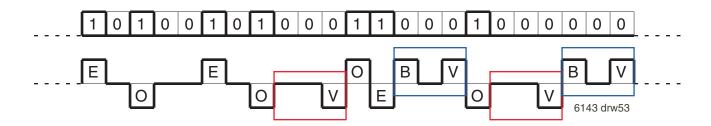

| Figure 3  | B3ZS Coding                                      | 60  |

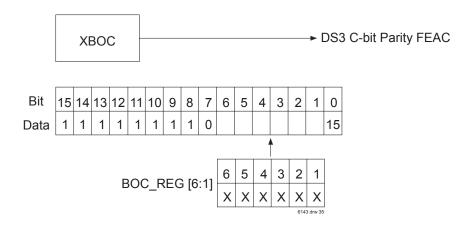

| Figure 4  | Transmit BOC                                     | 66  |

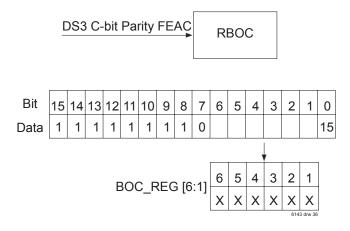

| Figure 5  | Receive BOC                                      | 66  |

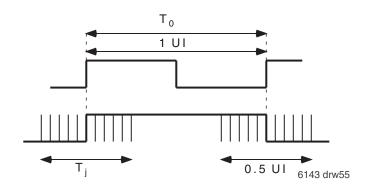

| Figure 6  | Jitter Definition                                | 69  |

| Figure 7  | Maximum Jitter Tolerance on DSn Interface Inputs | 70  |

| Figure 8  | M23 Multiplexer Block                            |     |

| Figure 9  | DS3 Stuff Block                                  | 72  |

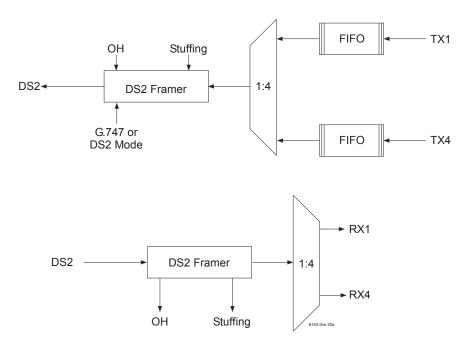

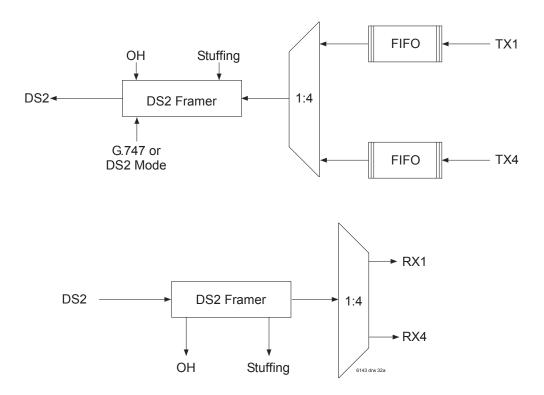

| Figure 10 | DS2 Framer Block                                 |     |

| Figure 11 | DS2 Frame                                        | 73  |

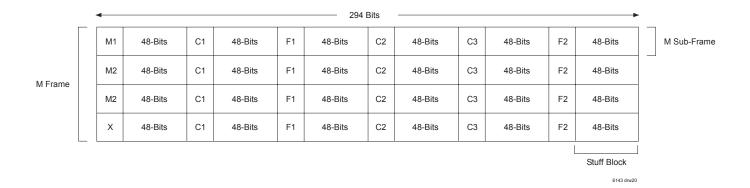

| Figure 12 | G.747 Frame Format                               | 74  |

| Figure 13 | M12 Block                                        | 77  |

| Figure 14 | DS2 Stuff Block                                  | 78  |

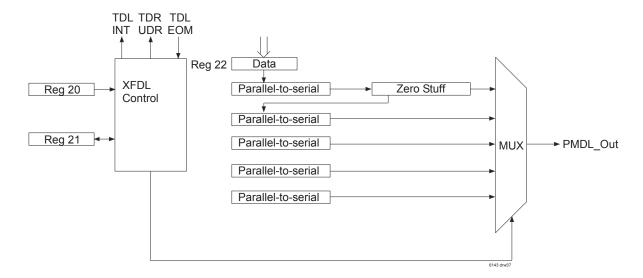

| Figure 15 | XFDL                                             | 79  |

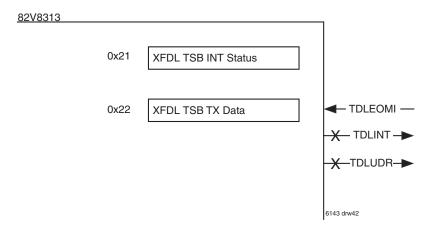

| Figure 16 | XFDL Polled Mode                                 | 80  |

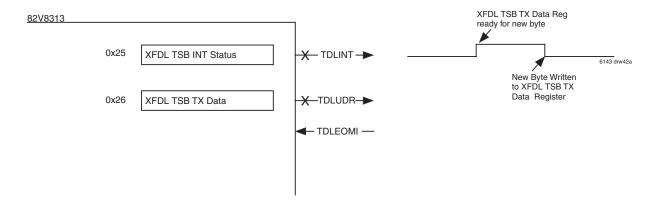

| Figure 17 | XFDL Interrupt Mode                              | 81  |

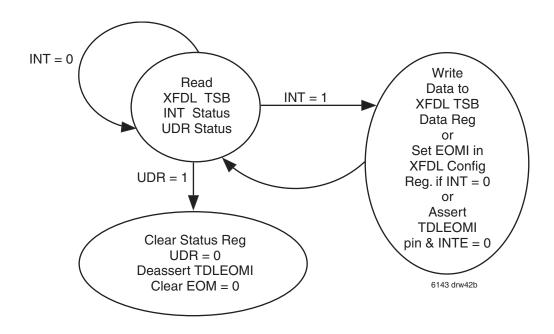

| Figure 18 | XFDL Interrupt Service Routine                   |     |

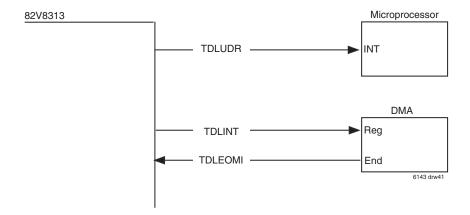

| Figure 19 | XFDL DMA Mode                                    |     |

| Figure 20 | XFDL Normal Data Sequence                        | 83  |

| Figure 21 | XFDL Underrun Sequence                           |     |

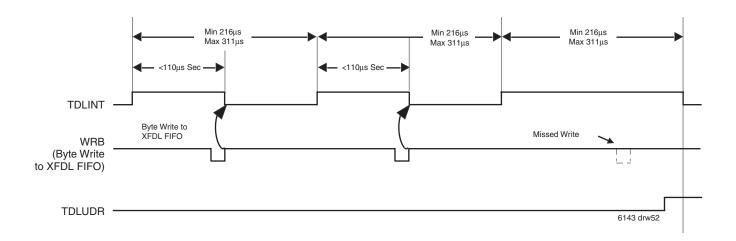

| Figure 22 | TDLINT Timing Normal Data TX                     | 85  |

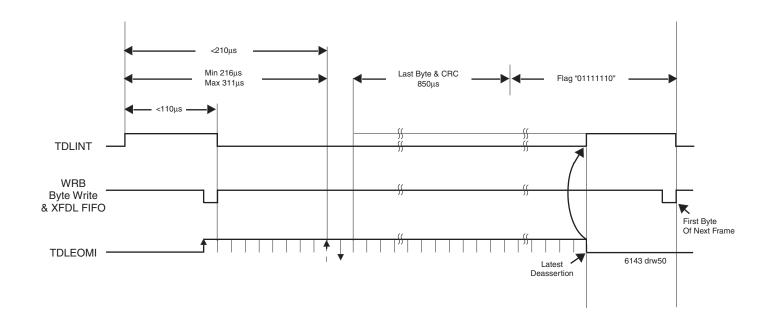

| Figure 23 | TDLEOMI Timing EOMI After CRC                    |     |

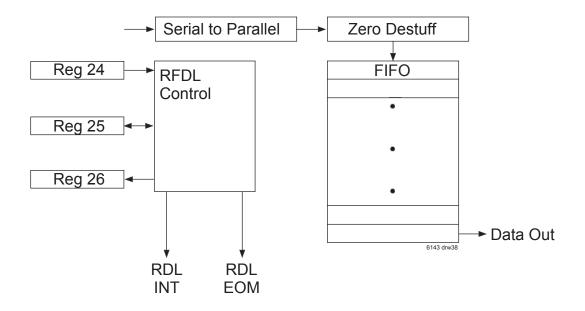

| Figure 24 | RFDL                                             |     |

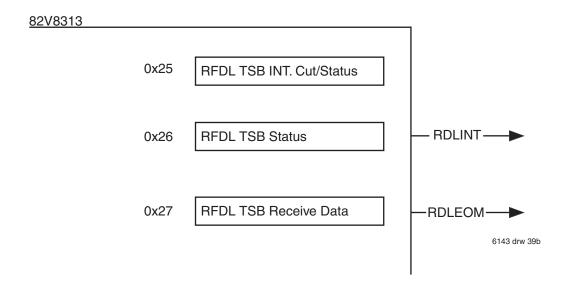

| Figure 25 | RFDL Polled Mode                                 | 88  |

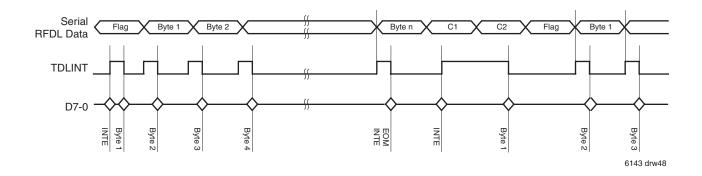

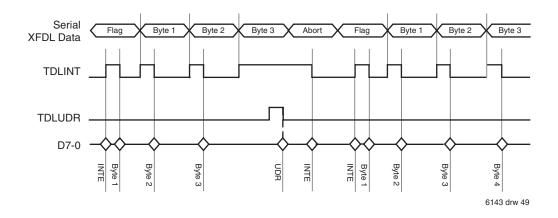

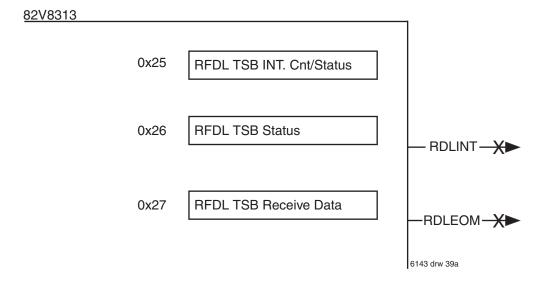

| Figure 26 | RFDL Interrupt Driven Mode                       | 89  |

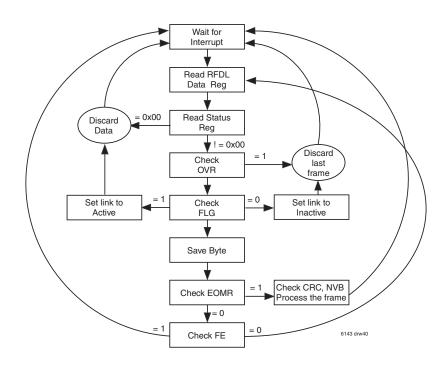

| Figure 27 | RFDL Interrupt Service Routine                   |     |

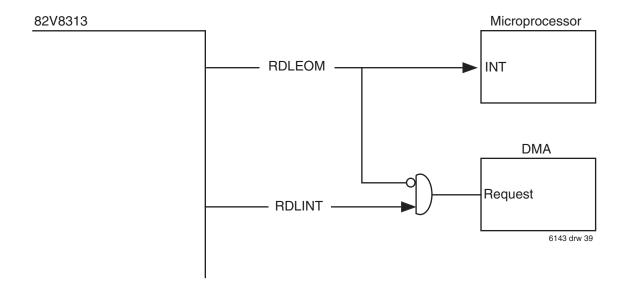

| Figure 28 | RFDL DMA Mode                                    |     |

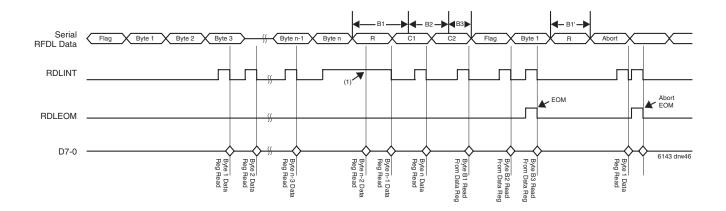

| Figure 29 | RFDL Normal Data And Abort Sequence              | 91  |

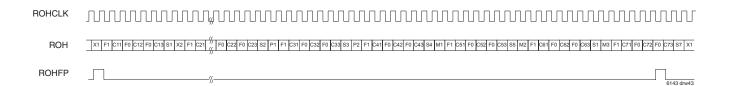

| Figure 30 | Receive DS3 OH Serial Stream                     |     |

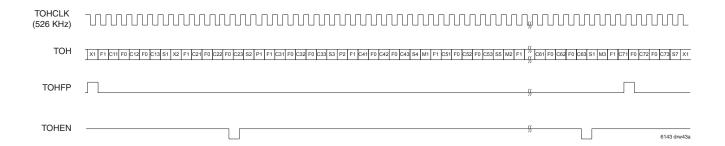

| Figure 31 | Transmit DS3 OH Serial Stream                    | 93  |

| Figure 32 | Functional Receive OH Timing Low-Speed           | 93  |

| Figure 33 | Functional Receive Timing PMON                   |     |

| Figure 34 | Functional Receive OH Timing High-Speed          |     |

| Figure 35 | DS3 Diagnostic Loopback                          |     |

| Figure 36 | DS3 Line Loopback                                |     |

| Figure 37 | DS2/G.747 Demultiplex Loopback                   |     |

| Figure 38 | DS1/E1 Demultiplex Loopback                      | 99  |

| Figure 39 | Microprocessor Read Access Timing                |     |

| Figure 40 | Microprocessor Write Access Timing               |     |

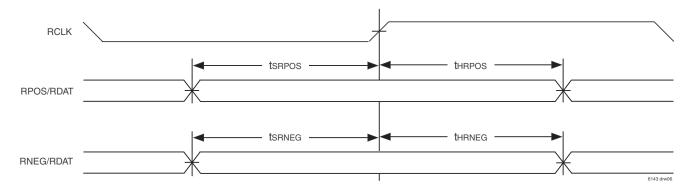

| Figure 41 | Receive DS3 Input Timing                         |     |

| Figure 42 | Transmit DS3 Input Timing                        |     |

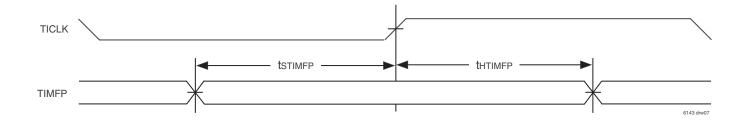

| Figure 43 | Transmit Overhead Input Timing                   |     |

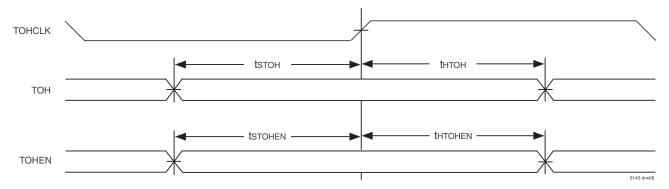

| Figure 44 | Transmit Tributary Input Timing                  |     |

| Figure 45 | Transmit Data Link Innut Timing                  | 107 |

#### IDT82V8313 **3.3 VOLT M13 MULTIPLEXER** Figure 46 Figure 47 Figure 48 Figure 49 Figure 50 Figure 51 Figure 52 Figure 53

### 3.3 VOLT M13 MULTIPLEXER

### **FEATURES:**

- Full featured single chip M13-ideal for upgrading existing multi-line T1/E1 line cards to single line channelized T3 service

- Small footprint 17mm x 17mm BGA package and 208 pin PQFP packages available

- ◆ 3.3V operation with 5V tolerant I/O

- 28 independent DS1 clock inputs each with programmable clock edge adapter

- 28 independent DS1 outputs eatch with programmable clock edge adapter

- M12 bypass for direct input of DS2 in to the M23 multiplexer

- Programmable clock edge

- Supports M23 or C-bit parity format formats

- G.747 formats for E1 to be multiplexed onto a DS3

- DS2 LOF detectors and DS2 AIS DS2 X-bit access

- ◆ DS2 transmit/receive X-bit control/status

- ◆ DS2 F, M, and X bit insertion

- ◆ DS2 FERF and AIS under microprocessor control

- Transmission of RAI and reserved bit under microprocessor control

- Programmable preemptive inversion of C-bits for remote loopback

- DS3 idle signal generators

- ◆ DS3 LOS, LOF, P-bit Parity, C-bit Parity, AIS and idle detectors

- DS3 X-bit access

- DS3 transmit and receive AIS generation and detection

- ◆ DS3 M-frame and M-subframe boundary indications

IDT an the IDT logo are registered trademarks of Integrated Device Technology, Inc.

DSC -6143/2

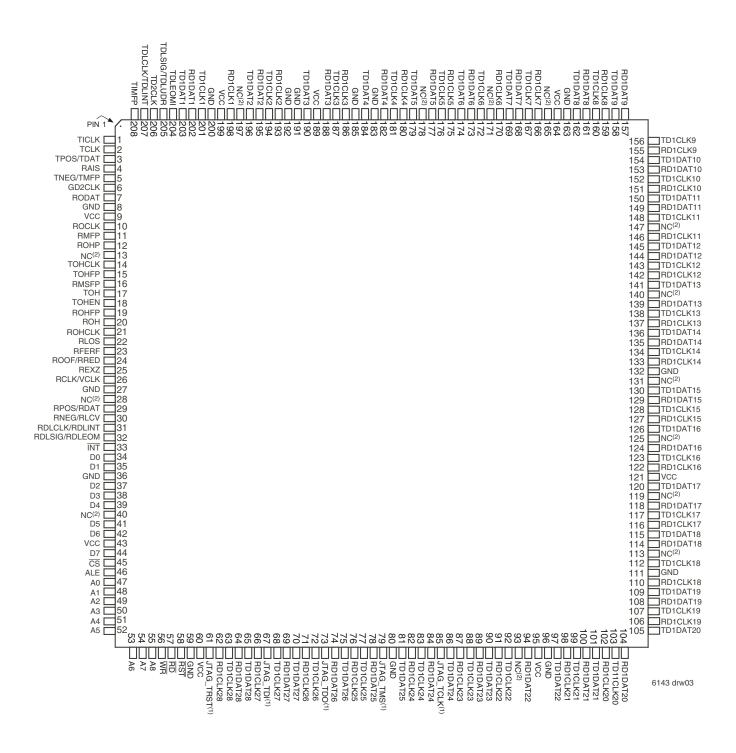

### **PACKAGE**

|   |                   | — A1           | BALL P                                   | AD COR                      | NER                   |                   |                     |                            |               |                            |                    |                  |                  |                   |                       |                            |

|---|-------------------|----------------|------------------------------------------|-----------------------------|-----------------------|-------------------|---------------------|----------------------------|---------------|----------------------------|--------------------|------------------|------------------|-------------------|-----------------------|----------------------------|

| Α | O<br>TCLK         | O<br>TD2CLK    | O<br>TD1<br>DAT1                         | RD1<br>DAT1                 | RD1<br>CLK1           | RD1<br>DAT2       | O<br>TD1<br>DAT3    | RD1<br>CLK3                | RD1<br>CLK4   | O<br>TD1<br>CLK5           | O<br>TD1<br>CLK6   | O<br>TD1<br>CLK7 | RD1<br>DAT8      | RD1<br>CLK8       | O<br>TD1<br>DAT9      | O<br>RD1<br>DAT9           |

| В | O<br>TPOS_<br>DAT | O<br>GD2CLK    | TIMEP                                    | TD1<br>CLK1                 | TD1<br>DAT2           | TD1<br>CLK2       | RD1<br>DAT3         | GND                        | TD1<br>CLK4   | RD1<br>DAT5                | RD1<br>DAT6        | RD1<br>DAT7      | TD1<br>DAT8      | TD1<br>CLK8       | RD1<br>CLK9           | TD1<br>CLK9                |

| С | TNEG_<br>MFP      | O              | RAIS                                     | TDLCLK                      | TDLSIG_<br>UDR        | RD1<br>CLK2       | TD1<br>CLK3         | O<br>TD1<br>DAT4           | RD1<br>DAT4   | TD1<br>DAT5                | TD1<br>DAT6        | TD1<br>DAT7      | RD1<br>CLK7      | TD1<br>CLK10      | RD1<br>DAT10          | TD1 DAT10                  |

| D | RODAT             | OROCLK         | O<br>RMFP                                | Ō                           | TDLEOMI               | 0                 | VCC                 | VCC                        | Vcc           | Vcc                        | RD1<br>CLK5        | RD1<br>CLK6      | TD1<br>CLK11     | RD1<br>DAT11      | TDI<br>DAT11          | RD1<br>CLK10               |

| E | ROHP              | O              | O                                        | RDLSIG<br>EOM               |                       |                   |                     |                            |               |                            | CLRS               | CLNO             | TD1<br>CLK12     | RD1<br>DAT12      | TD1 DAT12             | O<br>RD1                   |

| F | RMSFP             | ТОН            | O                                        | ROHFP                       |                       |                   |                     |                            |               |                            |                    |                  | TD1<br>CLK13     | RD1<br>DAT13      | O<br>TD1              | CLK11<br>O<br>RD1          |

| G | ROH               | OROHCLK        | RLOS                                     | Vcc                         |                       |                   | GND                 | O<br>GND                   | GND           | O<br>GND                   |                    |                  | VCC              | RD1<br>DAT14      | DAT13 O TD1 DAT14     | CLK12<br>O<br>RD1<br>CLK13 |

| н | RCLK              | ROOF_<br>RED   | O<br>RFERF                               | Vcc                         |                       |                   | O<br>GND            | O<br>GND                   | O<br>GND      | O<br>GND                   |                    |                  | Vcc              | TD1 DAT5          | RD1<br>CLK14          | TD1<br>CLK14               |

| J | RNEG_<br>LCV      | RPOS_<br>DAT   | O<br>REXZ                                | Vcc                         |                       |                   | GND                 | GND                        | O<br>GND      | O<br>GND                   |                    |                  | VCC              | RD1<br>DAT15      | TD1<br>CLK15          | RD1<br>CLK15               |

| К | O<br>D1           | O<br>D0        | $\displaystyle \bigcup_{\overline{INT}}$ | O                           |                       |                   | O<br>GND            | O<br>GND                   | GND           | GND                        |                    |                  | Vcc              | TD1<br>DAT16      | RD1<br>DAT16          | TD1<br>CLK16               |

| L | O<br>D5           | O<br>D4        | O<br>D3                                  | O<br>D2                     |                       |                   |                     |                            |               |                            |                    |                  | RD1<br>CLK16     | TD1 DAT17         | RD1<br>DAT17          | TD1<br>CLK17               |

| М | ALE               | $\frac{O}{CS}$ | O<br>D7                                  | O<br>D6                     |                       |                   |                     |                            |               |                            |                    |                  | RD1<br>CLK17     | TD1 DAT18         | RD1<br>DAT18          | TD1<br>CLK18               |

| N | O<br>A2           | O<br>A1        | O<br>A0                                  | RD1<br>DAT28                | O<br>TD1<br>CLK27     | O                 | Vcc                 | Vcc                        | Vcc           | Vcc                        | Vcc                | TD1<br>CLK23     | TD1<br>CLK22     | RD1<br>CLK18      | TD1 DAT19             | RD1<br>DAT19               |

| Р | O<br>A4           | O<br>A3        | O<br>EX_RST                              | TD1<br>CLK28                | JTAG_<br>TDI          | RD1<br>CLK26      | RD1<br>DAT26        | TD1<br>CLK25               | RD1<br>DAT25  | RD1<br>CLK24               | O<br>JTAG_<br>TCLK | RD1<br>DAT23     | RD1<br>DAT22     | TD1<br>CLK21      | TD1<br>CLK19          | RD1<br>CLK19               |

| R | O<br>A5           | O<br>A8        | $\bigcap_{\overline{RD}}$                | O<br>RD1                    | O<br>RD1              | O<br>TD1          | O<br>JTAG_          | O<br>RD1                   | O<br>JTAG_    | O<br>TD1                   | O<br>TD1           | O<br>TD1         | O<br>TD1         | O<br>RD1          | O<br>RD1              | O<br>TD1                   |

| т | O<br>A6           | O<br>A7        | $\displaystyle \bigcup_{\overline{WR}}$  | CLK28<br>O<br>JTAG_<br>TRST | CLK27<br>TD1<br>DAT28 | DAT27  RD1  DAT27 | TDO<br>TD1<br>CLK26 | CLK25<br>O<br>TD1<br>DAT26 | TMS TD1 DAT25 | CLK24<br>O<br>RD1<br>DAT24 | DAT24 O RD1 CLK23  | DAT23  RD1 CLK22 | DAT22  RD1 CLK21 | DAT21 O TD1 DAT21 | CLK20<br>TD1<br>CLK20 | DAT20<br>O<br>RD1<br>DAT20 |

|   | 1                 | 2              | 3                                        | 4                           | 5                     | 6                 | 7                   | 8                          | 9             | 10                         | 11                 | 12               | 13               | 14                | 15                    | 16                         |

6143 drw02

PBGA: 1mm pitch, 17mm x 17mm (BB208-1, order code: BB)

TOP VIEW

NOTE: 1. JTAG 2. NC = No Connect

PQFP: 0.50mm pitch, 28mm x 28mm (DS208-1, order code: DS)

TOP VIEW

PACKAGE 3 June 3, 2004

### **PIN DESCRIPTIONS**

| SYMBOL    | NAME                                                         | I/O | TQFP<br>PIN NO. | BGA<br>Pin No. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------------------|-----|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

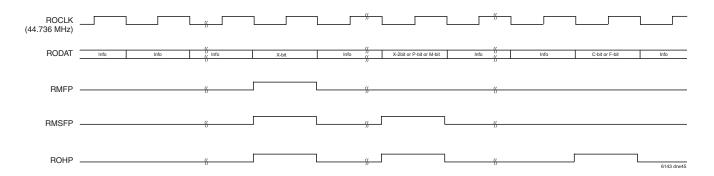

| RCLK      | Receive Clock                                                | I   | 26              | H1             | This is the DS3 receive clock input. RCLK is nominally a 44.736 MHz, 50% duty cycle clock.                                                                                                                                                                                                                                                                                                                                                     |

| RPOS/RDAT | Receive Positive<br>Pulse/Receive<br>Data                    | I   | 29              | J2             | In dual rail mode, this pin is RPOS and represents the positive pulses of a B3ZS-encoded signal. In single rail mode, this pin is RDAT and represents the unipolar DS3 input data. The M13 can be configured to sample data on either the rising or falling edge of RCLK.                                                                                                                                                                      |

| RNEG/RLCV | Receive<br>Negative Pulse/<br>Receive Line<br>Code Violation | I   | 30              | J1             | In dual rail mode, this pin is RNEG and represents the negative pulses of a B3ZS-encoded signal. In single rail mode, this pin is RLCV and can be used to insert line code violations on the DS3 input. The M13 can be configured to sample data on either the rising or falling edge of RCLK.                                                                                                                                                 |

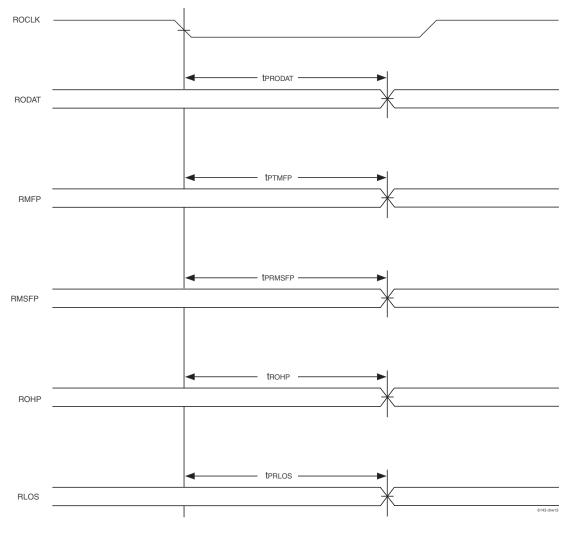

| ROCLK     | Receive Output<br>Clock                                      | 0   | 10              | D2             | The DS3 receive output clock is a buffered version of the input RCLK. Like the RCLK, this is nominally a 44.736 MHz, 50% duty cycle clock. REXZ, RLOS, RMFP, RMSFP, and RODAT are updated on the falling edge of ROCLK.                                                                                                                                                                                                                        |

| RODAT     | Receive Output<br>Data                                       | 0   | 7               | D1             | This is a 44.736 Mb/s DS3 NRZ receive data stream decoded from the B3ZS line signal. RODAT is aligned to the frame alignment signals RMFP, RMSFP, and ROHP. RODAT is updated in the falling edge of ROCLK.                                                                                                                                                                                                                                     |

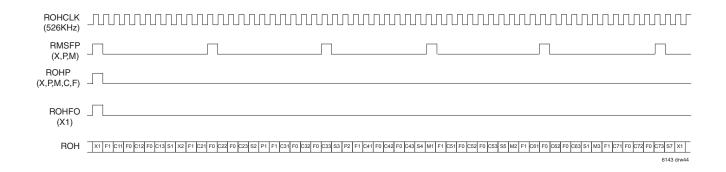

| RMFP      | Receive M-<br>Frame Pulse                                    | 0   | 11              | D3             | The receive M-frame pulse signal and marks the first bit in the M-frame (X1) of the DS3 data on RODAT. In an OOF (Out Of Frame) condition the M13 internal counters will maintain the old M-frame alignment position. When the framer regains frame alignment the RMFP timing will be updated to the new timing. This may result in a change of frame alignment. RMFP is updated on the falling edge of ROCLK.                                 |

| RMSFP     | Receive M-<br>subframe Frame<br>Pulse                        | 0   | 16              | F1             | The receive M-subframe pulse signal and marks the first bit of each M-subframe (X, P, and M) in each M-subframe of the DS3 on RODAT. In an OOF (Out Of Frame) condition the M13 internal counters will maintain the old M-frame alignment position. When the framer regains frame alignment the RMSFP timing will be updated to the new timing. This may result in a change of frame alignment. RMSFP is updated on the falling edge of ROCLK. |

| ROHP      | Receive<br>Overhead Pulse                                    | 0   | 12              | E1             | The receive overhead pulse signal and marks the overhead bit positions (X, P, M, C, and F) in the DS3 data on RODAT. In an OOF (Out Of Frame) condition the M13 internal counters will maintain the old frame alignment position. When the framer regains frame alignment, the ROHP timing will be updated to the new timing. This may result in a change of frame alignment. ROHP is updated in the falling edge of ROCLK.                    |

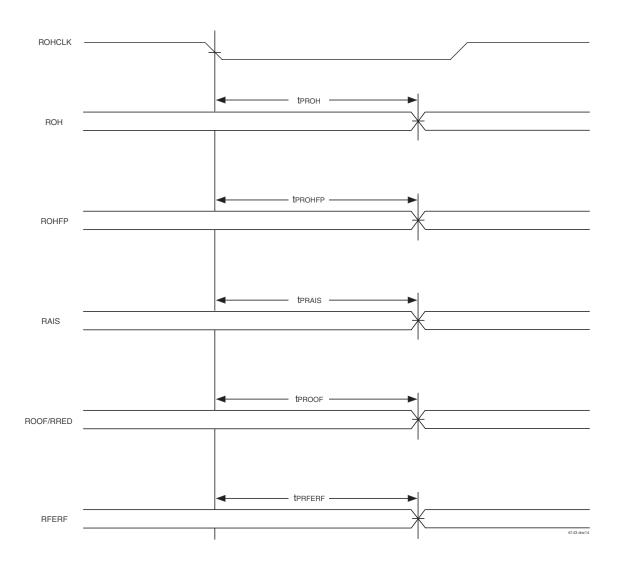

| ROHCLK    | Receive<br>Overhead Clock                                    | 0   | 21              | G2             | The receive overhead clock and transitions on each overhead bit. ROHCLK is nominally a 526 KHz. RAIS, RFERF, RFERR, RIDL, ROH, ROHFP, and ROOF are updated on the falling edge of ROHCLK.                                                                                                                                                                                                                                                      |

| ROH       | Receive<br>Overhead Data                                     | 0   | 20              | G1             | The receive overhead data signal transmits the overhead bits, C, F, M, P, and X bits from the receive DS3 stream. ROH is updated on the falling edge of ROHCLK.                                                                                                                                                                                                                                                                                |

| ROHFP     | Receive<br>Overhead<br>Frame Pulse                           | 0   | 19              | F4             | The receive overhead frame pulse is used to mark the positions of the overhead bits within the overhead stream, ROH. ROHFP will remain high during the X1 overhead bit. ROHFP is updated on the falling edge of ROHCLK.                                                                                                                                                                                                                        |

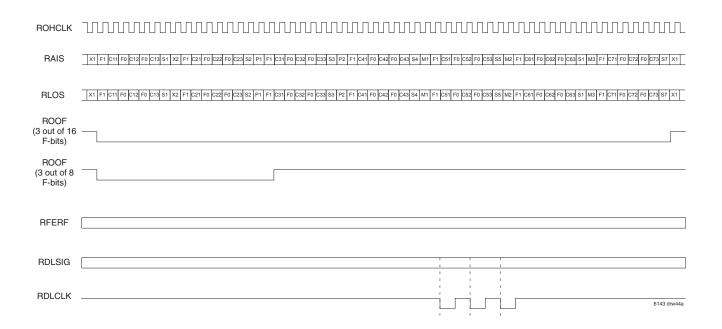

| RLOS      | Receive Loss of<br>Signal                                    | 0   | 22              | G3             | The receive loss of signal will remain high when the dual rail NRZ format stream is selected or when a loss of signal condition is detected (175 successive zeros on RPOS and RNEG). When the one's density is greater than 33% for 175 +/i 1 bit period on the RPOS and RNEG inputs, RLOS will be set low. RLOS is updated on the falling edge of ROCLK.                                                                                      |

| SYMBOL            | NAME                                                          | I/O | TQFP<br>PIN NO. | BGA<br>Pin No. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------------------------|-----|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REXZ              | Receive<br>Excessive Zeros                                    | 0   | 25              | J3             | The receive excessive zero indicates the detection of an excessive zero condition. When 3 or more successive zeros are received on the DS3 bipolar stream REXZ pulses high for one ROCLK cycle. In the uni-polar mode, REXZ is low. REXZ is updated on the falling edge of ROCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RAIS              | Receive Alarm<br>Indication Signal                            | 0   | 4               | C3             | The receive alarm indication signal is used to indicate and AIS (alarm indication) in the received DS3 signal. The RAIS will be set high when the AIS pattern has been detected for 2.23 ms or 13.5 ms as programmed by software. When the AIS pattern is absent in the DS3 signal for 2.23 ms or 13.5 ms the RAIS will be set low. RAIS is updated on the falling edge of ROHCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ROOF/RRED         | Receive Out of<br>Frame/Receive<br>Red Alarm                  | 0   | 24              | H2             | ROOF/RREF will be ROOF when the REDO bit in the Master Alarm Enable register is 0 and will indicate an receive out-of-frame error. When no out-of-frame errors exist the ROOF will be low. ROOF will be high when there is an out-of-frame condition: 3 out of 16 (default) or 3 out of 8 consecutive F-bit errors are detected, or when more M-bit errors are detected in 3 out of 4 consecutive M-frames. ROOF is updated on the falling edge of ROHCLK. ROOF/RRED will be RRED when the REDO bit the Master Alarm Enable register is 1 and will indicate an out-of-frame condition or a DS3 loss of signal condition. A DS3 out-of-frame condition is considered when there are no transitions for 2.23 ms or 13.5 ms (software programmable) and RRED will be set high. RRED will be reset low when the out-of-frame condition or loss of signal condition are absent for 2.23 or 13.5 ms. RRED is updated on the falling edge of ROHCLK.                                                                                                                                                                                                                                                                                                                                                                                    |

| RFERF             | Receive Far End<br>Receive Failure                            | 0   | 23              | НЗ             | The receive far end receive failure reflects the internal state of the internal FERF but the RFERF state is delayed by two M-frames. FERF is set high when both X1 and X2 are 0 in the M-frame. When X1 and X2 are both high in the M-frame, FERF is set low. Otherwise, FERF remains in its previous state when X1 • X2 in the current frame. The RFERF latency is used to provide better than 99.99% chance of freezing (holding FERF in its previous state) upon a valid state value during an out-of-frame. RFERF is updated every M-frame on the falling edge on ROHCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RDLCLK/<br>RDLINT | Receive Data<br>Link Clock/<br>Receive Data<br>Link Interrupt | 0   | 31              | D4             | RDLCLK/RDLINT will be RDLCLK when the REXHDLC bit in the Master HDLC Configuration Register is set to 1 and is used as the receive data link clock when an external HDLC receiver is selected. The RDLCLK is the clock for the external processing of the data link signal extracted by the DS3 framer. RDLCLK is nominally a 28.2 kHz clock that is low for at least 1.9us per cycle and is updated 3 times per M-frame. RDLCLK is updated on the falling edge of the ROHCLK. RDLCLK/RDLINT will be RDLINT when the REXHDLC bit in the Master HDLC Configuration Register is set to 0 and is used as the data link interrupt when an internal HDLC receiver is selected. When an HDLC receiver event occurs the RDLINT will reflect a change in status. By reading the Interrupt Enable/Status register, the interrupt will be cleared, both the register and the RDLINT pin. RDLINT is updated on the falling edge of ROHCLK. RDLINT is a configurable active low open-drain out or active high open-drain output. In the case where an external DMA device is used, RDLINT would be directly connected, however if the interrupt is being handled by a microprocessor, the RFDL may be wired-ORed with the $\overline{\text{INT}}$ output. In this later case, RDLINT should be configured as a active-low open drain output. |

| SYMBOL            | NAME                                                                   | I/O | TQFP<br>PIN NO.                          | BGA<br>Pin No.                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|------------------------------------------------------------------------|-----|------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDLSIG/<br>RDLEOM | Receive Data<br>Link Signal/<br>Receive Data<br>Link End Of<br>Message | 0   | 32                                       | E4                                      | RDLSIG/RDLEOM will be RDLSIG when the REXHDLC bit in the Master HDLC Configuration Register is set to 1 and is used as the receive data link signal when an external HDLC receiver is selected. The RDLSIG is the C-bit message used in C-bit parity mode and transmits the three C-bits from the fifth M-subframe in the DS3 frame. RDLSIG is updated on the falling edge of the RDLCLK. RDLSIG/RDLEOM will be RDLEOM when the REXHDLC bit in the Master HDLC Configuration Register is set to 0 and is used as the receive end of message signal when an internal HDLC receiver is selected. RDLEOM is used to denote the last byte of a sequence that is read from the HDLC receiver or to denote an overflow condition in the receive HDLC buffer. RDLEOM is updated on the falling edge of ROHCLK. In order to clear/deassert the RDLEOM the supervising microprocessor must read the Interrupt Enable/Status Register. In the case where RDLEOM would be connected to a supervising microprocessor, an external DMA is used. The RDLEOM would be programmed to be active-low, open-drain and wired-ORed with the $\overline{\text{INT}}$ to signal the microprocessor that the a complete message is ready. |

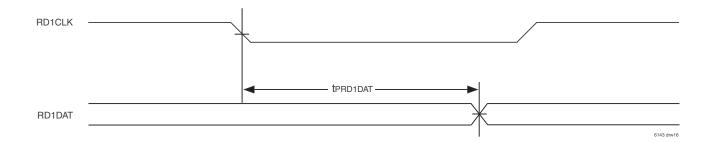

| RD1CLK1-28        | Receive DS1<br>Clock                                                   | 0   | *See TQFP<br>table below<br>for details. | *See BGA<br>table below<br>for details, | RD1CLK1-28 are the receive DS1 clocks used in conjunction with the RD1DAT. These clocks are at the T1 nominal rate of 1.544MHz, but will have jitter due to the demultiplexing and destuffing processes. RD1DAT28-1 can be programmed to update on either the rising or falling edge of RD1CLK. For G.747, the internal M12 multiplexers still uses the RD1CLKs to clock RD1DAT out, however every fourth clock, RD1CLK4, 8, 12, 16, 20, 24, and 28 clocks, is unused and in turn output LOW. These clocks run at the nominal rate of 2.048MHz but will have jitter due to the demultiplexing and destuffing processes. If a DS2 is inserted into the M13, thereby bypassing the M12 multiplexer, every fourth clock RD1CLK4, 8, 12, 16, 20, 24, and 28 can be used as a DS2 clock. In this case the unused clocks for that group will output LOW. The DS2 clock has a nominal rate of 6.312MHz.                                                                                                                                                                                                                                                                                                                  |

| RD1DAT1-28        | Receive DS1<br>Data                                                    | 0   | *See TQFP<br>table below<br>for details. | *See BGA<br>table below<br>for details  | RD1DAT1-28 is the DS1 data demultiplexed from the incoming DS3 stream. RD1DAT1-28 are updated on either the rising or falling edge of the corresponding RD1CLK1-28. In G.747, where the M12 multiplexers mux E1 data, RD1DAT 4, 8, 12, 16, 20, 24, and 28 are held low, while the remaining streams operate at a nominal 2.048MHz data rate. M12 multiplexers are bypassed and DS2 data is output the fourth stream of the group is used to output data. The remaining three streams of the group will be held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TD1CLK1-28        | Transmit DS1<br>Clock                                                  | I   | *See TQFP<br>table below<br>for details. | *See BGA<br>table below<br>for deatils  | The transmit DS1 clock, TD1CLK1-28 is used to sample incoming data on TD1DAT1-28 to be multiplexed into a DS3. The M13 expects a nominal 1.544MHz clocks and expects minimal jitter and wander of a standard DS1. TD1DAT1-28 are sampled on either the rising or falling edge of TD1CLK1-28. In G.747 multiplexing not all TD1 inputs are used. In this case, every fourth input (TD1CLK4, 8, 12, 16, 20, 24, and 28) is unused, ignored and must be tied to GND. The remaining clocks should be running at a nominal rate of 2.048MHz and expects minimal jitter and wander of a standard DS1. When the internal M12 multiplexers are bypassed, the M13 device will use every fourth clock (TD1CLK4, 8, 12, 16, 20, 24, and 28) as the DS2 input clock. In this case, the remaining clocks are unused, ignored and the unused inputs must be tied to GND.                                                                                                                                                                                                                                                                                                                                                        |

| TD1DAT1-28        | Transmit DS1<br>Data                                                   | I   | *See TQFP<br>table below<br>for details. | *See BGA<br>table below<br>fo details   | The transmit DS1 data TD1DAT is the input data that is multiplexed in to a DS3. Input data can be programmed to sample on either the rising or falling edges of TD1CLK1-28. In G.747, where the M12 multiplexers mux E1 data, every fourth data stream (TD1DAT4, 8, 12, 16, 20, 24, and 28) is ignored and must be tied to GND. In cases where a DS2 is inserted directly into the M23 stage, every fourth TD1DAT (TD1DAT4, 8, 12, 16, 20, 24, and 28) can be used. In this case the remaining TD1DAT streams of the group are ignored and must be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYMBOL            | NAME                                                            | I/O | TQFP<br>PIN NO. | BGA<br>Pin No. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------|-----|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GD2CLK            | Generated DS2<br>Clock                                          | 0   | 6               | B2             | In M13 and C-bit parity modes, this is the transmit generated DS2 clock. In M13 operation this clock is nominally a 6.311993 MHz clock which translates to a 39.1% stuffing ratio. In C-bit parity mode this clock is nominally a 6.3062723 MHz clock, which translates to a stuffing rate of 100% (used for C-bit parity). The GD2CLK may be tied directly to the TD2CLK clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TD2CLK            | Transmit DS2<br>Clock                                           | I   | 206             | A2             | The TD2CLK is the transmit DS2 clock and is the clock used in the M12 multiplexer. TD2CLK is nominally a 6.312 MHz, 50% duty cycle clock and can be derived from the GD2CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TDLSIG/<br>TDLUDR | Transmit Data<br>Link Signal/<br>Transmit Data<br>Underrun      | 0   | 205             | C5             | The TDLSIG/TDLUDR will be transmit data link, TDLSIG, when the TEXHDLC bit in the Master HDLC Configuration Register is a logic 1. When an external HDLC receiver is selected, TDLSIG will carry the the three C-bits in M-subframe #5 in the DS3. When C-bit parity mode is not enabled TDLSIG is ignored. TDLSIG is sampled on the rising edge of TDLCLK.The TDLSIG/TDLUDR will be the transmit data link underrun, TDLUDR, when the TEXHDLC bit in the Master HDLC Configuration Register is a logic 0. When an internal HDLC receiver is selected, TDLUDR is asserted when an internal HDLC transmitter underruns. TDLUDR can be cleared (deasserted) by writing to the XFDL Interrupt Status Register. TDLUDR is a programmable polarity, open-drain output. On reset, TDLSIG/TDLUDR is TDLSIG. The TEXHDLC register should be programmed after reset to the appropriate mode. When an external DMA is used, TDLUDR will be configured as an active-low output and wired-ORed with the $\overline{\text{INT}}$ output and routed to the supervising microprocessor. In that way, in the case of a transmit buffer underrun the supervising microprocessor will be notified.                                                                                                                                                                                                    |

| TDLCLK/<br>TDLINT | Transmit Data<br>Link Clock/<br>Transmit Data<br>Link Interrupt | 0   | 207             | C4             | The TDLCLK/TDLINT will be transmit data link clock, TDLCLK, when the TEXHDLC bit in the Master HDLC Configuration Register is a logic 1. When an external HDLC receiver is selected, TDLCLK will provide the timing for the external maintenance data link inserted by the DS3. TDLCLK is nominally a 28.2 KHz clock which is low for at least 1.9us per cycle. TDLCLK is updated on the falling edge of the TOHCLK and cycles three times per M-frame (one for each C-bit). The TDLCLK/TDLINT will be the transmit data link interrupt, TDLINT, when the TEXHDLC bit in the Master HDLC Configuration Register is a logic 0. When an internal HDLC receiver is selected, TDLINT is asserted when the last data byte is written to the internal HDLC transmitter. A write to the XFDL Configuration Register will end the current message transmission while a write to the XFDL Transmit Data Register will provide more data. TDLINT is a programmable polarity, open-drain output. On reset, TDLCLK/TDLINT is TDLINT. The TEXHDLC register should be programmed after reset to the appropriate mode. When an external DMA is used, TDLINT will be configured as an active-low output and wired-ORed with the $\overline{\text{INT}}$ output and routed to the supervising microprocessor. In that way, the supervising microprocessor will be notified and can service the XFDL. |

| TDLEMOI           | Transmit Data<br>Link End Of<br>Message Input                   | I   | 204             | D5             | The transmit data link end of message input, TDLEMOI, is an alternate method for an external DMA controller to signal the end of the transmitted message to the HDLC transmitter. As the TDLEMOI is an alternative to writing the XFDL configuration register, appropriately the TDLEMOI will set the EOM bit in the XFD: Configuration register. The TDLEMOI input may be asserted before or after the write of the last byte, but must be asserted before the next byte (within 210 us of the last assertion of TDLINT or the $\overline{\text{INT}}$ bit in the XFDL Status Register). If no data transmission is pending, TDLEMOI is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYMBOL    | NAME                                                              | I/O | TQFP<br>PIN NO. | BGA<br>Pin No. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------|-----|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TICLK     | Transmit Input<br>Clock                                           | I   | 1               | C2             | The transmit input clock, TICLK, provides the timing for the DS3 input. TICLK is nominally a 44.736 MHz, 50% duty cycle clock. TIMFP is sampled on the rising edge of TICLK.                                                                                                                                                                                                                                                                                                                                  |

| TIMFP     | Transmit Input<br>M-frame Frame<br>Pulse                          | I   | 208             | B3             | The transmit M-frame pulse, TIMFP, provides the timing/alignment of the M-frame within the DS3 data, TDAT. The first bit (X1) of the M-frame on TDAT will occur within several TICLK cycle and will be confirmed by the output on TMFP. TIMFP may be pulled low if this kind of feedback is not required. TIMFP is sampled on the rising edge of TICLK.                                                                                                                                                       |

| TOH       | Transmit<br>Overhead Data                                         | ļ   | 17              | F2             | The transmit overhead data, TOH, represents the overhead bits (C, F, M, P, and X) that may be inserted into the transmitted DS3. TOH is sampled on the rising edge of TOHCLK.                                                                                                                                                                                                                                                                                                                                 |

| TOHEN     | Transmit<br>Overhead<br>Enable                                    | I   | 18              | F3             | The transmit overhead insertion, TOHEN, is the enable signal that is used in conjunction with the TOH, data input. When TOHEN is high the associated data on TOH will be inserted in to the DS3. When the TOHEN is low, the internal DS3 framer generates and inserts the DS3 overhead bits into the output DS3 stream. TOHEN is sampled on the rising edge of TOHCLK.                                                                                                                                        |

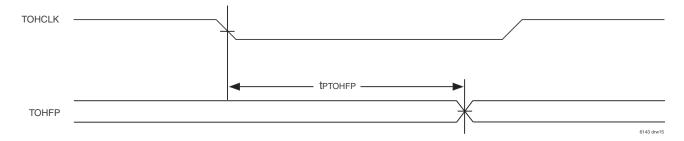

| TOHFP     | Transmit<br>Overhead<br>Frame Pulse                               | 0   | 15              | E3             | The transmit overhead frame position, TOHFP, marks the beginning of the first M-frame, and aligns the TOH data to the DS3 M-frame. TOHFP will be high during the X1 overhead bit position. TOHFP is updated on the falling edge of TOHCLK.                                                                                                                                                                                                                                                                    |

| TOHCLK    | Transmit<br>Overhead Clock                                        | 0   | 14              | E2             | The transmit overhead clock, TOHCLK, provides the timing transmit overhead bits. TOHCLK is nominally a 526 KHz clock. TOHFP is updated on the falling edge of TOHCLK. TOH and TOHEN are sampled on the rising edge of TOHCLK.                                                                                                                                                                                                                                                                                 |

| JCLK      | Transmit DS3<br>Clock                                             | 0   | 2               | A1             | The transmit clock, TCLK, provides timing for other circuitry to synchronize with the DS3 transmitter. TCLK is nominally a 44.736 MHz, 50% duty cycle clock.                                                                                                                                                                                                                                                                                                                                                  |

| TPOS/TDAT | Transmit DS3<br>Positive Pulse/<br>Transmit DS3<br>Data           | 0   | 3               | B1             | In dual rail mode, TPOS/TDAT, is TPOS and represents the positive pulses of a B3ZS-encoded line. TPOS is updated on the falling edge of TCLK by default but may be configured to update on the rising edge of TCLK. In single rail mode, TPOS/TDAT, is TDAT and represents the unipolar DS3 output data. Like the TPOS, TDAT is updated on the falling edge of TCLK by default but may be configured to update on the rising edge of TCLK.                                                                    |

| TNEG/TMFP | Transmit DS3<br>Negative Pulse/<br>Transmit Multi-<br>frame Pulse | 0   | 5               | C1             | In dual rail mode, TNEG/TMFP, is TNEG and represents the negative pulses of a B3ZS-encoded line. TNEG is updated on the falling edge of TCLK by default but may be configured to update on the rising edge of TCLK. In single rail mode, TNEG/TMFP, is TMFP and represents the transmit multi-frame pulse. TMFP will be high during the first bit of the DS3 multiframe output on TDAT. TMFP is updated on the falling edge of TCLK by default but may be configured to update on the rising edge of TCLK.    |

| ĪNT       | Interrupt                                                         | 0   | 33              | К3             | $\overline{\text{INT}}$ is the output interrupt pin. When an interrupt occurs in any of the TSBs, DS2 FRMR, DS3 FRMR, MX12, MX23, PMON, or RBOC, $\overline{\text{INT}}$ will go low, unless the interrupt is masked. In order to clear $\overline{\text{INT}}$ , all pending interrupt TSBs must be read and cleared, otherwise $\overline{\text{INT}}$ will remain low. $\overline{\text{INT}}$ is an open drain output so it can be wired-ORed with other active-low open-drain output pins of the device. |

| <u>CS</u> | Chip Select                                                       | I   | 45              | M2             | This active LOW input is used by a microprocessor to activate the microprocessor port. $\overline{\text{CS}}$ must go low for at least once after powerup. If $\overline{\text{CS}}$ is not used it must be tied to an inverted version of $\overline{\text{RST}}$ .                                                                                                                                                                                                                                          |

| RD        | Microprocessor<br>Read                                            | I   | 57              | R3             | This active low input controls the direction of the data bus lines (D0-7) during a microprocessor access. When $\overline{RD}$ is low, D0-7 are output.                                                                                                                                                                                                                                                                                                                                                       |

| WR        | Microprocessor<br>Write                                           | I   | 56              | Т3             | This active low input controls the direction of the data bus lines (D0-7) during a microprocessor access. When $\overline{WR}$ is low, D0-7 are input.                                                                                                                                                                                                                                                                                                                                                        |

| SYMBOL | NAME                         | I/O | TQFP<br>PIN NO.                         | BGA<br>Pin No.                         | DESCRIPTION                                                                                                                                                                                                                                                                                           |

|--------|------------------------------|-----|-----------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-7   | Microprocessor<br>Data       | I/O | *See TQFP<br>table below<br>for details | *See BGA<br>table below<br>for deatils | These pins are the data bits of the microprocessor port.                                                                                                                                                                                                                                              |

| A0-8   | Microprocessor<br>Address    | I   | *See TQFP<br>table below<br>for details | *See BGA<br>table below<br>for details | These address lines access all internal memories.                                                                                                                                                                                                                                                     |

| RST    | Reset                        | I   | 58                                      | P3                                     | This input puts the IDT82V8313 into a reset state that clears the device internal counters and registers. The RESET pin must be held LOW for a minimum of 100ns to properly reset the device. This pin has a weak internal pull-up resistor.                                                          |

| ALE    | Address Latch<br>Enable      | I   | 46                                      | M1                                     | The address latch enable is an active high input that will latch the A0-7 address bus. The ALE is used in a multiplexed address/data microprocessor environment. The ALE has a weak internal pull-up resistor.                                                                                        |

| VCC    | VCC                          | I   | *See TQFP<br>table below<br>for details | *See BGA<br>table below<br>for details | This is the +3.3 Volt power supply for the core of the device.                                                                                                                                                                                                                                        |

| VCC    | VCC                          | I   | *See TQFP<br>table below<br>for details | *See BGA<br>table below<br>for details | This is the +3.3 Volt power supply for the i/o of the device.                                                                                                                                                                                                                                         |

| GND    | Ground                       | I   | *See TQFP<br>table below<br>for details | *See BGA<br>table below<br>for details | Ground Rail.                                                                                                                                                                                                                                                                                          |

| TDI    | JTAG Test<br>Serial Data In  | I   |                                         | P5                                     | JTAG serial test instructions and data are shifted in on this pin. This pin is pulled HIGH by an internal pull-up when not driven.                                                                                                                                                                    |

| TDO    | JTAG Test<br>Serial Data Out | 0   |                                         | R7                                     | JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high-impedance state when JTAG scan is not enabled.                                                                                                                                                            |

| TRST   | JTAG Test<br>Reset           | I   |                                         | T4                                     | Asynchronously initializes the JTAG Test Access Port controller by putting it in the Test-Logic-Reset state. This pin is pulled HIGH by an internal pull-up when not driven. This pin should be pulsed LOW on power-up, or held LOW, to ensure that the IDT72V71660 is in the normal functional mode. |

| TCLK   | JTAG Test<br>Clock           | I   |                                         | P11                                    | Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                            |

| TMS    | JTAG Test<br>Mode Select     | I   |                                         | R9                                     | JTAG signal that controls the state transitions of the Test Access Port controller. This pin is pulled HIGH by an internal pull-up when not driven.                                                                                                                                                   |

### **TQFP PIN NUMBER TABLE**

| SYMBOL     | NAME                      | I/O | PIN NUMBER                                                                                                                           |

|------------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| RD1CLK1-28 | Receive DS1<br>Clock      | 0   | 198, 193, 186, 180, 175, 170, 166, 159, 155, 151, 146, 142, 137, 133, 127, 122, 116, 110, 106, 102, 98, 91, 87, 82, 76, 71, 66, 62.  |

| RD1DAT1-28 | Receive DS1<br>Data       | 0   | 202, 195, 188, 182, 177, 173, 168, 161, 157, 153, 149, 144, 139, 135, 129, 124, 118, 114, 108, 104, 100, 94, 89, 84, 78, 74, 69, 64. |

| TD1CLK1-28 | Transmit DS1<br>Clock     | I   | 201, 194, 187, 181, 176, 172, 167, 160, 156, 152, 148, 143, 138, 134, 128, 123, 117, 112, 107, 103, 99, 92, 88, 83, 77, 72, 68, 63.  |

| TD1DAT1-28 | Transmit DS1<br>Data      | I   | 203. 196, 190, 184, 179, 174, 169, 162, 158, 154, 150, 145, 141, 136, 130, 126, 120, 115, 109, 105, 101, 97, 90, 86, 81, 75, 70, 65. |

| D0-7       | Microprocessor<br>Data    | I/O | 34, 35, 37, 38, 39, 41, 42, 44.                                                                                                      |

| A0-8       | Microprocessor<br>Address | I   | 47, 48, 49, 50, 51, 52, 53, 54, 55.                                                                                                  |

| Vcc        | Vcc                       | I   | 9, 43, 60, 95, 121, 164, 189, 199.                                                                                                   |

| GND        | Ground                    | I   | 8, 11, 27, 36, 59, 80, 96, 111, 132, 163, 183, 185, 191, 192, 200.                                                                   |

### **BGA PIN NUMBER TABLE**

| SYMBOL     | NAME                      | I/O | PIN DESCRIPTION                                                                                                                      |

|------------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| RD1CLK1-28 | Receive DS1<br>Clock      | 0   | A 5, C6, A8, A9, D11, D12, C13, A14, B15, D16, E16, F16, G16, H16, J16, L13, M13, N14, R16, R15, T13, T12, T11, P10, R8, P6, R5, R4. |

| RD1DAT1-28 | Receive DS1<br>Data       | 0   | A4, A6, B7, C9, B10, B11, B12, A13, A16, C15, D14, E14, J14, K15, L15, M15, N16, J15, R14, P13, T10, P9, P7, T6, N4.                 |

| TD1CLK1-28 | Transmit DS1<br>Clock     | I   | B4, B6, C7, B9, A10, A11, A12, B14, B16, C14, D13, E13, F13, H16, J15, K16, L16, M16, P15, T15, P14, N13, N12, R10, P8, T7, N5, P4.  |

| TD1DAT1-28 | Transmit DS1<br>Transmit  | I   | A3, B5, A7, C8, C10, C11, C12, B13, A15, C16, D15, E15, F15, G15, H14, K14, L14, M14, N15, R16, T14, R13, R12, R11, T9, T8, R6, T5.  |

| D0-7       | Microprocessor<br>Data    | I/O | K2, K1, L4, L3, L2, L1, M4, M3.                                                                                                      |

| A0-8       | Microprocessor<br>Address | I   | N3, N2, P2, P1, R1,T1, T2, R2.                                                                                                       |

| Vcc        | Vcc                       | I   | G4, H4, J4, K4, N6, N7, N8, N9, N10, N11, K13, J13, K13, G13, D6, D7, D8, D9, D10.                                                   |

| GND        | Ground                    | I   | B8, D6, G7-G10, H7-H10, J7-J10, K7-K10.                                                                                              |

# REGISTER MEMORY MAP TABLE 2 — REGISTER MEMORY MAP

| Reg          | R/W | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Register<br>Name                                  |

|--------------|-----|----------|----------|----------|----------|----------|----------|----------|----------|---------------------------------------------------|

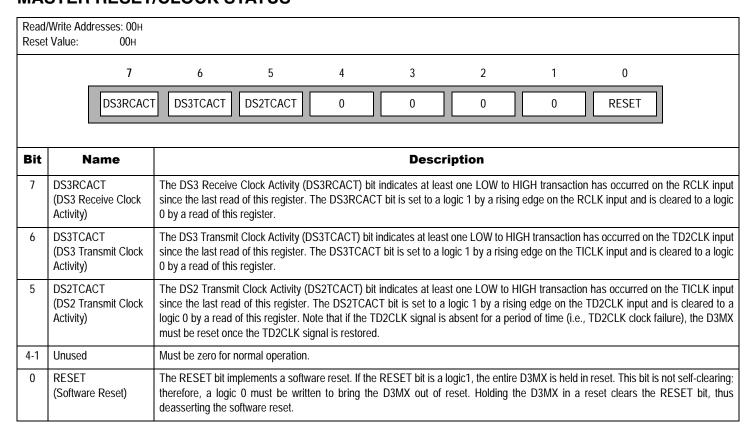

| 00н          | R/W | DS3RCACT | DS3TCACT | DS2TCACT | -        | -        | -        | -        | Reset    | Master Reset/Clock<br>Status                      |

| 01н          | R   | ID7      | ID6      | ID5      | ID4      | ID3      | ID2      | ID1      | ID0      | Revision/Global<br>PMON Update                    |

| 02н          | R/W | EXD2CLK  | BYP7     | BYP6     | BYP5     | BYP4     | BYP3     | BYP2     | BYP1     | Master Bypass<br>Configuration                    |

| 03н          | R/W | REXHDLC  | TEXHDLC  | -        | -        | REOMPOL  | TUDRPOL  | RINTPOL  | TINTPOL  | Master HDLC<br>Configuration                      |

| 04н          | R/W | -        |          | -        | -        | LINEAIS1 | LINEAIS2 | LLBE     | DLBE     | Master Loopback<br>Configuration                  |

| 05н          | R/W | -        | -        | -        | TINV     | TFALL    | TUNI     | RINV     | RFALL    | Master Interface<br>Configuration                 |