# Flash Memory 32M (×16) Flash Memory + 8M(×16) SRAM

(Model No.: LRS1383F)

Spec No.: MFM2-J14424 Issue Date: April 26,2002

#### LRS1383F

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- Office electronics

- Instrumentation and measuring equipment

- · Machine tools

- Audiovisual equipment

- Home appliance

- Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- Mainframe computers

- Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- Rescue and security equipment

- Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- Aerospace equipment

- Communications equipment for trunk lines

- Control equipment for the nuclear power industry

- Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

#### LRS1383F

1

|                                            | Contents                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Desci                                   | iption                                                                                                                                                                                                                                                                                                                                                          |

| 2. Pin C                                   | onfiguration                                                                                                                                                                                                                                                                                                                                                    |

| 3. Truth 3.1 3.2                           | Table                                                                                                                                                                                                                                                                                                                                                           |

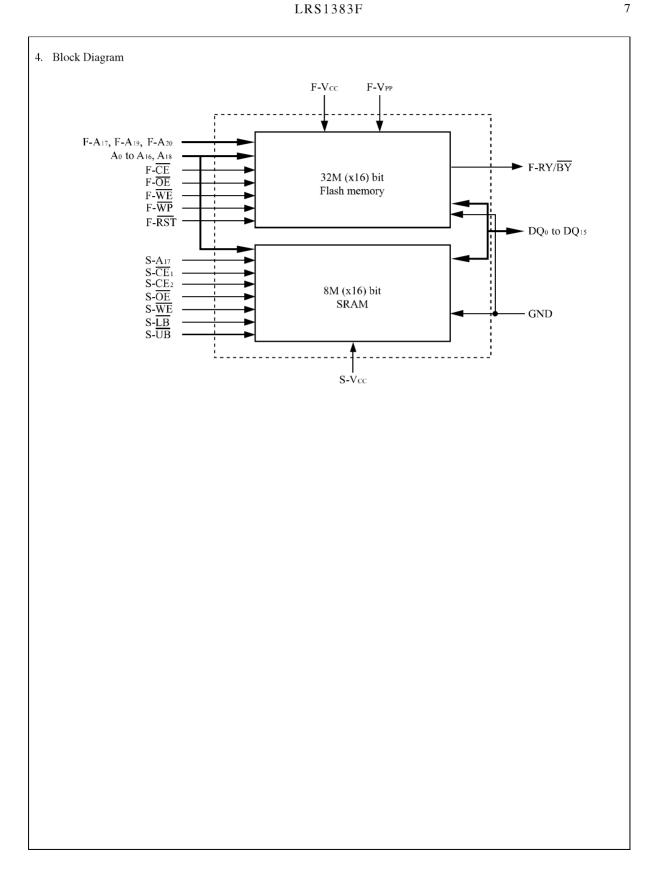

| 4. Block                                   | Diagram                                                                                                                                                                                                                                                                                                                                                         |

| 5. Comr<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | nand Definitions for Flash Memory         8           Command Definitions         8           Identifier Codes for Read Operation         10           Functions of Block Lock and Block Lock-Down         11           Block Locking State Transitions upon Command Write         11           Block Locking State Transitions upon F-WP Transition         12 |

| 6. Status                                  | Register Definition                                                                                                                                                                                                                                                                                                                                             |

| 7. Mem                                     | ory Map for Flash Memory                                                                                                                                                                                                                                                                                                                                        |

| 8. Absol                                   | ute Maximum Ratings                                                                                                                                                                                                                                                                                                                                             |

| 9. Recoi                                   | nmended DC Operating Conditions                                                                                                                                                                                                                                                                                                                                 |

| 10. Pin (                                  | Capacitance                                                                                                                                                                                                                                                                                                                                                     |

| 11. DC l                                   | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                      |

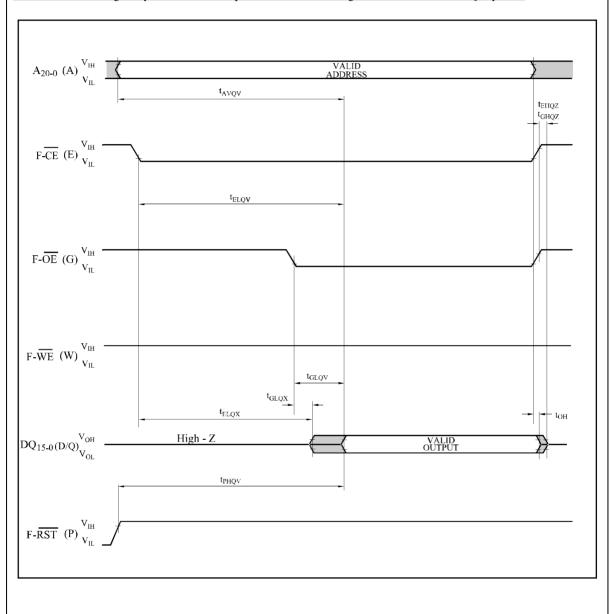

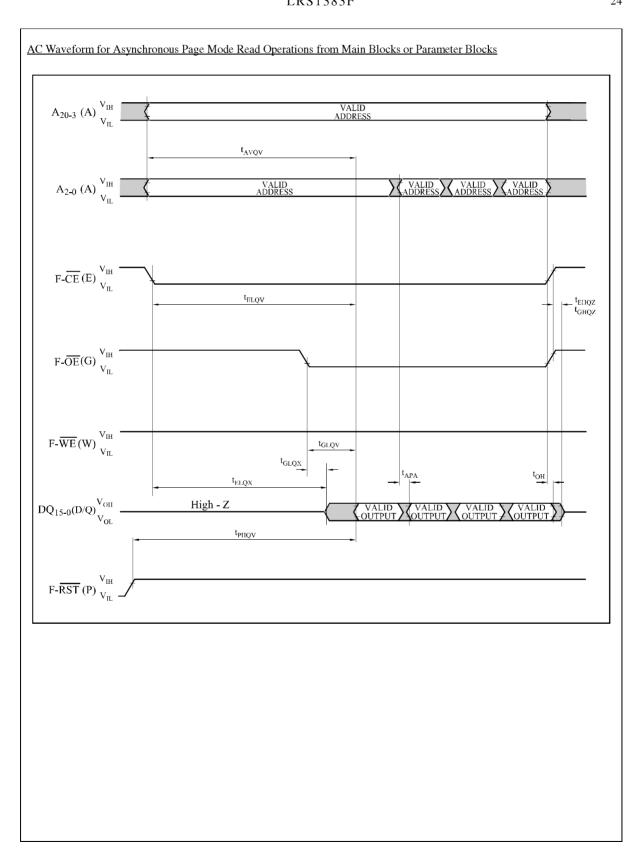

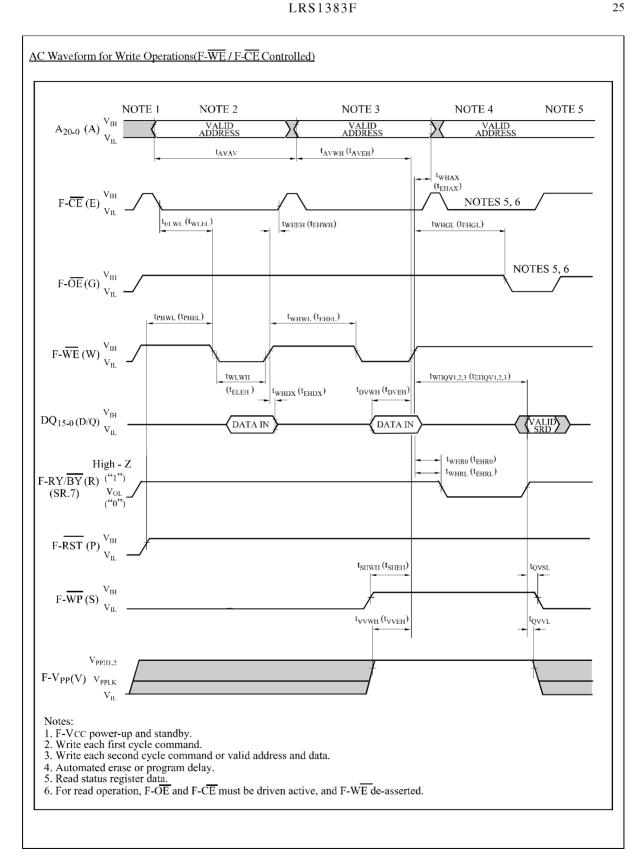

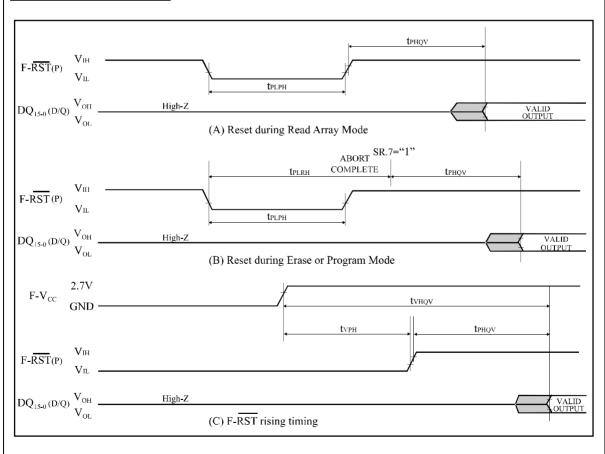

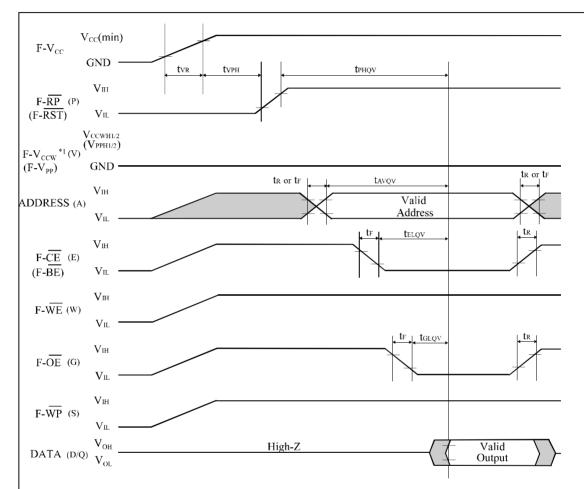

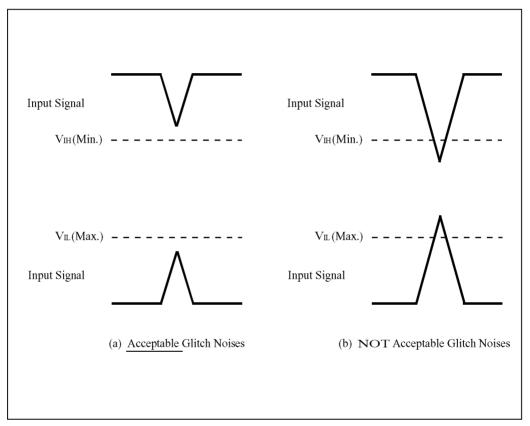

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5       | Electrical Characteristics for Flash Memory.       20         AC Test Conditions.       20         Read Cycle.       20         Write Cycle (F-WE/F-CE Controlled).       21         Block Erase, Full Chip Erase, (Page Buffer) Program Performance.       22         Flash Memory AC Characteristics Timing Chart       23         Reset Operations       26  |

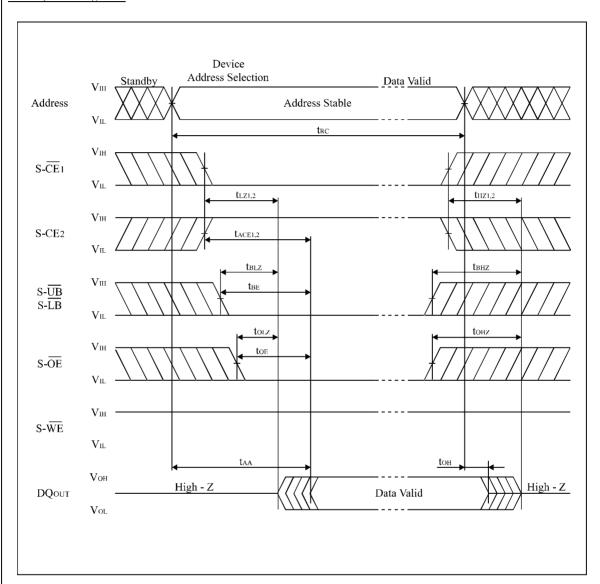

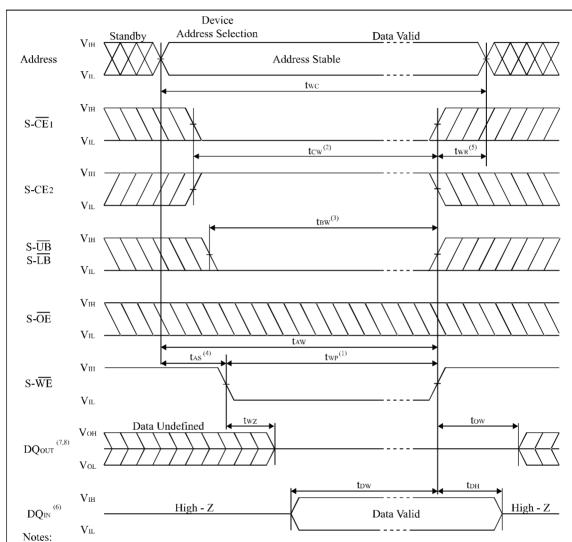

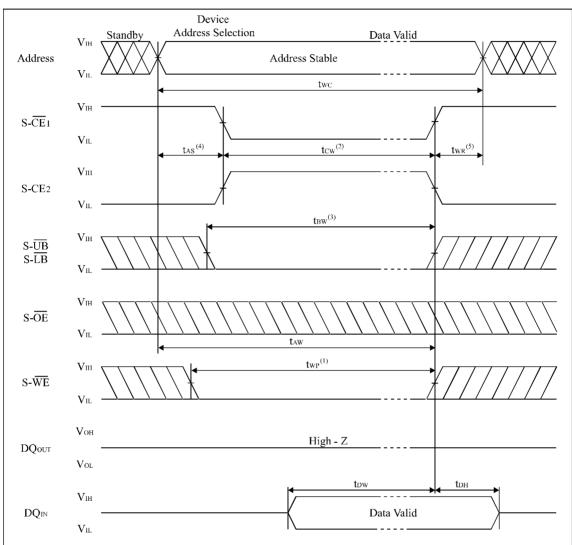

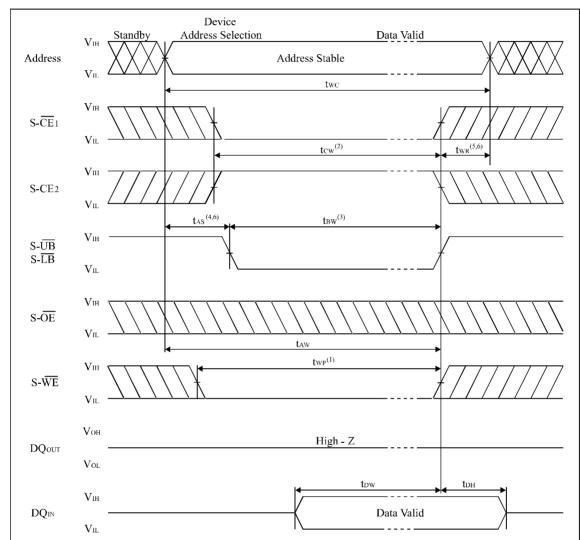

| 13.1<br>13.2<br>13.3                       | Electrical Characteristics for SRAM       27         AC Test Conditions       27         Read Cycle       27         Write Cycle       28         SRAM AC Characteristics Timing Chart       29                                                                                                                                                                 |

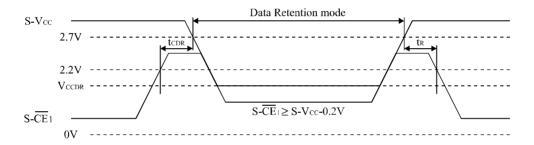

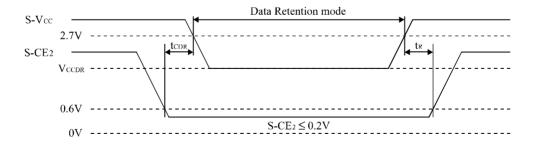

| 14. Data                                   | Retention Characteristics for SRAM                                                                                                                                                                                                                                                                                                                              |

| 15. Note                                   | s 34                                                                                                                                                                                                                                                                                                                                                            |

| 16. Flasl                                  | n Memory Data Protection                                                                                                                                                                                                                                                                                                                                        |

| 17. Desi                                   | gn Considerations                                                                                                                                                                                                                                                                                                                                               |

|                                            | ted Document Information                                                                                                                                                                                                                                                                                                                                        |

2

#### **SHARP**

1. Description

The LRS1383F is a combination memory organized as 2,097,152 x16 bit flash memory and 524,288 x16 bit static RAM in one package.

#### Features

- Power supply

Operating temperature

2.7V to 3.3V

-25°C to +85°C

- Not designed or rated as radiation hardened

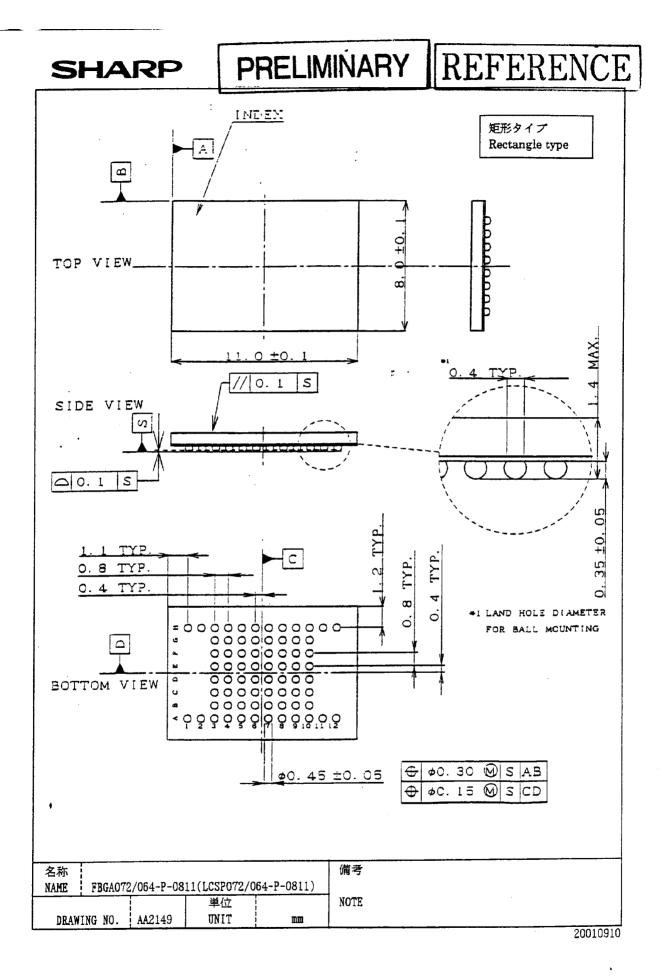

- 72pin CSP (LCSP072-P-0811) plastic package

- Flash memory has P-type bulk silicon, and SRAM has P-type bulk silicon

#### Flash Memory

- Access Time •••• 85 ns (Max.)

- Power supply current (The current for F-V  $_{CC}$  pin and F-V  $_{PP}$  pin)

Standby  $\bullet \bullet \bullet \bullet \qquad 25 \ \mu A \qquad (Max. \ F-\overline{CE} = F-\overline{RST} = F-V_{CC} \pm 0.2V)$

- Optimized Array Blocking Architecture

Eight 4K-word Parameter Blocks

Sixty-Three 32K-word Main Blocks

Bottom Parameter Location

- Extended Cycling Capability

100,000 Block Erase Cycles (F-V<sub>pp</sub> = 1.65V to 3.3V) 1,000 Block Erase Cycles and total 80 hours (F-V<sub>pp</sub> = 11.7V to 12.3V)

- Enhanced Automated Suspend Options

Word Write Suspend to Read Block Erase Suspend to Word Write

Block Erase Suspend to Read

#### SRAM

- Access Time •••• 70 ns (Max.)

- Power Supply current

Operating current  $\bullet \bullet \bullet \bullet = 50 \text{ mA}$  (Max.  $t_{RC}$ ,  $t_{WC} = \text{Min.}$ )

• • • • 8 mA (Max.  $t_{RC}$ ,  $t_{WC} = 1\mu s$ , CMOS Input)

Standby current  $\bullet \bullet \bullet \bullet \quad 25 \,\mu A \quad (Max.$

Data retention current  $\bullet \bullet \bullet \bullet \bullet = 25 \,\mu\text{A} \quad (\text{Max. S-V}_{CC} = 3.0\text{V})$

LRS1383F 3

#### 2. Pin Configuration - INDEX (TOP View) 1 2 3 4 5 6 7 8 9 10 11 12 NC A15 A13 A12 GND NC NC NC (F-A20 A14 $(s-\overline{w}\overline{E})$ В A10 **A**9 DQ15 (DQ14) DQ7 A16 (DQ13 DQ6 DQ4 C (S-A17 DQ5 NC RY/BY (F-RST $T_1$ DQ12 (S-CE2 D GND T2 (S-Vcc (F-Vcc (DQ11 Т3 DQ10 DQ2 DQ3 (F-A19 Ε $S-\overline{LB}$ S-UB S-OE NC DQ9 DQ8 DQ0 F DQ1 $(S-\overline{CE})$ **A**7 A6 **A**3 **A**2 Αı G NC F-CE (F-ŌĒ Η NC $A_0$ GND NC

Note) From T1 to T3 pins are needed to be open. Two NC pins at the corner are connected. Do not float any GND pins.

| Pin                                                          | Description                                                                                                                                                                                                                                                        | Type                 |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $A_0$ to $A_{16}$ , $A_{18}$                                 | Address Inputs (Common)                                                                                                                                                                                                                                            | Input                |

| F-A <sub>17</sub> ,<br>F-A <sub>19</sub> , F-A <sub>20</sub> | Address Inputs (Flash)                                                                                                                                                                                                                                             | Input                |

| S-A <sub>17</sub>                                            | Address Input (SRAM)                                                                                                                                                                                                                                               | Input                |

| F-Œ                                                          | Chip Enable Input (Flash)                                                                                                                                                                                                                                          | Input                |

| $S-\overline{CE}_1$ , $S-CE_2$                               | Chip Enable Inputs (SRAM)                                                                                                                                                                                                                                          | Input                |

| F-WE                                                         | Write Enable Input (Flash)                                                                                                                                                                                                                                         | Input                |

| S-WE                                                         | Write Enable Input (SRAM)                                                                                                                                                                                                                                          | Input                |

| F- <del>OE</del>                                             | Output Enable Input (Flash)                                                                                                                                                                                                                                        | Input                |

| S- <del>OE</del>                                             | Output Enable Input (SRAM)                                                                                                                                                                                                                                         | Input                |

| $S-\overline{LB}$                                            | SRAM Byte Enable Input (DQ <sub>0</sub> to DQ <sub>7</sub> )                                                                                                                                                                                                       | Input                |

| S-UB                                                         | SRAM Byte Enable Input (DQ <sub>8</sub> to DQ <sub>15</sub> )                                                                                                                                                                                                      | Input                |

| F-RST                                                        | $\label{eq:Reset Power Down Input (Flash)} Block erase and Write: V_{IH} \\ Read: V_{IH} \\ Reset Power Down: V_{IL}$                                                                                                                                              | Input                |

| F-WP                                                         | Write Protect Input (Flash) When $F-\overline{WP}$ is $V_{IL}$ , locked-down blocks cannot be unlocked. Erase or program operation can be executed to the blocks which are not locked and locked-down. When $F-\overline{WP}$ is $V_{IH}$ , lock-down is disabled. | Input                |

| F-RY/BY                                                      | Ready/Busy Output (Flash) During an Erase or Write operation : V <sub>OL</sub> Block Erase and Write Suspend : High-Z (High impedance)                                                                                                                             | Open Drain<br>Output |

| DQ <sub>0</sub> to DQ <sub>15</sub>                          | Data Inputs and Outputs (Common)                                                                                                                                                                                                                                   | Input / Outpu        |

| $F-V_{CC}$                                                   | Power Supply (Flash)                                                                                                                                                                                                                                               | Power                |

| $S-V_{CC}$                                                   | Power Supply (SRAM)                                                                                                                                                                                                                                                | Power                |

| F-V <sub>PP</sub>                                            | $\begin{array}{l} \mbox{Monitoring Power Supply Voltage (Flash)} \\ \mbox{Block Erase and Write}: F-V_{PP} = V_{PPH1/2} \\ \mbox{All Blocks Locked}: F-V_{PP} < V_{PPLK} \end{array}$                                                                              | Input                |

| GND                                                          | GND (Common)                                                                                                                                                                                                                                                       | Power                |

| NC                                                           | Non Connection                                                                                                                                                                                                                                                     | =                    |

| T <sub>1</sub> to T <sub>3</sub>                             | Test pins (Should be all open)                                                                                                                                                                                                                                     | _                    |

#### 3. Truth Table

#### 3.1 Bus Operation<sup>(1)</sup>

| э.т <b>Ба</b> з ор. |                   |         |      |       |      |      |                     |                   |      |      |                  |      |                                       |   |        |    |        |

|---------------------|-------------------|---------|------|-------|------|------|---------------------|-------------------|------|------|------------------|------|---------------------------------------|---|--------|----|--------|

| Flash               | SRAM              | Notes   | F-CE | F-RST | F-OE | F-WE | $S-\overline{CE}_1$ | S-CE <sub>2</sub> | S-OE | S-WE | S- <del>LB</del> | S-UB | $\mathrm{DQ}_0$ to $\mathrm{DQ}_{15}$ |   |        |    |        |

| Read                |                   | 3,5     |      |       | L    |      |                     | •                 |      |      |                  | •    | (7)                                   |   |        |    |        |

| Output<br>Disable   | Standby           | 5       | L    | Н     | Н    | Н    | (8)                 |                   | (8)  |      | (8)              |      | X                                     | X | (8     | 3) | High-Z |

| Write               |                   | 2,3,4,5 |      |       |      | L    |                     |                   |      |      |                  |      | $D_{IN}$                              |   |        |    |        |

|                     | Read              | 5       |      |       |      |      |                     |                   | L    | Н    |                  | (9   | 9)                                    |   |        |    |        |

| Standby             | Output<br>Disable | r.      | 5 H  | Н     | X    | X    | L                   | Н                 | Н    | Н    | X                | X    | High-Z                                |   |        |    |        |

| Stalldby            |                   | 3       |      |       |      | Λ    |                     |                   | X    | X    | Н                | Н    | Tilgii-Z                              |   |        |    |        |

|                     | Write             | 5       |      |       |      |      |                     |                   | X    | L    |                  | (9   | 9)                                    |   |        |    |        |

|                     | Read              | 5,6     |      |       |      |      |                     |                   | L    | Н    |                  | (9   | 9)                                    |   |        |    |        |

| Reset Power         | Output 5.5        | ut 5.6  | 5,6  | 5.6   | X    | L    | X                   | X                 | L    | Н    | Н                | Н    | X                                     | X | High-Z |    |        |

| Down                | Disable           | 3,0     | Λ    | L     | X    | X    | L                   | Н                 | X    | X    | Н                | Н    | riigii-Z                              |   |        |    |        |

|                     | Write             | 5,6     |      |       |      |      |                     |                   | X    | L    |                  | (9   | 9)                                    |   |        |    |        |

| Standby             |                   | 5       | Н    | Н     |      |      |                     | •                 |      |      |                  |      |                                       |   |        |    |        |

| Reset Power<br>Down | Standby           | 5,6     | X    | L     | X    | X    | (8                  | 3)                | X    | X    | (3               | 8)   | High-Z                                |   |        |    |        |

|                     |                   |         |      |       |      | •    |                     |                   |      |      |                  |      |                                       |   |        |    |        |

#### Notes:

- 1.  $L = V_{IL}$ ,  $H = V_{IH}$ , X = H or L, High-Z = High impedance. Refer to the DC Characteristics.

- 2. Command writes involving block erase, (page buffer) program are reliably executed when  $F-V_{PP}=V_{PPH1/2}$  and  $F-V_{CC}=2.7V$  to 3.3V.

Command writes involving full chip erase is reliably executed when F-V<sub>PP</sub> = V<sub>PPH1</sub> and F-V<sub>CC</sub> = 2.7V to 3.3V. Block erase, full chip erase, (page buffer) program with F-V<sub>PP</sub> < V<sub>PPH1/2</sub> (Min.) produce spurious results and should not be attempted.

- 3. Never hold  $F-\overline{OE}$  low and  $F-\overline{WE}$  low at the same timing.

- 4. Refer Section 5. Command Definitions for Flash Memory valid D<sub>IN</sub> during a write operation.

- 5. F- $\overline{WP}$  set to  $V_{IL}$  or  $V_{IH}$ .

- 6. Electricity consumption of Flash Memory is lowest when  $F-\overline{RST} = GND \pm 0.2V$ .

#### 7. Flash Read Mode

| Mode                  | Address               | DQ <sub>0</sub> to DQ <sub>15</sub> |  |  |

|-----------------------|-----------------------|-------------------------------------|--|--|

| Read Array            | X                     | $\mathrm{D}_{\mathrm{OUT}}$         |  |  |

| Read Identifier Codes | See 5.2               | See 5.2                             |  |  |

| Read Query            | Refer to the Appendix | Refer to the Appendix               |  |  |

#### 8. SRAM Standby Mode

| $\overline{}$ |                   |                  |      |

|---------------|-------------------|------------------|------|

| $S-CE_1$      | S-CE <sub>2</sub> | S- <del>LB</del> | S-UB |

| Н             | X                 | X                | X    |

| X             | L                 | X                | X    |

| X             | X                 | Н                | Н    |

9. S-UB, S-LB Control Mode

| S- <del>LB</del> | S-UB | DQ <sub>0</sub> to DQ <sub>7</sub> | $\mathrm{DQ}_8$ to $\mathrm{DQ}_{15}$ |

|------------------|------|------------------------------------|---------------------------------------|

| L                | L    | $\mathrm{D}_{\mathrm{OUT}}$        | D <sub>OUT</sub> /D <sub>IN</sub>     |

| L                | Н    | $\mathrm{D}_{\mathrm{OUT}}$        | High-Z                                |

| Н                | L    | High-Z                             | D <sub>OUT</sub> /D <sub>IN</sub>     |

3.2 Simultaneous Operation Modes Allowed with Four Planes  $^{(1,\,2)}$

|                        |               | THEN THE MODES ALLOWED IN THE OTHER PARTITION IS: |                |               |                 |                           |                |                    |                    |                           |  |  |

|------------------------|---------------|---------------------------------------------------|----------------|---------------|-----------------|---------------------------|----------------|--------------------|--------------------|---------------------------|--|--|

| IF ONE PARTITION IS:   | Read<br>Array | Read ID                                           | Read<br>Status | Read<br>Query | Word<br>Program | Page<br>Buffer<br>Program | Block<br>Erase | Full Chip<br>Erase | Program<br>Suspend | Block<br>Erase<br>Suspend |  |  |

| Read Array             | X             | X                                                 | X              | X             | X               | X                         | X              |                    | X                  | X                         |  |  |

| Read ID                | X             | X                                                 | X              | X             | X               | X                         | X              |                    | X                  | X                         |  |  |

| Read Status            | X             | X                                                 | X              | X             | X               | X                         | X              | X                  | X                  | X                         |  |  |

| Read Query             | X             | X                                                 | X              | X             | X               | X                         | X              |                    | X                  | X                         |  |  |

| Word Program           | X             | X                                                 | X              | X             |                 |                           |                |                    |                    | X                         |  |  |

| Page Buffer<br>Program | X             | X                                                 | X              | X             |                 |                           |                |                    |                    | X                         |  |  |

| Block Erase            | X             | X                                                 | X              | X             |                 |                           |                |                    |                    |                           |  |  |

| Full Chip Erase        |               |                                                   | X              |               |                 |                           |                |                    |                    |                           |  |  |

| Program<br>Suspend     | X             | X                                                 | X              | X             |                 |                           |                |                    |                    | X                         |  |  |

| Block Erase<br>Suspend | X             | X                                                 | X              | X             | X               | X                         |                |                    | X                  |                           |  |  |

#### Notes:

- 1. "X" denotes the operation available.

2. Configurative Partition Dual Work Restrictions:

Status register reflects partition state, not WSM (Write State Machine) state - this allows a status register for each partition.

Only one partition can be erased or programmed at a time - no command queuing.

Commands must be written to an address within the block targeted by that command.

#### 5. Command Definitions for Flash $Memory^{(11)}$

#### 5.1 Command Definitions

|                                                  | Bus             |         | F                   | irst Bus Cyc           | le                  | Second Bus Cycle    |                        |                     |

|--------------------------------------------------|-----------------|---------|---------------------|------------------------|---------------------|---------------------|------------------------|---------------------|

| Command                                          | Cycles<br>Req'd | Notes   | Oper <sup>(1)</sup> | Address <sup>(2)</sup> | Data <sup>(3)</sup> | Oper <sup>(1)</sup> | Address <sup>(2)</sup> | Data <sup>(3)</sup> |

| Read Array                                       | 1               | 2       | Write               | PA                     | FFH                 |                     |                        |                     |

| Read Identifier Codes                            | ≥2              | 2,3,4   | Write               | PA                     | 90H                 | Read                | IA                     | ID                  |

| Read Query                                       | ≥2              | 2,3,4   | Write               | PA                     | 98H                 | Read                | QA                     | QD                  |

| Read Status Register                             | 2               | 2,3     | Write               | PA                     | 70H                 | Read                | PA                     | SRD                 |

| Clear Status Register                            | 1               | 2       | Write               | PA                     | 50H                 |                     |                        |                     |

| Block Erase                                      | 2               | 2,3,5   | Write               | BA                     | 20H                 | Write               | BA                     | D0H                 |

| Full Chip Erase                                  | 2               | 2,5,9   | Write               | X                      | 30H                 | Write               | X                      | D0H                 |

| Program                                          | 2               | 2,3,5,6 | Write               | WA                     | 40H or<br>10H       | Write               | WA                     | WD                  |

| Page Buffer Program                              | ≥4              | 2,3,5,7 | Write               | WA                     | E8H                 | Write               | WA                     | N-1                 |

| Block Erase and (Page Buffer)<br>Program Suspend | 1               | 2,8,9   | Write               | PA                     | ВОН                 |                     |                        |                     |

| Block Erase and (Page Buffer)<br>Program Resume  | 1               | 2,8,9   | Write               | PA                     | D0H                 |                     |                        |                     |

| Set Block Lock Bit                               | 2               | 2       | Write               | BA                     | 60H                 | Write               | BA                     | 01H                 |

| Clear Block Lock Bit                             | 2               | 2,10    | Write               | BA                     | 60H                 | Write               | BA                     | D0H                 |

| Set Block Lock-down Bit                          | 2               | 2       | Write               | BA                     | 60H                 | Write               | BA                     | 2FH                 |

| Set Partition Configuration<br>Register          | 2               | 2,3     | Write               | PCRC                   | 60H                 | Write               | PCRC                   | 04H                 |

#### Notes:

- 1. Bus operations are defined in 3.1 Bus Operation.

- 2. The address which is written at the first bus cycle should be the same as the address which is written at the second bus cycle.

X=Any valid address within the device.

PA=Address within the selected partition.

IA=Identifier codes address (See 5.2 Identifier Codes for Read Operation).

$QA = Query\ codes\ address.\ Refer\ to\ the\ LH28F320BF,\ LH28F640BF,\ LH28F128BF\ series\ Appendix\ for\ details.$

$BA = Address\ within\ the\ block\ being\ erased,\ set/cleared\ block\ lock\ bit\ or\ set\ block\ lock-down\ bit.$

WA=Address of memory location for the Program command or the first address for the Page Buffer Program command. PCRC=Partition configuration register code presented on the address  $A_0$ - $A_{15}$ .

- 3. ID=Data read from identifier codes (See 5.2 Identifier Codes for Read Operation).

- QD=Data read from query database. Refer to the LH28F320BF, LH28F640BF, LH28F128BF series Appendix for details. SRD=Data read from status register. See 6. Status Register Definition for a description of the status register bits.

WD=Data to be programmed at location WA. Data is latched on the rising edge of  $F-\overline{WE}$  or  $F-\overline{CE}$  (whichever goes high first). N-1=N is the number of the words to be loaded into a page buffer.

- 4. Following the Read Identifier Codes command, read operations access manufacturer code, device code, block lock configuration code, partition configuration register code (See 5.2 Identifier Codes for Read Operation).

The Read Query command is available for reading CFI (Common Flash Interface) information.

- 5. Block erase, full chip erase or (page buffer) program cannot be executed when the selected block is locked. Unlocked block can be erased or programmed when  $F-\overline{RST}$  is  $V_{IH}$ .

- 6. Either 40H or 10H are recognized by the CUI (Command User Interface) as the program setup.

- 7. Following the third bus cycle, inputs the program sequential address and write data of "N" times. Finally, input the any valid address within the target partition to be programmed and the confirm command (D0H). Refer to the LH28F320BF, LH28F640BF, LH28F128BF series Appendix for details.

| 8.  | If the program operation in one partition is suspended and the erase operation in other partition is also suspended, the suspended program operation should be resumed first, and then the suspended erase operation should be resumed next.                         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.  | Full chip erase operation can not be suspended.                                                                                                                                                                                                                      |

|     | Following the Clear Block Lock Bit command, block which is not locked-down is unlocked when $F-\overline{WP}$ is $V_{IL}$ . When $F-\overline{WP}$ is $V_{IH}$ , lock-down bit is disabled and the selected block is unlocked regardless of lock-down configuration. |

| 11. | Commands other than those shown above are reserved by SHARP for future device implementations and should not be                                                                                                                                                      |

|     | used.                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                      |

#### 5.2 Identifier Codes for Read Operation

|                                  | Code                             | Address [A <sub>15</sub> -A <sub>0</sub> ] <sup>(4)</sup> | Data<br>[DQ <sub>15</sub> -DQ <sub>0</sub> ] | Notes |

|----------------------------------|----------------------------------|-----------------------------------------------------------|----------------------------------------------|-------|

| Manufacturer Code                | Manufacturer Code                | 0000Н                                                     | 00B0H                                        |       |

| Device Code                      | 32M Bottom Parameter Device Code | 0001H                                                     | 00B5H                                        | 1     |

|                                  | Block is Unlocked                |                                                           | $DQ_0 = 0$                                   | 2     |

| Disability of Configuration Code | Block is Locked                  | Block<br>Address                                          | $DQ_0 = 1$                                   | 2     |

| Block Lock Configuration Code    | Block is not Locked-Down         | + 2                                                       | $DQ_1 = 0$                                   | 2     |

|                                  | Block is Locked-Down             |                                                           | $DQ_1 = 1$                                   | 2     |

| Device Configuration Code        | Partition Configuration Register | 0006Н                                                     | PCRC                                         | 3     |

#### Notes:

- 1. Bottom parameter device has its parameter blocks in the plane 0 (The lowest address).

- 2.  $DQ_{15}$ - $DQ_2$  is reserved for future implementation.

- 3. PCRC=Partition Configuration Register Code.

- 4. The address  $A_{20}$ - $A_{16}$  are shown in below table for reading the manufacturer, device, lock configuration, device configuration code.

The address to read the identifier codes is dependent on the partition which is selected when writing the Read Identifier Codes command (90H).

See Chapter 6. Partition Configuration Register Definition (P.15) for the partition configuration register.

#### Identifier Codes for Read Operation on Partition Configuration (32M-bit device)

| Partit | ion Configuration Re | gister | Address (32M-bit device) |

|--------|----------------------|--------|--------------------------|

| PCR.10 | PCR.9                | PCR.8  | $[A_{20}-A_{16}]$        |

| 0      | 0                    | 0      | 00H                      |

| 0      | 0                    | 1      | 00H or 08H               |

| 0      | 1                    | 0      | 00H or 10H               |

| 1      | 0                    | 0      | 00H or 18H               |

| 0      | 1                    | 1      | 00H or 08H or 10H        |

| 1      | 1                    | 0      | 00H or 10H or 18H        |

| 1      | 0                    | 1      | 00H or 08H or 18H        |

| 1      | 1                    | 1      | 00H or 08H or 10H or 18H |

#### 5.3 Functions of Block Lock and Block Lock-Down

|                      |      | (2)          |              |                   |                                      |

|----------------------|------|--------------|--------------|-------------------|--------------------------------------|

| State                | F-WP | $DQ_1^{(1)}$ | $DQ_0^{(1)}$ | State Name        | Erase/Program Allowed <sup>(2)</sup> |

| [000]                | 0    | 0            | 0            | Unlocked          | Yes                                  |

| [001](3)             | 0    | 0            | 1            | Locked            | No                                   |

| [011]                | 0    | 1            | 1            | Locked-down       | No                                   |

| [100]                | 1    | 0            | 0            | Unlocked          | Yes                                  |

| [101] <sup>(3)</sup> | 1    | 0            | 1            | Locked            | No                                   |

| [110] <sup>(4)</sup> | 1    | 1            | 0            | Lock-down Disable | Yes                                  |

| [111]                | 1    | 1            | 1            | Lock-down Disable | No                                   |

#### Notes:

- DQ<sub>0</sub> = 1: a block is locked; DQ<sub>0</sub> = 0: a block is unlocked.

DQ<sub>1</sub> = 1: a block is locked-down; DQ<sub>1</sub> = 0: a block is not locked-down.

- 2. Erase and program are general terms, respectively, to express: block erase, full chip erase and (page buffer) program operations.

- 3. At power-up or device reset, all blocks default to locked state and are not locked-down, that is, [001] (F-\overline{WP} = 0) or [101] (F-\overline{WP} = 1), regardless of the states before power-off or reset operation.

- 4. When  $F-\overline{WP}$  is driven to  $V_{IL}$  in [110] state, the state changes to [011] and the blocks are automatically locked.

#### 5.4 Block Locking State Transitions upon Command Write<sup>(4)</sup>

| Current State |      |        |        | Result after Lock Command Written (Next State) |                           |                              |  |

|---------------|------|--------|--------|------------------------------------------------|---------------------------|------------------------------|--|

| State         | F-WP | $DQ_1$ | $DQ_0$ | Set Lock <sup>(1)</sup>                        | Clear Lock <sup>(1)</sup> | Set Lock-down <sup>(1)</sup> |  |

| [000]         | 0    | 0      | 0      | [001]                                          | No Change                 | [011] <sup>(2)</sup>         |  |

| [001]         | 0    | 0      | 1      | No Change <sup>(3)</sup>                       | [000]                     | [011]                        |  |

| [011]         | 0    | 1      | 1      | No Change                                      | No Change                 | No Change                    |  |

| [100]         | 1    | 0      | 0      | [101]                                          | No Change                 | [111] <sup>(2)</sup>         |  |

| [101]         | 1    | 0      | 1      | No Change                                      | [100]                     | [111]                        |  |

| [110]         | 1    | 1      | 0      | [111]                                          | No Change                 | [111] <sup>(2)</sup>         |  |

| [111]         | 1    | 1      | 1      | No Change                                      | [110]                     | No Change                    |  |

- 1. "Set Lock" means Set Block Lock Bit command, "Clear Lock" means Clear Block Lock Bit command and "Set Lock-down" means Set Block Lock-Down Bit command.

- 2. When the Set Block Lock-Down Bit command is written to the unlocked block ( $DQ_0 = 0$ ), the corresponding block is locked-down and automatically locked at the same time.

- 3. "No Change" means that the state remains unchanged after the command written.

- 4. In this state transitions table, assumes that F- $\overline{WP}$  is not changed and fixed  $V_{IL}$  or  $V_{IH}$ .

#### 5.5 Block Locking State Transitions upon F-WP Transition<sup>(4)</sup>

| D : C. (                        |       | Current | State  |        | Result after F-WP Transition (Next State) |                                           |  |

|---------------------------------|-------|---------|--------|--------|-------------------------------------------|-------------------------------------------|--|

| Previous State                  | State | F-WP    | $DQ_1$ | $DQ_0$ | $F-\overline{WP} = 0 \rightarrow 1^{(1)}$ | $F-\overline{WP} = 1 \rightarrow 0^{(1)}$ |  |

| -                               | [000] | 0       | 0      | 0      | [100]                                     | -                                         |  |

| -                               | [001] | 0       | 0      | 1      | [101]                                     | -                                         |  |

| [110] <sup>(2)</sup>            | [011] | 0       | 1      | 1      | [110]                                     | -                                         |  |

| Other than [110] <sup>(2)</sup> | [011] | U       | 1      | 1      | [111]                                     | -                                         |  |

| -                               | [100] | 1       | 0      | 0      | -                                         | [000]                                     |  |

| -                               | [101] | 1       | 0      | 1      | -                                         | [001]                                     |  |

| -                               | [110] | 1       | 1      | 0      | -                                         | [011] <sup>(3)</sup>                      |  |

| -                               | [111] | 1       | 1      | 1      | -                                         | [011]                                     |  |

- 1. "F- $\overline{WP} = 0 \rightarrow 1$ " means that F- $\overline{WP}$  is driven to  $V_{IH}$  and "F- $\overline{WP} = 1 \rightarrow 0$ " means that F- $\overline{WP}$  is driven to  $V_{IL}$ .

- 2. State transition from the current state [011] to the next state depends on the previous state.

- 3. When  $F-\overline{WP}$  is driven to  $V_{IL}$  in [110] state, the state changes to [011] and the blocks are automatically locked.

- 4. In this state transitions table, assumes that lock configuration commands are not written in previous, current and next state.

#### 6. Status Register Definition

SHARP

#### Status Register Definition

| R    | R    | R      | R    | R    | R     | R   | R |

|------|------|--------|------|------|-------|-----|---|

| 15   | 14   | 13     | 12   | 11   | 10    | 9   | 8 |

| WSMS | BESS | BEFCES | PBPS | VPPS | PBPSS | DPS | R |

| 7    | 6    | 5      | 4    | 3    | 2     | 1   | 0 |

#### SR.15 - SR.8 = RESERVED FOR FUTURE ENHANCEMENTS (R)

SR.7 = WRITE STATE MACHINE STATUS (WSMS)

1 = Ready

0 = Busy

SR.6 = BLOCK ERASE SUSPEND STATUS (BESS)

1 = Block Erase Suspended

0 = Block Erase in Progress/Completed

SR.5 = BLOCK ERASE AND FULL CHIP ERASE STATUS (BEFCES)

1 = Error in Block Erase or Full Chip Erase

0 = Successful Block Erase or Full Chip Erase

SR.4 = (PAGE BUFFER) PROGRAM STATUS (PBPS)

1 = Error in (Page Buffer) Program

0 = Successful (Page Buffer) Program

$SR.3 = F-V_{PP} STATUS (VPPS)$

1 = F-V<sub>PP</sub> LOW Detect, Operation Abort

$0 = F-V_{PP} OK$

SR.2 = (PAGE BUFFER) PROGRAM SUSPEND STATUS (PBPSS)

1 = (Page Buffer) Program Suspended

0 = (Page Buffer) Program in Progress/Completed

SR.1 = DEVICE PROTECT STATUS (DPS)

1 = Erase or Program Attempted on a Locked Block, Operation Abort

0 = Unlocked

SR.0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

Notes:

Status Register indicates the status of the partition, not WSM (Write State Machine). Even if the SR.7 is "1", the WSM may be occupied by the other partition when the device is set to 2, 3 or 4 partitions configuration.

Check SR.7 or F-RY/ $\overline{BY}$  to determine block erase, full chip erase, (page buffer) program completion. SR.6 - SR.1 are invalid while SR.7= "0".

If both SR.5 and SR.4 are "1"s after a block erase, full chip erase, page buffer program, set/clear block lock bit, set block lock-down bit or set partition configuration register attempt, an improper command sequence was entered.

SR.3 does not provide a continuous indication of F-V<sub>PP</sub> level. The WSM interrogates and indicates the F-V<sub>PP</sub> level only after Block Erase, Full Chip Erase, (Page Buffer) Program command sequences. SR.3 is not guaranteed to report accurate feedback when F-V<sub>PP</sub> $\neq$ V<sub>PPH1/2</sub> or V<sub>PPLK</sub>.

SR.1 does not provide a continuous indication of block lock bit. The WSM interrogates the block lock bit only after Block Erase, Full Chip Erase, (Page Buffer) Program command sequences. It informs the system, depending on the attempted operation, if the block lock bit is set. Reading the block lock configuration codes after writing the Read Identifier Codes command indicates block lock bit status.

SR.15 - SR.8 and SR.0 are reserved for future use and should be masked out when polling the status register.

|     | Extended Status Register Definition |    |    |    |    |   |   |

|-----|-------------------------------------|----|----|----|----|---|---|

| R   | R                                   | R  | R  | R  | R  | R | R |

| 15  | 14                                  | 13 | 12 | 11 | 10 | 9 | 8 |

| SMS | R                                   | R  | R  | R  | R  | R | R |

| 7   | 6                                   | 5  | 4  | 3  | 2  | 1 | 0 |

XSR.15-8 = RESERVED FOR FUTURE ENHANCEMENTS (R)

XSR.7 = STATE MACHINE STATUS (SMS)

1 = Page Buffer Program available

0 = Page Buffer Program not available

XSR.6-0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

Notes:

After issue a Page Buffer Program command (E8H), XSR.7="1" indicates that the entered command is accepted. If XSR.7 is "0", the command is not accepted and a next Page Buffer Program command (E8H) should be issued again to check if page buffer is available or not.

XSR.15-8 and XSR.6-0 are reserved for future use and should be masked out when polling the extended status register.

LRS1383F

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | Partit | ion Configuration | on Register Defi                                                                                               | nition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|

| R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R  | R      | R                 | R                                                                                                              | PC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PC1                                  | PC0                                          |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14 | 13     | 12                | 11                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                    | 8                                            |

| R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R  | R      | R                 | R                                                                                                              | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R                                    | R                                            |