### FEATURES

- Complies with Bellcore and ITU-T specifications for jitter tolerance, jitter transfer, and jitter generation

- On-chip high-frequency PLLs for clock generation and clock recovery

- Supports 155.52 Mbit/s (OC-3) and 622.08 Mbit/s (OC-12)

- Selectable reference frequencies of 19.44 or 77.76 MHz

- Interface to both LVPECL and LVTTL logic

- Simple interface with 3.3 V or 5 V optical modules

- Directly compatible with 3.3 V or 5 V network interface devices

- 8-bit LVTTL data path

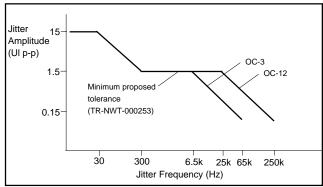

- Compact 10 mm 64 PQFP package

- Diagnostic loopback mode

- Low jitter LVPECL serial interface

- Single 3.3 V supply

### **APPLICATIONS**

- SONET/SDH-based transmission systems

- SONET/SDH modules

- SONET/SDH test equipment

- ATM over SONET/SDH

- Section repeaters

- Add Drop Multiplexers (ADM)

- Broad-band cross-connects

- Fiber optic terminators

- Fiber optic test equipment

### **GENERAL DESCRIPTION**

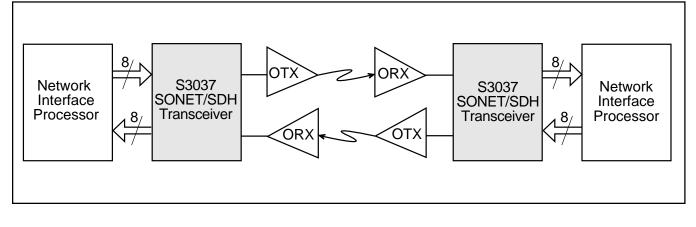

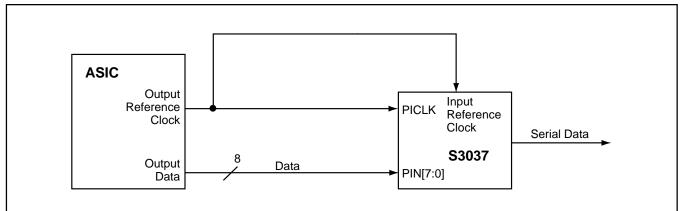

The S3037 SONET/SDH transceiver chip is a fully integrated serialization/deserialization SONET OC-12 (622.08 Mbit/s) and OC-3 (155.52 Mbit/s) interface device. The chip performs all necessary serial-to-parallel and parallel-to-serial functions in conformance with SONET/SDH transmission standards. The device is suitable for SONET-based ATM applications. Figure 1 shows a typical network application.

On-chip clock synthesis is performed by the highfrequency phase-locked loop on the S3037 transceiver chip allowing the use of a slower external transmit clock reference. Clock recovery is performed on the device by synchronizing its on-chip VCO directly to the incoming data stream. The S3037 also performs SONET/SDH frame detection. The chip can be used with a 19.44 or 77.76 MHz reference clock, in support of existing system clocking schemes.

The low jitter LVPECL interface guarantees compliance with the bit-error rate requirements of the Bellcore and ITU-T standards. The S3037 is packaged in a 10 mm 64 PQFP, offering designers a small package outline.

### Figure 1. System Block Diagram

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### SONET OVERVIEW

Synchronous Optical Network (SONET) is a standard for connecting one fiber system to another at the optical level. SONET, together with the Synchronous Digital Hierarchy (SDH) administered by the ITU-T, forms a single international standard for fiber interconnect between telephone networks of different countries. SONET is capable of accommodating a variety of transmission rates and applications.

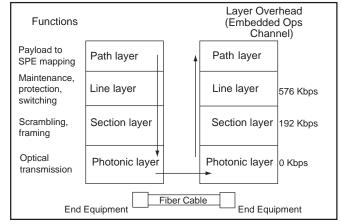

The SONET standard is a layered protocol with four separate layers defined. These are:

- Photonic

- Section

- Line

- Path

Figure 2 shows the layers and their functions. Each of the layers has overhead bandwidth dedicated to administration and maintenance. The photonic layer simply handles the conversion from electrical to optical and back with no overhead. It is responsible for transmitting the electrical signals in optical form over the physical media. The section layer handles the transport of the framed electrical signals across the optical cable from one end to the next. Key functions of this layer are framing, scrambling, and error monitoring. The line layer is responsible for the reliable transmission of the path layer information stream carrying voice, data, and video signals. Its main functions are synchronization, multiplexing, and reliable transport. The path layer is responsible for the actual transport of services at the appropriate signaling rates.

### **Data Rates and Signal Hierarchy**

Table 1 contains the data rates and signal designations of the SONET hierarchy. The lowest level is the basic SONET signal referred to as the synchronous transport

signal level-1 (STS-1). An STS-*N* signal is made up of *N* byte-interleaved STS-1 signals. The optical counterpart of each STS-*N* signal is an optical carrier level-*N* signal (OC-*N*). The S3037 chip supports OC-3 and OC-12 rates (155.52 and 622.08 Mbit/s).

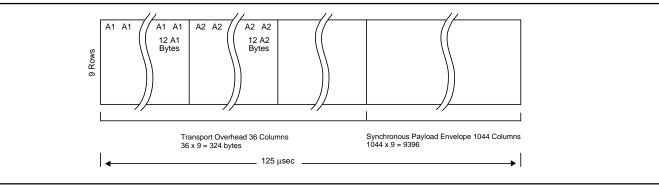

### Frame and Byte Boundary Detection

The SONET/SDH fundamental frame format for STS-12 consists of 36 transport overhead bytes followed by Synchronous Payload Envelope (SPE) bytes. This pattern of 36 overhead and 1044 SPE bytes is repeated nine times in each frame. Frame and byte boundaries are detected using the A1 and A2 bytes found in the transport overhead. (See Figure 3.)

For more details on SONET operations, refer to the Bellcore SONET standard document.

### Figure 2. SONET Structure

Table 1. SONET Signal Hierarchy

| Elec.  |        | Optical | Data Rate (Mbit/s) |

|--------|--------|---------|--------------------|

| STS-1  |        | OC-1    | 51.84              |

| STS-3  | STM-1  | OC-3    | 155.52             |

| STS-12 | STM-4  | OC-12   | 622.08             |

| STS-24 | STM-8  | OC-24   | 1244.16            |

| STS-48 | STM-16 | OC-48   | 2488.32            |

### S3037 OVERVIEW

The S3037 transceiver implements SONET/SDH serialization/deserialization, transmission, and frame detection/recovery functions. The block diagram in Figure 6 shows the basic operation of the chip. This chip can be used to implement the front end of SONET equipment, which consists primarily of the serial transmit interface and the serial receive interface. The chip handles all the functions of these two elements, including parallel-to-serial and serial-to-parallel conversion, clock generation and recovery, and system timing. The system timing circuitry consists of management of the data stream, framing, and clock distribution throughout the front end.

The S3037 is divided into a transmitter section and a receiver section. The sequence of operations is as follows:

Transmitter Operations:

- 1. 8-bit parallel input

- 2. Parallel-to-serial conversion

- 3. Serial output

Receiver Operations:

- 1. Clock and data recovery from serial input

- 2. Frame detection

- 3. Serial-to-parallel conversion

- 4. 8-bit parallel output

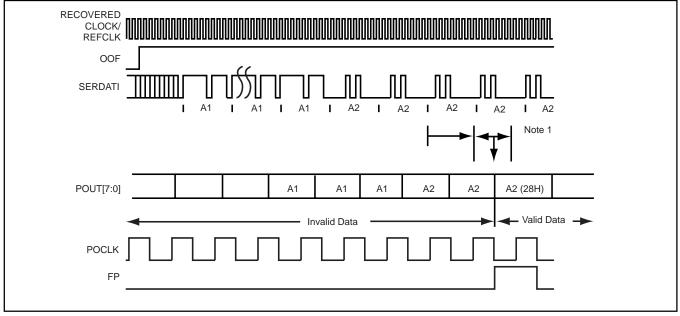

Internal clocking and control functions are transparent to the user. Details of data timing can be seen in Figures 10 through 15.

The S3037 supports clock recovery for the OC-12/ STM-4 or OC-3/STM-1 data rates. Differential serial data is input to the chip at the specified rate and clock recovery is performed on the incoming data stream. A reference clock is required to minimize the PLL lock time and provide a stable output clock source in the absence of serial input data. Retimed data and clock are output from the S3037.

#### Suggested Interface Devices

| AMCC CONGO | (S1201) POS/ATM SONET Mapper |

|------------|------------------------------|

| AMCC NILE  | (S1202) ATM SONET Mapper     |

### **CHARACTERISTICS**

#### Performance

The S3037 PLL complies with the jitter specifications proposed for SONET/SDH equipment defined by the T1X1.6/91-022 document, when used as specified.

#### **Jitter Transfer**

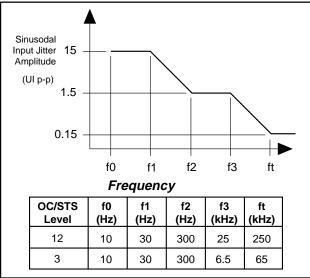

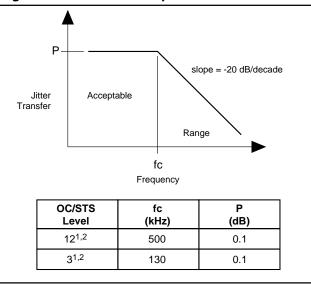

Jitter transfer function is defined as the ratio of jitter on the output OC-N/STS-N signal to the jitter applied on the input OC-N/STS-N signal versus frequency. Jitter transfer requirements are shown in Figure 5. The measurement condition is that input sinusoidal jitter up to the mask level in Figure 4 be applied for each of the OC-N/STS-N rates.

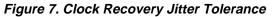

#### Input Jitter Tolerance

Input jitter tolerance is defined as the peak to peak amplitude of sinusoidal jitter applied on the input signal that causes an equivalent 1 dB optical/electrical power penalty. SONET input jitter tolerance requirements are shown in Figure 4. S3037 performance is shown in Table 2.

#### **Jitter Generation**

The jitter of the serial data outputs shall not exceed 0.01 UI rms when a serial data input with less than 14 ps (OC-12) or 56 ps (OC-3) rms jitter is presented to the serial data inputs.

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### Figure 4. Input Jitter Tolerance Specification

### Figure 5. Jitter Transfer Specification

1. Bellcore Specifications: TR-NWT-000253, Issue 2, December 1991.

2. CCITT Recommendations: G.958.

| Parameter                  | Min | Тур  | Мах | Units | Conditions          |

|----------------------------|-----|------|-----|-------|---------------------|

|                            | 0.4 | 0.65 |     | UI    | 250 kHz < f< 5 MHz  |

| Jitter Tolerance<br>STS-12 | 1.5 | 4    |     | UI    | 300 Hz < f< 25 kHz  |

|                            | 15  | 20   |     | UI    | 10 Hz < f< 30 Hz    |

|                            | 0.4 | 0.8  |     | UI    | 65 kHz < f< 1.3 MHz |

| Jitter Tolerance<br>STS-3  | 1.5 | 5    |     | UI    | 300 Hz < f< 6.5 kHz |

|                            | 15  | 22   |     | UI    | 10 Hz < f< 30 Hz    |

#### Table 2. Jitter Tolerance

Figure 6. S3037 Transceiver Functional Block Diagram

#### Transmitter ►TSDP/N 8 D PIN[7:0] 8:1 PARALLEL TO SERIAL PICLK · ► PCLK TIMING GEN RSTB LLEB SLPTIME CLOCK 0 SYNTHESIZER 1 TXCAP1 \_ TXCAP2 -MODE 0 -MODE 1 REFCLKP/N-レ TTLREF . Receiver 8 1:8 SERIAL ► POUT[7:0] TO PARALLEL TIMING OOF POCLK GEN FRAME RSTB BYTE RSTB DETECT ► FP DLEB RSDP/N · 1 BACKUP RSTB-REFERENCE 0 GEN 0 1 0 SDPECL TESTEN CLOCK AND DATA RECOVERY RXCAP1 ► RXCAP2 ł RSTB ·

S3037

### S3037 TRANSCEIVER FUNCTIONAL DESCRIPTION

### TRANSMITTER OPERATION

The S3037 transceiver chip performs the serializing stage in the processing of a transmit SONET STS-3 or STS-12 bit serial data stream. It converts the 8-bit parallel 19.44 or 77.76 Mbits/sec data stream into bit serial format at 155.52 or 622.08 Mbit/sec.

A high-frequency bit clock can be generated from a 19.44 or 77.76 MHz frequency reference by using an integral frequency synthesizer consisting of a phase-locked loop circuit with a divider in the loop.

Diagnostic loopback is provided (transmitter to receiver). See Other Operating Modes.

### **Clock Synthesizer**

The clock synthesizer, shown in the block diagram in Figure 6, is a monolithic PLL that generates the serial output clock phase synchronized with the input reference clock (REFCLKP/N or TTLREF).

The REFCLKP/N input must be generated from an LVPECL crystal oscillator which has a frequency accuracy that meets the values specified in Table 9 in order for the TSD frequency to have the same accuracy required for operation in a SONET system. Lower accuracy crystal oscillators may be used in applications less demanding than SONET/SDH. TTLREF must be at logic "one" if REFCLKP/N are used.

For TTL reference operation, the TTLREF input should be driven with an LVTTL crystal oscillator output with the ppm accuracy specified in Table 9 for SONET compliance. In this mode, REFCLKP should be connected to LVPECL "high" and REFCLKN should be tied to LVPECL "low."

Table 3. Reference Frequency Options

| MODE<br>[1:0] | REFERENCE CLOCK<br>FREQUENCY | OPERATING<br>MODE |

|---------------|------------------------------|-------------------|

| 00            | 19.44 MHz                    | STS-12            |

| 11            | 77.76 MHz                    | STS-12            |

| 01            | 19.44 MHz                    | STS-3             |

| 10            | 77.76 MHz                    | STS-3             |

The on-chip PLL consists of a phase detector, which compares the phase relationship between the VCO output and the REFCLKP/N input, a loop filter which converts the phase detector output into a smooth DC voltage, and a VCO, whose frequency is varied by this voltage.

The loop filter generates a VCO control voltage based on the average DC level of the phase discriminator output pulses. The loop filter's corner frequency is optimized to minimize output phase jitter.

### **Timing Generation**

The timing generation function, seen in Figure 6, provides a byte rate version of the transmit serial clock. This circuitry also provides an internally generated load signal, which transfers the PIN[7:0] data from the parallel input register to the serial shift register.

The PCLK output is a byte rate version of transmit serial clock at 19.44 or 77.76 MHz. PCLK is intended for use as a byte speed clock for upstream multiplexing and overhead processing circuits. Using PCLK for upstream circuits will ensure a stable frequency and phase relationship between the data coming into and leaving the S3037 device.

### Parallel-to-Serial Converter

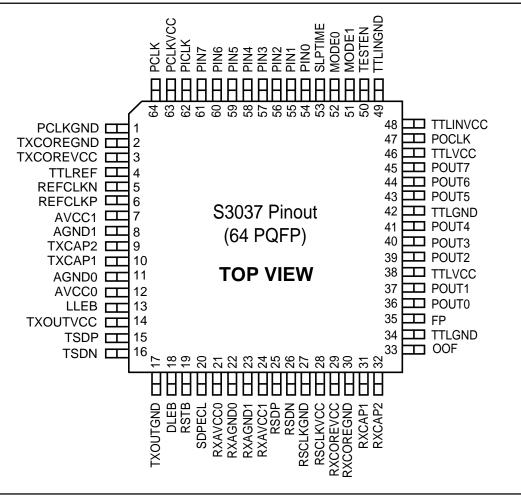

The parallel-to-serial converter shown in Figure 6 is comprised of two byte-wide registers. The first register latches the data from the PIN[7:0] bus on the rising edge of PICLK. The second register is a parallel loadable shift register which takes its parallel input from the first register.

The load signal, which latches the data from the parallel to the serial shift register, has a fixed relationship to PCLK. If PICLK is tied to PCLK, the PIN[7:0] data latched into the parallel register will meet the timing specifications with respect to the load signal. If PICLK is not tied to PCLK, the delay must meet the timing requirements shown in Figure 10.

Table 4. Reference Jitter Limits

| Frequency<br>Band | Maximum Reference<br>Clock Jitter | Operating<br>Mode |

|-------------------|-----------------------------------|-------------------|

| 12 kHz to 5 MHz   | 14 ps rms                         | STS-12            |

| 12 kHz to 1 MHz   | 56 ps rms                         | STS–3             |

### **RECEIVER OPERATION**

The S3037 transceiver chip provides the first stage of digital processing of a receive SONET STS-3 or STS-12 bit-serial stream. It converts the bit-serial 155.52 or 622.08 Mbit/sec data stream into a 19.44 or 77.76 Mbits 8-bit parallel data format.

Clock recovery is performed on the incoming scrambled NRZ data stream. A 19.44 or 77.76 MHz reference clock is required for phase locked loop start-up and proper operation under loss of signal conditions. An integral prescaler and phase locked loop circuit are used to multiply this reference to the nominal bit rate.

### **Clock Recovery**

Clock recovery, as shown in the block diagram in Figure 6, generates a clock that is at the same frequency as the incoming data bit rate at the RSD input or, in loopback, the transmitter data output. The clock is phase aligned by a PLL so that it samples the data in the center of the data eye pattern.

The phase relationship between the edge transitions of the data and those of the generated clock are compared by a phase/frequency discriminator. Output pulses from the discriminator indicate the required direction of phase corrections. These pulses are smoothed by an integral loop filter. The output of the loop filter controls the frequency of the Voltage Controlled Oscillator (VCO), which generates the recovered clock.

The loop filter transfer function is optimized to enable the PLL to track the jitter, yet tolerate the minimum transition density expected in a received SONET data signal. This transfer function yields the typical capture time stated in Table 9 for random incoming NRZ data. A single external clean-up capacitor is utilized as part of the loop filter.

The total loop dynamics of the clock recovery PLL yield a jitter tolerance which exceeds the minimum tolerance proposed for SONET equipment by the Bellcore TR-NWT-000253 standard, shown in Figure 7.

### Lock Detect

The S3037 contains a lock detect circuit which monitors the integrity of the serial data inputs. If the received serial data fails the frequency test, the PLL will be forced to lock to the local reference clock. This will maintain the correct frequency of the POCLK output under loss of signal or loss of lock conditions. If the recovered clock frequency deviates from the local reference clock frequency by more than the specified ppm, the PLL will go out of lock. The lock detect circuit will poll the input data stream in an attempt to reacquire lock to data. If the recovered clock frequency is determined to be within the specified ppm, the PLL will go into lock. The assertion of SDPECL will also cause an out-of-lock condition. See Table 9.

#### **Backup Reference Generator**

The backup reference generator seen in Figure 6 provides backup reference clock signals to the clock recovery block when the clock recovery block detects a loss of signal condition. It contains a counter that divides the clock output from the clock recovery block down to the same frequency as the reference clock.

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### Frame and Byte Boundary Detection

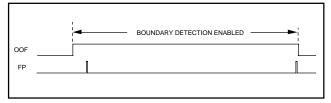

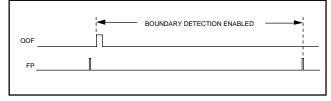

The frame and byte boundary detection circuitry searches the incoming data for three consecutive A1 bytes followed immediately by three consecutive A2 bytes. Framing pattern detection is enabled and disabled by the out-of-frame (OOF) input. Detection is enabled by a rising edge on OOF, and remains enabled for the duration that OOF is set High. It is disabled when a framing pattern is detected and OOF is no longer set High. When framing pattern detection is enabled, the framing pattern is used to locate byte and frame boundaries in the incoming data stream (RSD or looped transmitter data). The timing generator block takes the located byte boundary and uses it to block the incoming data stream into bytes for output on the parallel output data bus (POUT[7:0]). The frame boundary is reported on the Frame Pulse (FP) output when any 48-bit pattern matching the framing pattern is detected on the incoming data stream. When framing pattern detection is disabled, the byte boundary is frozen to the location found when detection was previously enabled. Only framing patterns aligned to the fixed byte boundary are indicated on the FP output.

The probability that random data in an STS-3 or STS-12 stream will generate the 48-bit framing pattern is extremely small. It is highly improbable that a mimic pattern would occur within one frame of data. Therefore, the time to match the first frame pattern and to verify it with down-stream circuitry, at the next occurrence of the pattern, is expected to be less than the required 250 µs, even for extremely high bit error rates.

Once down-stream overhead circuitry has verified that frame and byte synchronization are correct, the OOF input can be set Low to disable the frame search process from trying to synchronize to a mimic frame pattern. (See Figures 12-14.)

### Serial-to-Parallel Converter

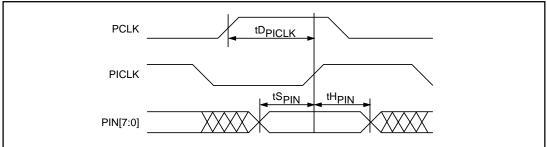

The serial-to-parallel converter consists of three 8-bit registers. The first is a serial-in, parallel-out shift register, which performs serial-to-parallel conversion clocked by the clock recovery block. The second is an 8-bit internal holding register, which transfers data from the serial-to-parallel register on byte boundaries as determined by the frame and byte boundary detection block. On the falling edge of the free running POCLK, the data in the holding register is transferred to an output holding register which drives POUTP/N[7:0].

The delay through the Serial to Parallel converter can vary from 1.5 to 2.5 byte periods (12 to 20 serial bit periods) measured from the first bit of an incoming byte to the beginning of the parallel output of that byte. The variation in the delay is dependent on the alignment of the internal parallel load timing, which is synchronized to the data byte boundaries, with respect to the falling edge of POCLK, which is independent of the byte boundaries. The advantage of this serial-to-parallel converter is that POCLK is neither truncated nor extended during reframe sequences.

### OTHER OPERATING MODES

### **Diagnostic Loopback**

When the Diagnostic Loopback Enable (DLEB) input is active, a loopback from the transmitter to the receiver at the serial data rate can be set up for diagnostic purposes.

The differential serial output data from the transmitter is routed to the clock recovery unit and serial-to-parallel block in place of the normal Receive Data Stream (RSD). In Diagnostic Loopback mode the SDPECL input is ignored.

### Line Loopback

When Line Loopback Enable (LLEB) is active, a loopback from the receiver to the transmitter at the serial data rate can be set up for facility loopback testing. The recovered clock is used to retime the incoming data before driving the TSDP/N outputs. In line loopback mode the SDPECL input is ignored.

### Serial Loop Timing

In Serial Loop Timing (SLPTIME) mode, the clock synthesizer PLL of the S3037 is bypassed, and the timing of the entire transmitter section is controlled by the recovered receive serial clock. This mode is entered by using the SLPTIME input.

In this mode the REFCLKP/N, TTLREF, and MODE[1:0] inputs are ignored for all transmit functions.

### **Forward Clocking**

For both 77.78 MHz and 19.44 MHz reference operation, the S3037 operates in the forward clocking mode. The PLL locks the PCLK output of the transmitter section to the reference clock with a fixed and repeatable phase relationship. This allows the transmitter data source to also be the timing source for the serial clock synthesis. (See Figure 15.)

#

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

S3037

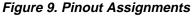

Table 5. S3037 Transmitter Pin Assignment and Descriptions (Active High unless otherwise stated.)

| Pin Name                                                     | Level           | I/O | Pin #                                        | Description                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------|-----------------|-----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN7<br>PIN6<br>PIN5<br>PIN4<br>PIN3<br>PIN2<br>PIN1<br>PIN0 | LVTTL           | Ι   | 61<br>60<br>59<br>58<br>57<br>56<br>55<br>54 | Parallel Data Input. A 77.76 Mbits/s or 19.44 Mbits/s, aligned to<br>the PICLK parallel input clock. PIN[7] is the most significant bit<br>(corresponding to bit 1 of each PCM word, the first bit<br>transmitted). PIN[0] is the least significant bit (corresponding to<br>bit 8 of each PCM word, the last bit transmitted). PIN[7:0] is<br>sampled on the rising edge of PICLK. |

| PICLK                                                        | LVTTL           | I   | 62                                           | Parallel Input Clock. A 77.76 or 19.44 MHz, nominally 50% duty cycle input clock, to which PIN[0] is aligned. PICLK is used to transfer the data on the PIN inputs into a holding register in the parallel-to-serial converter. The rising edge of PICLK samples PIN[7:0].                                                                                                          |

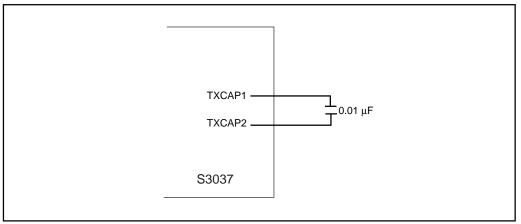

| TXCAP1<br>TXCAP2                                             | Analog          | I   | 10<br>9                                      | Loop Filter Capacitor. The TX loop filter capacitor is connected to these pins. See Figure 16.                                                                                                                                                                                                                                                                                      |

| TSDP<br>TSDN                                                 | Diff.<br>LVPECL | 0   | 15<br>16                                     | Transmit Serial Data. Differential LVPECL serial data stream signals, normally connected to an optical transmitter module.                                                                                                                                                                                                                                                          |

| PCLK                                                         | LVTTL           | 0   | 64                                           | Parallel Clock. A reference clock generated by dividing the internal bit clock by eight. It is normally used to coordinate byte-wide transfers between upstream logic and the S3037 device.                                                                                                                                                                                         |

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

|--|

| Pin Name                                                             | Level           | I/O | Pin #                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------|-----------------|-----|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSDP<br>RSDN                                                         | Diff.<br>LVPECL | I   | 25<br>26                                     | Receive Serial Data. Stream signals normally connected to an optical receiver module. A clock is recovered from transitions on the RSD inputs.                                                                                                                                                                                                                                                                                                                                  |

| OOF                                                                  | LVTTL           | I   | 33                                           | Out Of Frame Indicator used to enable framing pattern detection<br>logic in the S3037. The framing pattern detection logic is<br>enabled by a rising edge on OOF, and remains enabled until<br>frame boundary is detected or when OOF is set Low, whichever<br>is longer. OOF is an asynchronous signal with a minimum pulse<br>width of one POCLK period. (See Figures 12 through 14.)                                                                                         |

| SDPECL                                                               | LVPECL          | I   | 20                                           | Signal Detect. LVPECL with internal pull-down. Active High. A single-ended 10k LVPECL input to be driven by the external optical receiver module to indicate a loss of received optical power. When SDPECL is inactive, the data on the Serial Data In (RSDP/N) pins will be internally forced to a constant zero. When SDPECL is active, data on the RSDP/N pins will be processed normally.                                                                                   |

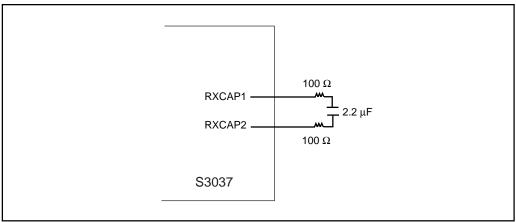

| RXCAP1<br>RXCAP2                                                     | Analog          | I   | 31<br>32                                     | Loop Filter Capacitor. The RX loop filter capacitor and resistors are connected to these pins. See Figure 17.                                                                                                                                                                                                                                                                                                                                                                   |

| POUT7<br>POUT6<br>POUT5<br>POUT4<br>POUT3<br>POUT2<br>POUT1<br>POUT0 | LVTTL           | 0   | 45<br>44<br>43<br>41<br>40<br>39<br>37<br>36 | Parallel Data Output bus. A 77.76 Mbit/s or 19.44 Mbit/s, aligned to the POCLK parallel output clock. POUT[7] is the most significant bit (corresponding to bit 1 of each PCM word, the first bit received). POUT[0] is the least significant bit (corresponding to bit 8 of each PCM word, the last bit received). POUT[7:0] is updated on the falling edge of POCLK.                                                                                                          |

| FP                                                                   | LVTTL           | 0   | 35                                           | Frame Pulse. Indicates frame boundaries in the incoming data<br>stream (RSD). If framing pattern detection is enabled, as<br>controlled by the OOF input, FP pulses High for one POCLK<br>cycle when a 48-bit sequence matching the framing is detected<br>on the RSD inputs. When framing pattern detection is disabled,<br>FP pulses High when the incoming data stream, after byte<br>alignment, matches the framing pattern. FP is updated on the<br>falling edge of POCLK. |

| POCLK                                                                | LVTTL           | 0   | 47                                           | Parallel Output Clock. A 77.76 or 19.44 MHz, nominally 50% duty cycle, byte rate output clock that is aligned to POUT[7:0] byte serial output data. POUT[7:0] and FP are updated on the falling edge of POCLK.                                                                                                                                                                                                                                                                  |

| Table 7. S3037 Common Pin Assignment and Descriptions | (Active High unless otherwise stated.) |

|-------------------------------------------------------|----------------------------------------|

|-------------------------------------------------------|----------------------------------------|

| Pin Name           | Level           | I/O | Pin #    | Description                                                                                                                                                                                                                              |

|--------------------|-----------------|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTEN             | LVTTL           | I   | 50       | Test Clock Enable Signal. Active High. Set High to bypass the PLL during production tests.                                                                                                                                               |

| REFCLKP<br>REFCLKN | Diff.<br>LVPECL | I   | 6<br>5   | Reference Clock Input. Used as the reference for the internal bit clock frequency synthesizer. REFCLKP must be connected to a logic one and REFCLKN to a logic zero state if TTLREF is used.                                             |

| TTLREF             | LVTTL           | I   | 4        | TTL Reference Clock input that can be used as the reference<br>for the internal bit clock frequency synthesizer. (Must be tied<br>High if REFCLKP/N is used).                                                                            |

| DLEB               | LVTTL           | I   | 18       | Diagnostic Loopback Enable. Active Low. Selects diagnostic<br>loopback. When DLEB is High, the S3037 device uses the<br>primary data (RSD) inputs. When Low, the S3037 device uses<br>the diagnostic loopback data from the transmitter. |

| RSTB               | LVTTL           | I   | 19       | Master Reset. Reset input for the device. Active Low. Initializes the device to a known state for production testing. Tie High for normal operation.                                                                                     |

| LLEB               | LVTTL           | I   | 13       | Line Loopback Enable. Active Low. Selects line loopback. When LLEB is Low, the S3037 will route the retimed serial data from the receive section to the transmitter outputs.                                                             |

| MODE1<br>MODE0     | LVTTL           | I   | 51<br>52 | Operating Mode select inputs. Used to select the reference clock frequency and the operating speed (see Table 3). Also used for test.                                                                                                    |

| SLPTIME            | LVTTL           | I   | 53       | Serial Clock Loop Time Select input. Active High. Used to<br>enable the recovered clock from the receive section to be used<br>in place of the synthesized transmit clock.                                                               |

S3037

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

| Pin Name  | Level | I/O | Pin #    | Description  |

|-----------|-------|-----|----------|--------------|

| RXAVCC0,1 | 3.3 V |     | 21<br>24 | Power Supply |

| RXAGND0,1 | GND   |     | 22<br>23 | Ground (0 V) |

| RSCLKGND  | GND   |     | 27       | Ground (0 V) |

| RSCLKVCC  | 3.3 V |     | 28       | Power Supply |

| RXCOREVCC | 3.3 V |     | 29       | Power Supply |

| RXCOREGND | GND   |     | 30       | Ground (0 V) |

| TTLGND    | GND   |     | 34<br>42 | Ground (0 V) |

| TTLINGND  | GND   |     | 49       | Ground (0 V) |

| TTLVCC    | 3.3 V |     | 38<br>46 | Power Supply |

| TTLINVCC  | 3.3 V |     | 48       | Power Supply |

| PCLKVCC   | 3.3 V |     | 63       | Power Supply |

| PCLKGND   | GND   |     | 1        | Ground (0 V) |

| TXCOREVCC | 3.3 V |     | 3        | Power Supply |

| TXCOREGND | GND   |     | 2        | Ground (0 V) |

| AGND0,1   | GND   |     | 11<br>8  | Ground (0 V) |

| AVCC0,1   | 3.3 V |     | 12<br>7  | Power Supply |

| TXOUTVCC  | 3.3 V |     | 14       | Power Supply |

| TXOUTGND  | GND   |     | 17       | Ground (0 V) |

### Table 8. S3037 Power and Ground Pin Assignments

#

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### S3037

### Figure 8. 64 PQFP Package

## SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### Table 9. Performance Specifications

| Parameter                                                                                                                                   | Min | Тур                | Max                              | Units     | Conditions                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|----------------------------------|-----------|--------------------------------------------------------------------------------------------------|

| Nominal VCO<br>Center Frequency                                                                                                             |     | 622.08             |                                  | MHz       |                                                                                                  |

| Data Output Jitter<br><b>STS-12</b><br>-19.44 MHz Ref Clk<br>-77.76 MHz Ref Clk<br><b>STS-3</b><br>-19.44 MHz Ref Clk<br>-77.76 MHz Ref Clk |     |                    | 0.007<br>0.004<br>0.003<br>0.002 | UI (rms)  | rms jitter, in lock                                                                              |

| Reference Clock<br>Frequency Tolerance                                                                                                      | -20 |                    | +20                              | ppm       | Required to meet SONET output<br>frequency specification                                         |

| OC-3/STS-3 and<br>OC-12/STS-12<br>Capture Range<br>Lock Range<br>Capture Time                                                               |     | ±200<br>±12%<br>32 |                                  | ppm<br>µs | With respect to fixed reference frequency                                                        |

| Acquisition Lock Time                                                                                                                       |     |                    | 16                               | μs        | Minimum transition density of 20%<br>With device already powered up and<br>valid reference clock |

| Reference Clock<br>Input Duty Cycle                                                                                                         | 40  |                    | 60                               | % of UI   |                                                                                                  |

| Reference Clock Rise & Fall Times                                                                                                           |     |                    | 2.0                              | ns        | 20% to 80% of amplitude                                                                          |

| LVPECL Output Rise & Fall Times                                                                                                             |     |                    | 450                              | ps        | 20% to 80%, 50 $\Omega$ load, 5 pF cap                                                           |

| Frequency difference at<br>which PLL goes out of<br>lock (REFCLK<br>compared to the divided<br>down VCO clock).                             | 340 | 610                | 732                              | ppm       | Previously in lock.                                                                              |

| Frequency difference at<br>which receive PLL goes<br>into lock (REFCLK<br>compared to the divided<br>down VCO clock).                       | 244 | 305                | 366                              | ppm       | Previously out of lock.                                                                          |

| OC-12/STS-12<br>Jitter Tolerance                                                                                                            | 0.4 |                    |                                  | UI        | Sinusoidal input jitter. Amplitude on<br>SERDATIP/N data inputs from 250<br>kHz to 5 MHz.        |

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### Table 10. Absolute Maximum Ratings

| Parameter                               | Min  | Тур | Max             | Units |

|-----------------------------------------|------|-----|-----------------|-------|

| Storage Temperature                     | -65  |     | 150             | °C    |

| Voltage on $V_{cc}$ with Respect to GND | -0.5 |     | +5.0            | V     |

| Voltage on any LVTTL Input Pin          | -0.5 |     | +5.5            | V     |

| Voltage on any LVPECL Input Pin         | 0    |     | V <sub>cc</sub> | V     |

| LVTTL Output Sink Current               |      |     | 8               | mA    |

| LVTTL Output Source Current             |      |     | 8               | mA    |

| High Speed LVPECL Output Source Current |      |     | 50              | mA    |

### **ESD** Ratings

The S3037 is rated to the following ESD voltages based on the human body model:

1. All pins are rated at or above 1000 V except Pin1, Pin10, Pin31, and Pin32.

### Table 11. Recommended Operating Conditions

| Parameter                                                         | Min        | Тур | Max   | Units |

|-------------------------------------------------------------------|------------|-----|-------|-------|

| Ambient Temperature Under Bias                                    | 0          |     | 70    | °C    |

| Voltage on V <sub>cc</sub> with Respect to GND<br>3.3 V Operation | 3.135      | 3.3 | 3.465 | V     |

| Voltage on any LVTTL Input Pin                                    | 0          |     | 5.5   | V     |

| Voltage on any LVPECL Input Pin                                   | VCC<br>-2V |     | VCC   | V     |

| ICC Supply Current                                                |            |     | 350   | mA    |

| PD Power Dissipation                                              |            |     | 1.21  | W     |

### Table 12. LVTTL Input/Output DC Characteristics

| Parameter       | Description               | Min        | Тур | Мах                    | Units  | Conditions                                                           |  |

|-----------------|---------------------------|------------|-----|------------------------|--------|----------------------------------------------------------------------|--|

| V <sub>OH</sub> | Output High Voltage (TTL) | 2.1<br>2.2 |     |                        | V<br>V | $V_{CC} = min, I_{OH} = -2.4 mA$<br>$V_{CC} = min, I_{OH} = -0.1 mA$ |  |

| V <sub>OL</sub> | Output Low Voltage (TTL)  |            |     | 0.5                    | V      | $V_{\rm CC}$ = min, $I_{\rm OL}$ = 2.4 mA                            |  |

| V <sub>IH</sub> | Input High Voltage (TTL)  | 2.0        |     | TTL<br>V <sub>cc</sub> | V      | $I_{_{\rm H}} @ 1 \text{ mA at } V_{_{\rm IH}} = 5.5 \text{ V}$      |  |

| V <sub>IL</sub> | Input Low Voltage (TTL)   | 0          |     | 0.8                    | V      |                                                                      |  |

| I <sub>IH</sub> | Input High Current (TTL)  |            |     | 20                     | μA     | V <sub>IN</sub> = 2.4 V                                              |  |

| I <sub>IL</sub> | Input Low Current (TTL)   | -500       |     |                        | μA     | V <sub>IN</sub> = 0.5 V                                              |  |

S3037

**4MC**

### Table 13. LVPECL Input/Output DC Characteristics

| Parameter            | Description                      | Min                       | Тур   | Max                       | Units | Conditions                                                  |

|----------------------|----------------------------------|---------------------------|-------|---------------------------|-------|-------------------------------------------------------------|

| V <sub>IL</sub>      | Input Low Voltage                | V <sub>cc</sub><br>-2.000 |       | V <sub>cc</sub><br>–1.441 | V     | Guaranteed Input Low<br>Voltage for single-ended<br>inputs  |

| V <sub>IH</sub>      | Input High Voltage               | V <sub>cc</sub><br>–1.225 |       | V <sub>cc</sub><br>-0.570 | V     | Guaranteed Input High<br>Voltage for single-ended<br>inputs |

| V <sub>IL</sub>      | Input Low Voltage                | V <sub>cc</sub><br>-2.000 |       | V <sub>cc</sub><br>-0.700 | V     | Guaranteed Input Low<br>Voltage for differential<br>inputs  |

| V <sub>IH</sub>      | Input High Voltage               | V <sub>cc</sub><br>–1.750 |       | V <sub>cc</sub><br>-0.450 | V     | Guaranteed Input High<br>Voltage for differential<br>inputs |

| V <sub>ID</sub>      | Input Differential Voltage       | 0.200                     | 0.500 | 1.400                     | V     | Differential Input Voltage                                  |

| I <sub>IHD</sub>     | Differential Input High Current  | -0.500                    |       | 20.000                    | μA    | V <sub>ID</sub> = 500 mV                                    |

| I <sub>ILD</sub>     | Differential Input Low Current   | -0.500                    |       | 20.000                    | μA    | V <sub>ID</sub> = 500 mV                                    |

| I <sub>IH</sub>      | Single Ended Input High Current  |                           |       | 100                       | μA    | SD Input has internal<br>24k to 1.8 V load<br>resistor      |

| I <sub>IL</sub>      | Single Ended Input Low Current   |                           |       | -100                      | μA    | SD Input has internal<br>24k to 1.8 V load<br>resistor      |

| V <sub>ol</sub>      | Output Low Voltage <sup>1</sup>  | V <sub>cc</sub><br>-2.000 |       | V <sub>cc</sub><br>-1.500 | V     | 50 $\Omega$ termination to $V_{cc}$ –2 V                    |

| V <sub>OH</sub>      | Output High Voltage <sup>1</sup> | V <sub>cc</sub><br>–1.110 |       | V <sub>cc</sub><br>-0.670 | V     | 50 $\Omega$ termination to V <sub>cc</sub> –2 V             |

| V <sub>od</sub>      | Output Differential Voltage      | 0.800                     |       | 2.66                      | V     | 50 $\Omega$ termination to V <sub>cc</sub> –2 V             |

| V <sub>OSINGLE</sub> | Output Single Ended Voltage      | 0.400                     |       | 1.330                     | V     | 50 $\Omega$ termination to V <sub>cc</sub> –2 V             |

1. Output macros are 10k PECL equivalent.

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### Table 14. Transmitter AC Timing Characteristics

| Parameter           | Description                       | Min | Мах | Units |

|---------------------|-----------------------------------|-----|-----|-------|

| tD <sub>PICLK</sub> | PICLK Delay from PCLK             | 0   | 5.5 | ns    |

| tS <sub>PIN</sub>   | PIN [7:0] Setup Time w.r.t. PICLK | 1.5 |     | ns    |

| tH <sub>PIN</sub>   | PIN [7:0] Hold Time w.r.t. PICLK  | 1.0 |     | ns    |

### Table 15. Receiver AC Timing Characteristics

| Parameter          | Description                                                                                             | Min      | Мах    | Units    |

|--------------------|---------------------------------------------------------------------------------------------------------|----------|--------|----------|

|                    | POCLK Duty Cycle                                                                                        | 40       | 60     | %        |

| tP <sub>POUT</sub> | POCLK Low to POUT [7:0] Valid Prop. Delay @ STS-3<br>POCLK Low to POUT [7:0] Valid Prop. Delay @ STS-12 | -8<br>-3 | 0<br>1 | ns<br>ns |

| tS <sub>POUT</sub> | POUT [7:0] and FP Setup Time w.r.t. POCLK <sup>1</sup>                                                  | 4        |        | ns       |

| tH <sub>POUT</sub> | POUT [7:0] and FP Hold Time w.r.t. POCLK <sup>1</sup>                                                   | 3        |        | ns       |

1. Setup and hold times are specified for an interface which directly connects the S3037 receiver parallel outputs to the data and clock inputs on an external register.

### Figure 10. PIN AC Input Timing

- 1. When a setup time is specified on LVTTL signals between an input and a clock, the setup time is the time in nanoseconds from the 50% crossover point of the input to the 50% crossover point of the clock.

- 2. When a hold time is specified on LVTTL signals between an input and a clock, the hold time is the time in nanoseconds from the 50% crossover point of the clock to the 50% crossover point of the input.

Notes on Output Timing:

- 1. Output propagation delay time of LVTTL outputs is the time in nanoseconds from the 50% crossover point of the reference signal to the 30% or 70% point of the output.

- 2. Maximum output propagation delays of LVTTL outputs are measured with a 15 pF load on the outputs.

S303

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

### **RECEIVER FRAMING**

Figure 12 shows a typical reframe sequence in which a byte realignment is made. The frame and byte boundary detection is enabled by the rising edge of OOF and remains enabled while OOF is High. Both boundaries are recognized upon receipt of the third A2 byte which is the first data byte to be reported with the correct byte alignment on the outgoing data bus (POUT[7:0]). Concurrently, the frame pulse is set High for one POCLK cycle.

When interfacing with a section terminating device, the OOF input remains High for one full frame after the first frame pulse while the section terminating device verifies internally that the frame and byte alignment are correct, as shown in Figure 13. Since at least one framing pattern has been detected since the rising edge of OOF, boundary detection is disabled when OOF is set Low. The frame and byte boundary detection block is activated by the rising edge of OOF, and stays active until the first FP pulse or until OOF goes Low, whichever occurs last. Figure 12 shows a typical OOF timing pattern which occurs when the S3037 is connected to a down stream section terminating device. OOF remains High for one full frame after the first FP pulse. The frame and byte boundary detection block is active until OOF goes Low.

Figure 14 shows the frame and byte boundary detection activation by a rising edge of OOF, and deactivated by the first FP pulse.

### Figure 12. Frame and Byte Boundary Detection

1. Range of input to output delay can be 1.5 to 2.5 POCLK cycles.

#### Figure 13. OOF Operation Timing

### Figure 14. Alternate OOF Timing

### S3037 WITH DATA CLOCK SYNCHRONOUS TO REFERENCE CLOCK

In some applications it is necessary to "forward clock" the data in a SONET/SDH system. In this application the reference clock from which the High speed serial clock is synthesized and the parallel data clock both originate from the same (usually TTL/CMOS) clock source. This application note explains how the AMCC S3037 can be configured to operate in this mode.

### **Clock Control Logic Description**

The timing control logic in the S3037 automatically generates an internal load signal which has a fixed relationship to the reference clock. The logic takes into account the variation of the reference clock to the internal load signal over temperature and voltage.

The connections required to implement the design are shown in Figure 15. The setup and hold times for the PICLK to the data must be met by the controller ASIC. It is recommended that latching the data on the falling edge of the output reference clock be latched in order to meet the required specifications.

### **Possible Problems**

In order to meet the jitter generation specifications required by SONET, the jitter of the reference clock must be minimized. It may be difficult to meet the SONET jitter generation specifications using a reference clock input with a TTL reference source.

### **Power Sequencing**

When the S3037 is operated with a 5 volt controller such as the PMC5355 SUNI, it is recommended that power be applied to the S3037 before or simultaneously (time difference less than 1 ms) with the application of power to the 5 volt controller. If this condition cannot be met, series resistance of at least 33  $\Omega$  is required on all TTL inputs driven from the 5 volt environment.

Please note that 33  $\Omega$  is already recommended on dynamically switching input signals such as PIN[7:0], OOF, PICLK, and TTL REF to limit overshoot and ringing. Static control lines such as LLEB, DLEB, SLPTIME, MODE[1:0], and RSTB should also be provided with series resistors of at least 33  $\Omega$  (100 Ohms recommended) to limit input current if the 5 volt environment is powered while the 3.3 volt VCC of the S3037 is off.

# SONET/SDH/ATM OC-3/12 TRANSCEIVER W/CDR

Figure 16. Transmitter Loop Filter Capacitor Connections

### Figure 17. Receiver Loop Filter Capacitor Connections

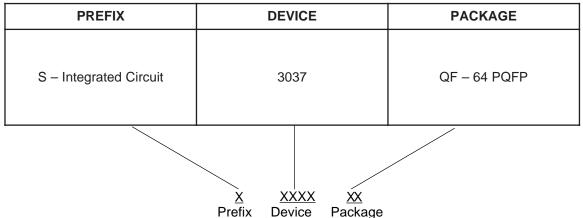

#### **Ordering Information**

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (858) 450-9333 • (800) 755-2622 • Fax: (858) 450-9885

http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation. Copyright ® 1999 Applied Micro Circuits Corporation