C3052 C3053 C3054 C3057

## CMOS Monolithic Serial Interface PCM Codec/Filter Family

#### General Description

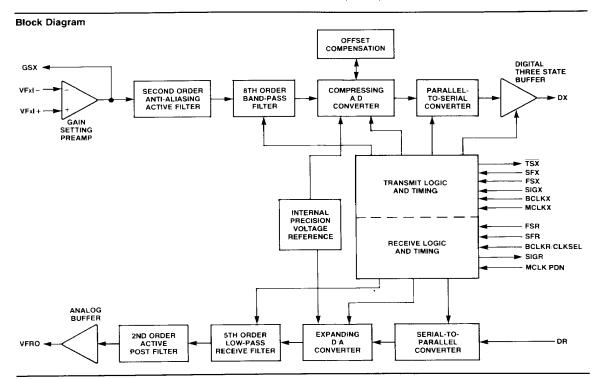

CMD's family of CMOS monolithic  $\mu$ -law and A-law CODEC filter circuits provide precision A/D and D/A signal conversion as well as the transmit and receive filtering required for companded PCM systems. Within each device, the encode section features an input gain adjust amplifier, an active RC anti-aliasing filter, offset compensation circuitry, and a switchedcapacitor band-pass filter for rejecting frequencies outside a 200 to 3400 Hz band. Filtered signals are sampled and encoded into the compressed  $\mu$ -law or A-law format and shifted out through the serial interface. The decode section features an expanding decoder for reconstructing the μ-law or A-law encoded signal, a low-pass filter with Sin x/x correction followed by an active RC smoothing filter, and a output power amplifier capable of driving low impedance loads. All devices within the CMD CODEC/filter family meet or exceed AT&T D3/D4 and CCITT specifications, and are manufactured using CMD's state-of-the-art CMOS process technology for increased noise immunity, higher reliability and reduced power consumption.

#### Features

- Four complete CODEC/filtering systems:

- C3052 μ-law with signaling (18 pin version)

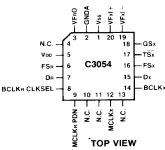

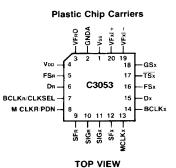

- C3053  $\mu$ -law with signaling (20 pin version)

- C3054  $\mu$ -law without signaling (16 pin version) C3057 A-law (16 pin version)

- Pin compatible with industry standard (3052,53,54.57) Low power CMOS design; 60 mW operating (typ), 3 mW standby (typ)

- Low-pass and high-pass transmit filtering

- Receive low-pass filtering with Sin x/x correction

- Resistor programmable gain setting preamp for transmit section

- Synchronous or asynchronous transmit and receive operation

- Serial I/O interface

- 1.536 MHz, 1.544 MHz, or 2.048 MHz master clock timing; variable bit clock timing from 64 KHz to 2.048 MHz

- Short and long frame sync timing

- Active RC anti-aliasing and post filters

- Precision internal voltage reference and offset compensation circuits

- Automatic power-down by removing frame sync's and/or single pin nower-down

- TTL or CMOS compatible interface

- ± 5V power input

#### Pin Function Table

| ₽in              | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vss              | Negative power supply. Vss = 5V ± 5%                                                                                                                                                                                                                                                                                                                                                         |

| GRND             | Ground reference for all signals. Internally connected to both analog and digital ground.                                                                                                                                                                                                                                                                                                    |

| VFRO             | Receive channel analog output.                                                                                                                                                                                                                                                                                                                                                               |

| Voo              | Positive power supply. Vpo = +5V ± 5%                                                                                                                                                                                                                                                                                                                                                        |

| FSR              | Receive channel 8 KHz frame synchronization pulse input. Sync'd with receive bit clock, this signal determines when PCM data is to be shifted into the receive channel data input, DR. This pin may also be used to specify short frame sync receive signaling frames in the 18 and 20 pin signaling devices (C3052 and C3053).                                                              |

| DR               | Receive channel data input. PCM data will be clocked into DR on the eight consecutive clocks of BCLKR following the FSR rising edge. See timing diagrams.                                                                                                                                                                                                                                    |

| BCLKR/<br>CLKSEL | Receive channel bit clock input. BCLKR is used to shift PCM data into the receive channel data input, DR. BCLKR may vary from 64 KHz to 2.048 MHz but must be synchronous with MCLKR and FSR. In synchronous operation, this pin is used as a logic input to specify the master clock frequency (Table 1). In this case, BCLKX is used for both the transmit and receive channel bit clocks. |

| MCLKR/<br>PDN    | Receive channel master clock input. MCLKR must be 1.536 MHz, 1.544 MHz, or 2.048 MHz. In synchronous operation, this pin is used as a power-down control. In this case, MCLKX is used for both transmit and receive master clocks and MCLKR.PDN is connected continuously low. When MCLKR.PDN is connected high, the device is powered down.                                                 |

| MCLKX            | Transmit channel master clock input. May be 1.536 MHz, 1.544 MHz, or 2.048 MHz. In synchronous operation, MCLKX is used for all internal master clock timing (both transmit and receive).                                                                                                                                                                                                    |

| BCLKX            | Transmit channel bit clock input. BCLKX is used to shift out the PCM data at the transmit channel output, DX. BCLKX may vary from 64 KHz to 2.048 MHz, but must be synchronous with MCLKX and FSX. In synchronous operation, BCLKX is used for all internal bit clock timing (both transmit and receive).                                                                                    |

| Pin    | Description                                                                                                                                                                                                                                                                                                                         |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DX     | Transmit channel data output. PCM data is shifted out of this three-state output on the eight consecutive transmit bit clocks following a rising edge of FSX. See timing diagrams.                                                                                                                                                  |

| FSX    | Transmit channel 8 KHz frame synchronization pulse input. Sync'd with BCLKX, this signal determines when the encoded PCM data is shifted out the transmit channel data output, DX. This pin may also be used to specify short frame sync transmit signaling frames in the 18 and 20 pin signaling devices (C3052 and C3053).        |

| TSX    | Transmit channel timeslot indicator output. This active low open drain output pulses low during output of valid transmit data.                                                                                                                                                                                                      |

| GSX    | Analog output of the transmit channel input gain-<br>adjust amplifier. GSX may be used to externally<br>set gain of the transmit channel. Connected<br>externally to VFxI – for a gain of 1.                                                                                                                                        |

| VFxI · | Inverting input to the transmit channel input gain-adjust amplifier.                                                                                                                                                                                                                                                                |

| VFxI+  | Non-inverting input to the transmit channel input gain-adjust amplifier.                                                                                                                                                                                                                                                            |

| SIGR   | Receive channel signaling bit output. During a receive signaling frame, the eighth bit of the incoming PCM data is output at SIGR. This output pin is only used in the 18 and 20 pin signaling devices (C3052 and C3053).                                                                                                           |

| SIGX   | Transmit channel signaling bit input. During a transmit signaling frame, data at this input is transmitted as the eighth bit of the PCM word at the transmit data output, DX. This input pin is only used in the 18 and 20 pin signaling devices (C3052 and C3053). If not used, this pin should be left open circuit or tied high. |

| SFR    | Receive channel signaling frame sync input. This pin is only used in the 20 pin signaling version (C3053). It is used to specify a long frame sync receive signaling frame. When high during FSR, the eighth bit of the incoming PCM word is output at SIGR. If not used, this pin should be left open circuit or tied low.         |

| SFX    | Transmit channel signaling frame sync input. This pin is only used in the 20 pin signaling version (C3053). It is used to specify a long frame sync transmit signaling frame. When high during FSX, data at SIGX is inserted into the eighth bit of the PCM word. If not used, this pin should be left open circuit or tied low.    |

### Pin Configurations (Continued)

# Plastic Chip Carriers

#### VEX. -VE ٧ss N.C. 18 GSx 17 ·TS C3052 16 ·FSx Dr 15 Dx BCLKR/CLKSEL BCLKx SIGR MCLKR: PDN Š MCLKX O TOP VIEW

**Plastic Chip Carriers**

### **Functional Description**

## Power-up/Power-down

When power is first applied, this device immediately goes into powerdown mode. In power-down mode, all circuits except those required for power-up are deactivated and DX and VF<sub>R</sub>O outputs are placed in high impedance states. Minimum power is consumed in this mode as the device waits to power up.

In synchronous operation, the device can be powered up by pulsing FSX and/or FSR while applying a TTL or CMOS low level to MCLKR/PDN. In asynchronous operation, the device is powered up by pulsing FSX and/or FSR while a clock is applied to the MCLKR/PDN pin. In either case, the PCM data output, DX, will be valid after the second FSX pulse.

The device is automatically powered down in the absence of both FSX and FSR pulses. Approximately 1.5 ms after both FSX and FSR are continuously low, the device goes into power-down mode. In addition, the device can be powered down at any time by applying a TTL or CMOS high level to the MCLKR:PDN pin.

## Synchronous and Asynchronous Operation

The C3052 series CODEC/filters may operate in synchronous or asynchronous mode. Synchronous operation is when MCLKX and BCLKX are used as the master clocks and bit clocks, respectively, for both the transmit and receive channels. This allows MCLKR/PDN to be used as a power-down control and BCLKR/CLKSEL to be used to specify the master clock frequency. Internal circuitry detects if clocks are present on MCLKR/PDN and BCLKR/CLKSEL and if not, MCLKX and BCLKX are automatically used for both transmit and receive sections. MCLKX may be 1.536 MHz, 1.544 MHz, or 2.048 MHz. BCLKX may be from 64 KHz to 2.048 MHz.

Asynchronous operation is when separate transmit and receive master clocks and transmit and receive bit clocks are applied. In this mode, MCLKX and MCLKR must be 1.536 MHz or 1.544 MHz for the  $\mu$ -law devices, and must be 2.048 MHz for the A-law devices. BCLKX and BCLKR may vary from 64 KHz to 2.048 MHz.

In either mode of operation, FSX must be synchronous with BCLKX and MCLKX. FSR must be synchronous with BCLKR and MCLKR. When operating in the synchronous mode, the BCLKR-CLKSEL pin should be used to specify the master clock frequencies. If the master clock frequency is 1.536 MHz or 1.544 MHz, BCLKR/CLKSEL should be connected high for  $\mu$ -law devices and low for A-law devices. If the master clock frequency is 2.048 MHz, BCLKR/CLKSEL should be connected low for  $\mu$ -law and high for A-law. If the BCLKR/CLKSEL input is being clocked, the master clock must be 1.536 MHz or 1.544 MHz for  $\mu$ -law and 2.048 MHz for A-law. The following table summarizes what the master clock frequencies must be depending on the state of the BCLKR/CLKSEL pin.

Table 1. Master clock frequency specification

| BCLKR/CLKSEL |                  | Master clock frequency  |  |  |  |  |  |

|--------------|------------------|-------------------------|--|--|--|--|--|

| 1            | (μ-law versions) | 1.536 MHz or 1.544 MHz* |  |  |  |  |  |

| 0            | (μ-law versions) | 2.048 MHz               |  |  |  |  |  |

| clocked      | (μ-law versions) | 1.536 MHz or 1.544 MHz  |  |  |  |  |  |

| 1            | (A-law version)  | 2.048 MHz               |  |  |  |  |  |

| 0            | (A-law version)  | 1.536 MHz or 1.544 MHz  |  |  |  |  |  |

| clocked      | (A-law version)  | 2.048 MHz               |  |  |  |  |  |

<sup>\*</sup>Note that the device automatically compensates for the 193rd clock pulse in each frame for the 1.544 MHz master clock.

#### Short and Long Frame Sync's

The CODEC/filter will operate with either short or long frame sync pulses. A short frame sync pulse is one bit clock period long (or two, for short frame signaling). A long frame sync pulse is three or more bit clock periods long. Upon power initialization, the device assumes short frame sync timing. The CODEC/filter will use the transmit frame sync pulse, FSX, to determine whether short or long frame sync's are being applied. Thus both transmit and receive channels must use the same length frame sync pulse. All 4 versions of the CODEC/filter operate in either short or long frame mode. Details of short and long frame timing are specified in the 'CODEC/filter Timing' section.

#### Signaling

The C3052 and the C3053 CODEC/filters contain circuitry to extract signaling information in the PCM data stream. During a transmit signaling frame, the encoder encodes the incoming analog signal and inserts the data present on the SIGX pin in place of the least significant (eighth) bit of the encoded PCM word. The 7 encoded bits of the PCM word and the signaling bit are shifted out through DX. Similarly, during a receive signaling frame, the least significant bit of the PCM word read in from DR, is latched and stored on the SIGR output pin until updated at the end of the next signaling frame. The decoder interprets the tost LSB as "1/2" to minimize noise and distortion.

Signaling in short frame sync mode may be performed by either the 18 pin signaling device (C3052) or the 20 pin signaling device (C3053). If the 20 pin signaling device is used, then pins SFX and SFR are not used and must be connected low or left open circuit. A frame sync pulse two bit clock periods long is used to indicate a signaling frame.

Signaling in long frame sync mode can only be performed by using the 20 pin signaling device (C3053). The two extra pins, SFX and SFR, are used to indicate signaling frames. A pulse on SFX indicates a transmit signaling frame and a pulse on SFR indicates a receive signaling frame.

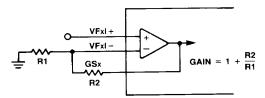

### Transmit Channel Operation

Gain Setting Input Amplifier — The transmit channel input is a gain setting input amplifier which can be used for passband gain adjustment (see Figure 1). It can be connected to provide a gain of 20 dB without degrading the noise performance of the filter. The amplifier can be used in the inverting or differential amplifier mode.

## **Functional Description (Continued)**

Figure 1. Transmit Filter Gain Adjustment

Transmit Filter — Before the incoming analog signal is sampled and encoded, a transmit filter bandlimits the signal to 4 KHz and rejects any 50 Hz and 60 Hz components. A minimum attenuation of 30 dB and 26 dB is provided at 50 Hz and 60 Hz, respectively. The transmit filter consists of an active RC anti-aliasing filter followed by an 8th order switched capacitor bandpass filter. The bandpass filter consists of a 5th order lowpass and 3rd order highpass section. The transmit filter provides a passband flatness and stopband attenuation which exceeds the Bell D3 and D4 specifications as well as the CCITT G.712 recommendations.

$\mu\text{-law/A-law}$  Encoder — The encoding begins with the transmit frame sync pulse, FSX. The output of the transmit filter is sampled and held on a switched capacitor array. An analog to digital conversion is then performed according to  $\mu\text{-law}$  (C3052, C3053, C3054) or A-law (C3057 coding conventions (see Table 2). Any DC offset due to the filters or comparator is cancelled by an on-chip offset compensation circuit. The offset compensation circuit uses a sign bit integration technique where the sign bit is averaged over a long time to compute the offset which is then subtracted from the input to the encoder. The encoded 8-bit PCM word is clocked out of DX at the beginning of the next encode cycle. The open drain TSX output pulses low during valid DX data.

#### **Receive Channel Operation**

$\mu\text{-law/A-law}$  Decoder — The decoding begins with the receive frame sync pulse, FSR. The 8-bit PCM word is serially latched in at DR on eight consecutive receive bit clocks. A digital to analog conversion is then performed on the PCM data according to the  $\mu\text{-law}$  or A-law format.

Receive Lowpass Filter — The output of the D/A converter is followed by a 5th order lowpass switched capacitor filter clocked at 128 KHz. This filter performs the required lowpass filtering and sin x/x correction necessary to accurately recover the original analog signal. The filter provides passband flatness and stopband rejection which fulfills or exceeds the Bell D3 and D4 specifications and the CCITT G.172 recommendations. The 5th order lowpass filter is followed by an active RC lowpass smoothing filter.

Output Power Amplifier — The receive channel analog output is a low impedance power amplifier capable of driving loads as low as 600 ohms.

#### Precision Voltage Reference

The CODEC/filter devices are equipped with an on-chip temperature and power supply stable bandgap voltage reference. The bandgap voltage reference supplies individual references to both the transmit and receive channels for extremely accurate gain responses.

Table 2. μ-law/A-law Encoding Format

| Input at GSx                   | μ-law           | A-law (1) |

|--------------------------------|-----------------|-----------|

| Vin = + Full Scale (2)         | 10000000        | 10101010  |

| V <sub>in</sub> = + 0 volts    | 11111111        | 11010101  |

| V <sub>in</sub> = - 0 volts    | 0 1 1 1 1 1 1 1 | 01010101  |

| V <sub>in</sub> = - Full Scale | 00000000        | 00101010  |

- A-law includes even bit inversion for transmission.

- Full Scale is 2.5V.

#### CODEC/filter Timing

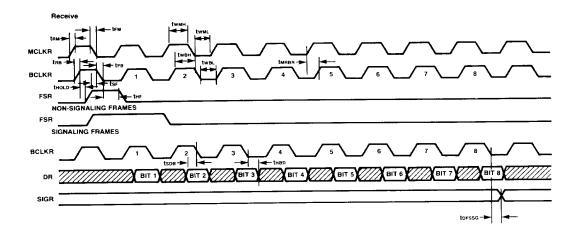

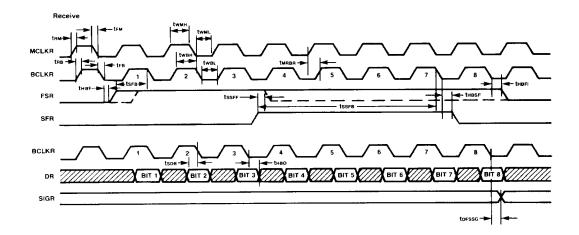

## Transmit Channel, Short Frame Sync Timing

FSX must be one or two bit clock periods long and must go high while BCLKX is high. On the first rising edge of BCLKX after FSX, DX is enabled and the sign bit is output. The next seven BCLKX rising edges output the remaining seven bits (MSB to LSB). The following BCLKX rising edge disables the DX output. In a signaling frame, FSX is a two bit clock periods long and the signaling bit is transmitted in place of the LSB. The signaling bit at SIGX must be valid at least 100 ns before and 50 ns after the seventh BCLKX falling edge.

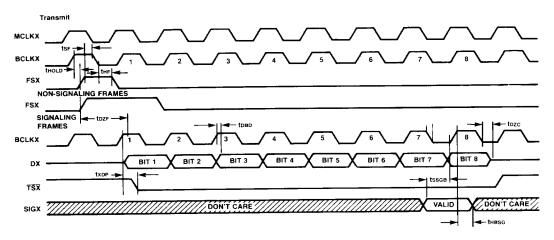

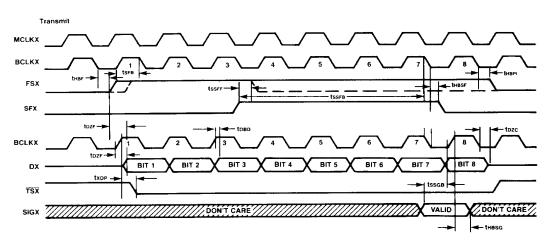

## Transmit Channel, Long Frame Sync Timing

FSX must be three or more bit clock periods long. When BCLKX is 64 KHz, FSX must be low for a minimum of 160 ns. FSX may go high while BCLKX is high or low. The rising edge of FSX or the rising edge of BCLKX, whichever comes later, enables the DX output and clocks out the sign bit. The next seven BCLKX rising edges clock out the remaining seven bits. The DX output is disabled by the eighth BCLKX falling edge or by FSX going low, whichever comes later. If the signaling frame sync pulse, SFX, is present, the signaling bit is transmitted in place of the LSB. The signaling data bit must be valid at least 100 ns before and 50 ns after the 7th BCLKR falling edge. SFX must be high at least 60 ns before the falling edge of FSX. In addition, it must be high at least 60 ns before and 100 ns after the seventh BCLKX falling edge.

## Receive Channel, Short Frame Sync Timing

FSR must be one or two bit clock periods long. FSR must go high while BCLKR (or BCLKX, if BCLKR is not clocked) is high. With FSR high during a falling edge of BCLKR, the next falling edge of BCLKR latches in the sign bit. The following seven BCLKR falling edges latch in the remaining seven bits (MSB to LSB). If FSR is two bit clock periods long, the last bit latched in from DR is stored at SIGR within 300 ns after the eighth BCLKR falling edge.

## Receive Channel, Long Frame Sync Timing

FSR must be three or more bit clock periods long. If BCLKR is 64 KHz, FSR must be low for at least 160 ns. FSR may go high while BCLKR is high or low. The first falling edge of BCLKR after the FSR risinge dge latches in the sign bit. The next seven BCLKR falling edges latch in the remaining seven bits. If the signaling frame sync pulse, SFR, is present, the last bit latched in from DR is stored at SIGR within 300 ns after the 8th BCLKR falling edge. SFR must be high at least 60 ns before the FSR falling edge. It must also be high at least 60 ns before and 100 ns after the seventh BCLKR falling edge.

## **Timing Specifications**

| Parameter                                                                               | Symbol        | Min | Тур                                              | Max   | Units | Conditions                                               |

|-----------------------------------------------------------------------------------------|---------------|-----|--------------------------------------------------|-------|-------|----------------------------------------------------------|

| Master Clocks                                                                           | 1 -           |     |                                                  |       |       | MCLKX or MCLKR                                           |

| Frequency                                                                               | 1/tpm         |     | 1.536                                            |       | MHz   |                                                          |

| requests                                                                                |               |     | 1.544                                            | 1     | MHz   |                                                          |

|                                                                                         |               |     | 2.048                                            |       | MHz   |                                                          |

| Width of High                                                                           | twmH          | 160 |                                                  | ļ     | nS    |                                                          |

| Width of Low                                                                            | twmL          | 160 | 1                                                |       | nS    |                                                          |

|                                                                                         | trm           | 100 |                                                  | 50    | nS    |                                                          |

| Rise Time                                                                               | L I           |     |                                                  | 50    | nS    |                                                          |

| Fall Time                                                                               | tFM           |     | <del> </del>                                     | - 30  |       |                                                          |

| Bit Clocks                                                                              |               |     | 1                                                |       | _     | BCLKX or BCLKR                                           |

| Period                                                                                  | tPB           | 485 | 488                                              | 15725 | nS    |                                                          |

| Width of High                                                                           | twan          | 160 |                                                  |       | nS nS |                                                          |

| Width of Low                                                                            | twaL          | 160 |                                                  |       | nS    |                                                          |

| Rise Time                                                                               | tras          |     |                                                  | 50    | nS    |                                                          |

| Fall Time                                                                               | tғв           |     |                                                  | 50    | nS    |                                                          |

| Time from MCLKX/R Rising edge to                                                        | <b>I</b> MRBR | 0   |                                                  |       | nS    |                                                          |

| BCLKX/R Rising Edge                                                                     |               |     | <b>_</b>                                         |       |       |                                                          |

| Hold Time from Bit Clock<br>High to Frame Sync Rising Edge                              | THOLD         | 0   |                                                  |       | nS    | Short Frame Mode Only                                    |

| Set-Up Time from Frame Sync<br>High to Bit Clock Falling Edge                           | tsr           | 50  |                                                  |       | nS    | Short Frame Mode Only                                    |

| Hold Time from Bit Clock                                                                | the           | 100 |                                                  |       | nS    | Short Frame Mode Only                                    |

| Low to Frame Sync Falling Edge                                                          | UNF           |     |                                                  |       |       |                                                          |

| Hold Time from Bit Clock<br>Low to Frame Sync Rising Edge                               | tнвғ          | 0   |                                                  |       | nS    | Long Frame Mode Only                                     |

| Set-Up Time from Frame Sync                                                             | tsfB          | 80  |                                                  |       | nS    | Long Frame Mode Only                                     |

| High to Bit Clock Falling Edge Hold Time from Bit Clock                                 | ther          | 100 | <del>                                     </del> |       | nS    | Long Frame Mode Only,                                    |

| Low to Frame Sync Falling Edge                                                          |               |     |                                                  |       |       | After 3rd Bit Clock Period                               |

| Minimum Width of FSX or FSR Low Level                                                   | twFL          | 160 |                                                  |       | nS    | Long Frame Mode Only,<br>64 KHz Bit Clocks               |

| Delay Time from 1st BCLKX<br>High to TSX Low                                            | txpp          |     |                                                  | 140   | nS    | Load = 150 pF plus<br>2 LSTTL Loads                      |

| Delay Time from FSX or<br>BCLKX Rising Edge, Whichever<br>Comes Later, to DX Data Valid | tozr          | 20  |                                                  | 165   | nS    | 1st Data Bit Only,<br>CL = 0 pF to 150 pF                |

| Delay Time from BCLKX High<br>to DX Data Valid                                          | toso          | 0   |                                                  | 180   | nS    | Load = 150 pF plus<br>2 LSTTL Loads                      |

| Delay Time from 8th BCLKX<br>Low to DX Data Output Disabled                             | tozc          | 50  |                                                  | 165   | nS    |                                                          |

| Set-Up Time from DR Valid to BCLKR falling Edge                                         | tsdb          | 50  |                                                  |       | nS    |                                                          |

| Hold Time from BCLKR<br>Low to DR Invalid                                               | tнво          | 50  |                                                  |       | nS    |                                                          |

| Set-Up Time from SIGX Valid to 7th BCLKX Falling Edge                                   | tssga         | 100 |                                                  |       | nS    | C3052 and C3053 Only                                     |

| Hold Time from 7th BCLKX Falling to SIGX Invalid                                        | these         | 50  |                                                  |       | nS    | C3052 and C3053 Only                                     |

| Delay Time from 8th BCLKR<br>Low to SIGR Valid                                          | torssg        |     |                                                  | 300   | nS    | C3052 and C3053 Only,<br>Load = 50 pF plus 2 LSTTL Loads |

| Set-Up Time from SFX/R<br>High to FSX/R Falling Edge                                    | tssff         | 60  |                                                  |       | nS    | C3053 Only                                               |

| Set-Up Time from SFX/R High to 7th BCLKX/R Falling Edge                                 | tssfb         | 60  |                                                  |       | nS    | C3053 Only                                               |

| Hold Time from 7th BCLKX/R<br>Low to SFX/R Falling Edge                                 | these         | 100 |                                                  |       | nS    | C3053 Only                                               |

Figure 2. Short Frame Sync Timing

Figure 3. Long Frame Sync Timing

## **Absolute Maximum Ratings:**

Exceeding these ratings may result in permanent damage. Functional operation under these conditions is not implied.

| Parameter                                 | Symbol | Value                                               |

|-------------------------------------------|--------|-----------------------------------------------------|

| Vpp with respect to GRND                  | VDDC   | 7V                                                  |

| Vss with respect to GRND                  | Vssc   | 7V                                                  |

| Voltage at any Analog Input or Output     | VAMAX  | V <sub>DD</sub> + 0.3V to<br>V <sub>SS</sub> - 0.3V |

| Voltage at any Digital Input<br>or Output | VDMAX  | V <sub>DD</sub> ± 0.3V to<br>GRND = 0.3V            |

| Operating Temperature                     | TA     | - 25°C to + 125°C                                   |

| Storage Temperature                       | Ts     | -65°C to +150°C                                     |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated values.

## DC and Operating Characteristics:

Unless otherwise noted: GRND = 0V,  $V_{DD} = +5V$ ,  $V_{SS} = -5V$ ,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$

| Parameter                          | Symbol                 | Min            | Тур         | Max          | Units  | Test Conditions           |

|------------------------------------|------------------------|----------------|-------------|--------------|--------|---------------------------|

| Operating Supply Voltages          | V <sub>DD</sub><br>Vss | 4.75<br>- 5.25 | 5.0<br>-5.0 | 5.25<br>4.75 | V<br>V | Ref. to GRND              |

| V <sub>DD</sub> Power-down Current | lopo                   |                | 0.5         | 1.5          | mA     | Device in Power-down Mode |

| Vss Power-down Current             | Isso                   |                | 0.05        | 0.3          | mA     | Device in Power-down Mode |

| Von Operating Current              | IDD1                   |                | 6.0         | 9.0          | mA     | Active Operation          |

| Vss Operating Current              | Issı                   |                | 6.0         | 9.0          | mA     | Active Operation          |

## Digital Interface

| Input Low Voltage                       | VIL | i i        | 0.6               | V           | All Digital Inputs                                                         |

|-----------------------------------------|-----|------------|-------------------|-------------|----------------------------------------------------------------------------|

| Input High Voltage                      | Vін | 2.2        |                   | ٧           | All Digital Inputs                                                         |

| Output Low Voltage<br>SIGR<br>DX<br>TSX | Vol |            | 0.4<br>0.4<br>0.4 | V<br>V<br>V | I = 1.0 mA<br>I = 3.2 mA<br>I = 3.2 mA, Open Drain                         |

| Output High Voltage<br>SIGR<br>DX       | Vон | 2.4<br>2.4 |                   | V<br>V      | I = -1.0 mA<br>I = 3.2 mA                                                  |

| Input Low Current                       | hi  | 10         | 10                | μΑ          | All Digital Inputs,<br>GRND ≲ Vin ≲ Vil                                    |

| Input High Current                      | lін | - 10       | 10                | μА          | All Digital Inputs,<br>V <sub>IH</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub> |

| High Impedance State Output Current     | loz | - 10       | 10                | μΑ          | DX output,<br>GRND ≤ Vout ≤ Vbb                                            |

## Transmit Filter Gain Setting Input Amplifier

| Input Leakage Current, VFxI + , VFxI - | lex   | 200   | 200 | nA     | 2.5V % Vin % 2.5V   |

|----------------------------------------|-------|-------|-----|--------|---------------------|

| Input Resistance, VFxI+, VFxI-         | Rix   | 10    |     | M ohms | -2.5V ≤ ViN ≤ 2.5V  |

| Input Offset Voltage, VFxI - , VFxI -  | Vosx  | - 20  | 20  | mV     |                     |

| Common Mode Rejection, VFxI+, VFxI     | CMRR× | 60    |     | dB     | - 2.5V ≤ ViN ≤ 2.5V |

| Common Mode Range, VFxI                | Vcmx  | - 2.5 | 2.5 | V      |                     |

| Power Supply Rejection, GSx            | PSRRx | 60    |     | dB     |                     |

| DC Open Loop Voltage Gain, GSx         | Avolx | 70    |     | dB     |                     |

| Open Loop Unity Gain Bandwidth, GSx    | fc    | 1.0   |     | MHz    |                     |

| Output Voltage Swing, GSx              | Vox   | ± 2.8 |     | V      | R∟ ≥ 10K ohms       |

| Load Capacitance, GSx                  | CLX   |       | 50  | pF     |                     |

| Minimum Load Resistance, GSx           | RLX   | 10    |     | K ohms |                     |

## DC and Operating Point Characteristics (Continued)

| Parameter                       | Symbol | Min  | Тур | Max | Units | Test Conditions |

|---------------------------------|--------|------|-----|-----|-------|-----------------|

| Receive Filter Output Amplifier |        |      |     |     |       | <u> </u>        |

| Output Resistance, VFRO         | Ron    |      | 1   | 3   | ohms  |                 |

| Minimum Load Resistance, VFRO   | RLR    | 600  |     |     | ohms  | VFnO = ± 2.5V   |

| Load Capacitance, VFnO          | Сія    |      |     | 500 | ρF    |                 |

| DC Output Offset Voltage, VFnO  | Vosa   | -200 |     | 200 | mV    |                 |

## Transmit Channel Transmission Characteristics:

Unless otherwise noted: TA =  $0^{\circ}$ C to  $70^{\circ}$ C, V<sub>DD</sub> = 5V  $\pm$  5%, V<sub>SS</sub> = -5V  $\pm$  5%, GRND = 0V, f = 1020 Hz, VFxI + = 0 dBmO, transmit pain setting input amplifier set for non-inverting unity gain.

| Parameter                                                                                                                     | Symbol                  | Min                                | Тур | Max                                                                | Units                                        | Test Conditions                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------|-----|--------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute gain at 1020 Hz                                                                                                      | Gax                     | - 0.15                             |     | 0.15                                                               | dB                                           | 0 dBmO Input Signal<br>TA = 25°C, V <sub>DD</sub> = 5V, V <sub>SS</sub> = -5'<br>Nominal 0 dBmO level is<br>4 dBm (600 ohms) = 1.2276 V <sub>rms</sub>                                      |

| Frequency Response 16 Hz 50 Hz 60 Hz 200 Hz 300 Hz to 3000 Hz 3300 Hz 3400 Hz 4000 Hz 4600 Hz 4600 Hz and Above               | GRX                     | - 1.8<br>- 0.15<br>- 0.35<br>- 0.7 |     | - 38<br>- 30<br>- 26<br>- 0.1<br>0.15<br>0.05<br>0<br>- 14<br>- 32 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB | Gain Relative to Gain at<br>1020 Hz, 0 dBmO Input Signal                                                                                                                                    |

| Gain Variation with Temperature at 1020 Hz                                                                                    | GAXT                    | - 0.1                              |     | 0.1                                                                | dB                                           | 0 dBmO Input Signal                                                                                                                                                                         |

| Gain Variation with Supplies at 1020 Hz                                                                                       | Gaxs                    | - 0.05                             |     | 0.05                                                               | dB                                           | 0 dBmO Input Signal<br>Supplies = ± 5%                                                                                                                                                      |

| Gain Variation with Level at 1020 Hz VFxl + = -40 dBmO to +3 dBmO VFxl + = -50 dBmO to -40 dBmO VFxl + = -55 dBmO to -50 dBmO | Gaxl                    | - 0.2<br>- 0.4<br>- 1.2            |     | 0.2<br>0.4<br>1.2                                                  | dB<br>dB<br>dB                               | Reference Level = -10 dBmO<br>Sinusoidal Test Method                                                                                                                                        |

| V <sub>DD</sub> Power Supply Rejection Vss Power Supply Rejection                                                             | PPSRx<br>NPSRx          | 40<br>40                           |     |                                                                    | dBC<br>dBC                                   | 100 mV <sub>ms</sub> at f Hz added to Vno $f=0$ KHz to 50 KHz Vno = 5.0V, VFxI+ = $-30$ dBm 100 mV <sub>ms</sub> at f Hz added to Vss $f=0$ KHz to 50 KHz Vss = $-5.0$ V, VFxI+ = $-30$ dBm |

| C Message Idle Channel Noise                                                                                                  | Nxc                     |                                    | 12  | 15                                                                 | dBrnCO                                       | C3052, C3053, C3054<br>VFxI+ = -50 dBm                                                                                                                                                      |

| P Message Idle Channel Noise                                                                                                  | Nxp                     |                                    | 74  | - 69                                                               | dBmOp                                        | C3057<br>VFxI + = -50 dBm                                                                                                                                                                   |

| Crosstalk, Receive to Transmit                                                                                                | CTRX                    |                                    | 90  | - 70                                                               | dB                                           | 0 dBmO Receive PCM Level<br>f = 300 Hz to 3400 Hz<br>VFxI + = -30 dBm                                                                                                                       |

| Signal to Total Distortion  VFxI + - 3 dBmO  VFxI + = 0 dBmO to -30 dBmO  VFxI +40 dBmO  VFxI + = -55 dBmO                    | STDX                    | 33<br>36<br>29<br>14               |     |                                                                    | dBC<br>dBC<br>dBC<br>dBC                     | Sinusoidal Test Method                                                                                                                                                                      |

| Harmonic Distortion                                                                                                           | D2HDX<br>D3HDX          |                                    |     | - 46<br>- 46                                                       | dB<br>dB                                     | 1020 Hz 0 dBmO Input Signal<br>Measure 2nd harmonic<br>Measure 3rd harmonic                                                                                                                 |

| Absolute Envelope Delay Delay Relative to DAX  f = 500-1000 Hz f = 1000-1600 Hz f = 1600-2600 Hz f = 2600-3000 Hz             | DAX<br>DAX <sub>R</sub> |                                    |     | 315<br>220<br>75<br>105<br>155                                     | μS<br>μS<br>μS<br>μS                         | f = 1600 Hz, dØ/dW  Deviation of envelope delay at freq. f, from that at 1600 Hz                                                                                                            |

Receive Channel Transmission Characteristics:

Unless otherwise noted:  $TA = 0^{\circ}C$  to  $70^{\circ}C$ ,  $VDD = 5V \pm 5\%$ ,  $VSS = -5V \pm 5\%$ , GRND = 0V, PCM code = Ideally encoded 0 dBmO Signal at

| Parameter                                                                                                                                          | Symbol         | Min                              | Тур | Max                       | Units                        | Test Conditions                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|-----|---------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute gain at 1020 Hz                                                                                                                           | GAR            | -0.15                            |     | 0.15                      | dB                           | 0 dBmO PCM Level $T_A=25^{\circ}C,\ V_{DD}=5V,\ Vss=-5V$ Nominal 0 dBmO Level is 4 dBm (600 ohms) = 1.2276 $V_{rms}$                                                                        |

| Frequency Response<br>0 Hz to 3000 Hz<br>3300 Hz<br>3400 Hz<br>4000 Hz                                                                             | Gar            | - 0.15<br>- 0.35<br>- 0.7        |     | 0.15<br>0.05<br>0<br>- 14 | dB<br>dB<br>dB<br>dB         | Gain Relative to Gain at 1020 Hz<br>0 dBmO PCM Level                                                                                                                                        |

| Gain Variation with Temperature at 1020 Hz                                                                                                         | GART           | - 0.1                            |     | 0.1                       | dB                           | 0 dBmO PCM Level                                                                                                                                                                            |

| Gain Variation with Supplies at 1020 Hz                                                                                                            | GARS           | - 0.05                           |     | 0.05                      | dB                           | 0 dBmO PCM Level<br>Supplies = ± 5%                                                                                                                                                         |

| Gain Variation with Level at 1020 Hz  PCM Level = -40 dBmO to +3 dBmO  PCM Level = -50 dBmO to -40 dBmO  PCM Level = -55 dBmO to -50 dBmO          | GARL           | - 0.2<br>0.4<br>1.2              |     | 0.2<br>0.4<br>1.2         | dB<br>dB<br>dB               | Reference Level = Ideally<br>encoded - 10 dBmO Signal at<br>1020 Hz<br>Sinusoidal Test Method                                                                                               |

| Receive Output Level                                                                                                                               | VRO            | - 2.5                            |     | 2.5                       | Volts                        | RL = 600 ohms                                                                                                                                                                               |

| V <sub>DD</sub> Power Supply Rejection 0 Hz to 4000 Hz 4 KHz to 25 KHz 25 KHz to 50 KHz Vss Power Supply Rejection 0 Hz to 4000 Hz 4 KHz to 25 KHz | PPSRR<br>NPSRR | 40<br>40<br>36<br>40<br>40<br>36 |     |                           | dBC<br>dB<br>dB<br>dBC<br>dB | 100 mV <sub>rms</sub> at f Hz added to Voo<br>V <sub>DD</sub> = 5.0V, PCM code = positive<br>zero<br>100 mV <sub>rms</sub> at f Hz added to Vss<br>Vss = -5.0V, PCM code =<br>positive zero |

| 25 KHz to 50 KHz                                                                                                                                   | NRC1           |                                  | 8   | 11                        | dBrnCO                       | C3052, C3053, C3054                                                                                                                                                                         |

| C Message Idle Channel Noise  P Message Idle Channel Noise                                                                                         | NRC2           |                                  | -82 | 12<br>- 79                | dBrnCO<br>dBmOp              | -50 dBm activation signal<br>C3052, C3053, C3054<br>PCM code = alternating<br>positive and negative zero<br>C3057<br>-50 dBm activation signal                                              |

| Crosstalk, Transmit to Receive                                                                                                                     | CTRR           |                                  | 90  | - 75                      | dB                           | 0 dBmO Transmit Input Signal<br>f = 300 Hz to 3400 Hz<br>DR = steady PCM code                                                                                                               |

| Signal to Total Distortion PCM Level = 3 dBmO PCM Level = 0 dBmO to -30 dBmO PCM Level = -40 dBmO PCM Level = -55 dBmO                             | STOR           | 33<br>36<br>30<br>15             |     |                           | dBC<br>dBC<br>dBC<br>dBC     | Sinusoidal Test Method                                                                                                                                                                      |

| Harmonic Distortion                                                                                                                                | D2HDR<br>D3HDR |                                  |     | - 46<br>- 46              | dB<br>dB                     | 1020 Hz, 0 dBmO PCM Code<br>Measure 2nd Harmonic<br>Measure 3rd Harmonic                                                                                                                    |

| Absolute Envelope Delay Delay Relative to DAR f = 500-1000 Hz f = 1000-1600 Hz f = 1600-2600 Hz f = 2600-3000 Hz                                   | DAR<br>DARR    | -40<br>-30                       |     | 200<br>125<br>175         | μS<br>μS<br>μS<br>μS         | f = 1600 Hz, DAR = dØ/dW  Deviation of Envelope Delay at freq. f to that of 1600 Hz                                                                                                         |

| Spurious Out-of-band Signals at the Channel Output f = 4600 Hz to 7600 Hz f = 7600 Hz to 8400 Hz f = 8400 Hz to 100 KHz                            | SOS            |                                  |     | - 32<br>- 40<br>- 32      | dB<br>dB<br>dB               | Loop Around Measurement<br>Apply 0 dBmO, 300 Hz-3400 Hz<br>signal at VFxI+, Measure at VF                                                                                                   |

| Intermodulation (Non-linear) Distortion                                                                                                            | IMD            |                                  |     | - 52                      | dB                           | Bell System 4 Tone Method per<br>Bell System Technical Ref.<br>#41009                                                                                                                       |

## **Applications**

The primary applications for the C3052 Family is in telephone systems:

- Switching Digital PBX's and Central Office Switching Systems

Transmission D3:D4 Type Channel Banks and Subscriber Carrier Systems

- Subscriber Instruments Digital Handsets and Office Workstations

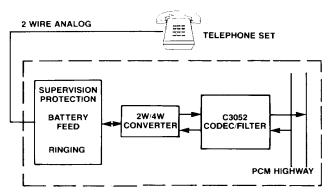

Figure 4. Typical Line Termination for Channel Bank