|   | 28 mW max-Standby                                                                   |

|---|-------------------------------------------------------------------------------------|

|   | 19 mW max-Self refresh                                                              |

|   | TTL-compatible                                                                      |

|   | 28-pin SRAM/ROM/EPROM compatible packa                                              |

|   | Built-in refresh multiplexer and refresh address<br>counter                         |

|   | Power-down self-refresh mode                                                        |

|   | Automatic precharge allows cycle time to be in<br>pendent of system skews           |

|   | Latched address, CS, and OE functions allow                                         |

| - | on multiplexed address/data bus                                                     |

|   | Read, early write, late write, external refresh, p refresh, and self-refresh cycles |

## **Performance Ranges**

Low power dissipation:

| Device      | †CEA   | LOEA  | tc     | ı  |

|-------------|--------|-------|--------|----|

| μPD4168C-12 | 120 ns | 45 ns | 220 ns | 65 |

| PD4168C−15  | 150 ns | 55 ns | 260 ns | 60 |

| ₽D4168C-20  | 200 ns | 70 ns | 330 ns | 55 |

| Standby                 | Н  | Н  | х |

|-------------------------|----|----|---|

| Power down self-refresh | L  | Н  | X |

|                         | C' | C' | н |

|                         | C' | C' | Н |

|                         | C' | C' | Н |

|                         | C' | C, | н |

| Pulse refresh           | C' | Н  | Х |

|                         | Н  | C, | L |

| External refresh        | Н  | C, | Н |

| Late Write              | Н  | C, | Н |

| Early write             | Н  | C, | Н |

|                         |    |    |   |

$H=V_{ijkl},\ L=V_{jjkl},\ C'=$  negative edge of clock pulse,  $X=V_{ijkl}$  or  $V_{ijkl}$

## Note:

(1) Depends on previous cycle

## **Absolute Maximum Ratings**

| Voltage on any pin relative to GND            | -1.0  |

|-----------------------------------------------|-------|

| Operating temperature, Topp                   | 0     |

| Storage temperature, T <sub>STG</sub>         | -55 t |

| Short circuit output current, 1 <sub>OS</sub> |       |

| Power dissipation, P <sub>D</sub>             |       |

Comment: Exposing the device to stresses above those listed lute Maximum Ratings could cause permanent damage. The not meant to be operated under conditions outside the liscribed in the operational sections of the specification. Exp absolute maximum rating conditions for extended periods make device reliability.

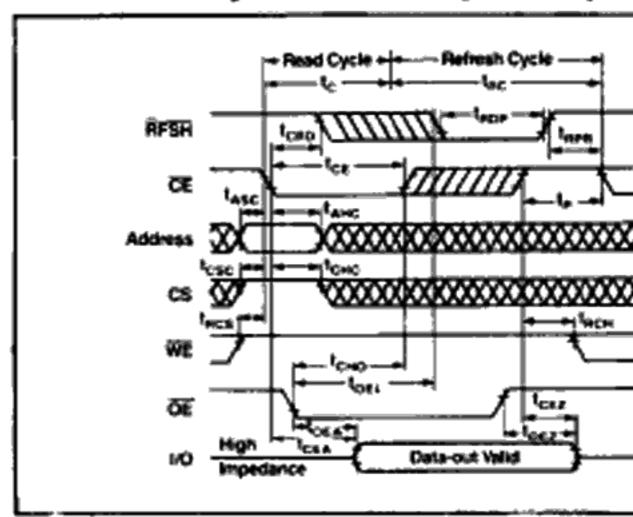

| Access time from CE                 | CEA              |      |

|-------------------------------------|------------------|------|

| Oata off time from CE               | †CEZ             |      |

| Access time from CE                 | TOEA             |      |

| Data off time from OE               | t <sub>OEZ</sub> |      |

| CE pulse width                      | tce              | 120  |

| CE precharge time                   | tp               | 90   |

| Address setup time to CE            | tasc             | 0    |

| Address hold time from CE           | tanc .           | 35   |

| CS setup time to CE                 | tese             | 0    |

| CS hold time from CE                | €снс             | 35   |

| Data setup time to CE, early write  | tosc             | - 10 |

| Data hold time from CE, early write | ‡DHC             | 90   |

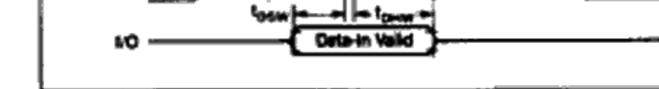

| Data setup time to WE, late write   | 1 <sub>0SW</sub> | 0    |

| Data hold time from WE, late write  | 1 <sub>DHW</sub> | 50   |

| WE setup time to CE, early write    | twsc             | -30  |

| WE hold time from CE, early write   | twic             | 90   |

| WE pulse duration                   | two              | 60   |

| CE hold time from WE, late write    | tchw             | 90   |

| WE setup time to CE, read cycle     | tacs             | 0    |

| WE hold time from CE, read cycle    | tach             | 0    |

| CE hold time from OE, read cycle    | t <sub>СНО</sub> | 45   |

| OE setup time to CE, write cycle    | t <sub>OES</sub> | 0    |

| OE hold time from CE, write cycle   | †0€H             | 0    |

|                                     |                  |      |

- (4)  $V_{EH}$  (min) and  $V_{EL}$  (max) are reference levels for measuring inpotential

- (5) Load = 2 TTL loads and 50 pF.

- (6)  $t_{CEZ}$  (max) and  $t_{OEZ}$  (max) define the time at which the output

- (7) t<sub>WSC</sub>≤t<sub>WSC</sub> (min), the cycle is a late write cycle.

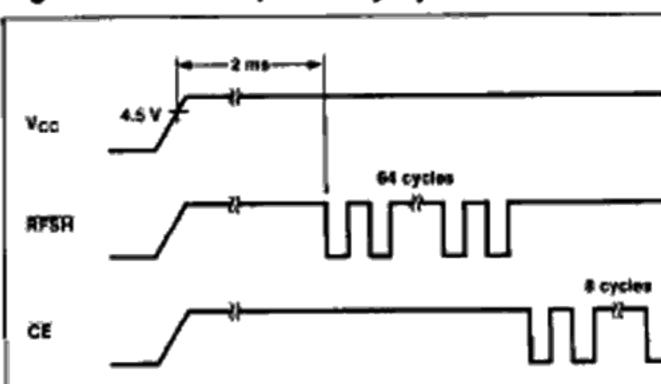

- (8) A power down self-refresh cycle is initiated when the RFSH is

Figure 1. Power-up Dummy Cycles

## Pulse Refresh Cycle after Read Cycle Complet