# 12-Bit, 8-Channel, Parallel Output ANALOG-TO-DIGITAL CONVERTER

### **FEATURES**

- 2.5V INTERNAL REFERENCE

- 8 INPUT CHANNELS

- 500kHz SAMPLING RATE

- SINGLE 5V SUPPLY

- ±1LSB: INL, DNL

- GUARANTEED NO MISSING CODES

- 70dB SINAD

- LOW POWER: 13mW

- TQFP-32 PACKAGE

### APPLICATIONS

- DATA ACQUISITION

- TEST AND MEASUREMENT

- INDUSTRIAL PROCESS CONTROL

- MEDICAL INSTRUMENTS

### DESCRIPTION

The ADS7852 is an 8-channel, 12-bit Analog-to-Digital (A/D) converter complete with sample-and-hold, internal 2.5V reference and a full 12-bit parallel output interface. Typical power dissipation is 13mW at at 500kHz throughput rate. The ADS7852 features both a nap mode and a sleep mode further reducing the power consumption to 2mW. The input range is from 0V to twice the reference voltage. The reference voltage can be overdriven by an external voltage.

The ADS7852 is ideal for multi-channel applications where low power and small size are critical. Medical instrumentation, high-speed data acquisition and laboratory equipment are just a few of the applications that would take advantage of the special features offered by the ADS7852. The ADS7852 is available in an TQFP-32 package and is fully specified and guaranteed over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Analog Inputs to AGND, Any Channel Input | –0.3V to (V <sub>D</sub> + 0.3V) |

|------------------------------------------|----------------------------------|

| REF <sub>IN</sub>                        | –0.3V to (V <sub>D</sub> + 0.3V) |

| Digital Inputs to DGND                   | –0.3V to (V <sub>D</sub> + 0.3V) |

| Ground Voltage Differences: AGND, DGND   | ±0.3V                            |

| +V <sub>SS</sub> to AGND                 | –0.3V to 6V                      |

| Power Dissipation                        | 325mW                            |

| Maximum Junction Temperature             | +150°C                           |

| Operating Temperature Range              | –40°C to +85°C                   |

| Storage Temperature Range                | –65°C to +150°C                  |

| Lead Temperature (soldering, 10s)        | +300°C                           |

|                                          |                                  |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

#### **PACKAGE/ORDERING INFORMATION**

| PRODUCT   | MAXIMUM<br>RELATIVE<br>ACCURACY<br>(LSB) | MAXIMUM<br>GAIN<br>ERROR<br>(LSB) | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING <sup>(1)</sup> | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|-----------|------------------------------------------|-----------------------------------|--------------|-----------------------|-----------------------------------|-----------------------------------|--------------------|------------------------------|

| ADS7852Y  | ±2                                       | ±40                               | TQFP-32      | PBS                   | –40°C to +85°C                    | A52                               | ADS7852Y/250       | Tape and Reel, 250           |

| ADS7852Y  | "                                        | "                                 | "            | "                     | "                                 | "                                 | ADS7852Y/2K        | Tape and Reel, 2000          |

| ADS7852YB | ±1                                       | ±25                               | TQFP-32      | PBS                   | –40°C to +85°C                    | A52                               | ADS7852YB/250      | Tape and Reel, 250           |

| ADS7852YB | "                                        | "                                 | "            | "                     | "                                 | "                                 | ADS7852YB/2K       | Tape and Reel, 2000          |

NOTE: (1) Performance Grade information is marked on the reel.

#### **ADS7852 CHANNEL SELECTION**

| A2 | A1 | A0 | CHANNEL SELECTED |

|----|----|----|------------------|

| 0  | 0  | 0  | Channel 0        |

| 0  | 0  | 1  | Channel 1        |

| 0  | 1  | 0  | Channel 2        |

| 0  | 1  | 1  | Channel 3        |

| 1  | 0  | 0  | Channel 4        |

| 1  | 0  | 1  | Channel 5        |

| 1  | 1  | 0  | Channel 6        |

| 1  | 1  | 1  | Channel 7        |

# **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}C$  to +85°C,  $f_S = 500kHz$ ,  $f_{CLK} = 16 \cdot f_S$ , and  $V_{SS} = +5V$ , using internal reference, unless otherwise specified.

|                                                                   |                                                                      | ADS7852Y |                     |                        | ADS7852YB |      |     |                    |

|-------------------------------------------------------------------|----------------------------------------------------------------------|----------|---------------------|------------------------|-----------|------|-----|--------------------|

| PARAMETER                                                         | CONDITIONS                                                           | MIN      | TYP                 | MAX                    | MIN       | TYP  | МАХ | UNITS              |

| RESOLUTION                                                        |                                                                      |          |                     | 12                     |           |      | *   | Bits               |

| ANALOG INPUT                                                      |                                                                      |          |                     |                        |           |      |     |                    |

| Input Voltage Range                                               |                                                                      | 0        |                     | 5                      | *         |      | *   | V                  |

| Input Impedance                                                   |                                                                      |          | 5M                  |                        |           | *    |     | Ω                  |

| Input Capacitance                                                 |                                                                      |          | 15                  |                        |           | *    |     | pF                 |

| Input Leakage Current                                             |                                                                      |          | ±1                  |                        |           | *    |     | μΑ                 |

| DC ACCURACY                                                       |                                                                      |          |                     |                        |           |      |     |                    |

| No Missing Codes                                                  |                                                                      | 12       |                     |                        | *         |      |     | Bits               |

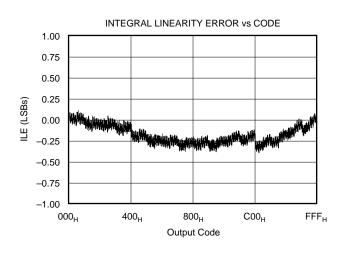

| Integral Linearity Error                                          |                                                                      |          |                     | ±2                     |           |      | ±1  | LSB <sup>(1)</sup> |

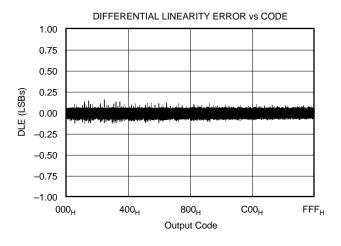

| Differential Linearity Error                                      |                                                                      |          | ±1                  |                        |           | ±0.5 | ±1  | LSB                |

| Offset Error                                                      |                                                                      |          | ±2                  | ±5                     |           | ±1   | *   | LSB                |

| Offset Error Drift                                                |                                                                      |          | ±4                  |                        |           | *    |     | ppm/°C             |

| Offset Error Match                                                |                                                                      |          |                     | ±1                     |           |      | *   | LSB                |

| Gain Error <sup>(1)</sup>                                         | Ext Ref = 2.5000V                                                    |          |                     | ±15                    |           |      | ±10 | LSB                |

| Gain Error                                                        | Int Ref                                                              |          |                     | ±40                    |           |      | ±25 | LSB                |

| Gain Error Drift                                                  |                                                                      |          | ±25                 | -                      |           | *    | -   | ppm/°C             |

| Gain Error Match                                                  |                                                                      |          |                     | ±1                     |           |      | *   | LSB                |

| Noise                                                             |                                                                      |          | 150                 |                        |           | *    |     | μVrms              |

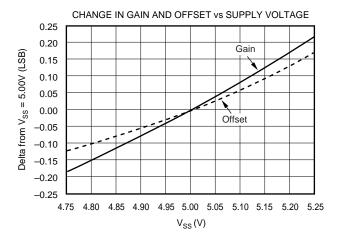

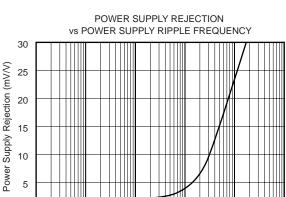

| Power Supply Rejection Ratio                                      | Worst-Case $\Delta$ , +V <sub>SS</sub> = 5V ±5%                      |          | 1.2                 |                        |           | *    |     | LSB                |

| SAMPLING DYNAMICS                                                 |                                                                      |          |                     |                        |           |      |     |                    |

| Conversion Time                                                   |                                                                      |          |                     | 13.5                   |           |      | *   | Clk Cycles         |

| Acquisition Time                                                  |                                                                      | 1.5      |                     | 10.0                   | *         |      | -~  | Clk Cycles         |

| Throughput Rate                                                   |                                                                      | 1.5      |                     | 500                    | -~        |      | *   | kHz                |

| Multiplexer Settling Time                                         |                                                                      |          | 500                 | 000                    |           | *    | ~   | ns                 |

| Aperture Delay                                                    |                                                                      |          | 5                   |                        |           | *    |     | ns                 |

| Aperture Jitter                                                   |                                                                      |          | 30                  |                        |           | *    |     | ps                 |

| AC ACCURACY                                                       |                                                                      |          |                     |                        |           |      |     | ро<br>             |

|                                                                   |                                                                      |          | 72                  |                        |           | *    |     | dB                 |

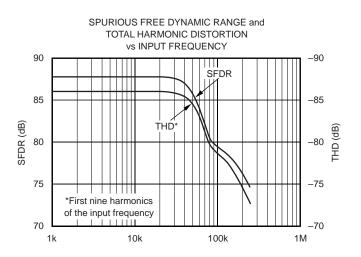

| Signal-to-Noise Ratio<br>Total Harmonic Distortion <sup>(3)</sup> |                                                                      |          | -74                 | 70                     |           | -77  | 76  | dB<br>dB           |

|                                                                   | $V_{IN} = 5Vp-p$ at 50kHz                                            | 60       | 70                  | -72                    | 71        | 72   | -76 | dВ                 |

| Signal-to-(Noise+Distortion)                                      | V <sub>IN</sub> = 5Vp-p at 50kHz<br>V <sub>IN</sub> = 5Vp-p at 50kHz | 68<br>76 | 70                  |                        | 71        | 77   |     | dB<br>dB           |

| Spurious Free Dynamic Range<br>Channel-to-Channel Isolation       | $V_{IN} = 5Vp-p$ at 50kHz<br>$V_{IN} = 5Vp-p$ at 50kHz               | 70       | 95                  |                        | 10        | *    |     | dB                 |

|                                                                   | VIN = 5VP-P at 50kHz                                                 |          | 35                  |                        |           | -7   |     |                    |

|                                                                   |                                                                      | 0.40     | 0.50                | 0.50                   |           |      |     |                    |

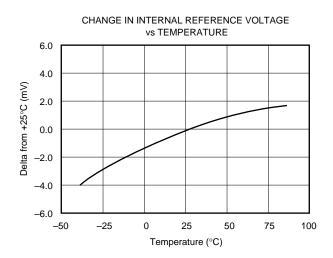

| Internal Reference Voltage                                        |                                                                      | 2.48     | 2.50                | 2.52                   | *         | *    | *   | V                  |

| Internal Reference Drift                                          | $\overline{CS} = GND$                                                |          | 30                  |                        |           | *    |     | ppm/°C             |

| Input Impedance                                                   | $\frac{CS}{CS} = V_{SS}$                                             |          | 5<br>5              |                        |           | *    |     | GΩ<br>GΩ           |

| Source Current <sup>(4)</sup>                                     | Static Load                                                          |          | 5                   | 50                     |           | *    | *   | μA                 |

|                                                                   | Static Load                                                          |          |                     |                        |           |      | ~   | μΑ                 |

|                                                                   |                                                                      | 2.0      |                     | 2.55                   | N-        |      | ×-  | v                  |

| Range<br>Resistance <sup>(5)</sup>                                | to Internal Reference Voltage                                        | 2.0      | 10                  | 2.55                   | *         | *    | *   | ν<br>kΩ            |

|                                                                   | to internal Reference voltage                                        |          | 10                  |                        |           | *    |     | K52                |

| DIGITAL INPUT/OUTPUT                                              |                                                                      |          |                     |                        |           |      |     |                    |

| Logic Family                                                      |                                                                      |          | CMOS                |                        |           | *    |     |                    |

| Logic Levels:                                                     |                                                                      | _        |                     |                        |           |      |     |                    |

| V <sub>IH</sub>                                                   | $I_{IH} = +5\mu A$                                                   | 3        |                     | +V <sub>SS</sub> + 0.3 | *         |      | *   | V                  |

| V <sub>IL</sub>                                                   | $I_{IL} = +5\mu A$                                                   | -0.3     |                     | 0.8                    | *         |      | *   | V                  |

| V <sub>OH</sub>                                                   | $I_{OH} = 250\mu A$                                                  | 3.5      |                     |                        | *         |      |     | V                  |

|                                                                   | $I_{OL} = 250 \mu A$                                                 |          | <br>(ani alut Dia a | 0.4                    |           |      | *   | V                  |

| Data Format                                                       |                                                                      | 5        | traight Bina        | ry                     |           | *    |     |                    |

| POWER SUPPLY REQUIREMENT                                          |                                                                      |          |                     |                        |           |      |     |                    |

| +V <sub>SS</sub>                                                  | Specified Performance                                                | 4.75     |                     | 5.25                   | *         |      | *   | V                  |

| Quiescent Current                                                 |                                                                      |          | 2.6                 | 3.5                    |           | *    | *   | mA                 |

| Normal Power                                                      |                                                                      |          | 13                  | 17.5                   |           | *    | *   | mW                 |

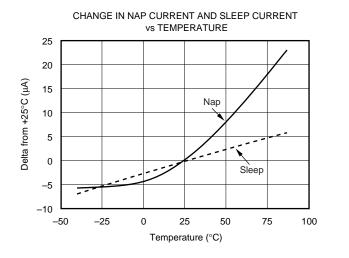

| Nap Mode Current <sup>(6)</sup>                                   |                                                                      |          | 600                 | 800                    |           | *    | *   | μΑ                 |

| Sleep Mode Current <sup>(6)</sup>                                 |                                                                      |          | 10                  | 30                     |           | *    | *   | μΑ                 |

| TEMPERATURE RANGE                                                 |                                                                      |          |                     |                        |           |      |     |                    |

| Specified Performance                                             |                                                                      | -40      |                     | +85                    | *         |      | *   | °C                 |

| Storage                                                           |                                                                      | -65      | 1                   | +150                   | *         | 1    | *   | °C                 |

\* Specifications same as ADS7852Y.

NOTES: (1) LSB means Least Significant Bit, with  $V_{REF}$  equal to +2.5V, one LSB is 1.22mV. (2) Measured relative to an ideal, full-scale input of 4.999V. Thus, gain error includes the error of the internal voltage reference. (3) Calculated on the first nine harmonics of the input frequency. (4) If the internal reference is required to source current to an external load, the reference voltage will change due to the internal 10k $\Omega$  resistor. (5) Can vary ±30%. (6) See Timing Characteristics for further detail.

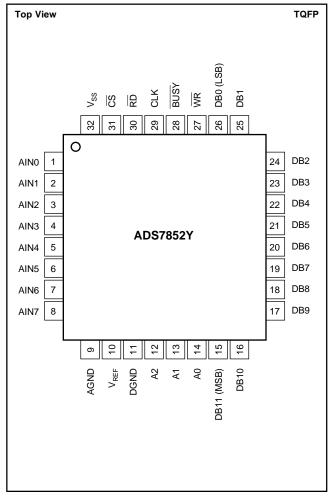

### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| PIN | NAME             | DESCRIPTION                                                                                                                                                                      |  |  |  |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | AIN0             | Analog Input Channel 0                                                                                                                                                           |  |  |  |

| 2   | AIN1             | Analog Input Channel 1                                                                                                                                                           |  |  |  |

| 3   | AIN2             | Analog Input Channel 2                                                                                                                                                           |  |  |  |

| 4   | AIN3             | Analog Input Channel 3                                                                                                                                                           |  |  |  |

| 5   | AIN4             | Analog Input Channel 4                                                                                                                                                           |  |  |  |

| 6   | AIN5             | Analog Input Channel 5                                                                                                                                                           |  |  |  |

| 7   | AIN6             | Analog Input Channel 6                                                                                                                                                           |  |  |  |

| 8   | AIN7             | Analog Input Channel 7                                                                                                                                                           |  |  |  |

| 9   | AGND             | Analog Ground, GND = 0V                                                                                                                                                          |  |  |  |

| 10  | V <sub>REF</sub> | Voltage Reference Input and Output. See Electrical Characteristics table for ranges. Decouple to ground with a $0.1\mu$ F ceramic capacitor and a $2.2\mu$ F tantalum capacitor. |  |  |  |

| 11  | DGND             | Digital Ground, GND = 0V                                                                                                                                                         |  |  |  |

| 12  | A2               | Channel Address. See Channel Selection<br>Table for details.                                                                                                                     |  |  |  |

| 13  | A1               | Channel Address. See Channel Selection<br>Table for details.                                                                                                                     |  |  |  |

| 14  | A0               | Channel Address. See Channel Selection<br>Table for details.                                                                                                                     |  |  |  |

| 15  | DB11             | Data Bit 11 (MSB)                                                                                                                                                                |  |  |  |

| 16  | DB10             | Data Bit 10                                                                                                                                                                      |  |  |  |

| 17  | DB9              | Data Bit 9                                                                                                                                                                       |  |  |  |

| 18  | DB8              | Data Bit 8                                                                                                                                                                       |  |  |  |

| 19  | DB7              | Data Bit 7                                                                                                                                                                       |  |  |  |

| 20  | DB6              | Data Bit 6                                                                                                                                                                       |  |  |  |

| 21  | DB5              | Data Bit 5                                                                                                                                                                       |  |  |  |

| 22  | DB4              | Data Bit 4                                                                                                                                                                       |  |  |  |

| 23  | DB3              | Data Bit 3                                                                                                                                                                       |  |  |  |

| 24  | DB2              | Data Bit 2                                                                                                                                                                       |  |  |  |

| 25  | DB1              | Data Bit 1                                                                                                                                                                       |  |  |  |

| 26  | DB0              | Data Bit 0 (LSB)                                                                                                                                                                 |  |  |  |

| 27  | WR               | Write Input. Active LOW. Use to start a new conversion and to select an analog channel via address inputs A0, A1 and A2 in combination with $\overline{CS}$ .                    |  |  |  |

| 28  | BUSY             | BUSY output goes LOW and stays LOW<br>during a conversion. BUSY rises when a<br>conversion is complete.                                                                          |  |  |  |

| 29  | CLK              | External Clock Input. The clock speed determines the conversion rate by the equation: $f_{CLK} = 16 \cdot f_{SAMPLE}$ .                                                          |  |  |  |

| 30  | RD               | Read Input. Active LOW. Use to read the data outputs in combination with $\overline{CS}$ . Also use (in conjunction with A0 or A1) to place device in power-down mode.           |  |  |  |

| 31  | ĊŚ               | Chip Select Input. Active LOW. The combination of $\overline{CS}$ taken LOW and $\overline{WR}$ taken LOW initiates a new conversion and places the outputs in tri-state mode.   |  |  |  |

| 32  | V <sub>SS</sub>  | Voltage Supply Input. Nominally +5V. Decouple to ground with a 0.1 $\mu$ F ceramic capacitor and a 10 $\mu$ F tantalum capacitor.                                                |  |  |  |

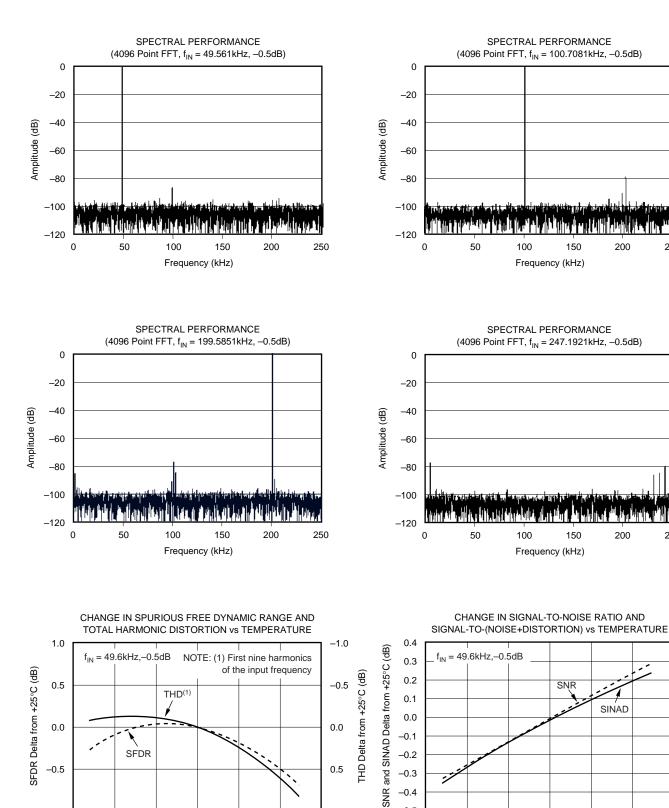

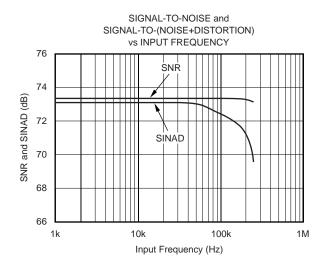

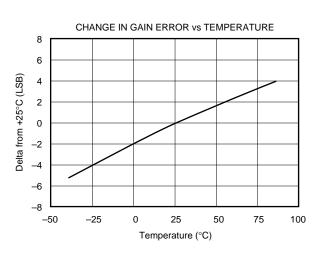

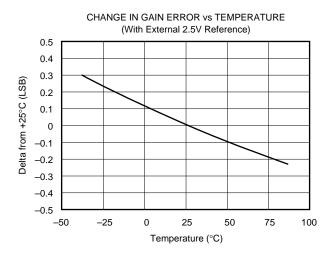

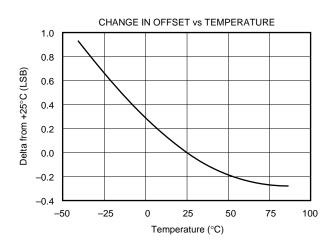

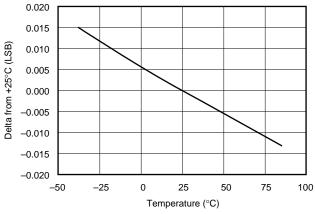

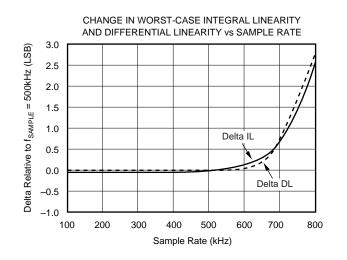

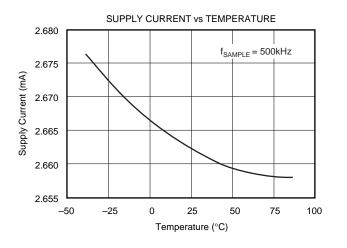

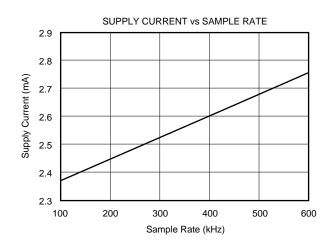

## **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $V_{SS} = +5V$ ,  $f_{SAMPLE} = 500$ kHz,  $f_{CLK} = 16 \cdot f_{SAMPLE}$ , and internal reference, unless otherwise specified.

-1.0

-50

-25

0

25

Temperature (°C)

50

75

1.0

100

-0.5

-50

-25

0

25

Temperature (°C)

50

75

100

250

250

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $V_{SS} = +5V$ ,  $f_{SAMPLE} = 500kHz$ ,  $f_{CLK} = 16 \bullet f_{SAMPLE}$ , and internal reference, unless otherwise specified.

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $V_{SS} = +5V$ ,  $f_{SAMPLE} = 500$ kHz,  $f_{CLK} = 16 \cdot f_{SAMPLE}$ , and internal reference, unless otherwise specified.

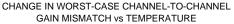

CHANGE IN WORST-CASE CHANNEL-TO-CHANNEL OFFSET MISMATCH vs TEMPERATURE 0.10 Delta from +25°C (LSB) 0.05 0.00 -0.05 -0.10 -50 -25 0 25 50 75 100 Temperature (°C)

CHANGE IN WORST-CASE INTEGRAL LINEARITY AND DIFFERENTIAL LINEARITY vs TEMPERATURE 0.050 Delta from +25°C (LSB) 0.025 Delta IL 0.000 -0.025 Delta DL -0.050 -50 -25 0 25 50 75 100

Temperature (°C)

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $V_{SS} = +5V$ ,  $f_{SAMPLE} = 500kHz$ ,  $f_{CLK} = 16 \cdot f_{SAMPLE}$ , and internal reference, unless otherwise specified.

### THEORY OF OPERATION

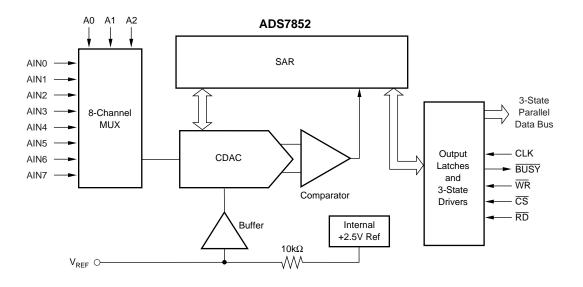

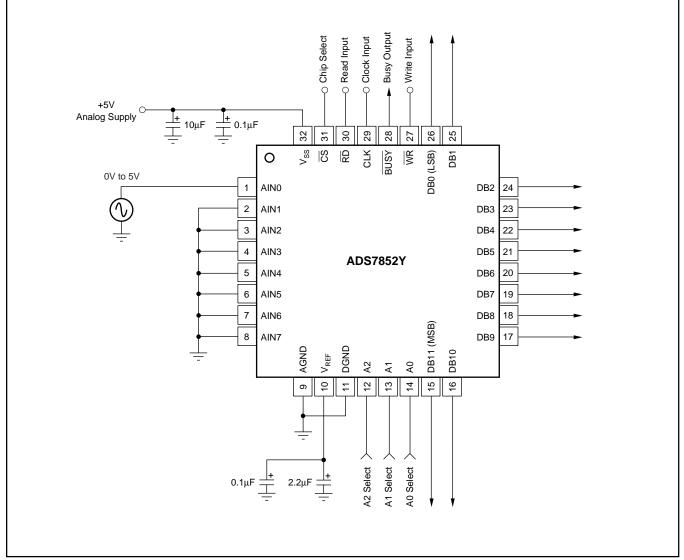

The ADS7852 is a high-speed successive approximation register (SAR) Analog-to-Digital (A/D) converter with an internal 2.5V bandgap reference. The architecture is based on capacitive redistribution which inherently includes a sample/hold function. The converter is fabricated on a 0.6micron CMOS process. Figure 1 shows the basic operating circuit for the ADS7852.

The ADS7852 requires an external clock to run the conversion process. This clock can vary between 200kHz (12.5Hz throughput) and 8MHz (500kHz throughput). The duty cycle of the clock is unimportant as long as the minimum HIGH and LOW times are at least 50ns and the clock period is at least 125ns. The minimum clock frequency is governed by the parasitic leakage of the Capacitive Digital-to-Analog (CDAC) capacitors internal to the ADS7852. The front-end input multiplexer of the ADS7852 features eight single-ended analog inputs. Channel selection is performed using the address pins A0 (pin 14), A1 (pin 13), and A2 (pin 12). When a conversion is initiated, the input voltage is sampled on the internal capacitor array. While a conversion is in progress, all channel inputs are disconnected from any internal function (see Truth Table for addressing).

The range of the analog input is set by the voltage on the  $V_{REF}$  pin. With the internal 2.5V reference, the input range is 0V to 5V. An external reference voltage can be placed on  $V_{REF}$ , overdriving the internal voltage. The range for the external voltage is 2.0V to 2.55V, giving an input voltage range of 4.0V to 5.1V.

FIGURE 1. Typical Circuit Configuration.

## ANALOG INPUTS

The ADS7852 features eight single-ended inputs. While the static current into each analog input is basically zero, the dynamic current depends on the input voltage and sample rate. Essentially, the current into the device must charge the internal hold capacitor during the sample period. After this capacitor has been fully charged, no further input current is required. For optimum performance, the source driving the analog inputs must be capable of charging the input capacitance to a 12-bit settling level within the sample period. This can be as little as 350ns in some operating modes. While the converter is in the hold mode, or after the sampling capacitor has been fully charged, the input impedance of the analog input is greater than  $1G\Omega$ .

## REFERENCE

The reference voltage on the  $V_{REF}$  pin establishes the fullscale range of the analog input. The ADS7852 can operate with a reference in the range of 2.0V to 2.55V corresponding to a full-scale range of 4.0V to 5.1V.

The voltage at the  $V_{REF}$  pin is internally buffered and this buffer drives the capacitor DAC portion of the converter. This is important because the buffer greatly reduces the dynamic load placed on the reference source. Since the voltage at  $V_{REF}$  will be unavoidably affected by noise and glitches generated during the conversion process, it is highly recommended that the  $V_{REF}$  pin be bypassed to ground as outlined in the sections that follow.

### INTERNAL REFERENCE

The ADS7852 contains an onboard 2.5V reference, resulting in a 0V to 5V input range on the analog input. The Specifications Table gives the various specifications for the internal reference. This reference can be used to supply a small amount of source current to an external load but the load should be static. Due to the internal 10k $\Omega$  resistor, a dynamic load will cause variations in the reference voltage, and will dramatically affect the conversion result. Note that even a static load will reduce the internal reference voltage seen at the buffer input. The amount of reduction depends on the load and the actual value of the internal "10k $\Omega$ " resistor. The value of this resistor can vary by ±30%.

The  $V_{REF}$  pin should be bypassed with a 0.1µF ceramic capacitor placed as close to the ADS7852 as possible. In addition, a 2.2µF tantalum capacitor should be used in parallel with the ceramic capacitor.

### EXTERNAL REFERENCE

The internal reference is connected to the  $V_{REF}$  pin and to the internal buffer via an on-chip 10k $\Omega$  series resistor. Because of this configuration, the internal reference voltage can easily be overridden by an external reference voltage. The voltage range for the external voltage is 2.00V to 2.55V, corresponding to an analog input range of 4.0V to 5.1V.

While the external reference will not have to provide significant dynamic current to the  $V_{REF}$  in, it does have to drive the series

10kΩ resistor that is connected to the 2.5V internal reference. Accounting for the maximum difference between the external reference voltage and the internal reference voltage, and the processing variations for the on-chip 10kΩ resistor, this current can be as high as 75µA. In addition, the V<sub>REF</sub> pin should still be bypassed to ground with at least a 0.1µF ceramic capacitor placed as close to the ADS7852 as possible. Depending on the particular reference and A/D conversion speed, additional bypass capacitance may be required, such as the 2.2µF tantalum capacitor shown in the Typical Circuit Configuration (Figure 1). Close attention should be paid to the stability of any external reference source that is driving the large bypass capacitors present at the V<sub>REF</sub> pin.

### **BASIC OPERATION**

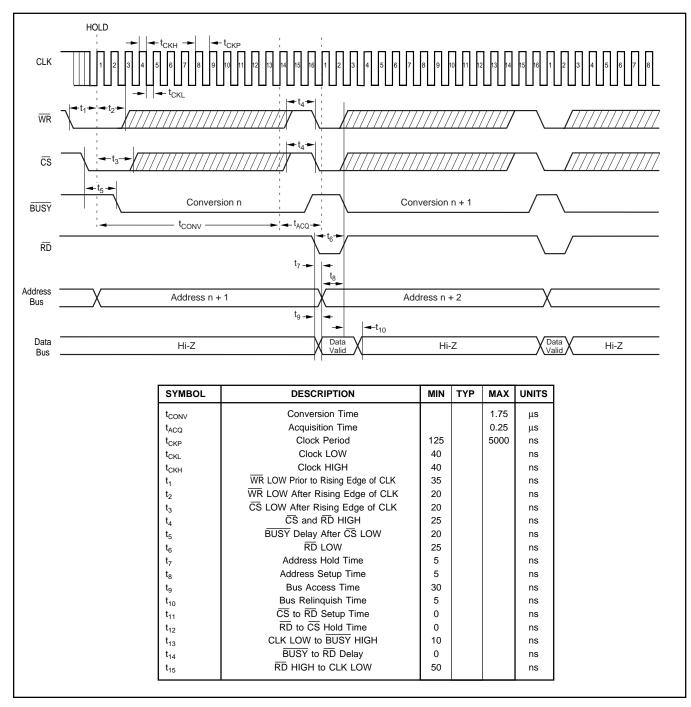

Figure 1 shows the simple circuit required to operate the ADS7852 with Channel 0 selected. A conversion can be initiated by bringing the WR pin (pin 27) LOW for a minimum of 35ns. BUSY (pin 28) will output a LOW during the conversion process and rises only after the conversion is complete. The 12 bits of output data will be valid on pins 15 through 26 following the rising edge of BUSY.

### STARTING A CONVERSION

A conversion is initiated on the falling edge of the WR input, with valid signals on A0, A1, A2, and CS. The ADS7852 will enter the conversion mode on the first rising edge of the external clock following the WR pin going LOW. The conversion process takes 13.5 clock cycles (1.5 cycles for the DB0 decision, 2 clock cycles for the DB5 decision, and 1 clock cycle for each of the other bit decisions). This allows 2.5 clock cycles for sampling. Upon initiating a conversion, the BUSY output will go LOW approximately 20ns after the falling edge of the WR pin. The BUSY output will return HIGH just after the ADS7852 has finished a conversion and the output data will be valid on pins 15 through 26. The rising edge of BUSY can be used to latch the output data into an external device. It is recommended that the data be read immediately after each conversion since the switching noise of the asynchronous data transfer can cause digital feedthrough degrading the converter's performance (See Figure 2).

### CHANNEL ADDRESSING

The selection of the analog input channel to be converted is controlled by address pins A0, A1, and A2. This channel becomes active on the rising edge of  $\overline{WR}$  with  $\overline{CS}$  held LOW. The data on the address pins should be stable for at least 10ns prior to  $\overline{WR}$  going HIGH.

The address pins are also used to control the power-down functions of the ADS7852. Careful attention must be paid to the status of the address pins following each conversion. If the user does not want the ADS7852 to enter either of the power-down modes following a conversion, the A0 and A1 pins must be LOW when RD and CS are returned HIGH after reading the data at the end of a conversion (see the Power-Down Mode section of this data sheet for more details).

FIGURE 2. ADS7852 Write/Read Timing.

#### **READING DATA**

Data from the ADS7852 will appear at pins 15 through 26. The MSB will output on pin 15 while the LSB will output on pin 26. The outputs are coded in Straight Binary (with  $OV = 000_H$  and  $5V = FFF_H$ ). Following a conversion, the BUSY pin will go HIGH. After BUSY has been HIGH for at least t<sub>14</sub> seconds, the CS and RD pins may be brought LOW to enable the 12-bit output bus. CS and RD must be held LOW for at least 25ns following BUSY HIGH. Data will be valid 30ns after the falling edge of both CS and RD. The output data will remain valid for 20ns following the rising edge of both CS and RD (See Figure 2 for the read cycle timing diagram).

|                                |              | DIGITAL OUTPUT<br>STRAIGHT BINARY |          |

|--------------------------------|--------------|-----------------------------------|----------|

| DESCRIPTION                    | ANALOG INPUT | BINARY CODE                       | HEX CODE |

| Least Significant<br>Bit (LSB) | 1.2207mV     |                                   |          |

| Full Scale                     | 4.99878V     | 1111 1111 1111                    | FFF      |

| Midscale                       | 2.5V         | 1000 0000 0000                    | 800      |

| Midscale –1LSB                 | 2.49878V     | 0111 1111 1111                    | 7FF      |

| Zero Full Scale                | 0V           | 0000 0000 0000                    | 000      |

Table I. Ideal Input Voltages and Output Codes.

#### ADS7852 SBAS111A

#### **POWER-DOWN MODE**

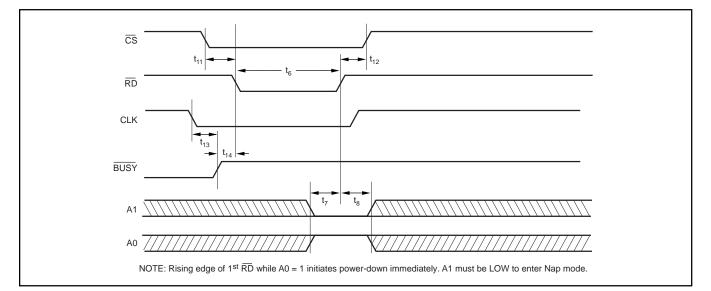

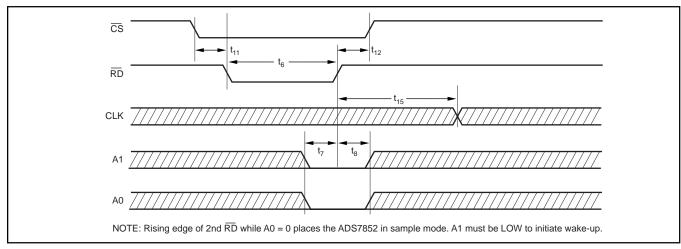

The ADS7852 has two different power-down modes: the Nap mode and the Sleep mode. In the Nap mode, all analog and digital circuitry, with the exception of the voltage reference, is powered off. In the Sleep mode, everything is powered off.

While the Sleep mode affords the lowest power consumption, the time to come out of Sleep mode can be considerable since it takes the internal reference voltage a finite amount of time to power up and reach a stable value. This latency can result in spurious output data for a minimum of ten conversion cycles at a 500kHz sampling rate. It should also be noted that any external load connected to the V<sub>REF</sub> pin will exacerbate this effect since a discharge path for the  $V_{REF}$ bypass capacitor is provided during the Sleep cycle. Even the parasitic leakage of the bypass capacitor itself should be considered if the unit is left in the Sleep mode for an extended period. After power-up, this capacitor must be recharged by the internal reference voltage and the on-chip  $10k\Omega$  series resistor. Under worst-case conditions (e.g., the bypass capacitor is completely discharged), the output data can be invalid for several hundred milliseconds.

Since the Nap mode maintains the voltage on the  $V_{REF}$  pin by keeping the internal reference powered-up, valid conversions are available immediately after the Nap mode is terminated.

The simplest way to use the power-down mode is following a conversion. After a conversion has finished and  $\overline{BUSY}$  has returned HIGH,  $\overline{CS}$  and  $\overline{RD}$  must be brought LOW for a minimum of 25ns. When  $\overline{RD}$  and  $\overline{CS}$  are returned HIGH, the ADS7852 will enter the power-down mode on the rising edge of  $\overline{RD}$ . If  $\overline{CS}$  is always kept LOW, the power-down mode will be controlled exclusively by  $\overline{RD}$ . Depending on the status of the A0 and A1 address pins, the ADS7852 will either enter the Nap mode, the Sleep mode, or be returned to normal operation in the sampling mode. See Table II and Figures 3 and 4 for further details.

| RD                                                                          | A2 | A1 | A0 | POWER-DOWN MODE |  |  |

|-----------------------------------------------------------------------------|----|----|----|-----------------|--|--|

| Ŀ                                                                           | Х  | 0  | 0  | None            |  |  |

| Ł                                                                           | х  | 1  | 0  | Sleep           |  |  |

| Ŀ                                                                           | х  | 0  | 1  | Nap             |  |  |

| 📕 X 1 1                                                                     |    |    | 1  | Sleep           |  |  |

| $\mathbf{J}$ = Signifies rising edge of $\overline{RD}$ pin. X = Don't care |    |    |    |                 |  |  |

TABLE II. ADS7852 Power-Down Mode.

FIGURE 3. Entering Nap Using RD and A0.

FIGURE 4. Initiating Wake-Up Using RD and A0.

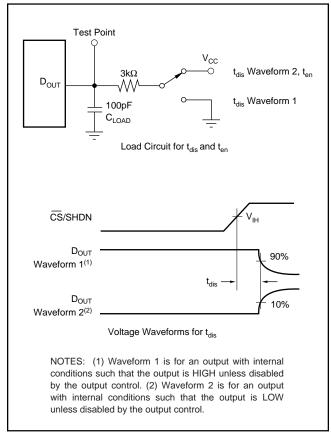

FIGURE 5. Timing Diagram and Test Circuits for Parameters in Figure 2.

In addition to using the address pins in conjunction with  $\overline{\text{RD}}$ , the power-down mode can also be terminated implicitly by starting a new conversion (e.g., taking  $\overline{\text{WR}}$  LOW while  $\overline{\text{CS}}$  is LOW). If it is desired to keep the ADS7852 in a power-down state for a period that is greater than dictated by the sampling rate, the convert signal driving the  $\overline{\text{WR}}$  pin must be disabled.

The typical supply current of the ADS7852, with a 5V supply and a 500kHz sampling rate, is 2.6mA. In the Nap mode, the typical supply current is  $600\mu$ A. In the Sleep mode, the current is typically reduced to  $10\mu$ A.

### LAYOUT

For optimum performance, care should be taken with the physical layout of the ADS7852 circuitry. This is particularly true if the CLK input is approaching the maximum throughput rate.

The basic SAR architecture is sensitive to glitches or sudden changes on the power supply, reference, ground connections and digital inputs that occur just prior to latching the output of the analog comparator. Thus, driving any single conversion for an n-bit SAR converter, there are n "windows" in which large external transient voltages can affect the conversion result. Such glitches might originate from switching power supplies, nearby digital logic, or high power devices. The degree of error in the digital output depends on the reference voltage, layout, and the exact timing of the external event. Their error can change if the external event changes in times with respect to the CLK input.

With this in mind, power to the ADS7852 should be clean and well bypassed. A  $0.1\mu$ F ceramic bypass capacitor should be placed as close to the device as possible. In addition, a  $1\mu$ F to  $10\mu$ F capacitor is recommended. If needed an even larger capacitor and a  $5\Omega$  or  $10\Omega$  series resistor may be used to low pass filter a noisy supply. The ADS7852 draws very little current from an external reference on average as the reference voltage is internally buffered. However, glitches from the conversion process appear at the V<sub>REF</sub> input and the reference is internal or external, the V<sub>REF</sub> pin should be bypassed with a  $0.1\mu$ F capacitor. An additional larger capacitor may also be used, if desired. If the reference voltage is external and originates from an op amp, make sure it can drive the bypass capacitor or capacitors without oscillation.

The GND pin should be connected to a clean ground point. In many cases, this will be the "analog" ground. Avoid connections which are too near the grounding point of a microcontroller or digital signal processor. If needed, run a ground trace directly from the converter to the power supply entry point. The ideal layout will include an analog ground plane dedicated to the converter and associated analog circuitry.

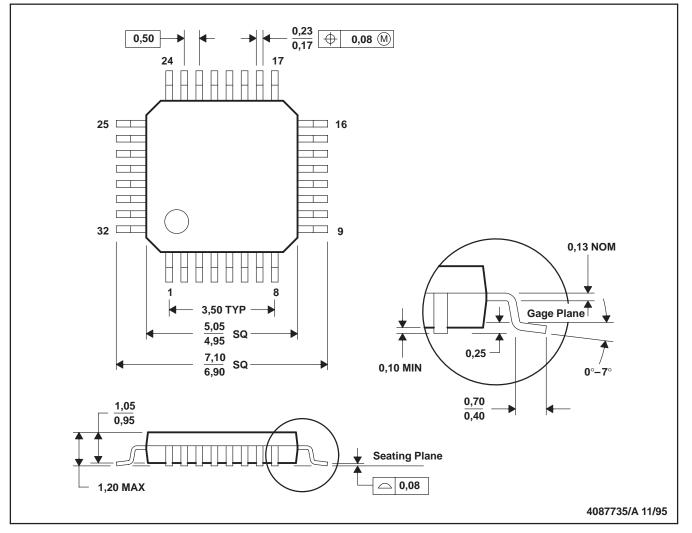

### PACKAGE DRAWING

#### PBS (S-PQFP-G32)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated