# N4901B SerialBERT 13.5 Gbps

# **Technical Specification**

Version 1.0

### General

The N4901B SerialBERT 13.5 Gbps operates within a range from 620 Mbps up to 13.5 Gbps. Available configurations are:

- $\cdot\,$  one Pattern Generator and one Error Detector

- · one Pattern Generator only

- · one Error Detector only

#### **Key values & Benefits**

- Range of operation 620 Mbps to 13.5 Gbps

- Jitter Injection, Jitter Tolerance measurement capabilities

- · True differential data generation and analysis

- CDR with ranges at approximately 3 Gbps, 6 Gbps and 10 Gbps

- Intuitive, state-of-the-art Windows XP. touchscreen user interface

- Inter-operability between N4901B and other instruments

- Compatability with existing remote commands e.g. Agilent 71612 and 86130A Series

- · Signal integrity

- · Fastest transition times

#### **Pattern Generator**

- · Pattern generation for PRBS or memory based patterns

- Flexible levels addressing a broad range of technologies, e.g. ECL, PECL (3.3V), LVDS, CML

#### **Error Detector**

- · BER Measurements

- · Automatic Threshold

- · Sampling Point

- $\cdot$  Search Data Polarity

- · G. 821 Measurement

- · Measurement Suite

- · Auto Alignment

#### **Measurement features**

- $\cdot \,$  Output Timing Jitter

- $\cdot\,$  Spectral Jitter

- $\cdot$  Output Level

- $\cdot\,$  Bit Error Rate

- · Fast Eye Mask

- $\cdot\,$  Eye Contour

#### Display

8" color LCD touchscreen

#### **Data Entry**

Touch-screen display, numeric keypad with up/down arrows, dial-knob control or USB keyboard and mouse. **Hard Disk** For local storage of user patterns and data. Internal or external disk available.

#### **Removable Storage**

- · Floppy Disk Drive 1.44 MB

- · USB Stick

#### **Online Help**

For comprehensive software support

#### Interfaces

GPIB (IEEE 488), LAN, parallel printer port, VGA output, 4 x USB 2.0, 1 x USB 1.1 ports

## **User Interface**

The time needed to set up the first measurement is minimised based on intuitive and easyto-learn interfaces.

The "N4901B SerialBERT 13.5 Gbps" User Interface is easily fitted to a variety of applications. In addition, the optimized measurement suite guarantees an immediate return on investment.

The User Interface provides the following functions:

- $\cdot\,$  Patter Generator Setup

- · Error Setup Analyser / Detector

- · Pattern Editor

- · Measurement Results

By utilizing network capabilities, N4901B SerialBERT is remote controllable via LAN. GPIB is available for MS Windows, Unix or Linux operating systems. Test executives can control the system by using National Instruments' LabVIEW, Agilent TestExec, and Microsoft<sup>®</sup> Excel or Visual Basic.

#### **Examples for Results Screens**

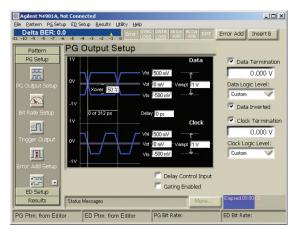

The Generator Pattern Editor allows simple access to timing & level parameters, as seen below.

Figure 1: Generator Setup

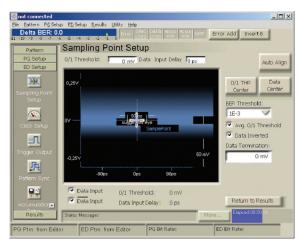

The Sampling Point Setup allows simple access to Sampling Point precision referring to timing point threshold.

**Figure 2: Error Detector Setup**

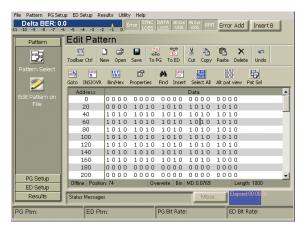

The Pattern Editor allows the operator to deal with user-specific data.

**Figure 3: Pattern Editor Setup**

The diagram below shows bit error results based on CCITT Ref. G.821.

| File Pattern PG Setup<br>Delta BER: 0.0<br>11 -10 -9 -8 -7 -6 | ED Setup Results Utility Help |                         | T Error Add Insert B                  |

|---------------------------------------------------------------|-------------------------------|-------------------------|---------------------------------------|

| Pattern                                                       | Accumulated Resu              | ilts                    |                                       |

| PG Setup                                                      | 0                             | Ratios                  |                                       |

| ED Setup                                                      | -2 -                          |                         |                                       |

| Results                                                       | 8 -4 -                        |                         |                                       |

|                                                               | - 6                           |                         | -                                     |

| BER Results                                                   | -10 -                         |                         |                                       |

| BER Results                                                   | -12                           | • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • |

| <b>1</b>                                                      |                               | Days                    |                                       |

| Accumulated<br>Results                                        | Accumulated Results G.821     | Measurements Interval   | Results Accumulation F                |

| Results                                                       | Measurements                  | Current Period          | Previous Period                       |

| <u></u>                                                       | Availability                  | 100                     | 99                                    |

| Eye Results                                                   | Unavailability                | 0                       | 0.5                                   |

|                                                               | Severely Errored Seconds      | 4                       | 5                                     |

|                                                               | Degraded Minutes              | 0                       | 0                                     |

|                                                               | Errored Seconds               | 30                      | 31                                    |

|                                                               | Status Messages               | Mo                      | re                                    |

| PG Ptrn:                                                      | ED Ptm:                       | PG Bit Rate:            | ED Bit Rate:                          |

Figure 4: G.821 Results

### **Measurement Suite**

The Measurement Suite of the SerialBERT 13.5 Gbps offers comprehensive analysis features, detailed insight for design verification and efficient pass/fail testing in manufacturing.

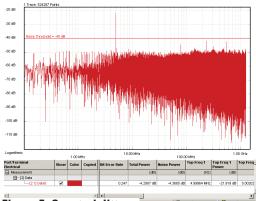

#### Spectral Jitter Decomposition (see Fig. 5)

It includes a measurement for the spectral decomposition of jitter components. The decomposition technique allows inband- and outbandcharacterization of circuits and devices including PLLs and CDRs. While debugging designs, the new measurement allows the exploration of the various components of deterministic jitter.

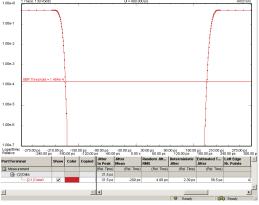

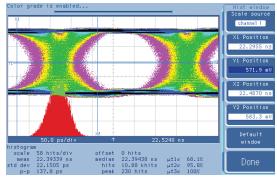

#### BERT Scan incl. Rj / Dj separation (see Fig. 6)

This measurement shows the BER of the DUT's output versus sample point delay, which is displayed as a curve with BER vs. sample delay and threshold. Available results are setup/hold time, phase margin, Jitter incl. extrapolation of total jitter (rms, peak-to-peak) and RJ/DJ Separation. The output timing measurement is available as a bathtub plot and as a histogram. This provides measurement of RJ, DJ and Total Jitter. The measurement method is equivalent to the IEE802.3ae method. In order to guarantee the validity of the measurement, a "quality of fit" value is also provided.

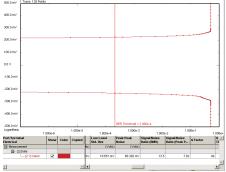

#### Output Level and Q Factor (see Fig. 7)

Figure 7 shows the sample BERT delay corresponding to the threshold. Available results are Q Factor, table.

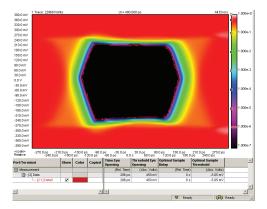

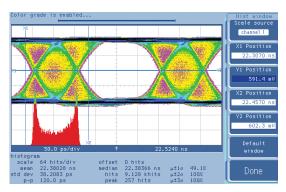

#### Eye Contour (see Fig. 8)

For device characterization the eye opening measurement generates a three-dimensional bit error rate (BER) diagram as a function of the sample delay and the sample threshold. Besides the eye opening, the eye contour measurement provides results for the optimum sample point. The eye opening measurement allows selecting different views such as eye contour, pseudo color and equal BER plots.

#### Fast Eye Mask

For fast pass/fail testing in manufacturing, this measurement checks up to 32 points, equivalent to mask testing.

**Figure 5: Spectral Jitter**

Figure 6: BERT Scan incl. Rj/Dj Separation

Figure 7: Output Level & Q Factor

**Figure 8: Eye Contour**

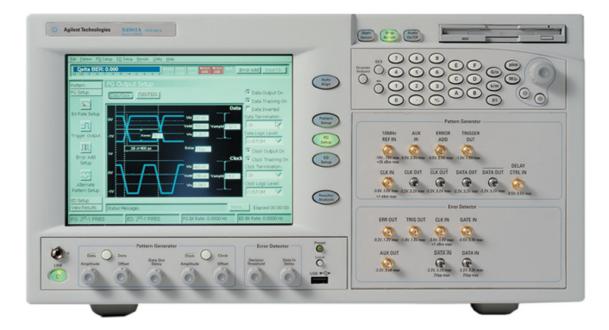

### **Pattern Generator**

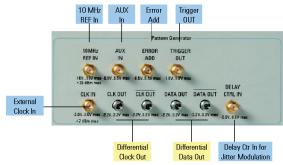

**Figure 9: Front View of Pattern Generator**

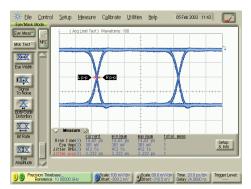

#### Waveform examples for Differential Data Output

Pulse Performance Measurement allows different amplitude voltages with variable amplitudes from 50mV...1.8V, output voltage. The window makes -2V...2.8V possible and a variable delay. An example is shown below in Figure 10.

Figure 10: 50% Signals at 2V

#### Features:

- · Polarity normal or inverted data

- $\cdot$  Data high level adjust

- · Data amplitude adjust

- · Clock/Data relative delay adjustment

- · Vertical data-eye cross-over adjust

- · Output gating

- $\cdot$  Error add

- $\cdot$  Delay control input

#### **Data Output**

| Table 1: Parameters for SerialBERT 13.5 Gbps General |                                                     |   |  |

|------------------------------------------------------|-----------------------------------------------------|---|--|

| Range of operation:                                  | 620 Mbps to 13.5 Gbps                               |   |  |

| Interface                                            | Differential or single-ended (1),                   | , |  |

|                                                      | DC coupled, 50 $\Omega$                             |   |  |

| Format                                               | NRZ, normal or inverted                             |   |  |

| Amplitude/Resolution                                 | 0.10 V to 1.8 V in 5 mV steps                       |   |  |

| Output voltage window                                | -2.0 V to +3.0 V                                    |   |  |

| Predefined Levels                                    | ECL, PECL (3.3V), LVDS, CML                         |   |  |

| Transition times                                     | < 25 ps pp (2)                                      |   |  |

| (10% to 90%)                                         |                                                     |   |  |

| Jitter                                               | 9 ps pp typical                                     |   |  |

| Clock/data delay                                     | ±0.75 ns                                            |   |  |

| Resolution                                           | 100 fs                                              |   |  |

| Terminations                                         | 50 $\Omega$ , -2 V to 3 V or 50 $\Omega$ AC coupled |   |  |

|                                                      | (the external termination voltage                   |   |  |

|                                                      | must be below the output high level)                |   |  |

| <b>Crossing point of adjustment</b>                  | nt 20%80% typical                                   |   |  |

| Single Error Inject                                  | Adds single errors on demand                        |   |  |

| Fixed Error Inject                                   | Fixed error ratios of 1 error in 10 <sup>n</sup>    |   |  |

|                                                      | bits, n = 3, 4, 5, 6, 7, 8, 9                       |   |  |

| Delay Control Input                                  | ± 100ps, DC to 1 GHz @ data rate                    |   |  |

|                                                      | <10.5 Gpbs                                          |   |  |

| Connector                                            | 2.4 mm female                                       |   |  |

| (1) he should such a death a                         | unused sutnut has to be terminet                    | 1 |  |

(1) In single-ended mode the unused output has to be terminated by a 50  $\Omega$  resistor to ground

(2) at ECL levels

#### **Clock Output**

| Clock Output                 | 1, differential or single-ended,      |  |

|------------------------------|---------------------------------------|--|

|                              | 2.4mm(f) (1)                          |  |

| Frequency                    | 620 MHz - 13.5 GHz                    |  |

| Impedance                    | 50 Ohm typ.                           |  |

| Amplitude/Resolution         | 0.1Vpp to 1.8 Vpp in 5mV steps        |  |

| Output voltage window        | -2.00 to +2.80 V                      |  |

| Short circuit current        | 72 mA max.                            |  |

| External termination voltage | -2V to +3V (2)                        |  |

| Addressable technologies     | LVDS, CML                             |  |

|                              | PECL; ECL (terminated to              |  |

|                              | 1.3V/0 V/-2 V) low voltage CMOS       |  |

| Transition times (10%-90%)   | <25 ps                                |  |

| Jitter                       | 1 ps RMS typ.                         |  |

| SSB phase noise              | < - 75 dBc with internal clock source |  |

| (10GHz@ 10kHz offset,        |                                       |  |

| 1Hz bandwidth)               |                                       |  |

(1) In single-ended mode, the unused output must be terminated with 50 Ohm to GND.

(2) External termination voltage must be less than 3V below  $\rm V_{OH}.$  External termination voltage must be less than 3V above  $\rm V_{OL}.$  Termination into AC is possible.

#### **10 MHz Reference Input**

A 10 MHz reference signal can be applied from which the internal clock is derived.

#### Table 3: Specifications

| Interface | AC coupled, 50 $\Omega$ nominal |

|-----------|---------------------------------|

| Amplitude | 200 mV to 2 V                   |

| Connector | SMA female                      |

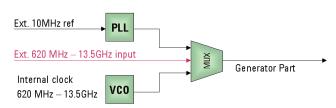

### **Clock Scheme**

#### Figure 11: Block Diagram for the Clock Section

#### Three clock paths are possible:

- 10 MHz Ref. Input used to synchronise SerialBERT

13.5 Gbps with other equipment at 10 MHz

- Ext. Clock Input operates from 620 MHz to 13.5 GHz. This allows the input of a FM modulated clock for Jitter Transfer or Jitter Tolerance measurements

- Internal clock reference operates from 620 MHz to 13.5 GHz

#### **Clock Input**

#### **Table 4: Clock Input**

| Tanto II offort III pat |                                 |

|-------------------------|---------------------------------|

| Frequency range         | 620 MHz to 13.5 GHz             |

| Interface               | AC coupled, 50 $\Omega$ nominal |

| Amplitude               | 150 mV to 2 V                   |

| Connector               | SMA female                      |

|                         |                                 |

#### **Table 5: Delay Control Input**

| Interface            | DC coupled, 50 $\Omega$ nominal  |

|----------------------|----------------------------------|

| Input voltage window | -250 mV to +250 mV               |

| Delay Range          | -100 ps to + 100 ps @ <10.5 Gbps |

| Modulation Bandwidth | DC to 1 GHz                      |

| Connector            | SMA female                       |

#### Modulation

Face Modulation operates between 620 and 13.5 Gbps. It is a linear  $\Delta d/\Delta t$  function that allows diverse signal distortions to be added.

Figure 12: Sinusoidal Jitter

Figure 13: Random Jitter

#### **Trigger Output**

This provides an electrical trigger synchronous with the pattern for use with an oscilloscope or other test equipment. There is a fixed delay of 32 ns typical between trigger and data output for the selected bit. It operates in two modes: pattern trigger and divided clock trigger.

#### **Pattern Trigger Mode**

For PRBS patterns the pulse is synchronized with a user specified trigger pattern. The repetition rate is 1 pulse for every 4th pattern repetition. For alternate patterns the trigger pulse occurs at bit 0 of the selected pattern. For all other patterns, the trigger pulse is synchronized to a user-definable bit in the pattern.

#### **Divided Clock Mode**

In divided clock mode the trigger is a square wave at the clock rate divided by 2, 4, 8, 10, 16, 20, 40, 64, 128.

#### Table 6: Specifications

| Pulse width      | Square wave                     |

|------------------|---------------------------------|

| Levels           | High: +0.5 V; Low -0.5 V typ.   |

| Transition times | 35 ps typical                   |

| Interface        | DC coupled, 50 $\Omega$ nominal |

| Connector        | SMA female                      |

|                  |                                 |

#### **Auxiliary Input**

This port can be used to control user programmable, alternate test patterns or inhibit data output (force the output data to a fixed low level). When Alternate Pattern Mode is selected the instrument will output one of two patterns (A or B). The auxiliary input controls which pattern is output in one of two modes. In both modes, switching between patterns is at the end of a pattern and is 'hitless' (error free).

#### Mode 1: One-shot

A rising edge on the auxiliary input inserts a single version of pattern B into repetitions of pattern A.

#### Mode 2: Alternate

The logic state of the signal at the auxiliary input determines which pattern is output. An active (TTL high) signal will output Pattern 3.

The auxiliary input may also be used to inhibit the data output signal. If Alternate Pattern mode is not selected, an active (TTL high) signal at the auxiliary input port forces (gates) the data to a logic zero at the next 32-bit boundary in the pattern.

#### **Auxiliary Input**

Switch between two different data sequences using an external trigger pulse

#### Figure 14: External Trigger Pulse

Table 7: Specifications

| Interface           | DC coupled, 50 $\Omega$ nominal |

|---------------------|---------------------------------|

| Levels              | TTL levels                      |

| Minimum Pulse Width | 100 ns                          |

| Connector           | SMA female                      |

### Patterns

#### **PRBS (HW Generated)**

- $2^{31}$  1 Polynomial:  $x^{31} + x^{28} + 1 = 0$  (inverted)

- $2^{23}$  1 Polynomial:  $x^{23} + x^{18} + 1 = 0$ (inverted) (ITU-T 0.151)

- $\cdot 2^{15} 1$  Polynomial:  $x^{15} + x^{14} + 1 = 0$ (inverted) (ITU-T 0.151)

- $2^{11}$  1 Polynomial:  $x^{11} + x^9 + 1 = 0$ (inverted) (ITU-T 0.152)

- $2^{10}$  1 Polynomial:  $x^{10} + x^7 + 1 = 0$  (inverted)

- $2^7 1$  Polynomial:  $x^7 + x^6 + 1 = 0$ (inverted) (ITU-T V.29)

#### **Zero Substitution**

Zeros can be substituted for data to extend the longest run of zeros in the patterns below. The longest run can be extended to the pattern length -1. The bit following the substituted zeros is set to 1.

#### Variable Mark Density

The ratio of ones to total bits in the patterns below can be set to 1/8, 1/4, 1/2, 3/4, or 7/8.

Available test patterns for zero and variables:

- $\cdot$  8388608 bits based on 223-1 PRBS

- $\cdot$  32768 bits based on 215-1 PRBS

- · 8192 bits based on 2<sup>13</sup>-1 PRBS

- · 2048 bits based on 211-1 PRBS

- · 1024 bits based on 2<sup>10</sup>-1 PRBS

- · 128 bits based on 27-1 PRBS

#### **User-programmable Test Patterns**

User defined patterns are available with variable length from 1 bit to 33,554,432 bits (2<sup>25</sup>).

#### Alternate Test Pattern

Switch between two equal length user programmable patterns, each up to 16,777,216 bits. Switching is possible by using a front panel key, GP-IB or the auxiliary input port. Changeover is synchronous with the end of the pattern. The length of the alternating patterns should be a multiple of 512 bits. Two methods of controlling pattern changeover are available: one-shot and alternate.

#### **External Error Inject Input**

The external "Error Inject Input" adds a single error to the data output for each rising edge at the input.

#### **Table 8: Specifications**

| Tuble 6. opcontoutions |                                 |

|------------------------|---------------------------------|

| Interface              | DC coupled, 50 $\Omega$ nominal |

| Levels                 | TTL compatible                  |

| Minimum pulse width    | 100 ns                          |

| Connector              | SMA female                      |

|                        |                                 |

#### **Delay Control Input**

The delay control modulates the delay of the data ouputs.

#### Table 9: Specifications

| Interface            | DC coupled, 50 $\Omega$ nominal |

|----------------------|---------------------------------|

| Input Voltage Window | -250 mV to +250 mV              |

| Delay Range          | -100 ps to +100 ps @ 10.5 Gbps  |

| Modulation Bandwidth | DC to 1 GHz                     |

| Connector            | SMA female                      |

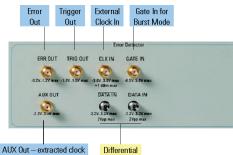

### **Error Detector**

(CDR) or data stream Data In

#### Figure 15: Front view Error Detector

#### **Data Input**

#### Features:

- Differential data inputs

- Data polarity normal or inverted data. .

- Clock/Data delay adjust.

- . Clock/Data auto-alignment.

- 0/1 decision threshold auto-alignment.

- Clock data recovery (CDR) for selected frequency ranges or ext. clock

#### Table 10: Parameters for N4901B Error Detector

| Range of operation         | 620 Mbps to 13.5 Gbps                |     |

|----------------------------|--------------------------------------|-----|

| Impedance                  | Single-ended: 50 $\Omega$ , -2.0V to |     |

|                            | +3.0V terminated <sup>(1)</sup>      |     |

|                            | Differential: 100 $\Omega$           |     |

| Termination Voltage        | -2 V to +3 V or off (true            |     |

|                            | differential mode)                   | (1) |

| Format                     | NRZ                                  |     |

| Max Input Amplitude        | 2.0 V                                |     |

| Sensitivity                | <50 mV pp (2                         |     |

| Decision threshold range   | -2 V to +3 V in 0.1 mV steps         |     |

| Max Levels                 | -2.2V to +3.2V                       |     |

| Phase Margin               | 1UI - 12ps typical                   | (3) |

| Clock/Data phase alignment | ent ±0.75 ns in 100 fs steps         |     |

| Clock data recovery (CDR)  | ) 9.9 Gbps to 10.9 Gbps              |     |

|                            | 4.23 Gbps to 6.40 Gbps               |     |

|                            | 2.11 Gbps to 3.20 Gbps               |     |

| CDR Output Jitter          | 0.01 UI <sub>rms</sub> typical       |     |

| Connector                  | 2.4 mm female                        |     |

|                            |                                      |     |

(1) A user has to define a 2V operating voltage window, which is in the range between -2.0 V to +3.0 V. Data signals, termination voltage and decision threshold have to be within this voltage window.

(2) @ 10 Gbps, BER 10<sup>-12</sup>, PRBS 2<sup>31</sup> -1.

(3) Based on internal clock

#### **Clock Input**

#### **Table 11: Specifications**

| Frequency range | 620 MHz to 13.5 GHz             |

|-----------------|---------------------------------|

| Interface       | AC coupled, 50 $\Omega$ nominal |

| Amplitude       | 100 mV to 1.2 V                 |

| Connector       | SMA female                      |

Possibilites for CDR movement or External Clock Input.

### **Trigger Out**

**Error Detector Pattern Trigger Output** This provides an electronic trigger synchronous with the selected error detector reference pattern. It operates in two modes, pattern trigger and divided clock trigger.

#### **Pattern Trigger Mode**

This provides an electrical trigger synchronous with the selected error detector reference pattern. In pattern mode the pulse is synchronized to repetitions of the output pattern. For PRBS patterns the repetition rate is 1 pulse for every 4th pattern repetition

#### **Divided Clock Mode**

In divided clock mode the trigger is a square wave at the clock rate divided by 4, 8, 16, 32, 40, 64, 128.

#### **Table 12: Specifications**

| Interface                          | DC coupled, 50 $\Omega$ nominal    |  |

|------------------------------------|------------------------------------|--|

| Levels High: + 0.5 V; Low: - 0.5 V |                                    |  |

| Minimum pulse width                | pattern length x clock period/2 at |  |

|                                    | 10Gb/s with 1000 bits = 50 ns      |  |

| Connector                          | SMA female                         |  |

#### **Errors Output**

This provides an electrical signal to indicate received errors. The output is the logical 'OR' of errors in a 128-bit segment of the data.

#### **Table 13: Specifications**

| Interface Format                  | RZ, active high                    |  |

|-----------------------------------|------------------------------------|--|

| Interface DC coupled, 50Ω nominal |                                    |  |

| Levels                            | High: 1V nominal; Low: 0 V nominal |  |

| Pulse Width                       | 128 clock periods                  |  |

| Connector                         | SMA female                         |  |

#### **Gating Input**

The Gating Input is used to enable the error counters including during burst gating mode. In both these cases the error counters will always be enabled for a multiple of 512 pattern bits

#### Table 14<sup>.</sup> Gating Input

| Interface levels | TTL levels        |

|------------------|-------------------|

| Pulse width      | 256 clock periods |

| Connector        | SMA female        |

Connecting an external termination to the gating input will pull it low and disable the instrument error counters. Gating resumes when the Gating Input returns high.

#### **AUX Output**

This output can be used to provide either clock or data signals:

**CLOCK:** clock signals from the input or recovered clock signals in CDR mode

**DATA:** data after being compared with the threshold

| Table ' | 15· | Specifications of AUX Ou | t |

|---------|-----|--------------------------|---|

| Ianic   | 13. | opecifications of AOA ou |   |

| Interface | AC coupled, 50 $\Omega$ nominal |

|-----------|---------------------------------|

| Amplitude | 600 mV nominal                  |

| Connector | SMA female                      |

#### Automatic Clock-to .Data Alignment

An important feature of the SerialBERT error detector is the ability to automatically align the clock and data inputs such that the error detector samples are in the middle of the eye (in the time axis).

### Automatic Threshold Center Search

#### Automatic Clock-Data Sampling Point Search

**Figure 16: Automatic Optimum Sampling Point Location**

#### **Audible Error Indicator**

Selectable to indicate errors, instantaneous error ratios, and errors above user-defined thresholds. On/Off volume control, and audible pitch changes with higher pitch corresponding to higher BER

#### Automatic 0/1 Threshold Centre

The 0/1 threshold center operation is used to set the 0/1 threshold midway between two points, top and bottom of the eye where the bit error ration is equal to a selectable threshold. There are three methods of determining the 0/1Threshold of input signals at the error detector data input: Manual, Automatic Track and Automatic Center.

#### Manual

0/1 threshold can be set manually.

#### **Automatic Track**

This continuously tracks the mean DC level of the input signal and adjusts the threshold accordingly. The 0/1 threshold calculated is displayed. Adjustment is made within approximately 100ms. limited to a 2V window selected by the user.

### Automatic Centre

The error detector sets the 0/1 threshold midway between two points, the top and bottom of the eye, where the bit error ratio is equal to a selectable threshold. The eye height is calculated and displayed. It is limited to a 2V window selected by the user.

### **Cable Droop Compensation**

The N4901B SerialBERT 13.5 Gbps provides an excellent waveform at the end of a 24" cable (N4910A). The cable droop is compensated and there is an excellent transition time <25 ps.

### **Mechanical Parameters**

| Table 16: General Mainframe Characteristics |                            |  |

|---------------------------------------------|----------------------------|--|

| Operating Temperature                       | 5 °C to 40 °C              |  |

| Storage Temperature                         | -40 °C to +70 °C           |  |

| Humidity 5 - 40 °C, 95% rel.Humid           |                            |  |

| Power Requirements                          | 100 - 240 Vac, ± 10%, 47 - |  |

|                                             | 63 Hz, 350 Vac             |  |

| Physical dimensions                         | Width: 424.5 mm            |  |

|                                             | Height: 221.5 mm           |  |

|                                             | Depth: 580.0 mm            |  |

| Weight (Net)                                | 24.5 kg                    |  |

| Weight (shipping) (Max) 36.0 kg             |                            |  |

### **Order Instructions**

| N4901B                                                      | SerialBERT 13.5 Gbps, USB Mouse                                                             |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 10-Configuration:<br>N4901B-100<br>N4901B-200<br>N4901B-300 | Pattern Generator & Erro <b>r</b> Detector<br>Pattern Generator only<br>Error Detector only |

| Calibration/Test Dat                                        |                                                                                             |

| N4901B-UK6                                                  | Commercial Calibration with Test Data                                                       |

| Accessories:                                                |                                                                                             |

| N4910A                                                      | Cable Kit: 2.4mm matched cable pair                                                         |

| N4911A-002                                                  | Adapter 3.5mm female to 2.4 mm male                                                         |

| N4912A                                                      | 2.4mm, 50 Ohm termination, male                                                             |

| Warranty                                                    |                                                                                             |

| R1280A                                                      | Standard Warranty:                                                                          |

|                                                             | 1 year Return-to-Agilent                                                                    |

|                                                             | Extended Warranty:                                                                          |

|                                                             | 3 years Return-to-Agilent, or                                                               |

|                                                             | 5 years Return-to-Agilent                                                                   |

| Calibration                                                 |                                                                                             |

| R1282A                                                      | Calibration plans are available to order for 3                                              |

Calibration plans are available to order for 3 or 5 years; calibration interval 12 month

#### **Related Literature**

| • | N4902B SerialBERT 7 Gbps                                 | 5989-0399EN |

|---|----------------------------------------------------------|-------------|

|   | Datasheet                                                |             |

| • | Agilent Physical Layer Test<br>Product Overview          | 5988-5914EN |

| • | N4902B SerialBERT 13.5 Gbps                              | 5988-9676EN |

|   | Product Note                                             |             |

| • | N4900 SerialBERT<br>Jitter Fundamentals Application Note | 5989-0089EN |

| • | Jitter Tolerance Testing                                 | 5989-0223EN |

|   | 81250 ParBERT Application Note                           |             |

| • | ParBERT 81250<br>Product Overview                        | 5968-9188E  |

Pub. No.

#### **Specification Assumptions**

The specifications in this brochure describe the instrument's warranted performance. Non-warranted values are stated as typical. All specifications are valid in a range from 5°C to 40°C ambient temperature after a 30 minute warm-up phase. If not otherwise stated, all inputs and outputs need to be terminated with 50 Ohms to ground. All specifications, if not otherwise stated, are valid using the recommended N4910A cable set (24 mm, 24" matched pair).

#### Agilent Technologies' Test and Measurement Support, Services, and Assistance

Agilent Technologies aims to maximize the value you receive, while minimizing your risk and problems. We strive to ensure that you get the test and measurement capabilities you paid for and obtain the support you need. Our extensive support resources and services can help you choose the right Agilent products for your applications and apply them successfully. Every instrument and system we sell has a global warranty. Support is available for at least five years beyond the production life of the product. Two concepts underlay Agilent's overall support policy: "Our Promise" and "Your Advantage."

#### **Our Promise**

Our Promise means your Agilent test and measurement equipment will meet its advertised performance and functionality. When you are choosing new equipment, we will help you with product information, including realistic performance specifications and practical recommendations from experienced test engineers. When you use Agilent equipment, we can verify that it works properly, help with product operation, and provide basic measurement assistance for the use of specified capabilities, at no extra cost upon request. Many self-help tools are available.

#### Your Advantage

Your Advantage means that Agilent offers a wide range of additional expert test and measurement services, which you can purchase according to your unique technical and business needs. Solve problems efficiently and gain a competitive edge by contracting with us for calibration, extra-cost upgrades, out-of-warranty repairs, and on-site education and training, as well as design, system integration, project management, and other professional services. Experienced Agilent engineers and technicians worldwide can help you maximize your productivity, optimize the return on investment of your Agilent instruments and systems, and obtain dependable measurement accuracy for the life of those products.

#### www.agilent.com/find/emailupdates

Get the lastest information on the products and applications you select.

#### www.agilent.com www.agilent.com/find/N4900 series www.agilent.com/find/product services

By internet, phone, or fax, get assistance with all your test & measurement needs

**Online assistance:** www.agilent.com/find/assist

**Phone or Fax** United States: (tel) 800 452 4844

Canada: (tel) 877 894 4414 (fax) 905 282 6495

China: (tel) 800 810 0189 (fax) 800 820 2816

Europe: (tel) (31 20) 547 2111 (fax) (31 20) 547 2390

Japan: (tel) (81) 426 56 7832 (fax) (81) 426 56 7840

Korea: (tel) (82 2) 2004 5004 (fax) (82 2) 2004 5115

Latin America: (tel) (650) 752 5000

Taiwan: (tel) 0800 047 866 (fax) 0800 286 331

**Other Asia Pacific Countries:** (tel) (65) 6375 8100 (fax) (65) 6836 0252 Email: tm asia@agilent.com

Product specifications and descriptions in this document subject to change without notice.

© Agilent Technologies, Inc. 2004 Printed in Germany, 5 February 2004 5989-0398EN

"MS Windows XP" is a registered trademark of Microsoft Corporation