# HY51C1000 IM×1-Bit CMOS DRAM

M131202B-APR91

#### DESCRIPTION

The HY51C1000 is a high speed, low power 1,048,576×1 bit CMOS dynamic random access memory. Fabricated with the HYUNDAI CMOS process, the HY51C1000 offers a fast page mode for high bandwidth and clock-free page operation, fast usable speed, CMOS standby current and inherently high CMOS reliability.

All inputs and outputs are TTL compatible. Input and output capacitances are significantly lowered to allow increased system performance.

Fast page mode operation allows random or sequential access of up to 1,024 bits within a row with cycle times as fast as 45ns. Because of static circuitry, the CAS clock is no longer in the critical timing path. The flow-through column latch allows address pipelining while relaxing many critical system timing requirements for fast usable speed. These features make the HY51C1000 ideally suited for cache based mainframe and mini computers, graphics, digital signal processing, and high performance microprocessor systems.

When  $\overline{RAS}$  is  $\geq V_{DD} - 0.2V$ , CMOS standby operation mode is active, and power drops to 1.5 mW (typically).

# BLOCK DIAGRAM RAS ON-CHIP ADDRESS COUNTER RAS CLOCK WRITE CLOCK ODDRESS PRE-DECODER COLUMN ADDRESS DECODER DATA OUTPUT RESTORE ADDRES EQUALIZER ROW ADD MEMORY ARRAY LATCH VBB GENERATOR

#### **FEATURES**

• Low power dissipation

- Operating current, 100ns: 75mA (max.)

- TTL standby current: 2.5mA (max.)

- CMOS standby current: 1.5mA (max.)

Read-Modify-Write capability

- RAS-only, Hidden, CAS-before-RAS refresh capability

- Common I/O capability

- Fast Page mode operation for a sustained data rate up to 22 MHz

- 512 refresh cycles/8 ms

- High reliability 18 pin 300 mil P-DIP and 20/26 pin SOJ

- Fast access time and cycle time (ns)

|                                                   | HY51C1000-80 | HY51C1000-10 | HY51C1000-12 |

|---------------------------------------------------|--------------|--------------|--------------|

| Max RAS Access<br>Time, t <sub>RAC</sub>          | 80           | 100          | 120          |

| Max CAS Access Time, t <sub>CAC</sub>             | 20           | 25           | 30           |

| Min Fast Page Mode<br>Cycle Time, t <sub>PC</sub> | 45           | 55           | 65           |

| Min Cycle Time, t <sub>RC</sub>                   | 160          | 190          | 220          |

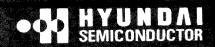

#### PIN CONNECTIONS

#### PIN NAMES

| RAS                            | ROW ADDRESS STROBE    |

|--------------------------------|-----------------------|

| CAS                            | COLUMN ADDRESS STROBE |

| WE                             | WRITE ENABLE          |

| A <sub>0</sub> -A <sub>9</sub> | ADDRESS INPUT         |

| DiN                            | DATA INPUT            |

| Dout                           | DATA OUTPUT           |

| Voo                            | POWER (+5V)           |

| Vss                            | GROUND                |

# ABSOLUTE MAXIMUM RATINGS

| SYMBOL            | PARAMETER                                                             | RATING      | UNT        |

|-------------------|-----------------------------------------------------------------------|-------------|------------|

| TA                | Ambient Temperature                                                   | 0 to 70     | °C         |

| T <sub>STG</sub>  | Storage Temperature (Plastic)                                         | -55 to 125  | °C         |

| V <sub>TERM</sub> | Voltage on Any Pin Except V <sub>DD</sub> Relative to V <sub>SS</sub> | -1.0 to 7.0 | V          |

| V <sub>DD</sub>   | Voltage on V <sub>DD</sub> Relative to V <sub>SS</sub>                | -1.0 to 7.0 | v          |

| I <sub>OUT</sub>  | Data Out Current                                                      | 50          | m <b>A</b> |

| P <sub>T</sub>    | Power Dissipation                                                     | 1.0         | w          |

NOTE: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

# DC CHARACTERISTICS

$(T_A=0$ °C to 70°C,  $V_{DD}=5V\pm 10\%$ ,  $V_{SS}=0V$ , unless otherwise noted.)

| OLD ADO:           |                                                     | DADAMETER TEST COMPETONS S                                                                    | SPEED | HY51C1000 |                     | UNIT       | NOTE |

|--------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|-----------|---------------------|------------|------|

| SYMBOL             | PARAMETER                                           | TEST CONDITIONS                                                                               |       | MIN. MAX. |                     | UNII       | NOIL |

| I <sub>LI</sub>    | Input Leakage Current (any input pin)               | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                              |       |           | 10                  | μΑ         |      |

| Iω                 | Output Leakage Current for<br>High Impedance State  | $\frac{V_{SS} \leq D_{OUT} \leq V_{DD}}{RAS, CAS} \text{ at } V_{IH}$                         |       |           | 10                  | μΑ         |      |

|                    |                                                     |                                                                                               | - 80  |           | 95                  |            |      |

| $I_{DD1}$          | V <sub>DD</sub> Supply Current, Operating           | $t_{RC} = t_{RC} $ (min.)                                                                     | -10   |           | 75                  | m <b>A</b> | 1,2  |

|                    |                                                     |                                                                                               | -12   |           | 70                  |            |      |

| I <sub>DD2</sub>   | V <sub>DD</sub> Supply Current, TTL Standby         | RAS, CAS at V <sub>IH</sub> , other inputs ≥ V <sub>SS</sub>                                  |       |           | 2.5                 | m <b>A</b> |      |

|                    |                                                     |                                                                                               | - 80  |           | 95                  | mA         |      |

| I <sub>DD3</sub>   | V <sub>DD</sub> Supply Current,<br>RAS-only Refresh | $t_{RC} = t_{RC} \text{ (min.)}$                                                              | -10   |           | 75                  |            | 2    |

|                    |                                                     |                                                                                               | -12   |           | 70                  |            |      |

|                    | V <sub>DD</sub> Supply Current,<br>Fast page mode   | Minimum Cycle                                                                                 | - 80  |           | 50                  | mA         |      |

| $I_{\mathrm{DD4}}$ |                                                     |                                                                                               | -10   |           | 40                  |            | 1,2  |

|                    |                                                     |                                                                                               | -12   |           | 35                  |            |      |

| l <sub>DD5</sub>   | V <sub>DD</sub> Supply Current,<br>CMOS Standby     | $\overline{RAS} \ge V_{DD} - 0.2V, \overline{CAS} = V_{IH}, \text{ other inputs } \ge V_{SS}$ |       |           | 1.5                 | mA         |      |

|                    |                                                     |                                                                                               | - 80  |           | 95.                 |            |      |

| $I_{DD6}$          | V <sub>DD</sub> Supply Current,                     | $t_{RC} = t_{RC} \text{ (min.)}$                                                              | - 10  |           | 75                  | mA         | 2    |

|                    | CALO DETOTE IN IS ACTION                            |                                                                                               | - 12  |           | 70                  |            |      |

| VIL                | Input Low Voltage (all inputs)                      |                                                                                               |       | -0.5      | 0.8                 | v          | 3    |

| VIH                | Input High Voltage (all inputs)                     |                                                                                               |       | 2.4       | V <sub>DD</sub> + 1 | v          | 3    |

| V <sub>OL</sub>    | Output Low Voltage                                  | I <sub>OL</sub> = 4.2mA                                                                       |       |           | 0.4                 | v          |      |

| V <sub>OH</sub>    | Output High Voltage                                 | $I_{OH} = -5mA$                                                                               |       | 2.4       |                     | V          |      |

$I_{1DD}$  is dependent on output loading when the device output is selected. Specified  $I_{DD}(max.)$  is measured with output open. 2.  $I_{DD}$  is dependent upon the number of address transitions. Specified  $I_{DD}(max.)$  is measured with a maximum of two transitions per address cycle in

Fast page mode.

3. Specified V<sub>IL</sub> (min.) is steady state operation. During transitions, V<sub>II</sub> may undershoot to −1.0V for a period not to exceed 20ns. All AC parameters are measured with V<sub>IL</sub> (min.)≥ V<sub>SS</sub> and V<sub>IH</sub> (max.) ≤ V<sub>DD</sub>.

# **AC CHARACTERISTICS**

$(T_A=0$ °C to 70°C,  $V_{DD}=5V\pm 10\%$ ,  $V_{SS}=0V$ , unless otherwise noted.)

|    |                     |                                          | HY51C1000 |      |      |      |      | Ī    |       |          |

|----|---------------------|------------------------------------------|-----------|------|------|------|------|------|-------|----------|

| #  | SYMBOL              | MBOL PARAMETER                           | 80 10     |      |      | 1    | 2    | UNIT | NOTES |          |

| Į  |                     |                                          | MIN.      | MAX. | MIN. | MAX. | MIN. | MAX. |       |          |

| 1  | tras                | RAS Pulse Width                          | 80        | 85K  | 100  | 85K  | 120  | 85K  | ns    |          |

| 2  | t <sub>RC</sub>     | Random Read or Write Cycle Time          | 160       |      | 190  |      | 220  |      | ns    |          |

| 3  | t <sub>RP</sub>     | RAS Precharge Time                       | 70        |      | 80   |      | 90   |      | ns    |          |

| 4  | tasr                | Row Address Set-up Time                  | 0         |      | 0    |      | 0    |      | ns    |          |

| 5  | t <sub>RAH</sub>    | Row Address Hold Time                    | 15        |      | 15   |      | 15   |      | ns    | _        |

| 6  | t <sub>CAR</sub>    | Column Address to RAS Set-up Time        | 40        |      | 45   |      | 55   |      | ns    |          |

| 7  | t <sub>RAD</sub>    | RAS to Column Address Delay Time         | 20        | 40   | 20   | 55   | 20   | 65   | ns    | 1        |

| 8  | t <sub>ASC</sub>    | Column Address Set-up Time               | 0         |      | 0    |      | 0    |      | ns    |          |

| 9  | t <sub>CAH</sub>    | Column Address Hold Time                 | 15        |      | 20   |      | 25   |      | ns    | <u> </u> |

| 10 | t <sub>RCD</sub>    | RAS to CAS Delay                         | 25        | 60   | 25   | 75   | 25   | 90   | ns    | 2        |

| 11 | trac                | Access Time From RAS                     |           | 80   |      | 100  |      | 120  | ns    | 3,4,5    |

| 12 | t <sub>CAA</sub>    | Access Time From Column Address          |           | 40   |      | 45   |      | 55   | ns    | 5,6,12   |

| 13 | tCAC                | Access Time From CAS                     |           | 20   |      | 25   |      | 30   | ns    | 6,12     |

| 14 | t <sub>CAS(R)</sub> | CAS Pulse Width in Read Cycle            | 20        |      | 25   |      | 30   |      | ns    |          |

| 15 | t <sub>RSH(R)</sub> | RAS Hold Time in Read Cycle              | 20        |      | 25   |      | 30   |      | ns    |          |

| 16 | t <sub>RCS</sub>    | Read Command Set-up Time                 | 0         |      | 0    |      | 0    |      | ns    |          |

| 17 | t <sub>RCH</sub>    | Read Command Hold Time Referenced to CAS | 5         |      | 5    |      | 5    |      | ns    | 7        |

| 18 | trrh                | Read Command Hold Time Referenced to RAS | 5         |      | 5    |      | 5    |      | ns    | 7        |

| 19 | t <sub>CRP</sub>    | CAS to RAS Precharge Time                | 5         | ļ    | 5    |      | 10   |      | ns    |          |

| 20 | toff                | Output Buffer Turn Off Delay             | 0         | 20   | 0    | 25   | 0    | 30   | ns    | 8        |

| 21 | t <sub>OH</sub>     | Output Data Hold Time From CAS           | 0         |      | 0    |      | 0    |      | ns    | 8        |

| 22 | twp                 | Write Pulse Width                        | 10        |      | 10   |      | 15   |      | ns    |          |

| 23 | t <sub>CP</sub>     | CAS Precharge Time                       | 10        |      | 10   |      | 15   |      | ns    |          |

| 24 | t <sub>AR</sub>     | Column Address Hold Time From RAS        | 60        |      | 70   |      | 80   |      | ns    |          |

| 25 | t <sub>CAS(W)</sub> | CAS Pulse Width in Write Cycle           | 25        |      | 30   |      | 35   |      | ns    |          |

| 26 | t <sub>RSH(W)</sub> | RAS Hold Time in Write Cycle             | 25        |      | 30   |      | 35   |      | ns    |          |

| 27 | twcr                | Write Command Hold Time From RAS         | 60        |      | 70   |      | 80   |      | ns    |          |

| 28 | twcs                | Write Command Set-up Time                | 0         |      | 0    |      | 0    |      | ns    | 9,10     |

| 29 | twch                | Write Command Hold Time                  | 15        |      | 20   |      | 25   |      | ns    |          |

| 30 | t <sub>DS</sub>     | Data-In Set-up Time                      | 0         |      | 0    |      | 0    |      | ns    | 11       |

| 31 | t <sub>DH</sub>     | Data-In Hold Time                        | 15        |      | 20   |      | 25   |      | ns    | 11       |

| 32 | tohr                | Data-In Hold Time Reference to RAS       | 60        |      | 70   |      | 80   |      | ns    |          |

| 33 | t <sub>RWC</sub>    | RMW Cycle Time                           | 190       |      | 220  |      | 255  |      | ns    |          |

| 34 | trrw                | RMW Cycle RAS Pulse Width                | 110       |      | 130  | 1    | 155  |      | ns    |          |

| 35 | t <sub>RWD</sub>    | RAS to WE Delay in RMW Cycle             | 80        |      | 100  | 1    | 120  |      | ns    | 9        |

| 36 | t <sub>CWD</sub>    | CAS to WE Delay                          | 20        | 1    | 25   |      | 30   |      | ns    | 9        |

| 37 | tawp                | Column Address to WE Delay               | 40        | -    | 45   |      | 55   |      | ns    | 9        |

| 38 | <del> </del>        | Access Time From Column Precharge        |           | 40   |      | 50   |      | 60   | ns    | 12       |

|    |                  | HY51C1000                               |      |      |      |      |      |      |      |       |

|----|------------------|-----------------------------------------|------|------|------|------|------|------|------|-------|

| #  | SYMBOL           | PARAMETER                               | 80   |      | 10   |      | 12   |      | UNIT | NOTES |

|    |                  |                                         | MIN. | MAX. | MIN. | MAX. | MIN. | MAX. |      |       |

| 39 | t <sub>PC</sub>  | Fast page mode Read or Write Cycle time | 45   |      | 55   |      | 65   |      | ns   |       |

| 40 | t <sub>PCM</sub> | Fast page mode Read-Modify-Write Cycle  | 70   |      | 85   |      | 100  |      | ns   |       |

| 41 | t <sub>RWL</sub> | Write Command to RAS Lead Time          | 25   |      | 25   |      | 30   |      | ns   |       |

| 42 | t <sub>CWL</sub> | Write Command to CAS Lead Time          | 25   |      | 25   |      | 30   |      | ns   |       |

| 43 | t <sub>RPC</sub> | RAS to CAS Precharge Time               | 0    |      | 0    |      | 0    |      | ns   |       |

| 44 | t <sub>CSR</sub> | CAS Set-up Time (CAS Before RAS Cycle)  | 10   |      | 10   |      | 10   |      | ns   |       |

| 45 | tchr             | CAS Hold Time (CAS Before RAS Cycle)    | 20   |      | 30   |      | 30   |      | ns   |       |

| 46 | t <sub>CSH</sub> | CAS Hold Time                           | 80   |      | 100  |      | 120  |      | ns   |       |

| 47 | t <sub>T</sub>   | Transition Time (Rise and Fall)         | 3    | 25   | 3    | 25   | 3    | 25   | ns   | 13,14 |

| 48 | t <sub>RI</sub>  | Refresh Interval (512 Cycle)            |      | 8    |      | 8    |      | 8    | ms   | 15    |

- [ Operation within the tRAD (max.) limit insures that tRAC (max.) can be met. tRAD (max.) is specified as a referenced point only. If tRAD is greater than the specified  $t_{RAD}$  (max.) limit, then the access time is controlled by  $t_{CAA}$  and  $t_{CAC}$

- 2.  $t_{RCD}$  (max.) is specified for reference only. Operation within  $t_{RCD}$  (max.) and  $t_{RAD}$  (max.) limit insure that  $t_{RAC}$  (max.) and  $t_{CAA}$  (max.) can be met. If  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max.) then the access time is controlled by  $t_{CAA}$  and  $t_{CAC}$ .

3. Assume  $t_{RAD} \le t_{RAD}$  (max.). If  $t_{RAD}$  is greater than  $t_{RAD}$  (max.) then  $t_{RAC}$  will increase by the amount that  $t_{RAD}$  exceeds  $t_{RAD}$  (max.).

4. Assume  $t_{RCD} \le t_{RCD}$  (max.). If  $t_{RCD}$  is greater than  $t_{RCD}$  (max.) then  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds  $t_{RCD}$  (max.)

- Measured with a load equivalent to two TTL loads and 100 pF.

- 6. Assume  $t_{RAD} \ge t_{RAD}$  (max.)

- Either  $t_{RRH}$  or  $t_{RCH}$  must be satisfied for a read cycle.  $t_{OF}$  and  $t_{OH}$  define the time at which the data output achieves the open circuit condition and is not referenced to the output voltage levels.

- 9. twcs, twhe, twhe, trub, tamb, temb, are not restrictive operating parameters.

- 10. t<sub>WCS</sub> (min.) must be satisfied in the early write cycle. 11. t<sub>DS</sub> and t<sub>DH</sub> are referenced to the latter occurrence of CAS or WE.

- 12. Access time is determined by the longer of  $t_{CAA}$ ,  $t_{CAC}$  or  $t_{CAP}$ .

- 13.  $t_T$  is measured between  $V_{1H}$  (min.) and  $V_{1L}$  (max.)

- 14. AC measurements assume t<sub>T</sub> = 5ns.

- 15. An initial pause of 200 µs is required after power-up and followed by a minimum of 8 initialization cycles (any combination of cycles containing a RAS clock such as RAS-only refresh). 8 initialization cycles are required after extended period of bias without clocks.

#### **CAPACITANCE**

$(T_A=25^{\circ}C, V_{DD}=5V\pm 10\%, V_{SS}=0V, \text{ unless otherwise noted.})$

| SYMBOL           | PARAMETER                | TYP. | MAX. | UNIT |

|------------------|--------------------------|------|------|------|

| C <sub>INI</sub> | Address, D <sub>IN</sub> | _    | 6    | pF   |

| C <sub>IN2</sub> | RAS, CAS, WE             | _    | 8    | pF   |

| C <sub>OUT</sub> | D <sub>OUT</sub>         | _    | 8    | pF   |

NOTE: Capacitance is measured at the worst case of voltage levels with a programmable capacitance meter.

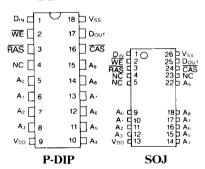

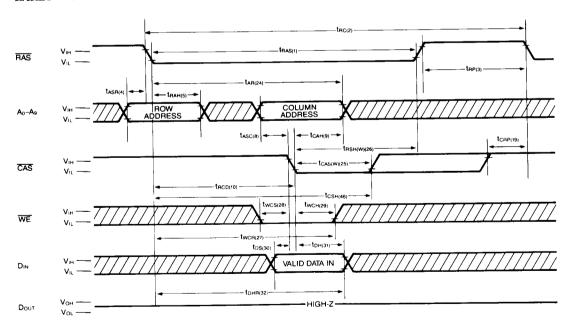

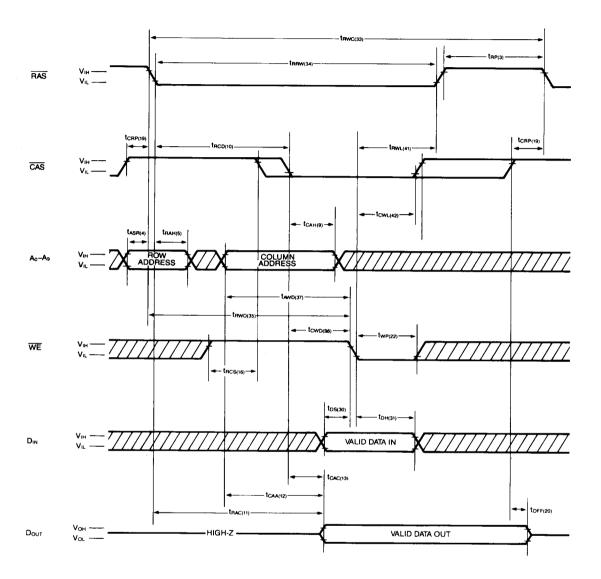

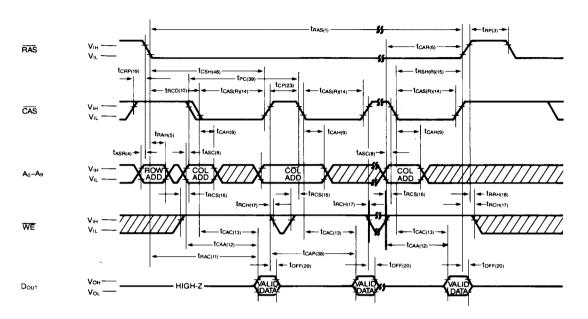

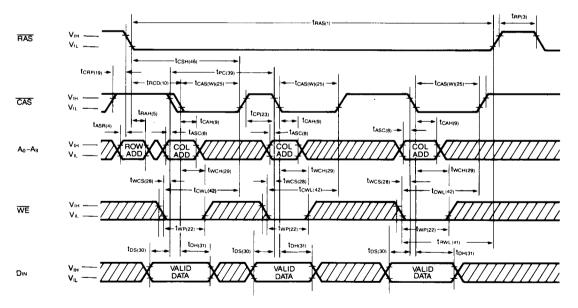

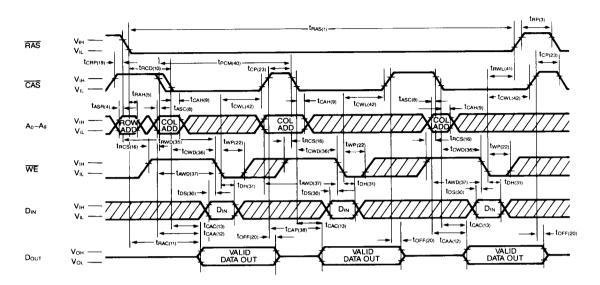

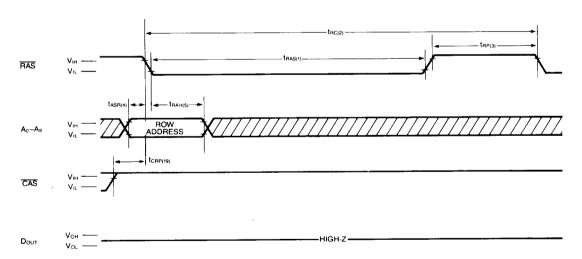

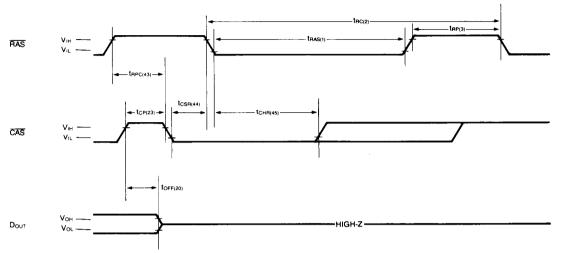

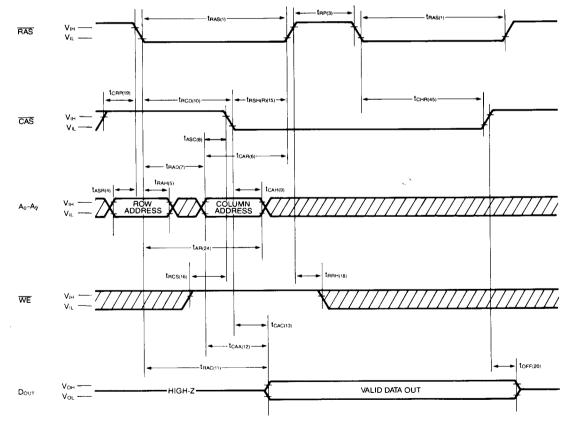

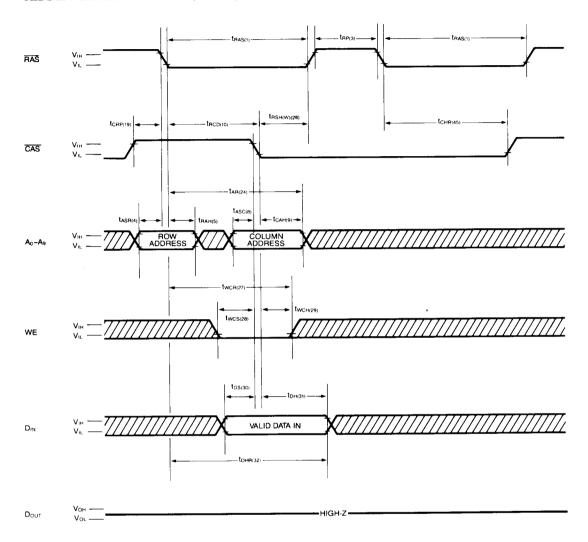

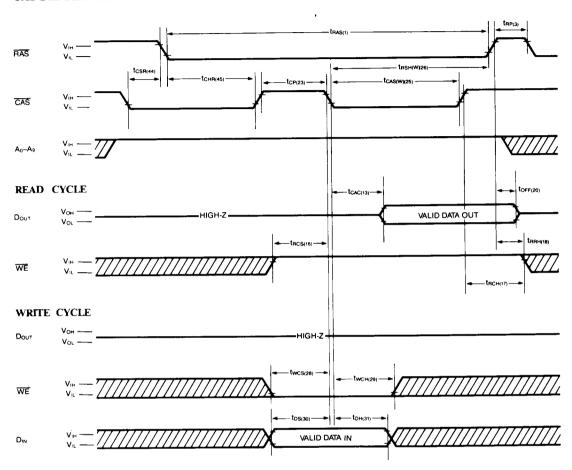

# TIMING DIAGRAM

#### READ CYCLE

# EARLY WRITE CYCLE

#### READ-MODIFY-WRITE CYCLE

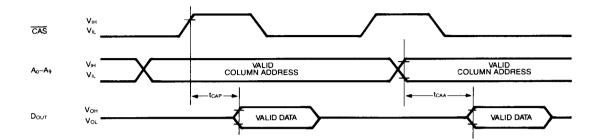

#### FAST PAGE MODE READ CYCLE

# FAST PAGE MODE EARLY WRITE CYCLE

# FAST PAGE MODE READ-MODIFY-WRITE CYCLE

# RAS-ONLY REFRESH CYCLE

# CAS-BEFORE-RAS REFRESH CYCLE

Note: WE, Ao-As=Don't care

# HIDDEN REFRESH CYCLE (READ)

# HIDDEN REFRESH CYCLE (WRITE)

# CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE

#### **FUNCTIONAL DESCRIPTION**

The HY51C1000 is a CMOS dynamic RAM optimized for high data bandwidth and low power applications. The functionality is similar to a traditional dynamic RAM. The HY51C1000 reads and writes one bit of data by multiplexing 20 bit address into 10 bit row and 10 bit column address. The row address is latched by Row Address Strobe( $\overline{RAS}$ ). The column address, however, flows through the internal address buffer and is latched by the Column Address Strobe ( $\overline{CAS}$ ). Because access time is primarily dependent on a valid column address, the delay time between  $\overline{RAS}$  and  $\overline{CAS}$  can be long without affecting the access time.

#### MEMORY CYCLE

The memory cycle is initiated by bringing  $\overline{RAS}$  low. Any memory cycle once initiated must not be ended or aborted prior to fulfilling the minimum  $t_{RAS}$  timing specification. This ensures proper device operation and data integrity. Additionally, a new cycle can not be initiated until the minimum precharge time  $t_{RP}/t_{CP}$  has elapsed.

#### READ CYCLE

A read cycle is performed by holding the Write Enable ( $\overline{WE}$ ) signal high during a  $\overline{RAS}/\overline{CAS}$  operation. The column address must be held for a minimum time specified by  $t_{AR}$ . Data output becomes valid only when  $t_{RAC}$ ,  $t_{CAC}$  and  $t_{CAA}$  are all satisfied. Consequently, the access time is dependent upon the timing relationship among the  $t_{RAC}$ ,  $t_{CAC}$  and  $t_{CAA}$ . For example, the access time is limited by  $t_{CAA}$  when  $t_{RAC}$  and  $t_{CAC}$  are both satisfied.

#### WRITE CYCLE

A write cycle is performed by taking WE and CAS low during a RAS operation. The column address is latched by CAS. The write can be WE controlled or CAS controlled depending upon the latter of WE or CAS low transition.

Consequently, the input data must be valid at or before the falling edge of  $\overline{WE}$  or  $\overline{CAS}$ , whichever occurs last. In a  $\overline{CAS}$  controlled write cycle (the leading edge or  $\overline{WE}$  occurs priors to or coincident with the  $\overline{CAS}$  low transition) the output( $D_{OUT}$ ) pin will be in the high impedance state at the beginning of the write function. Terminating the write action with  $\overline{RAS}$  or  $\overline{CAS}$  going high will maintain the data output ( $D_{OUT}$ ) in the high impedance state.

#### REFRESH CYCLE

To retain data, 512 RAS refresh cycle are required in an 8 ms period. The refresh operation can be performed two ways:

- Clocking each of 512 row address(A<sub>0</sub> through A<sub>8</sub>) with RAS at least every 8 ms period. Any combination of RAS cycle such as read, write, read-modify-write, or RAS-Only refresh cycle will perform a refresh on the selected row.

- 2. CAS-before-RAS refresh cycle: IF CAS go low prior to RAS go low, the chip enters a CAS-before-RAS refresh cycle. In CAS before-RAS-refresh cycle the HY51C1000 will use an internal nine-bit counter output as the source of the row address and will ignore the external address input.

This CAS-before-RAS refresh mode is a refresh only mode and no data access is allowed. Also, the CAS-before-RAS refresh cycle does not cause device selection and the state of the data output pin will remain in a high impedance state.

In order to guarantee the reliable operation of the CAS-before-RAS refresh mode, a internal counter test mode is provided. The user can use the counter test mode to write in a data pattern consecutively (512 write cycles) and then verify the data which has been written by 512 consecutive read cycles.

#### DATA RETENTION MODE

The HY51C1000 offers a CMOS standby mode that is entered by causing the  $\overline{RAS}$  clock

to swing between a valid  $V_{\rm 1L}$  and an "extra high"  $V_{\rm 1H}$  within 0.2V of  $V_{\rm DD}$ . While the  $\overline{RAS}$  clock is at the "extra high" level, the HY51C1000 power consumption is reduced to the low  $I_{\rm DDS}$  level. Overall  $I_{\rm DD}$  consumption when operating in this mode can be calculated as follows:

$$I = \frac{(t_{RC}) \times (I \text{ active}) + (t_{RX} - t_{RC}) \times (I_{DDS})}{t_{RX}}$$

Where  $t_{RC}$ =Refresh Cycle Time  $t_{RX}$ =Refresh Interval/512

#### FAST PAGE MODE OPERATION

Fast page mode operation permits all 1024 columns within a selected row of the device to be randomly accessed at a high data rate. Maintaining  $\overline{RAS}$  low while successive  $\overline{CAS}$  cycles are performed retains the row address internally, eliminating the need to reapply it. The column address buffer acts as a transparent or flow through latch while  $\overline{CAS}$  is high. Access begins from the valid column address rather than from  $\overline{CAS}$ , eliminating  $t_{ASC}$  and  $t_T$  from the critical timing path.  $\overline{CAS}$  latch the address into column address buffer and acts as an output enable.

During this operation, read, write, and read-modify-write, or read-write-read cycles are possible at random or sequential address within a row. Following the entry cycle into fast page mode, access time is  $t_{CAA}$  or  $t_{CAP}$  dependent. If the column address is valid prior to or coincident by  $t_{CAP}$  as shown in figure 1. If the column address is valid after the rising edge of  $\overline{CAS}$ , then the access time is determined by the valid column address specified by  $t_{CAA}$ . For both cases, the falling edge of  $\overline{CAS}$  latches the address and enable the output.

Fast page mode provides a sustanined data rate over 22  $MH_Z$  for applications that require high data rates, such as bit mapped graphics or high speed signal processing. The following equation can be used to calculate the data rate:

Data Rate =

$$\frac{1024}{t_{RC} + 1023 \times t_{PC}}$$

#### DATA OUT OPERATION

The HY51C1000 data output( $D_{OUT}$ ), which has tri-state capability, is controlled by  $\overline{CAS}$ . During a  $\overline{CAS}$  the high state ( $\overline{CAS}$  at  $V_{IH}$ ), the data output is in the high impedance state. The following table summarize the  $D_{OUT}$  state for various types of cycles.

| CYCLE                      | D <sub>OUT</sub> STATE   |

|----------------------------|--------------------------|

| Read Cycle                 | Data from Addressed      |

|                            | Memory Cell              |

| CAS Controlled Write Cycle | High Impedance           |

| (Early Write)              |                          |

| WE Controlled Write Cycle  | Active, Not Valid        |

| (Late Write)               |                          |

| Read-Modify-Write Cycle    | Data from Addressed      |

|                            | Memory Cell              |

| Fast Page Mode Read Cycle  | Data from Addressed      |

|                            | Memory Cell              |

| Fast Page Mode Write Cycle | High Impedance           |

| (Early Write)              |                          |

| Fast Page Mode Read-       | Data from Addressed      |

| Modify-Write Cycle         | Memory Cell              |

| RAS-Only Refresh Cycle     | High Impedance           |

| CAS-Before-RAS Refresh     | Data remain the previous |

| Cycle                      | cycle's state            |

|                            | (high Impedance or low   |

|                            | Impedance                |

| CAS-Only Cycle             | High Impedance           |

#### POWER ON

An initial pause of 200  $\mu$ s is required after the application of the  $V_{DD}$  power supply, followed by a minimum of eight initialization cycles (any combination of cycles containing a  $\overline{RAS}$  clock such as  $\overline{RAS}$ -only refresh cycle). Eight initialization cycles are required after extended periods of bias without clocks (greater than the refresh interval).

The  $V_{\rm DD}$  current (  $I_{\rm DD}$ ) requirement of the HY51C1000 during power on is dependent upon the input levels of  $\overline{RAS}$  and  $\overline{CAS}$ . If  $\overline{RAS} = V_{SS}$  during power on, the device will go into an active cycle and  $I_{\rm DD}$  will exhibit large current transients. It is recommended that  $\overline{RAS}$  and  $\overline{CAS}$  track with  $V_{\rm DD}$  or be held at a valid  $V_{\rm IH}$  level during power on.

# FIGURE 1. FAST PAGE MODE ACCESS TIME DETERMINATION