### Description

The  $\mu$ PD7002 is a high performance, low power, 10-bit CMOS analog-to-digital converter. Using the integrating technique the 7002 offers the designer full microprocessor interface, four multiplexed analog inputs, and low power CMOS construction.

#### **Features**

### **Ordering Information**

| Part     |             | Operating<br>Temperature |

|----------|-------------|--------------------------|

| Number   | Package     | Range                    |

| μPB7002C | Plastic DIP | -20°C to +70°C           |

# Absolute Maximum Ratings $T_A = +25$ °C

| . A - EO O            |                     |

|-----------------------|---------------------|

| Operating Temperature | -20°C to +70°C      |

| Storage Temperature   | -65°C to +150°C     |

| Power Supply Voltage  | -0.3 V to +7.0 V    |

| All Input Voltages    | -0.3 V to V + 0.3 V |

| Power Dissipation     | 300 mW              |

| Anales CND Voltage    | ± 0.3 V             |

Comment: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

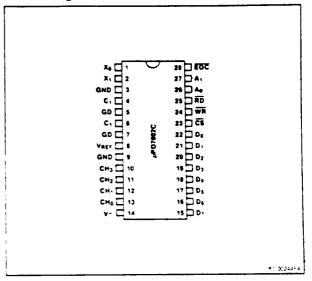

### Pin Configuration

### Pin Identification

| Pin    | Name          | Function                    |

|--------|---------------|-----------------------------|

| 1. 2   | Xo. Xi        | External clock input        |

| 3      | GND           | TTL ground                  |

| 4. 6   | CI            | Integrating capacitor       |

| 5, 7   | 60            | Guard                       |

| 8      | VREF          | Reference voltage input     |

| 9      | GND           | Analog ground               |

| 18     | CH3           | Analog channel 3            |

| 11     | CH2           | Analog channel 2            |

| 12     | CH1           | Analog channel 1            |

| 13     | CHO           | Analog channel 0            |

| 14     | V-            | Voltage (+5 V)              |

| 15-22  | D7-D0         | Data bes                    |

| 23     | <del>CS</del> | Chip select                 |

| 24. 25 | WA. AD        | Central bus                 |

| 26. 27 | Ag. A1        | Address bus                 |

| 28     | €0C           | End of conversion interrupt |

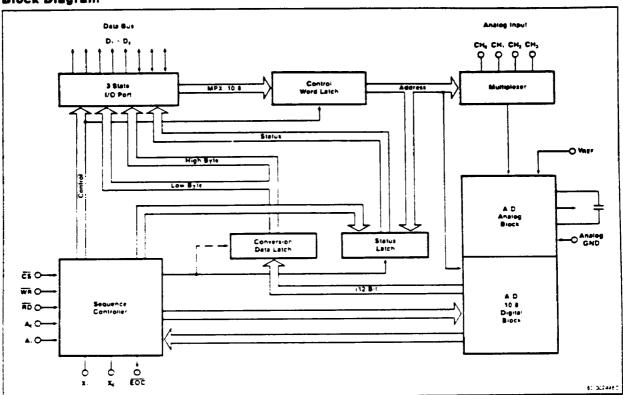

### **Block Diagram**

### Digital I/O Pin Function

| Pin    | Symbol    | Name              | 1/0                         | Function                                                                                                                                                                                                                       |

|--------|-----------|-------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. 2   | X0. X1    | Xtal              | _                           | Xtal OSC. X1 can be used as the input of external clock.                                                                                                                                                                       |

| 15-22  | 07-00     | Data Bus          | Three-state<br>(1 TTL) I/O) | A/D conversion data (High and Low Byte) and internal status output to 8-bit Data Bus. MP1 Address. B/10 salect and flag data input from bus. High impedance when $\mu$ PD7002 is not enabled ( $\overline{\text{CS}}$ = High). |

| 23     | <u>Cs</u> | Chip Select       | input                       | Low level of CS makes other input pins (WR, RD, Ag, Ag) enable and data transmission an receiving are possible through data bus pins.                                                                                          |

| 24     | WR        | Write             | Input                       | When $\overline{WR}=$ Law, $\mu PD7002$ receives new date from date bus.                                                                                                                                                       |

| 25     | ΝD        | Rest              | input                       | When $\overline{\mathrm{AD}}=\mathrm{Low}$ , $\mu\mathrm{PD7002}$ transmits conversion data and internal status to data bus.                                                                                                   |

| 26. 27 | Ap. A1    | Address           | Input                       | AO. A) designate the date in data bus (Nigh, Low, Status Byte).                                                                                                                                                                |

| 28     | EOC       | End of Conversion | Output<br>{1 TTL)           | EDC indicates the end of conversion to external chips. Read mode operation (high byte output) resetable EDC.                                                                                                                   |

### **DC Characteristics**

$T_A = 0$  °C to +50 °C; V+ = +5 V ± 0.25 V  $V_{REF} = +2.50$  V.  $I_{clk} = 1$  MHz.  $C_{INT} = 0.033 \,\mu\text{F}$ . 10-Bit Mode

|                                    |                  |             | Limits |      |        | Test                                                                                                                     |  |

|------------------------------------|------------------|-------------|--------|------|--------|--------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                          | Symbol           | Min.        | Typ.   | Max. | Unit   | Conditions                                                                                                               |  |

| Resolution, 7002C-1                |                  | 10          | 11     | 12   | Bits   |                                                                                                                          |  |

| Resolution, 7002C                  |                  | 9           | 11     | 12   | Bits   |                                                                                                                          |  |

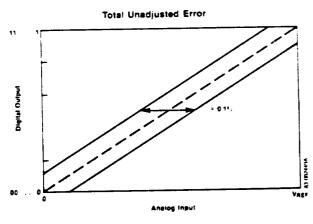

| Nonlinearity, 7002C-1              |                  |             | 0.05   | 0.1  | %FSR   |                                                                                                                          |  |

| Nonlinearity, 7002C                |                  |             | 0.1    | 0.2  | %FSR   |                                                                                                                          |  |

| Full Scale Error, 7002C-1          |                  |             | 0.05   | 0.1  | %FSR   |                                                                                                                          |  |

| Full Scale Error, 7002C            |                  |             | 0.1    | 0.2  | %FSR   |                                                                                                                          |  |

| Zero Scale Error. 7002C-1          |                  |             | 0.05   | 0.1  | %FSR   |                                                                                                                          |  |

| Zero Scale Error, 7002C            |                  |             | 0.1    | 0.2  | %FSR   |                                                                                                                          |  |

| Full Scale Temperature Coefficient |                  |             | 10     |      | ppm/°  |                                                                                                                          |  |

| Zero Scale Temperature Coefficient |                  |             | 10     |      | ppm/°C |                                                                                                                          |  |

| Analog Input Resistance            | RIN              |             | 1000   |      | MΩ     | V <sub>IN</sub> = 0 to V-                                                                                                |  |

| Total Unadjusted Error 1, 7002C-1  | TUET             |             | 0.05   | 0.1  | %FSR   |                                                                                                                          |  |

| Total Unadjusted Error 1, 7002C    | TUEI             |             | 0.1    | 0.2  | °₀FSR  |                                                                                                                          |  |

| Total Unadjusted Error 2, 7002C-1  | TUE2             |             | 0.05   | 0.1  | º.₀FSR |                                                                                                                          |  |

| Total Unadjusted Error 2, 7002C    | TUE2             |             | 0.1    | 0.2  | %FSR   |                                                                                                                          |  |

| Clock Input Current                | l <sub>cik</sub> |             | 5      | 50   | μÅ     | $X_1$ pin can be used as an external CMGS level clock input When external clock is applied. $X_0$ pin should be left spe |  |

| High Level Output Voltage          | V <sub>OH</sub>  | V 1.5       |        |      | ٧      | $t_0 = -1.6 \text{ mÅ}$ . $T_A = -20 \text{ to } -70 ^{\circ}\text{C}$                                                   |  |

| Low Level Output Voltage           | Vol              | <del></del> |        | 0.45 | V      | I <sub>O</sub> = 1.6 mA. T <sub>A</sub> = -20 to -70 °C                                                                  |  |

| Digital Input Leakage Current      | \$1LK            |             | 1      | 10   | μA     | 0 ≤ V <sub>IN</sub> ≤ V-                                                                                                 |  |

| Output Leakage Current             | louk             |             | 1      | 10   | μÅ     | 0 ≤ V <sub>IN</sub> ≤ V-                                                                                                 |  |

| Power Dissipation                  | Po               |             | 15     | 25   | mW     |                                                                                                                          |  |

### **AC Characteristics**

$T_A = +25$  °C; V+ = -5 V ± 0.25 V,  $V_{REF} = +2.5$  V,  $f_{cik} = 1$  MHz,  $C_{INT} = 0.033 \, \mu F$

|                                                      |                 |      | Limits |      |             | Test       |

|------------------------------------------------------|-----------------|------|--------|------|-------------|------------|

| Parameter                                            | Symbol          | Min. | Typ.   | Mox. | Valt        | Conditions |

| Conversion Speed (10 bit)                            | 1CONV           | 8.5  | 10     | 15   | m:          |            |

| Conversion Speed (8 bit)                             | LCONY           | 2.4  | 4      | 5    | <b>B</b> \$ |            |

| Address Setup Time CS.<br>Ap. Ajj to WR              | 1AW             | 50   |        |      | 14          |            |

| Address Setup Time CS.<br>Ag. All to RD              | <sup>1</sup> AR | 50   |        |      | 44          |            |

| Address Held Time WR to CS.<br>Ag. Ag                | twa             | 50   |        |      | 81          |            |

| Address Hold Time RD to CS.<br>Ag. Ag                | tra             | 50   |        |      | 83          |            |

| Low Level WR Pulse Width                             | tww             | 400  |        |      | ns          |            |

| Low Lovel RD Pulse Width                             | ten             | 400  |        |      | 84          |            |

| Data Setup Time Input Data to WR                     | 1DW             | 300  |        |      | RS          |            |

| Data Hold Time WR to Input Data                      | lwb             | 50   |        |      | AS          |            |

| Output Delay Time RD to Output<br>Data               | tap             |      |        | 300  | ns.         | Mote 1     |

| Delay Time to High Z Output RD to<br>Floating Output | 101             |      |        | 150  | AŞ          |            |

Note: 1 TTL load - 100 pF

# **Recommended Operating Conditions**

$T_{\Delta} = -25$ °C

|                           |                  |             | Limit | ·    |      | Test       |

|---------------------------|------------------|-------------|-------|------|------|------------|

| Parameter                 | Symbol           | Min.        | Typ.  | Max. | Unit | Conditions |

| Supply<br>Voltage         | ٧-               | 4.75        | 5.00  | 5.25 | V    |            |

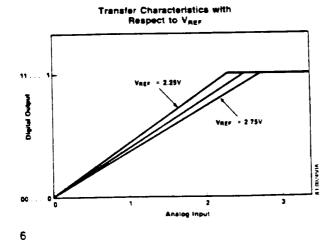

| Reference<br>Voltage      | VREF             | 2.25        | 2.50  | 2.75 | ٧    |            |

| Analog Input<br>Voltage   | Vin              | 0           |       | VREF | ٧    | Note 1     |

| Cieck<br>Fraquency        | 1 <sub>Gik</sub> | 0.5         | 1     | 3    | MHz  | Nate 2     |

| Integrating<br>Capacitor  | CINT             | 0.029       | 0.033 | 3    | μF   |            |

| High Lovel<br>Input       | VIH              | 2.2         |       |      | ٧    | Note 3     |

| Law Lavel<br>Input        | VIL              |             |       | 0.8  | ٧    | Note 3     |

| Nigh Level<br>Clack Input | AXHF             | V-<br>- 1.4 |       |      | ٧    | Note 3     |

| Low Love!<br>Clock input  | VXLL             |             |       | 1.4  | ¥    | Note 3     |

Notes: 1. Negative voltage input (< -0.2 V) decreases the input impedance. Furthermore, conversion error for the input through another MPX channel also increases.

### Notes [Cont.]:

- 2 integrating capacitor C<sub>INT</sub> depends on clock frequency and can be obtained as follows C<sub>INT</sub>(μF) = 0.033/f<sub>CIK</sub> (MHz). Note that conversion time is inversely proportional to the clock frequency.

- to the clock frequency 3  $T_A = -20$ °C to -70°C. V = -5 V  $\pm$  0.25 V

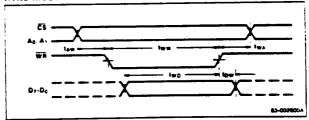

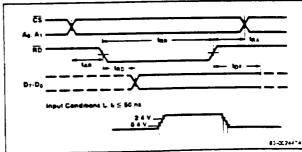

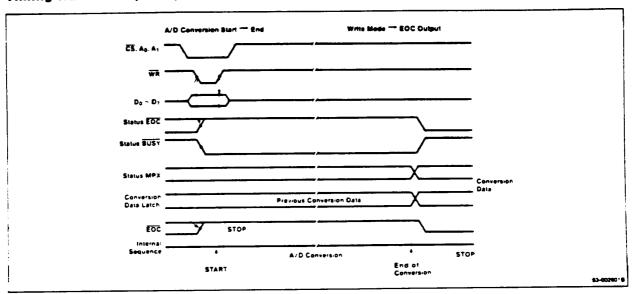

#### **Timing Waveforms**

#### Write Mode

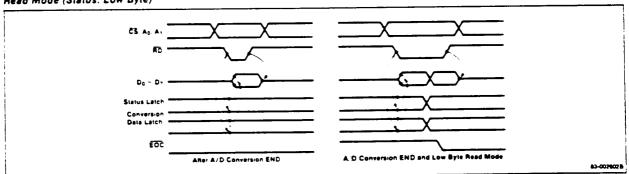

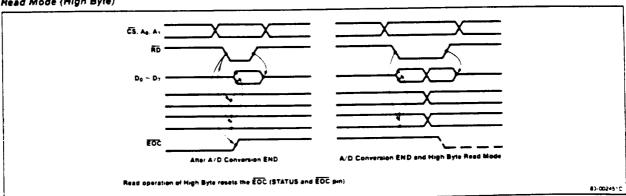

#### Read Mode

4

# Timing Waveforms (Cont.)

### Read Mode (Status, Low Byte)

### Read Mode (High Byte)

There is some uncertainty whether  $\overline{EOC}$  is set or not, when data read operation is made simultaneously with the end of A/D conversion. Furthermore, the reading error occurs at this time, so in this case a dual read operation is recommended.

# **Operating Characteristics**

### Addressing the Inputs

One of the four analog inputs is selected by initiating a write mode from the external controller with the control signals as follows:  $\overline{CS}$  (pin 23) = "low,"  $\overline{RD}$  (pin 25) = "high,"  $\overline{WR}$  (pin 24) = "low," A1 (pin 27) and A0 (pin 26) = "low."

The analog input select data is presented to D0 (pin 22) and D1 (pin 21) and the desired channel (1 to 4) is selected. The conversion resolution mode is also selected during "write" mode by presenting a "high" for 10-bit mode or "low" for 8-bit mode, to D3 at pin 19.

### Sequence

- □ Initiate "write" mode ( $\overline{CS} = 0$ ,  $\overline{RD} = 1$ ,  $\overline{WR} = 0$ , A1/A2 = 0).

- ☐ Present data for analog channel select to D0, D1.

| D0      | D1 |

|---------|----|

| CHO = L | L  |

| CH1 = H | L  |

| CH2 = L | н  |

| CH3 = H | н  |

Present conversion resolution data to D3.

During the write mode the only available function of the  $\mu$ PD7002 is data input from the controlling system. When the write function is terminated the A/D conversion process starts.

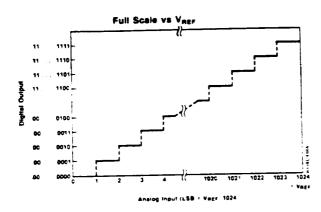

# The Conversion Process

During the "write" mode the internal sequence controller is initialized and ready to take control of the conversion process on the rising edge of the write pulse. All conversion functions take place with the  $\mu$ PD7002 in the "not selected" mode with the control signals set at:  $\overline{CS}$  = "low,"  $\overline{RD}$  and  $\overline{WR}$  "high... A0" and A1 "don't care." In the A/D section the analog signal is input via the multiplexer and compared to  $V_{REF}$  at pin 8 ( $V_{REF}$  sets the maximum full-scale input signal which can be converted). At this point the internal sample and hold for auto zero function and full scale correction are accomplished.

The processed analog signal is then passed to the analog section where the integrating capacitor is charged for a given time period controlled by the clock. In this case the period is 8192 clock periods. The capacitor is then terminated to ground and the falling slope is measured by the number of clock cycles to the zero crossing point. The number of clock cycles from peak to zero (falling slope) is proportional to the value of V<sub>IN</sub>. The integrator is then set up for the next conversion cycle.

The digital section converts the pulses from the analog section to 12-bit code and sends the converted code to the conversion data register where the data is latched and ready for "reading" by the controlling device. The data is then "read" in two bytes by addressing A0 and A1 while in the read mode. A1 = "low" A0 = "high" reads the high data byte (D0 to D7), and A1 = "high" A0 = "either" reads the low data byte (D7 to D4). During the low data byte read D0 to D3 are low and the data on D4 and D5 (bits 11 and 12) may not be accurate data.

The internal status can also be checked while in the read mode by setting A0 and A1 both "low."

#### **Operation of Individual Sections**

Sequence Controller (See Sequence Chart)

The Sequence Controller controls the internal sequence of A/D conversion and the operation of the three-state I/O buffer. It is initialized by the write mode operation (analog MPX address and 10-/8-bit choice). After the write mode operation, the Sequence Controller starts the A/D conversion, and outputs an EOC signal when the conversion is completed. There is no power-on-reset circuitry

#### A/D Conversion Block

In the A/D section, an analog signal is input through the MPX and is compared to V<sub>REF</sub>, after which it is converted to a digital output signal. Full scale analog input is equal to V<sub>REF</sub>, GND as an analog input is equal to zero scale. A/D conversion time depends on both analog input voltage and conversion mode (10/8 bit).

# Three-State I/O Port Section

The three-state I/O port section is controlled by the Sequence Controller. It accepts the MPX address input and conversion mode input (10-/8-bit choice). The three-state I/O port section outputs the internal status and conversion data high/low bytes.

#### **Conversion Data Latch**

After the end of conversion, the A/D section outputs new data to the Data Latch. The output of the Data Latch is connected to the three-state I/O ports, and the data can be read at any time. When Data Read occurs simultaneously with an internal data transfer, a read error occurs. Therefore, two read operations should be made, unless Data Read occurs after the end of conversion.

#### Status Latch

The status latch stores the status data internal to the chip, and the internal operation state can be referenced by the status data. Status includes the following:

BUSY, EOC: Internal sequence state of µPD7002. Write mode operation sets BUSY, and this is reset at the end of conversion. EOC is set at the end of conversion, and High Byte Read Operation resets EOC.

### MSB, 2nd; 10-/8-Bit Flag MPX

The data stored in the conversion Data Latch when the status reading operation is made can be output. Therefore, the data is refreshed at the end of conversion.

Access to the  $\mu$ PD7002 from the CPU can be made by both interrupt and polling methods. In the interrupt method use  $\overline{EOC}$  as an interrupt signal. In the polling method, use  $\overline{EOC}$  and  $\overline{BUSY}$  in Status Byte.

After the A/D conversion, the data in the conversion Data Latch does not change, and can be read repeatedly. Therefore, fundamental instructions like Load, Store, Move, etc. can be used to access data (by placing the address of the  $\mu$ PD7002 in memory area). Note that the access time ( $t_{RD}$ ) and the data setup time ( $t_{DW}$ ) of the  $\mu$ PD7002 are longer than that of the 8080 and 8085. The following program example shows the accessing of the  $\mu$ PD7002 by polling method in an 8080-based system.

MPX Channel Address Functions

| MPX Address |     | Analog Inp | ut Channel |     |

|-------------|-----|------------|------------|-----|

| Bit         | CHO | CHI        | CHZ        | CH3 |

| 01          | L   | l          | M          | H   |

| DO          | L   | N          | l          | Ħ   |

|       | Cont | rol T | ermin | els . |              | Internal             | Data 1/0                                                                                                                                                                              |  |  |  |  |

|-------|------|-------|-------|-------|--------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ČŠ    | RD   | WR    | Aı    | A7    | Mode         | Function             | Terminals                                                                                                                                                                             |  |  |  |  |

| H     | x    | X     | X     | X     | Not selected |                      |                                                                                                                                                                                       |  |  |  |  |

| <br>L | Ħ    | H     | x     | X     | Not selected | -                    | High impodence                                                                                                                                                                        |  |  |  |  |

| L     | H    | L     | L     | L     | Write mode   | Data latch A/D start | laput status, D1, D0 = MPX address D3 = 8-bit/10-bit conversion designation. Note 1, D7 = Flag input.                                                                                 |  |  |  |  |

| L     | H    | L     | L     | H     | Not selected | -                    |                                                                                                                                                                                       |  |  |  |  |

| Ĺ     | H    | L     | H     | Ĺ     | Not selected | _                    | Righ impedance                                                                                                                                                                        |  |  |  |  |

| L     | H    | L     | Н     | н     | Test mede    | Test status          | input status. Note 2                                                                                                                                                                  |  |  |  |  |

| L     | 1    | H     | L     | l     | Read mode    | Internal status      | $0_7 = \overline{\text{EDC}}$ , $0_6 = \text{BUSY}$ , $0_5 = \text{MSB}$ , $0_4 = 2\text{n6 MSB}$ , $0_3 = 8/10$ $0_2 = \text{Flag Output}$ , $0_1 = \text{MPX}$ , $0_0 = \text{MPX}$ |  |  |  |  |

| L     | l    | Н     | ī     | н     | Read mode    | High data byte       | D7-D0 = MSB - Bth bit                                                                                                                                                                 |  |  |  |  |

| L     | L    | Н     | H     | L     | Read mode    | Low data byte        | 07-00 = 9th - 10th bit                                                                                                                                                                |  |  |  |  |

| <br>L |      |       |       |       | Read mode    | Low data byte        | 03-00 = L                                                                                                                                                                             |  |  |  |  |

Notes: 1. Designation of number of conversion bits 8 bit =  $\pm$ : 10 bit =  $\pm$ .

2. Test Mode used for inspecting the device. The data input-output terminals assume an input state and are connected to the A/D counter. Therefore, the A/D conversion data read out after this is meaningless.

#### Ait Function

|     |        | Write Mode  |                    |               | Read Mode |               |        |

|-----|--------|-------------|--------------------|---------------|-----------|---------------|--------|

|     |        | Function    | Status Output      | High Syte     | Output    | Low Syte (    | Dutput |

| Bit | 1/0    |             |                    | 10-Bit Note 2 | 8-3it     | 10-Bit Note 2 | 8-Bit  |

| D 7 | Output | <del></del> | EOC                | MSB           | MSB       | 9th           | Note 3 |

| 06  | Dutput |             | Busy               | 2nd           | 2nd       | LSB           | Note 3 |

| 05  | Output |             | MSB Note 1         | 3rd           | 3rt       | <b>Q</b> 11   | Hote 3 |

| D4  | Output |             | 2nd Bit Note 1     | 4th           | 4th       | 012           | Note 3 |

| D3  | 1/0    | 10/8-Bit    | 10/8-Bit Note 1    | 5th           | 5th       | Low           | Lew    |

| D2  | 1/0    | Flag input  | Flag Output Note 1 | 6th           | 6th       | Lew           | Lew    |

| 01  | 1/0    | MPX Address | MPX Note 1         | 7th           | 7th       | Low           | Low    |

| DO  | 1/0    | MPX Address | MPX Note 1         | Bth           | 8th       | Low           | Low    |

Notes: 1 Previous conversion data

Previous conversion data

In 10-bit mode, the μPD7002 operates as a 12-bit converter. Therefore, 11th and 12th bit data appear at Q<sub>11</sub> and Q<sub>12</sub>, and the output of Q<sub>11</sub> and Q<sub>12</sub> varies with analog input, however, the data contain internal noise and are meaningless.

3. Not to be determined

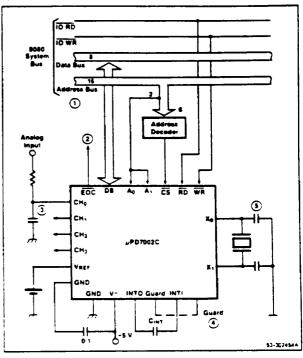

### Typical Applications

- The high level input voltage of the µPD7002C is 2.2 V.

In a minimum component system configuration, tying 50 kΩ resistors to DB<sub>0</sub>-DB<sub>7</sub>, A<sub>0</sub>, A<sub>1</sub>, CS, RD, and WR is recommended. The fan-out of DB<sub>0</sub>-DB<sub>7</sub> is 1 TTL level. In larger systems, use bus drivers as shown here.

- 2. Use EOC as an interrupt signal if you have an interrupt-driven system.

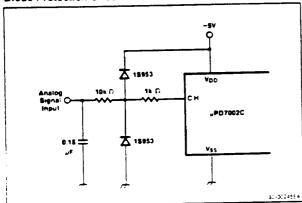

- Use a 100 Hz low pass filter to decrease the conversion error. Using the diode protection circuit shown here is effective protection against high voltage surges.

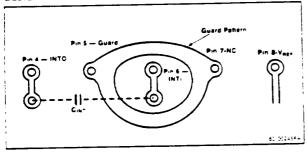

- 4. The μPD7002 uses the integration technique for A/D conversion, and it operates at a very low current level. The external integrating capacitor (C<sub>INT</sub>) is directly connected to the internal integrator. Using the guard pattern as shown below makes the operation less sensitive to leakage current.

- Capacitors are tied to the X and X<sub>0</sub> pins to stabilize the oscillation, use a ceramic capacitor about 50 pF. About 50 ms is required for stable oscillation after initial power-on. Therefore, the first Write Mode Operation should occur after this interval.

### Typical Microprocessor Interface

### Use of Bus Drivers

# Typical Applications (Cont.)

#### **Diode Protection Circult**

#### **Guard Pattern**

#### **Noise Reduction**

The  $\mu$ PD7002 is an integrating A/D converter; however, it operates at a relatively high speed and the normal mode noise rejection cannot be expected. Observance of the following points will minimize noise induction to the input of the analog circuit.

- ☐ Use lower impedance in GND connection

- Place the bypass capacitors for supply voltage and V<sub>REF</sub> and analog input close to the μPD7002 (one point GND is also effective)

- ☐ Isolate analog circuitry from digital circuitry:

- Component layout

- GND wire layout

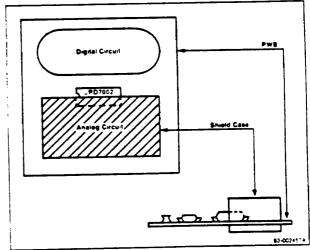

- Shielding of analog circuitry (pin configuration of the μPD7002 is suitable for the layout shown in the next figure)

# Shield for Analog Circuitry