#### ADVANCED PRODUCT INFORMATION

T-51-09-07

## **ZN454E**

#### TRIPLE 4-BIT VIDEO D-A CONVERTER

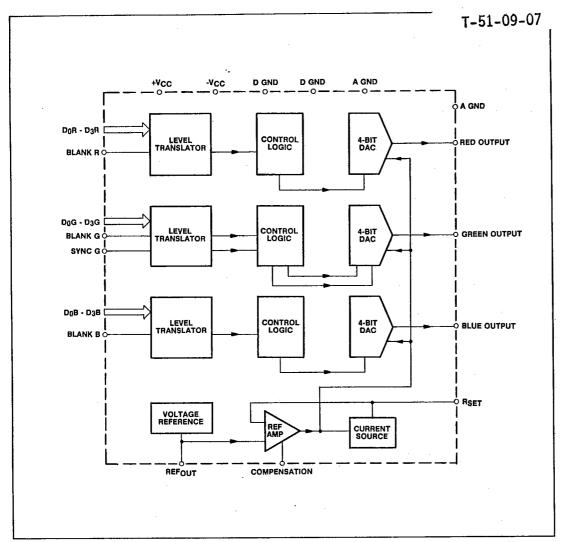

The ZN454 consists of three 4-bit D-A converters, providing a colour palette of 4096 possible display colours. The required logic translators, control logic, a reference voltage source and reference amplifier are also integrated on-chip.

Each D-A converter accepts 4-bit digital video data and SYNC/BLANK signals directly from a TTL source and produces a composite video output to directly drive a  $75\Omega$  line terminated by a  $75\Omega$  load at both ends.

The ZN454 is ideally suited for pixel colour generation in graphics display systems requiring 4-bit colour resolution. The high linearity of each DAC ensures excellent colour contrast and the fast update rate allows the device to be interfaced to monitors with a resolution of up to 1024 x 1280 pixels assuming a standard refresh rate of 60Hz.

#### **FEATURES**

- 3 Video DAC's Ideal for Colour Graphics

- Fast, 8ns Settling Time

- Update Rates to 100MHz

- Low Glitch Energy

- ¼ LSB Linearity Error

- On-Chip Reference Source

- Composite Sync and Blank Inputs

- TTL Compatible Inputs

- Generates Standard Video Signal Output Across a Doubly Terminated 75 Ohm Load

- 28 Pin DIL Package

#### **GENERAL CIRCUIT DESCRIPTION**

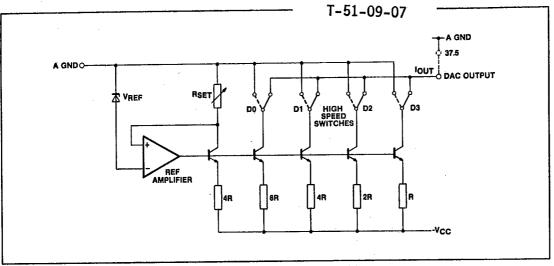

Each D-A converter of the ZN454 uses high speed switches to steer current from precision current sources to either analog ground or to the analog output – as governed by the digital inputs (see Fig.4). The analog output voltage is now obtained from these weighted current sources producing the desired voltage drop across the 37.5 $\Omega$  load impedance. The gain of the D-A converters is adjustable via RSET.

Since the ZN454 utilises current output DAC's the output impedance is inherently high. Thus a 75 $\Omega$  resistance is required (adjacent to each DAC output) to shunt this high impedance and provide the correct impedance for driving a 75 $\Omega$  line terminated in 75 $\Omega$  at the monitor. The desired 1V p-p composite signal will now be developed across this effective 37.5 $\Omega$  output impedance.

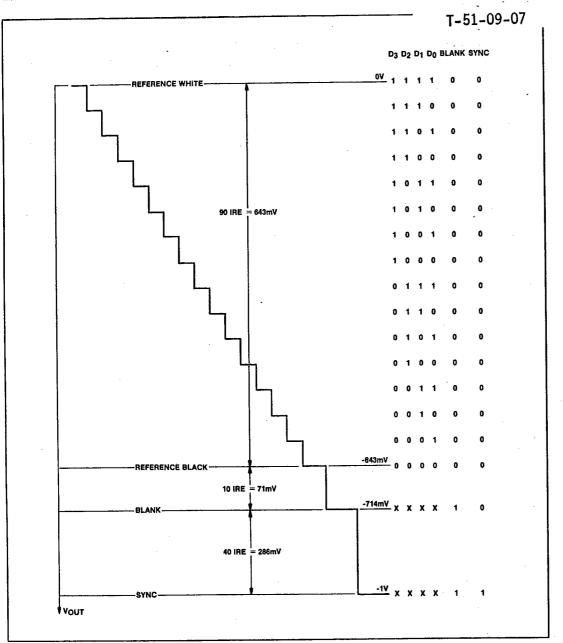

The grey scale output current of each DAC has 16 levels from 0 to -17mA nominally (see Fig.3). This develops 16

Fig.1 Pin connections - top view

levels of output voltage from 0 to -643mV across the specified 37.5 $\Omega$  load impedance, the 'REFERENCE WHITE' level (0V) corresponds to the digital input code 1111 and the 'REFERENCE BLACK' (-643mV) to 0000. A logic '1' on the BLANK input overrides the data inputs

A logic '1' on the BLANK input overrides the data inputs and drives the output to 71mV more negative than the 'REFERENCE BLACK' level. This corresponds to the 'BLANKING' (or 'blacker-than-black') level.

Activating the SYNC input (logic '1') with the BLANK input 'high' drives the output to 286mV more negative than the 'BLANKING' level. This voltage (nominally -1V) corresponds to the 'SYNC' level.

#### GAIN ADJUSTMENT (RSET)

RSET provides a means of adjusting the current in the weighted current sources. An amplifier compares the voltage developed across RSET, with the reference voltage. If RSET is increased/decreased the amplifier output causes the current through RSET to decrease/increase (to bring the voltage across RSET back in line with the reference voltage). This also causes the current in each of the current sources to decrease/increase (see Fig.3). In this manner the magnitude of the output waveform can be varied to obtain the desired levels.

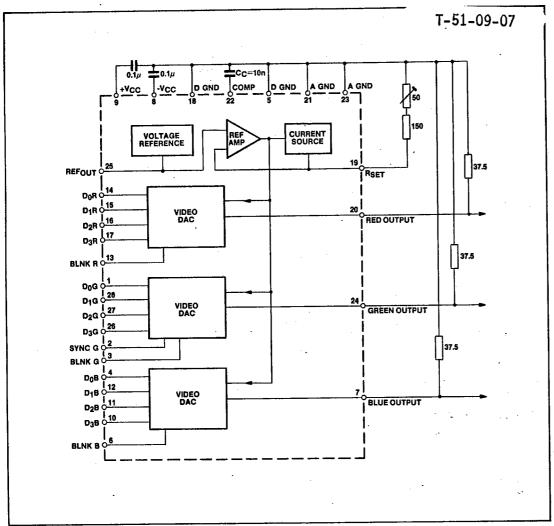

Fig.2 Block diagram

### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, +Vcc        | +6\             |

|-----------------------------|-----------------|

| Supply voltage, -Vcc        | -6\             |

| Logic input voltage         | +Vc             |

| Operating temperature range | 0°C to 70°C     |

| Storage temperature range   | -55°C to +125°C |

**ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):  $T_{amb} = 25$  °C, Vcc =  $\pm 5$ V, Rt =  $37.5\Omega$  and Rser =  $180\Omega$

T-51-09-07

| · Characteristic                            | Currh -1     | Value                |             |             | 11-11-   | 0                     |

|---------------------------------------------|--------------|----------------------|-------------|-------------|----------|-----------------------|

|                                             | Symbol       | Min.                 | Тур.        | Max.        | Units    | Conditions            |

| Resolution                                  |              | 4                    |             |             | Bits     |                       |

| LSB weight (current)                        |              | 1                    | 1.13        |             | mA       |                       |

| LSB weight (voltage)                        |              |                      | 43          |             | m∨       | Note 1                |

| Accuracy                                    |              |                      | ļ           |             |          |                       |

| Linearity error                             | İ            |                      | ±0.25       | ±0.5        | LSB      |                       |

| Differential linearity error                |              |                      |             | ±0.5        | LBS      | Note 2                |

| Offset error                                | ł            |                      | -5.0        | -15.0       | mV       |                       |

| Gain error                                  | 1            |                      |             | ±5          | % of     |                       |

|                                             |              |                      |             |             | nom.FSR  |                       |

| Speed performance - Grey scale output       |              |                      | 3           | ĺ           |          | 10-90% of final value |

| Rise/fall times (voltage)                   |              | l                    | 8           |             | ns<br>ns | Note 3                |

| Settling time (voltage) Maximum update rate |              |                      | 100         | i           | MHz      | Note 4                |

| Slew rate                                   |              | ļ                    | 180         |             | V/μs     | 10-90% of final value |

| Glitch energy                               |              |                      | 60          | 1           | pV-s     | Note 5                |

| Temperature coefficient                     |              |                      |             |             | F        |                       |

| Offset                                      |              | 1                    | 10          |             | ppm/°C   | Measured with         |

| Gain                                        | 1            |                      | 500         |             | ppm/°C   | internal reference    |

| Data, sync and blank inputs                 |              |                      |             |             |          |                       |

| Logic compatibility                         |              | TTL                  |             |             |          |                       |

| High level input voltage                    | VIH          | 2.0                  |             |             | 1 v 1    |                       |

| Low level input voltage                     | VIL          |                      |             | 0.8         | v        |                       |

| High level input current                    | [IH(1)       |                      |             | +20         | μΑ       | Vcc = max, Vin = 5.5V |

|                                             | f (H(2)      | 1                    | 1           | ±10         | μΑ       | Vcc = max, Vin = 2.4V |

| Low level input current                     | f IL         | L                    |             | -1.6        | mA       | Vcc = max, Vin = 0.4V |

| Coding (see Fig.2)                          |              | Complementary binary |             |             |          |                       |

| Output - Grey scale                         |              |                      |             |             |          |                       |

| Voltage range                               |              |                      | 0.64        | l           | V        | Note 1                |

| Current range                               | ł            | l                    | 17          | ĺ           | mA       | I More I              |

| Output - Composite sync                     |              |                      | İ           |             |          |                       |

| Voltage range                               |              |                      | 286         |             | mV       |                       |

| Current range                               |              |                      | 7.6         | 1           | mA       |                       |

| Output - Composite blanking                 |              |                      | İ           |             |          |                       |

| Voltage range                               |              | 1                    | 71          |             | mV       |                       |

| Current range                               |              |                      | 1.9         |             | mA       |                       |

| Output voltage compliance                   |              | 0                    |             | 1.5         | \ \      |                       |

| Internal voltage reference                  | 1            |                      | 1           |             |          |                       |

| Output voltage                              | VREF         |                      | -1.26       |             | V        | ·                     |

| Output voltage tolerance                    |              |                      | 000         | ±5.0        | %        | 000 to 7000           |

| Output voltage TC                           |              | 1                    | 200         |             | ppm/°C   | 0°C to 70°C           |

| Power supply requirements                   | ±V05         | 1 45                 | -           |             |          |                       |

| Supply voltage                              | +Vcc<br>-Vcc | 4.5<br>-4.5          | 5.0<br>-5.0 | 5.5<br>-5.5 | V        |                       |

| Supply current                              | +1cc         | -4.5                 | 22.5        | -5.5        | mA       | · ·                   |

|                                             | -lcc         |                      | 136.0       | 1           | mA       |                       |

NOTES

1. LSB and full-scale output levels adjustable with Rser.

2. Monotonicity guaranteed over full operating temperature range.

3. The settling time was measured as the time between the start of the output rising/falling edge to where the output entered and remained within ±1/2 LSB of the final value. The value quoted is for a transition from reference white to reference black and vice versa, and does not include the inherent input propagation delay (2-3ns). See section describing settling time measurement.

4. The maximum update rate is limited by the full-scale settling time to rated accuracy.

5. Measurement of glitch energy is discussed in a later section of this data sheet.

Fig.3 Typical composite video output waveform

Fig.4 Current source array (schematic)

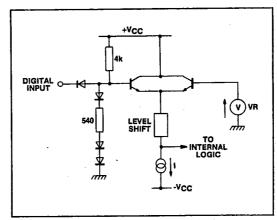

#### **DIGITAL INPUTS**

The digital inputs are high speed level translators (see

Fig.5).

The ZN454 requires very few external components for normal operation. Fig.6 illustrates the external component connections.

#### LAYOUT CONSIDERATIONS

When using the ZN454, as with any other device of this kind, certain precautions must be taken to obtain the best performance.

Some of the requirements are:

- A ground plane board providing a good earth and with good power supply connections, to keep noise to a minimum.

- 2. Good decoupling especially around all the fast switching circuits including a 0.1µF capacitor from both the +5V and -5V supplies positioned close to the ZN454. The ground connections for these capacitors should be adjacent.

- 3. Some physical separation between the digital input tracks to minimise crosstalk.

- 4. Matched digital input signal paths to avoid introducing any unnecessary time skew between the inputs. This would cause glitches on the DAC outputs with changing codes. Also the outputs from the driving device will have to be well matched for the same reason.

- 5.  $75\Omega$  resistors close to the DAC outputs, to provide the correct impedance for driving  $75\Omega$  lines.

# SETTLING TIME AND GLITCH ENERGY MEASUREMENT

In a finished design the ZN454 would be soldered directly into the board to obtain the best performance possible. However for evaluation purposes a socket really needs to be used. This will give some degradation in performance but useful results can still be obtained.

Fig.5 Equivalent circuit of sync, blank and data inputs

Measurement of settling time and glitch energy is not a straightforward task and all of the recommendations previously noted must be adhered to. If these parameters are to be measured using an oscilloscope, great care must be taken to avoid corrupting the analog outputs e.g. conventional probes cannot simply be clipped onto the outputs as this would cause reflections giving rise to errors. Instead the ZN454 needs a 75 $\Omega$  termination near the chip, a 75 $\Omega$  cable - also grounded close to the chip - connecting to a 75 $\Omega$  lead through termination at the oscilloscope. Optimum cable length is about 6 inches but it may need trimming around this. Also the oscilloscope obviously needs to have sufficient bandwidth to cope with the rise and fall times encountered.

The digital circuits driving the DAC's must not introduce too much noise, or time skew between the bit inputs. This

Fig.6 External component connections

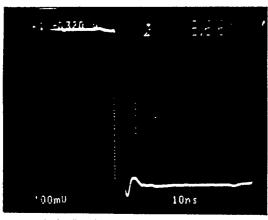

can considerably affect the results. However, a convenient way of minimising these problems for evaluation purposes, is to drive the digital inputs directly from a pulse generator. Full-scale transitions of the grey scale can now be monitored by wiring the inputs to a given DAC in parallel (terminating in 500) and clocking with the pulse generator.  $50\Omega$ ) and clocking with the pulse generator. Each output can now be examined in turn. The circuit diagram is as in Fig.6 except that the sync and blank inputs will be tied low. The 37.50 terminations on the DAC output, and the digital input signals are provided as described above. Fig.7 shows an actual trill-scale (gray social critical transitions). actual full-scale (grey scale) output transition measured using the above procedure, giving a settling time of 5.12ns.

Glitch energy measurements, at the major transition for example, can also be processed by divine the

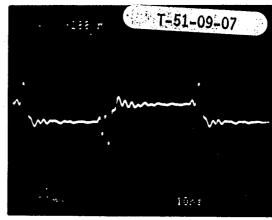

example, can also be measured by driving the digital inputs directly from a pulse generator but it will need to have well matched complementary outputs. Also the lead lengths from the generator to the digital inputs will have to be well matched (and terminated in  $50\Omega).$  This is so because this measurement is especially critical of any time skew between the input signals. Indeed even an ideal DAC would produce glitches if there were timing differences between these changing input signals. These time skew errors which would manifest themselves as exaggerated glitches on the DAC output, are referred to the point at which the input signals cross the digital input thresholds (=1.5V nom.). Thus the characteristics of the driving signals will have some effect on the amplitude of the glitches, which may be minimised by careful design. The circuit arrangement for measuring the glitch energy is as above but with the digital inputs being switched through different codes. Fig.8 shows an actual midscale glitch, measured using the above procedure.

Fig.7 Full-scale output transition - settling time

Fig.8 Mid-scale output glitch

#### **GLOSSARY OF VIDEO TERMS**

#### Raster scan

The method of sweeping a CRT one line at a time to generate and display images.

#### Composite video signal

The VIDEO signal plus the BLANK and SYNC signals.

#### Video signal

The portion of the composite VIDEO SIGNAL which varies in grey scale levels between 'reference white' and 'reference black' - this is the portion which is visually observed.

#### Sync signal

The portion of the video waveform that synchronises the raster scanning process.

#### Grey scale

The discrete levels between and including 'reference white' and 'reference black' - there are 16 levels for a 4-bit DAC.

#### Blanking level

The level separating the SYNC portion from the VIDEO portion. Usually referred to as the FRONT PORCH or BACK PORCH, this is the level which will shut off the electron guns resulting in the blackest possible display.

#### Sync level

The negative peak level of the sync signal.

#### Reference black level

The maximum negative level of the VIDEO signal.

#### Reference white level

The maximum positive level of the VIDEO signal.