(RAM-Provided 165-Channel LCD Driver for Liquid Crystal Dot Matrix Graphics)

# **HITACHI**

## **Description**

The HD66108T under control of an 8-bit MPU can drive a dot matrix graphic LCD (liquid-crystal display) employing bit-mapped display with support of an 8-bit MPU.

Use of the HD66108T enables a simple LCD system to be configured with only a small number of chips, since it has all the functions required for driving the display.

The HD66108T also enables highly-flexible display selection due to the bit-mapped method, in which one bit of data in a display RAM turns one dot of an LCD panel on or off. A single HD66108T can display a maximum of  $100 \times 65$  dots by using its on-chip  $165 \times 65$ -bit RAM. Also, by using several HD66108T's, a display can be further expanded.

The HD66108T employs the CMOS process and TCP package. Thus, if used together with an MPU, it can provide the means for a battery-driven pocket-size graphic display device utilizing the low current consumption of LCDs.

#### **Features**

• Four types of LCD driving circuit configurations can be selected:

| Configuration Type                        | No. of Column Outputs | No. of Row Outputs                 |

|-------------------------------------------|-----------------------|------------------------------------|

| Column outputs only                       | 165                   | 0                                  |

| Row outputs from the left and right sides | 100                   | 65 (from left: 32, from right: 33) |

| Row outputs from the right side 1         | 100                   | 65                                 |

| Row outputs from the right side 2         | 132                   | 33                                 |

- Seven types of multiplexing duty ratios can be selected: 1/32, 1/34, 1/36, 1/48, 1/50, 1/64, 1/66 Notes: The maximum number of row outputs is 65.

- Built-in bit-mapped display RAM: 10 kbits ( $165 \times 65$  bits)

- The word length of display data can be selected according to the character font: 8-bit or 6-bit

- A standby operation is available

- The display can be extended through a multi-chip operation

- A built-in CR oscillator

- An 80-system CPU interface:  $\phi = 4$  MHz

- Power supply voltage for operation: 2.7V to 6.0V

- LCD driving voltage: 6.0V to 15.0V

- Low current consumption: 400 μA max (at fOSC = 500 kHz, fOSC is external clock frequency)

- Package: 208-pin TCP (Tape-Carrier-Package)

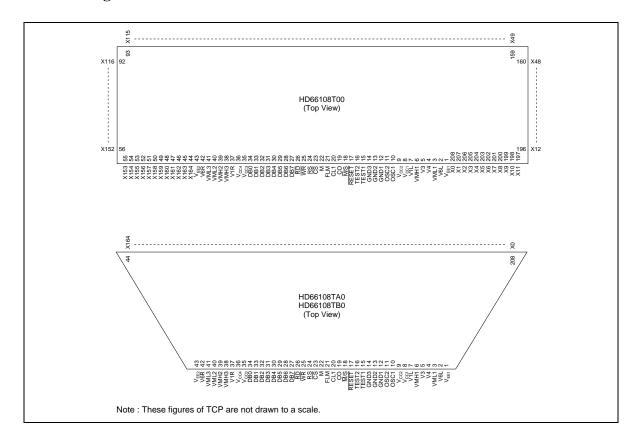

## **Ordering Information**

| Type No.   | Package     |                             |

|------------|-------------|-----------------------------|

| HD66108T00 | 208 pin TCP | (Quad)                      |

| HD66108TA0 |             | (Double side)               |

| HD66108TB0 |             | (Double side & folding TCP) |

| HCD66108BP |             | (Chip with bump)            |

Note: The details of TCP pattern are shown in "The Information of TCP."

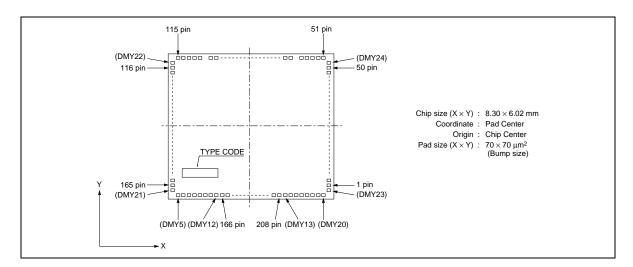

## **HD66108 Pad Arrangement**

# **HD66108 Pad Location Coordinates**

| Pin | Pad     | Coo          | rdinate | Pin | Pad     | Coo          | rdinate      | Pin | Pad  | Coor  | Coordinate   |     | Pad     | Coordinate   |              |

|-----|---------|--------------|---------|-----|---------|--------------|--------------|-----|------|-------|--------------|-----|---------|--------------|--------------|

| No. | Name    | X            | Υ       | No. | Name    | X            | Υ            | No. | Name | Х     | Υ            | No. | Name    | Х            | Υ            |

|     | (DMY23) | 4040         | -2550   | 34  | X33     | 4040         | 850          | 67  | Y66  | 1600  | 2900         | 101 | X100    | -1800        | 2900         |

| 1   | X0      | $\downarrow$ | -2450   | 35  | X34     | $\downarrow$ | 950          | 68  | X67  | 1500  | $\downarrow$ | 102 | X101    | -1900        | $\downarrow$ |

| 2   | X1      | $\downarrow$ | -2350   | 36  | X35     | $\downarrow$ | 1050         | 69  | X68  | 1400  | $\downarrow$ | 103 | X102    | -2000        | $\downarrow$ |

| 3   | X2      | $\downarrow$ | -2250   | 37  | X36     | $\downarrow$ | 1150         | 70  | X69  | 1300  | $\downarrow$ | 104 | X103    | -2100        | $\downarrow$ |

| 4   | Х3      | $\downarrow$ | -2150   | 38  | X37     | $\downarrow$ | 1250         | 71  | X70  | 1200  | $\downarrow$ | 105 | X104    | -2200        | $\downarrow$ |

| 5   | X4      | $\downarrow$ | -2050   | 39  | X38     | $\downarrow$ | 1350         | 72  | X71  | 1100  | $\downarrow$ | 106 | X105    | -2300        | $\downarrow$ |

| 6   | X5      | $\downarrow$ | -1950   | 40  | X39     | $\downarrow$ | 1450         | 73  | X72  | 1000  | $\downarrow$ | 107 | X106    | -2400        | $\downarrow$ |

| 7   | X6      | $\downarrow$ | -1850   | 41  | X40     | $\downarrow$ | 1550         | 74  | X73  | 900   | $\downarrow$ | 108 | X107    | -2500        | $\downarrow$ |

| 8   | X7      | $\downarrow$ | -1750   | 42  | X41     | $\downarrow$ | 1650         | 75  | X74  | 800   | $\downarrow$ | 109 | X108    | -2600        | $\downarrow$ |

| 9   | X8      | $\downarrow$ | -1650   | 43  | X42     | $\downarrow$ | 1750         | 76  | X75  | 700   | $\downarrow$ | 110 | X109    | -2700        | $\downarrow$ |

| 10  | X9      | $\downarrow$ | -1550   | 44  | X43     | $\downarrow$ | 1850         | 77  | X76  | 600   | $\downarrow$ | 111 | X110    | -3300        | $\downarrow$ |

| 11  | X10     | $\downarrow$ | -1450   | 45  | X44     | $\downarrow$ | 1950         | 78  | X77  | 500   | $\downarrow$ | 112 | X111    | -3400        | $\downarrow$ |

| 12  | X11     | $\downarrow$ | -1350   | 46  | X45     | $\downarrow$ | 2050         | 79  | X78  | 400   | $\downarrow$ | 113 | X112    | -3500        | $\downarrow$ |

| 13  | X12     | $\downarrow$ | -1250   | 47  | X46     | $\downarrow$ | 2150         | 80  | X79  | 300   | $\downarrow$ | 114 | X113    | -3600        | $\downarrow$ |

| 14  | X13     | $\downarrow$ | -1150   | 48  | X47     | $\downarrow$ | 2250         | 81  | X80  | 200   | $\downarrow$ | 115 | X114    | -3700        | 2900         |

| 15  | X14     | $\downarrow$ | -1050   | 49  | X48     | $\downarrow$ | 2350         | 82  | X81  | 100   | $\downarrow$ |     | (DMY24) | -4040        | 2550         |

| 16  | X15     | $\downarrow$ | -950    | 50  | X49     | $\downarrow$ | 2450         | 83  | X82  | 0     | $\downarrow$ | 116 | X115    | $\downarrow$ | 2450         |

| 17  | X16     | $\downarrow$ | -850    |     | (DMY24) | 4040         | 2550         | 84  | X83  | -100  | $\downarrow$ | 117 | X116    | $\downarrow$ | 2350         |

| 18  | X17     | $\downarrow$ | -750    | 51  | X50     | 3700         | 2900         | 85  | X84  | -200  | $\downarrow$ | 118 | X117    | $\downarrow$ | 2250         |

| 19  | X18     | $\downarrow$ | -650    | 52  | X51     | 3600         | $\downarrow$ | 86  | X85  | -300  | $\downarrow$ | 119 | X118    | $\downarrow$ | 2150         |

| 20  | X19     | $\downarrow$ | -550    | 53  | X52     | 3500         | $\downarrow$ | 87  | X86  | -400  | $\downarrow$ | 120 | X119    | $\downarrow$ | 2050         |

| 21  | X20     | $\downarrow$ | -450    | 54  | X53     | 3400         | $\downarrow$ | 88  | X87  | -500  | $\downarrow$ | 121 | X120    | $\downarrow$ | 1950         |

| 22  | X21     | $\downarrow$ | -350    | 55  | X54     | 3300         | $\downarrow$ | 89  | X88  | -600  | $\downarrow$ | 122 | X121    | $\downarrow$ | 1850         |

| 23  | X22     | $\downarrow$ | -250    | 56  | X55     | 2700         | $\downarrow$ | 90  | X89  | -700  | $\downarrow$ | 123 | X122    | $\downarrow$ | 1750         |

| 24  | X23     | $\downarrow$ | -150    | 57  | X56     | 2600         | $\downarrow$ | 91  | X90  | -800  | $\downarrow$ | 124 | X123    | $\downarrow$ | 1650         |

| 25  | X24     | $\downarrow$ | -50     | 58  | X57     | 2500         | $\downarrow$ | 92  | X91  | -900  | $\downarrow$ | 125 | X124    | $\downarrow$ | 1550         |

| 26  | X25     | $\downarrow$ | 50      | 59  | X58     | 2400         | $\downarrow$ | 93  | X92  | -1000 | $\downarrow$ | 126 | X125    | $\downarrow$ | 1450         |

| 27  | X26     | $\downarrow$ | 150     | 60  | X59     | 2300         | $\downarrow$ | 94  | X93  | -1100 | $\downarrow$ | 127 | X126    | $\downarrow$ | 1350         |

| 28  | X27     | $\downarrow$ | 250     | 61  | X60     | 2200         | $\downarrow$ | 95  | X94  | -1200 | $\downarrow$ | 128 | X127    | $\downarrow$ | 1250         |

| 29  | X28     | $\downarrow$ | 350     | 62  | X61     | 2100         | $\downarrow$ | 96  | X95  | -1300 | $\downarrow$ | 129 | X128    | $\downarrow$ | 1150         |

| 30  | X29     | $\downarrow$ | 450     | 63  | X62     | 2000         | $\downarrow$ | 97  | X96  | -1400 | $\downarrow$ | 130 | X129    | $\downarrow$ | 1050         |

| 31  | X30     | $\downarrow$ | 550     | 64  | X63     | 1900         | $\downarrow$ | 98  | X97  | -1500 | $\downarrow$ | 131 | X130    | $\downarrow$ | 950          |

| 32  | X31     | $\downarrow$ | 650     | 65  | X64     | 1800         | $\downarrow$ | 99  | X98  | -1600 | $\downarrow$ | 132 | X131    | $\downarrow$ | 850          |

| 33  | X32     | 4040         | 750     | 66  | X65     | 1700         | 2900         | 100 | X99  | -1700 | 2900         | 133 | X132    | $\downarrow$ | 750          |

Note: The pin marked by \* must be hold  $V_{cc}$ .

| Pin  | Pad      | Cod          | ordinate | _ Pin   | Pad                      | Cod   | ordinate     | _ Pin | Pad              | C    | oordinate    |

|------|----------|--------------|----------|---------|--------------------------|-------|--------------|-------|------------------|------|--------------|

| No.  | Name     | Х            | Υ        | No.     | Name                     | х     | Υ            | No.   | Name             | Х    | Υ            |

| 134  | X133     | -4040        | 650      | *       | (DMY6)                   | -3650 | -2900        | 192   | RESET            | 1030 | -2850        |

| 135  | X134     | $\downarrow$ | 550      | *       | (DMY7)                   | -3550 | $\downarrow$ | 193   | TEST2            | 1160 | $\downarrow$ |

| 136  | X135     | $\downarrow$ | 450      | *       | (DMY8)                   | -3450 | $\downarrow$ | 194   | TEST1            | 1290 | $\downarrow$ |

| 137  | X136     | $\downarrow$ | 350      | *       | (DMY9)                   | -3350 | $\downarrow$ | 195   | BND3             | 1400 | $\downarrow$ |

| 138  | X137     | $\downarrow$ | 250      | *       | (DMY10)                  | -3250 | $\downarrow$ | 196   | GND2             | 1500 | $\downarrow$ |

| 139  | X138     | $\downarrow$ | 150      | *       | (DMY11)                  | -3150 | $\downarrow$ | 197   | GND1             | 1600 | $\downarrow$ |

| 140  | X139     | $\downarrow$ | 50       | *       | (DMY12)                  | -3050 | -2900        |       | (GNDA)           | 1700 | $\downarrow$ |

| 141  | X140     | $\downarrow$ | -50      | 166     | $V_{\text{EE2}}$         | -2920 | -2872        | 198   | OSC2             | 1815 | $\downarrow$ |

| 142  | X141     | $\downarrow$ | -150     | 167     | VGR                      | -2820 | $\downarrow$ | 199   | OSC1             | 1995 | $\downarrow$ |

| 143  | X142     | $\downarrow$ | -250     | 168     | VML3                     | -2720 | $\downarrow$ | 200   | V <sub>CC2</sub> | 2105 | -2850        |

| 144  | X143     | $\downarrow$ | -350     | 169     | VML2                     | -2620 | $\downarrow$ | 201   | V <sub>cc1</sub> | 2205 | -2882        |

| 145  | X144     | $\downarrow$ | -450     | 170     | VMH2                     | -2520 | $\downarrow$ | 202   | VIL              | 2320 | $\downarrow$ |

| 146  | X145     | $\downarrow$ | -550     | 171     | VMH3                     | -2420 | $\downarrow$ | 203   | VMH1             | 2420 | $\downarrow$ |

| 147  | X146     | $\downarrow$ | -650     | 172     | VIR                      | -2320 | $\downarrow$ | 204   | V3               | 2520 | $\downarrow$ |

| 148  | X147     | $\downarrow$ | -750     | 173     | V <sub>CC4</sub>         | -2210 | -2872        | 205   | V4               | 2620 | $\downarrow$ |

| 149  | X148     | $\downarrow$ | -850     | 174     | V <sub>CC3</sub>         | -2110 | -2850        | 206   | VML1             | 2720 | $\downarrow$ |

| 150  | X149     | $\downarrow$ | -950     |         | (V <sub>CCA</sub> )      | -2010 | $\downarrow$ | 207   | V6L              | 2820 | $\downarrow$ |

| 151  | X150     | $\downarrow$ | -1050    | 175     | DB0                      | -1860 | $\downarrow$ | 208   | V <sub>EE1</sub> | 2920 | -2882        |

| 152  | X151     | $\downarrow$ | -1150    | 176     | DB1                      | -1660 | $\downarrow$ | *     | (DMY13)          | 3050 | -2900        |

| 153  | X152     | $\downarrow$ | -1250    | 177     | DB2                      | -1460 | $\downarrow$ | *     | (DMY14)          | 3150 | $\downarrow$ |

| 154  | X153     | $\downarrow$ | -1350    | 178     | DB3                      | -1260 | $\downarrow$ | *     | (DMY15)          | 3250 | $\downarrow$ |

| 155  | X154     | $\downarrow$ | -1450    | 179     | DB4                      | -1060 | $\downarrow$ | *     | (DMY16)          | 3350 | $\downarrow$ |

| 156  | X155     | $\downarrow$ | -1550    | 180     | DB5                      | -860  | $\downarrow$ | *     | (DMY17)          | 3450 | $\downarrow$ |

| 157  | X156     | $\downarrow$ | -1650    | 181     | DB6                      | -660  | <b>\</b>     | *     | (DMY18)          | 3550 | $\downarrow$ |

| 158  | X157     | $\downarrow$ | -1750    | 182     | DB7                      | -460  | $\downarrow$ | *     | (DMY19)          | 3650 | $\downarrow$ |

| 159  | X158     | $\downarrow$ | -1850    | 183     | RD                       | -285  | $\downarrow$ | *     | (DMY20)          | 3750 | -2900        |

| 160  | X159     | $\downarrow$ | -1950    | 184     | WR                       | -155  | $\downarrow$ |       |                  |      | (Unit : µm   |

| 161  | X160     | $\downarrow$ | -2050    | 185     | RS                       | -25   | -            | _     |                  |      |              |

| 162  | X161     | $\downarrow$ | -2150    | 186     | CS                       | 105   | $\downarrow$ | _     |                  |      |              |

| 163  | X162     | $\downarrow$ | -2250    | 187     | М                        | 250   | $\downarrow$ | _     |                  |      |              |

| 164  | X163     | $\downarrow$ | -2350    | 188     | FLM                      | 440   | $\downarrow$ | _     |                  |      |              |

| 165  | X164     | $\downarrow$ | -2450    | 189     | CL1                      | 580   | $\downarrow$ | _     |                  |      |              |

| -    | (DMY21)  | -4040        | -2550    | 190     | СО                       | 755   | $\downarrow$ | _     |                  |      |              |

| *    | (DMY5)   | -3750        | -2900    | 191     | MS                       | 900   | -2850        | _     |                  |      |              |

| Note | : The pi | n mark       | ked by * | must be | e hold V <sub>cc</sub> . |       |              | _     |                  |      |              |

## **Pin Arrangement**

# **Pin Description**

| Classification     | No. of Pins                                      | Symbol                                                       | I/O | No.of Pins | Function                                                                                                                                                                                        |

|--------------------|--------------------------------------------------|--------------------------------------------------------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power              | 8, 9, 35, 36                                     | V <sub>CC1</sub> -V <sub>CC4</sub>                           | _   | 4          | Connect these pins to V <sub>cc</sub> .                                                                                                                                                         |

| supply             | 12 to 14                                         | GND1-GND3                                                    | _   | 3          | Ground these pins.                                                                                                                                                                              |

|                    | 1, 43                                            | $V_{\text{EE1}}, V_{\text{EE2}}$                             |     | 2          | These pins supply power to the LCD driving circuits and should usually be set to the V6 level.                                                                                                  |

|                    | 2, 7<br>37, 42<br>4, 5<br>6, 39, 38<br>3, 40, 41 | V6L, V1L,<br>V1R, V6R,<br>V4, V3,<br>VMH1–VMH3,<br>VML1–VML3 | _   | 12         | Apply an LCD driving voltage V1 to V6 to these pins.                                                                                                                                            |

| CPU interface      | 23                                               | CS                                                           | I   | 1          | Input a chip select signal via this pin. A CPU can access the HD66108T's internal registers only while the $\overline{\text{CS}}$ signal is low.                                                |

|                    | 25                                               | WR                                                           | I   | 1          | Input a write enable signal via this pin.                                                                                                                                                       |

|                    | 26                                               | RD                                                           | I   | 1          | Input a read enable signal via this pin.                                                                                                                                                        |

|                    | 24                                               | RS                                                           | I   | 1          | Input a register select signal via this pin.                                                                                                                                                    |

|                    | 27 to 34                                         | DB7-DB0                                                      | I/O | 8          | Data is transferred between the HD66108T and a CPU via these pins.                                                                                                                              |

| LCD driving output | 44 to 208                                        | X164-X0                                                      | 0   | 165        | These pins output LCD driving signals. The X0–X31 and X100–X164 pins are column/row common pins and output row driving signals when so programmed. X32–X99 pins are column pins.                |

| LCD interface      | 21                                               | FLM                                                          | I/O | 1          | This pin outputs a first line marker when the HD66108T is a master chip and inputs the signal when the chip is a slave chip.                                                                    |

|                    | 20                                               | CL1                                                          | I/O | 1          | This pin outputs latch clock pulses of display data when the chip is a master chip and inputs clock CL1 pulses when the chip is a slave chip.                                                   |

|                    | 22                                               | М                                                            | I/O | 1          | This pin outputs or inputs an M signal, which converts LCD driving outputs to AC; it outputs the signal when the HD66108T is a master chip and inputs the signal when the chip is a slave chip. |

| Classification | No.of<br>Pins | Symbol          | I/O | No.of<br>Pins                                                          | Function                                                                                                                                                             |

|----------------|---------------|-----------------|-----|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control        | 10            | OSC1            | I   | 1                                                                      | Input system clock pulses via this pin.                                                                                                                              |

| signals        | 11            | OSC2            | 0   | This pin outputs clock pulses generated by the internal CR oscillator. |                                                                                                                                                                      |

|                | 19            | СО              | 0   | 1                                                                      | This pin outputs the same clock pulses as the system clock pulses. Connect with the OSC1 pin of a slave chip.                                                        |

|                | 18            | M/S             | I   | 1                                                                      | This pin specifies master/slave. Set this pin low when the HD66108T is a master chip and set high when the chip is a slave chip; must not be changed after power-on. |

|                | 17            | 17 RESET I 1    |     | 1                                                                      | Input a reset signal via this pin. Setting this pin low initializes the HD66108T.                                                                                    |

|                | 15, 16        | TEST1,<br>TEST2 | I   | 2                                                                      | These pins input a test signal and must be set low.                                                                                                                  |

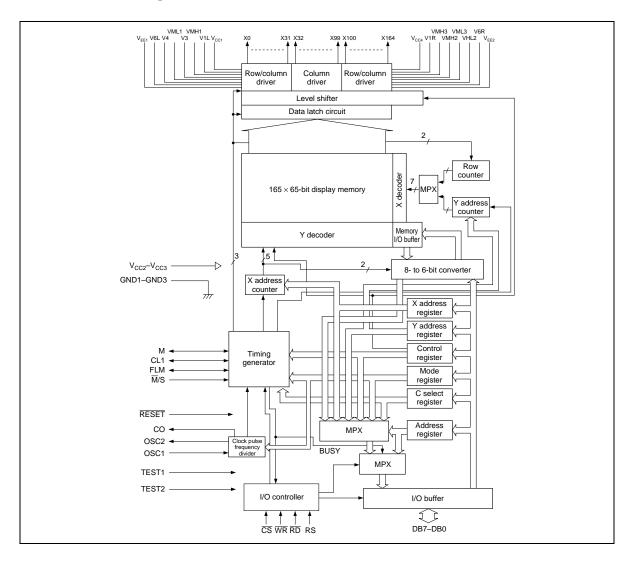

## **Internal Block Diagram**

## **Register List**

|    |    | Re | eg. | No. | Reg.   | Register | Register Read/Data Bit Assignment |      |      |      |    |     |     |         |     |                |       |

|----|----|----|-----|-----|--------|----------|-----------------------------------|------|------|------|----|-----|-----|---------|-----|----------------|-------|

| CS | RS |    |     |     | Symbol | _        | Write                             |      | 6    | 5    | 4  | 3   | 2   | 1       | 0   | Busy Time      | Notes |

| 1  | _  | -  | _   | _   | _      | Invalid  | _                                 |      |      |      |    |     |     |         |     | -              | 1     |

| 0  | 0  |    |     | _   | AR     | Address  | R                                 | Busy | STBY | DISP |    |     | R   | egister | No. | None           | _     |

|    |    |    |     |     |        |          | W                                 |      |      |      |    |     |     |         |     |                |       |

| 0  | 1  | 0  | 0   | 0   | DRAM   | Display  | R                                 | D7   | D6   | D5   | D4 | D3  | D2  | D1      | D0  | 8 clocks max   | 2     |

|    |    |    |     |     |        | memory   | W                                 |      |      |      |    |     |     |         |     |                | 3     |

| 0  | 1  | 0  | 0   | 1   | XAR    | Х        | R                                 |      |      |      |    |     | XAD |         |     | None           | _     |

|    |    |    |     |     |        | address  | W                                 |      |      |      |    |     |     |         |     | 1.5 clocks max |       |

| 0  | 1  | 0  | 1   | 0   | YAR    | Υ        | R                                 |      |      |      |    | YAD |     |         |     | None           |       |

|    |    |    |     |     |        | address  | W                                 |      |      |      |    |     |     |         |     | 1.5 clocks max |       |

| 0  | 1  | 0  | 1   | 1   | FCR    | Control  | R                                 | INC  | WLS  | PON  | ı  | ROS |     | DUT     | 1   | None           |       |

|    |    |    |     |     |        |          | W                                 |      |      |      |    |     |     |         |     |                |       |

| 0  | 1  | 1  | 0   | 0   | MDR    | Mode     | R                                 |      |      |      |    | FFS |     | D       | WS  | None           |       |

|    |    |    |     |     |        |          | W                                 |      |      |      |    |     |     |         |     |                |       |

| 0  | 1  | 1  | 0   | 1   | CSR    | C select | R                                 |      |      | EOR  |    |     | CLN |         |     | None           |       |

|    |    |    |     |     |        |          | W                                 |      |      |      |    |     |     |         |     |                |       |

| 0  | 1  | 1  | 1   | 0   | _      | Invalid  | _                                 |      |      |      |    |     |     |         |     | -              |       |

| 0  | 1  | 1  | 1   | 1   | _      | Invalid  | _                                 |      |      |      |    |     |     |         |     | -              |       |

Notes: 1. Shaded bits are invalid. Writing 1 or 0 to invalid bits does not affect LSI operation. Reading these bits returns 0.

- 2. DRAM is not actually a register but can be handled as one.

- 3. Setting the WLS bit of control register to 1 invalidates D7 and D6 bits of the display memory register.

- 4. DRAM must not be written to or read from until a time period of t<sub>CL1</sub> has elapsed rewriting the DUTY bit of FCR or the FFS bit of MDR. t<sub>CL1</sub> can be obtained from the following equation; in general, a time period of 1 ms or greater is sufficient if the frame frequency is 60–90 Hz.

$$t_{CL1} = \frac{D2}{\text{Ni-f}_{CLK}(\text{kHz})} \text{(ms)} \dots$$

Equation

D2 (duty correction value): 192 (duty = 1/32, 1/34, or 1/36)

128 (duty = 1/48 or 1/50)

96 (duty = 1/64 or 1/66)

Ni (frequency-division ratio specified by the mode register's FFS bits):

2, 1, 1/2, 1/3, 1/4, 1/6, or 1/8

Refer to "6. Clock and Frame Frequency."

f<sub>CLK</sub>: Input clock frequency (kHz)

## **System Description**

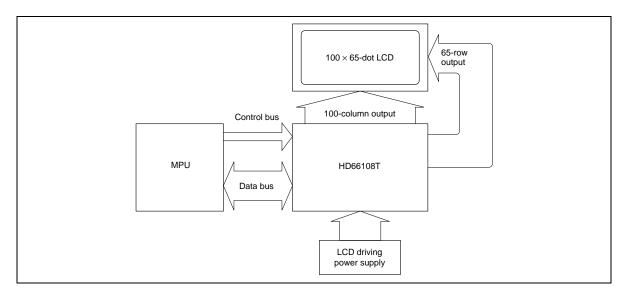

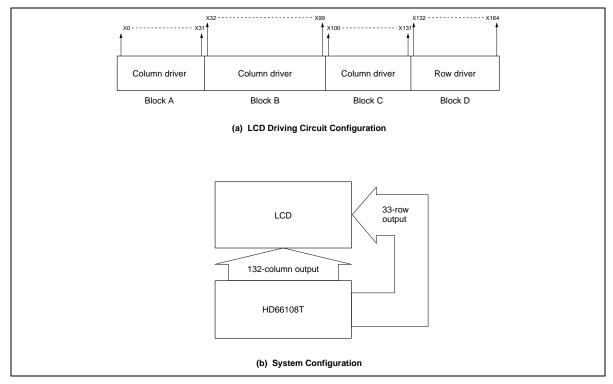

The HD66108T can assign a maximum of 65 out of 165 channels to row outputs for LCD driving. It also incorporates a timing generator and display memory, which are necessary to drive an LCD.

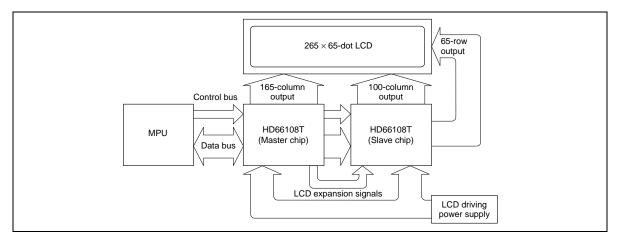

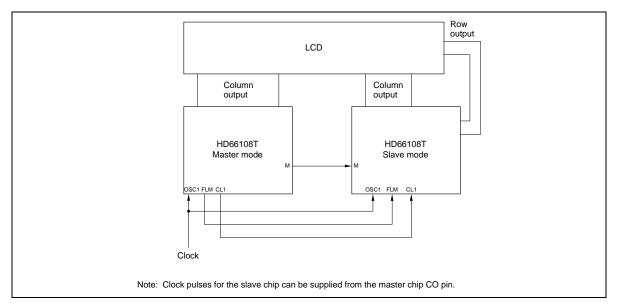

If connected to an MPU and supplied with LCD driving voltage, one HD66108T chip can be used to configure an LCD system with a  $100 \times 65$  dot panel (Figure 1). In this case, clock pulses should be supplied by the internal CR oscillator or the MPU.

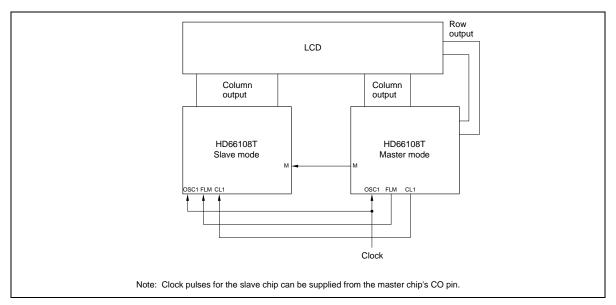

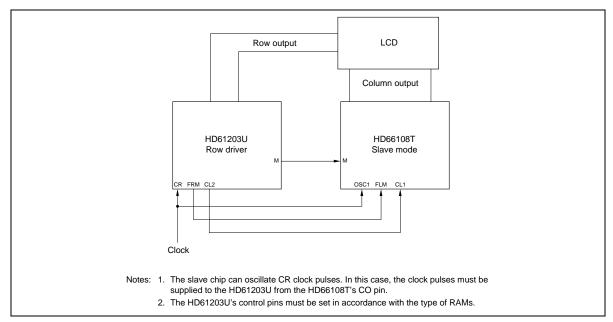

Using LCD expansion signals CL1, FLM and M enables the display size to be expanded. In this case, LCD expansion signal pins output corresponding signals when pin  $\overline{M}/S$  is set low for master mode and conversely input corresponding signals when pin  $\overline{M}/S$  is set high for slave mode; LCD expansion signal pins of both master chip and slave chips must be mutually connected. Figure 2 shows a basic system configuration using two HD66108T chips.

Figure 1 Basic System Configuration (1)

Figure 2 Basic System Configuration (2)

## **Functional Description**

#### 1. Display Size Programming

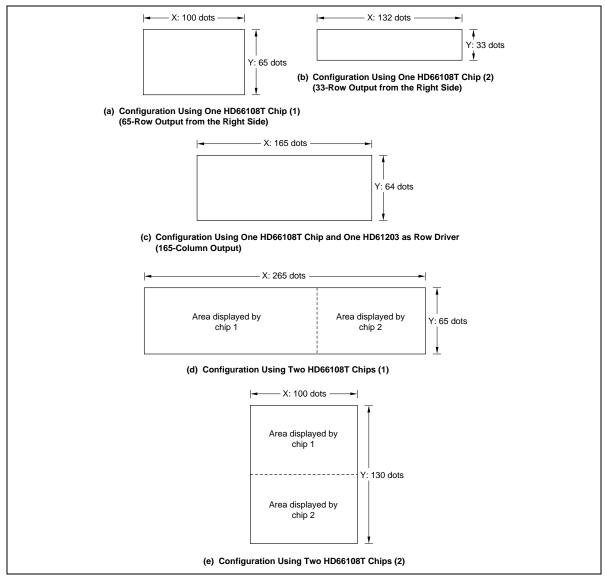

A variety of display sizes can be programmed by changing the system configuration and internal register settings.

#### (1) System Configuration Using One HD66108T Chip

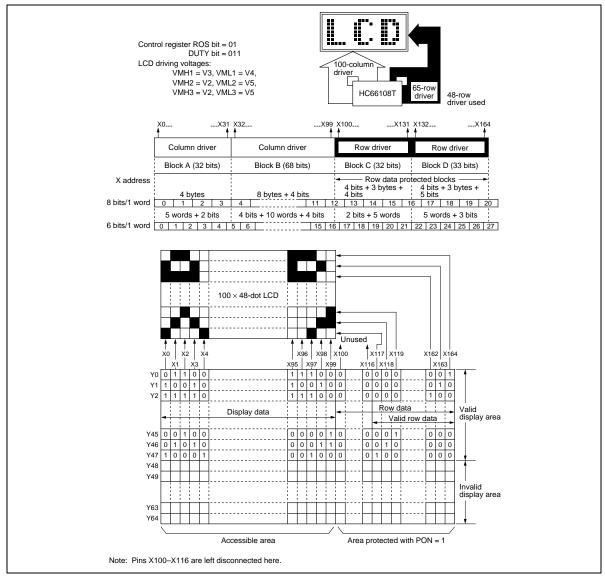

When the 65-row-output mode is selected by internal register settings, a maximum of 100 dots in the X direction can be displayed (Figure 3 (a)). Display size in the Y direction can be selected from 32, 34, 36, 48, 50, 64, and 65 dots according to display duty setting. Note that Y direction settings does not affect those in the X direction (100 dots).

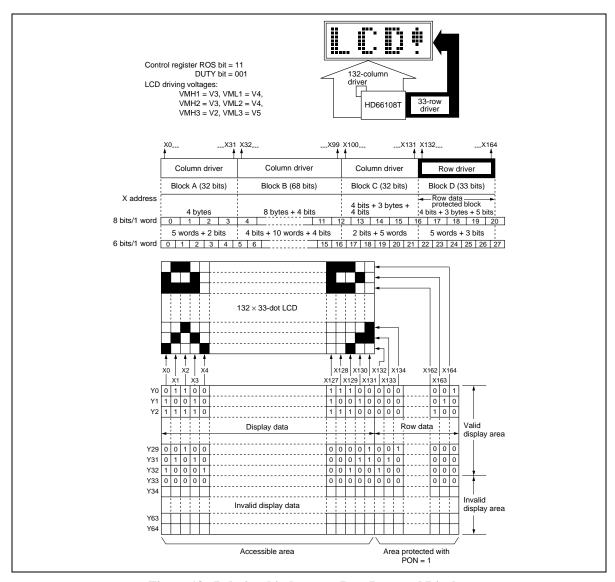

When the 33-row-output mode is selected by internal register settings, a maximum of 132 dots in the X direction can be displayed (Figure 3 (b)).

Table 1 shows the relationship between display sizes and the control register's (FCR) ROS and DUTY bits. ROS and DUTY bit settings determine the function of X pins. For more details, refer to "4.1 Row Output Pin Selection."

#### (2) System Configuration Using One HD66108T Chip and One HD61203 Chip as Row Driver

A maximum of 64 dots in the Y direction and 165 dots in the X direction can be displayed. 48 or 64 dots in the Y direction can be selected by HD61203 pin settings (Figure 3 (c)).

#### (3) System Configuration Using Two or more HD66108T Chips

X direction size can be expanded by 165 dots per chip. Figure 3 (d) shows a  $265 \times 65$ -dot display. Y direction size can be expanded up to 130 dots with 2 chips; a  $100 \times 130$ -dot display provided by 2 chips is shown in Figure 3 (e).

Table 1 Relationship between Display Size and Register Settings (No. of Dots)

| ROS Bit Setting                             | Duty Bit Setting (Multiplexing Duty Ratio) |            |        |        |        |        |        |  |  |  |  |

|---------------------------------------------|--------------------------------------------|------------|--------|--------|--------|--------|--------|--|--|--|--|

| (X0-X164 Pin Function)                      | 1/32                                       | 1/34       | 1/36   | 1/48   | 1/50   | 1/64   | 1/66   |  |  |  |  |

| 165-column-output                           | Specifie                                   | d by a row | driver |        |        |        |        |  |  |  |  |

| 65-row-output from the right side           | X: 100                                     | X: 100     | X:100  | X: 100 | X: 100 | X: 100 | X:100  |  |  |  |  |

|                                             | Y: 32                                      | Y: 34      | Y: 36  | Y: 48  | Y: 50  | Y: 64  | Y: 65  |  |  |  |  |

| 65-row-output from the left and right sides | X: 100                                     | X: 100     | X:100  | X: 100 | X: 100 | X: 100 | X:100  |  |  |  |  |

|                                             | Y: 32                                      | Y: 34      | Y: 36  | Y: 48  | Y: 50  | Y: 64  | Y: 65  |  |  |  |  |

| 33-row-output from the right side           | X: 132                                     | X: 132     | X: 132 | X: 132 | X: 132 | X: 132 | X: 132 |  |  |  |  |

|                                             | Y: 32                                      | Y: 33      | Y: 33  | Y: 33  | Y: 33  | Y: 33  | Y: 33  |  |  |  |  |

Figure 3 Relationship between System Configurations and Display Sizes

#### 2. Display Memory Construction and Word Length Setting

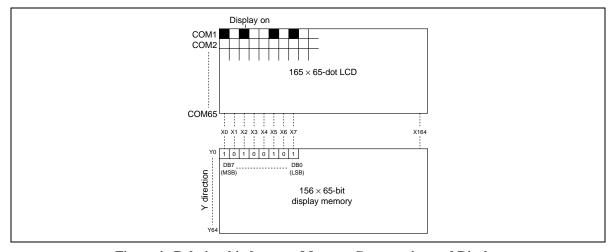

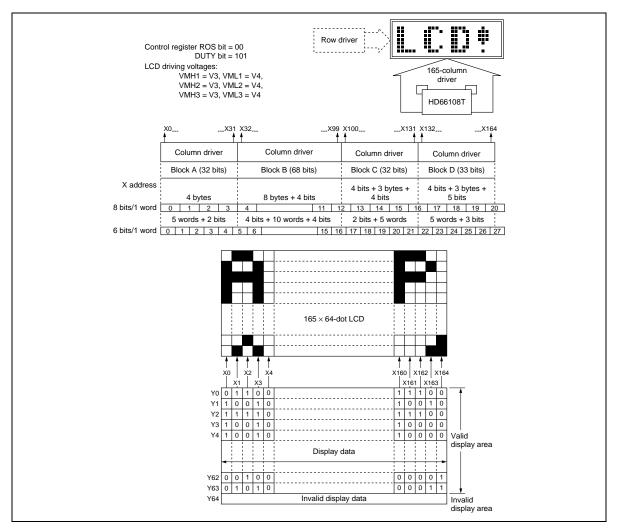

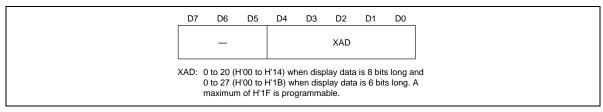

The HD66108T has a bit-mapped display memory of  $165 \times 65$  bits. As shown in Figure 4, data from the MPU is stored in the display memory, with the MSB (most significant bit) on the left and the LSB (least significant bit) on the right.

The sections on the LCD panel corresponding to the display memory bits in which 1's are written will be displayed as on (black).

Display area size of the internal RAM is determined by control register (FCR) settings (refer to Table 1).

The start address in the Y direction for the display area is always Y0, independent of the register setting. In contrast, the start address in the X direction is X0 in the modes for 165-column-output, 65-row-output from the right side, and 33-row-output from the right side, and is X32 in the 65-row-output mode from the left and right sides.

Each display area contains the number of dots shown in Table 1, beginning from each start address.

For more detail, refer to "4.2 Row Output Data Setting," Figures 15 to 19.

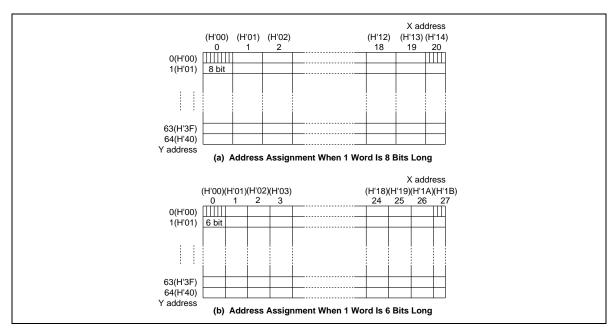

In the display memory, one X address is assigned to each word of 8 or 6 bits long in X direction. (Either 8 or 6 bits can be selected as word length of display data.) Similarly, one Y address is assigned to each row in Y direction.

Accordingly, X address 20 in the case of 8-bit word and X address 27 in the case of 6-bit word have 5 and 3 bits of display data, respectively. Nevertheless, data is also stored here with the MSB on the left (Figure 5).

Figure 4 Relationship between Memory Construction and Display

Figure 5 Display Memory Addresses

## 3. Display Data Write

#### 3.1 Display Memory and Data Register Accesses

## (1) Access

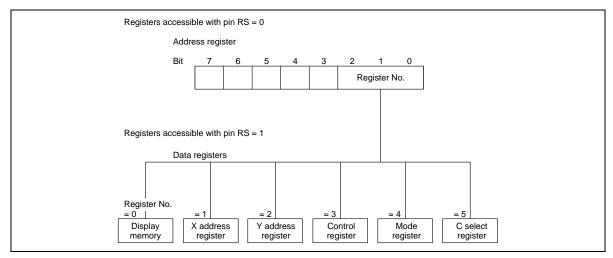

Figure 6 shows the relationship between the address register (AR) and internal registers and display memory in the HD66108T. Display memory shall be referred to as a data register since it can be handled as other registers.

To access a data register, the register address assigned to the desired register must be written into the address register's Register No. bits. The MPU will access only that register until the register address is updated.

Figure 6 Relationship between Address Register and Register No.

## (2) Busy Check

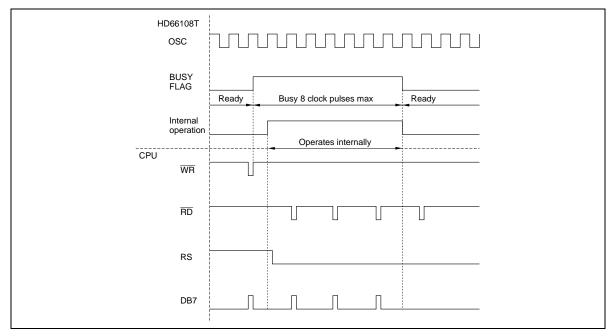

A busy time period appears after display memory read/write or X or Y address register write, since post-access processing is performed synchronously with internal clock pulses. Updating data in registers other than the address register is disabled during this time. Subsequent data must be input after confirming ready mode by reading the address register. The busy time period is a maximum of 8 clock pulses after display memory read/write and a maximum of 1.5 clock pulses after X or Y address register write (Figure 7).

Figure 7 Relationship between Clock Pulses and Busy Time (Updating Display Data)

## (3) Dummy Read

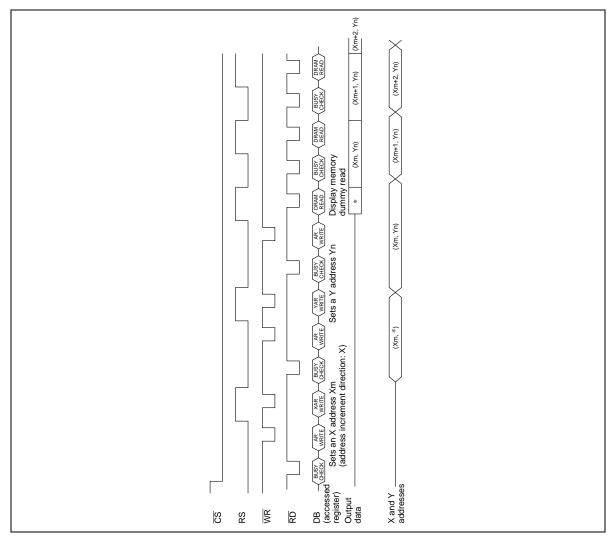

When reading out display data, the data which is read out immediately after setting the X and Y addresses is invalid. Valid data can be read out after one dummy read, which is performed after setting the X and Y addresses desired (Figure 8).

Figure 8 Display Memory Reading

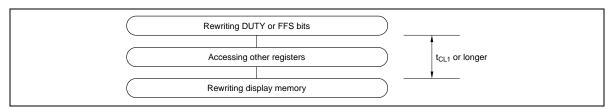

#### (4) Limitations on Access

As shown in Figure 9, the display memory must not be rewritten until a time period of  $t_{CLI}$  or longer has elapsed after rewriting the control register's DUTY bits or the mode register's FFS bits. However, display memory and registers other than the control register and mode register can be accessed even during this time period.  $t_{CLI}$  can be obtained from the following equation. If using an LSI with a frame frequency of 60 Hz or greater, a time period of 1 ms should be sufficient.

$$t_{CL1} = \frac{D2}{Ni \cdot f_{CLK}(kHz)}$$

(ms) ...... Equation 1

D2 (duty correction value):

192 (duty = 1/32, 1/34, or 1/36)

128 (duty = 1/48 or 1/50)

96 (duty = 1/64 or 1/66)

Ni (frequency-division ratio specified by the mode register's FFS bits):

2, 1, 1/2, 1/3, 1/4, 1/6, or 1/8

## 3.2 X and Y address Counter Auto-Incrementing Function

f<sub>cl k</sub>: Input clock frequency (kHz)

As described in "2. Display Memory Construction and Word Length Setting," the HD66108T display memory has X and Y addresses. Internal X address counter and Y address counter both employ an auto-incrementing function. After display data is read or written, the X or Y address is incremented according to the address increment direction selected by internal register.

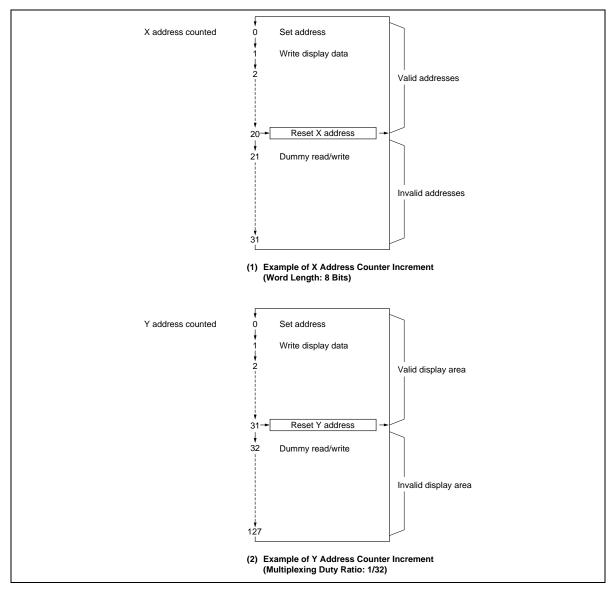

Although X addresses up to 20 are valid when 8 bits make up one word (up to 27 when 6 bits make up one word), the X address counter can count up to 31 since it is a 5-bit free counter. Similarly, although Y addresses up to 64 are valid, the Y address counter can count up to 127. Consequently, X or Y address must be reset at an appropriate point as shown in Figure 10.

Figure 9 Rewriting Display Memory after Rewriting Registers

Figure 10 X/Y Address Counter Increment

#### 4. Selection for LCD Driving Circuit Configuration

#### 4.1 Row Output Pin Selection

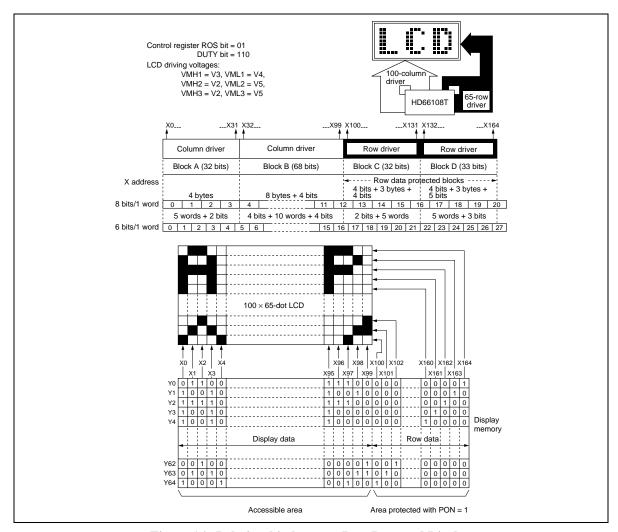

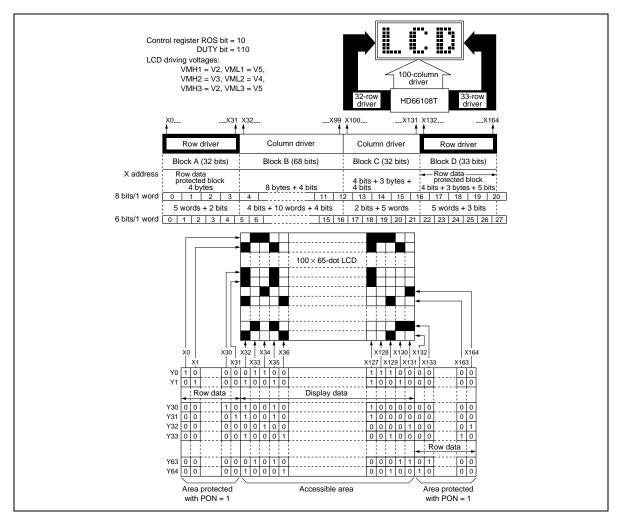

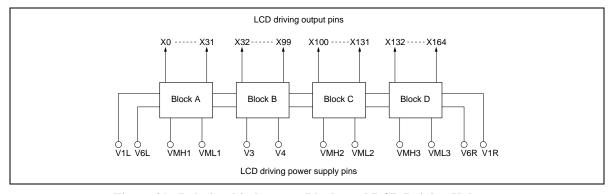

The HD66108T can assign a maximum of 65 pins for row outputs among the 165 pins named X0–X164. The X0–X164 pins can be classified into four blocks labelled A, B, C, and D (Figure 11 (a)). Blocks A, C, and D consist of row/column common pins and block B consists of column pins only. The output function of the LCD driving pins and the combination of blocks can be selected by internal registers.

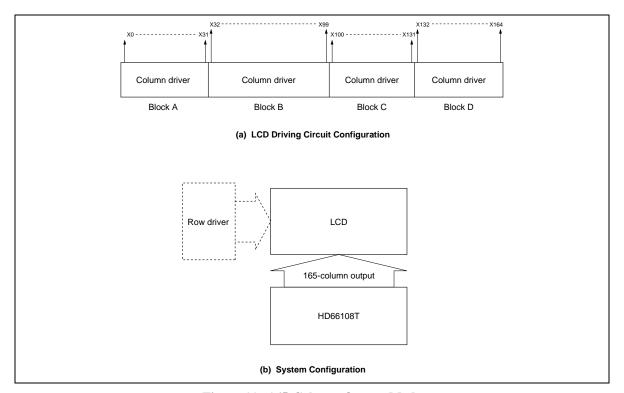

Figure 11 shows an example of 165-column-output mode. This configuration is useful when using more than one HD66108T chip or using the HD66108T as a slave chip of the HD61203U.

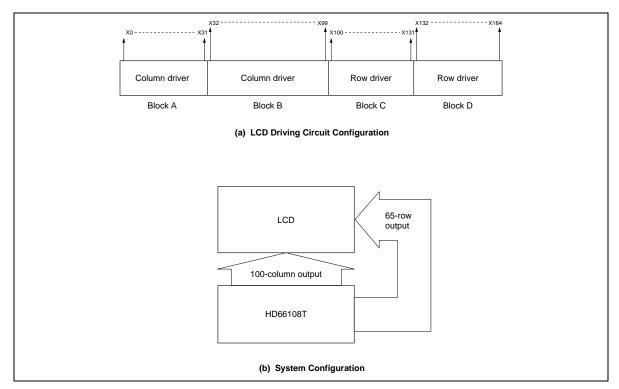

Figure 12 shows an example of 65-row-output mode from the right side. Blocks A and B are used for column output and blocks C and D (X100–X164 pins) for row output. This configuration offers an easy way of connecting row output lines in the case of using one or more HD66108T chips.

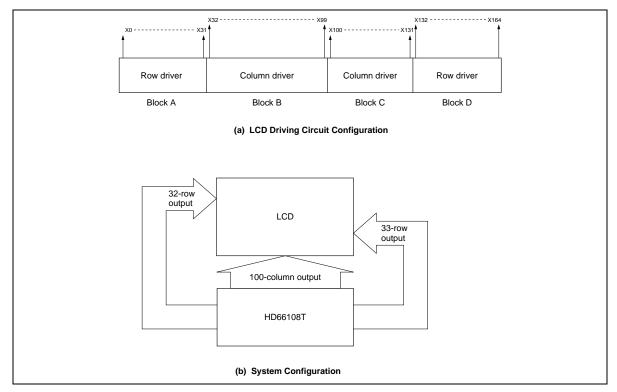

Figure 13 shows an example of 65-row-output mode from the left and right sides. 32 pins of X0–X31 and 33 pins of X132–X164 are used for row output here. This configuration offers an easy way of connecting row output lines in the case of using only one HD66108T chip.

Figure 14 shows an example of 33-row-output mode from the right side. Block D, i.e., X132–X164 pins, is used for row outputs. This configuration provides a means for assigning many pins to column outputs when 1/32 or 1/34 multiplexing duty ratio is desired.

In all modes, it is row data and multiplexing duty ratio that determine which pins are actually used among the pins assigned to row output. Y values shown in Table 1 indicate the numbers of pins that are actually used. Pins not used must be left disconnected.

Figure 11 165-Column-Output Mode

Figure 12 65-Row-Output Mode from the Right Side

Figure 13 65-Row-Output Mode from the Left and Right Sides

Figure 14 33-Row-Output-Mode from the Right Side

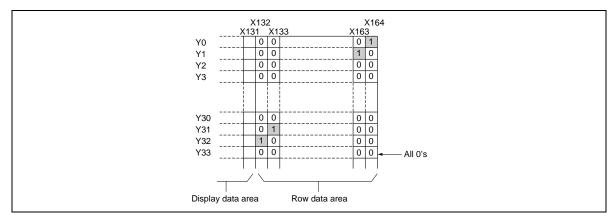

#### 4.2 Row Output Data Setting

If certain LCD driving output pins are assigned to row output, data must be written to display memory for row output. The specific area to which this data must be written depends on the row-output mode and the procedure of writing row data to the display memory (0 or 1 to which bits?) depends on which X pin drives which line of the LCD. Row data area is determined by the control register's (FCR) ROS and DUTY bits and is identical to the protected area, which will be described below. (165-column-output mode has no protected area, thus requiring no row data to be written (Figure 15).)

Procedure of writing row data to the display memory is as follows. First, 1 must be written to the bit at the intersection between line Yj and line (column) Xi (column). Line Yj is filled with data to be displayed on the first line of the LCD and line Xi is connected to pin Xn, which drives the first line of the LCD. Following this, 0s must be written to the remaining bits on line Yj in the row data area. This rule applies to subsequent lines on the LCD.

Table 2 shows the relationship between FCR settings and protected areas.

Figure 16 shows the relationship between row data and display. Here the mode is 65-row output from the right side. Display data on Y0 is displayed on the first line of the LCD and data on Y64 is displayed on the 65th line of the LCD. If X164 is connected to the first line of the LCD and X100 is connected to the 65th line of the LCD, 1s must be written to the bits on the diagonal line between coordinates (X164, Y0) and (X100, Y64) and 0s to the remaining bits. Row data protect function must be turned off before writing row data and be turned on after writing row data. Turning on the row data protect function disables read/write of display memory area corresponding to the row output pins, i.e., prevents row data from being destroyed. In Figure 16, display memory area corresponding to pins X100 to X164 is protected.

Figures 17 to 19 show examples of row data settings. Some multiplexing duty ratios result in invalid display areas. Although an invalid display area can be read from or written to, it will not be displayed.

Table 2 Relationship between FCR Settings and Protected Areas

#### Control Register (FCR)

|     |   |   | ROS          | LCD Driving Signal Output Pins Connected to |         |

|-----|---|---|--------------|---------------------------------------------|---------|

| PON | 4 | 3 | Mode         | Protected Area of Display Memory            | Figures |

| 1   | 0 | 0 | 165-column   | No area protected                           | 15      |

| 1   | 0 | 1 | 65-row (R)   | X100-X164                                   | 16, 19  |

| 1   | 1 | 0 | 65-row (L/R) | X0-X31 and X132-X164                        | 17      |

| 1   | 1 | 1 | 33-row (R)   | X132-X164                                   | 18      |

65-row (R): 65-row-output mode from the right side

65-row (L/R): 65-row-output mode from the left and right sides

33-row (R): 33-row-output mode from the right side

Figure 15 Relationship between Row Data and Display (165-Column Output, 1/64 Multiplexing Duty Ratio)

Figure 16 Relationship between Row Data and Display (65-Row Output from the Right Side, 1/66 Multiplexing Duty Ratio)

Figure 17 Relationship between Row Data and Display (65-Row Output from the Left and Right Sides, 1/66 Multiplexing Duty Ratio)

Figure 18 Relationship between Row Data and Display (33-Row Output from the Right Side, 1/34 Multiplexing Duty Ratio)

Figure 19 Relationship between Row Data and Display (65-Row Output from the Right Side, 1/48 Multiplexing Duty Ratio)

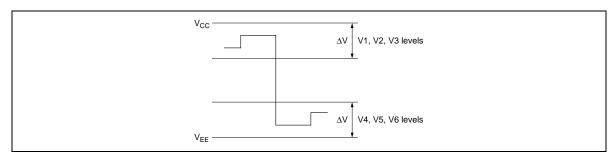

#### 4.3 LCD Driving Voltage Setting

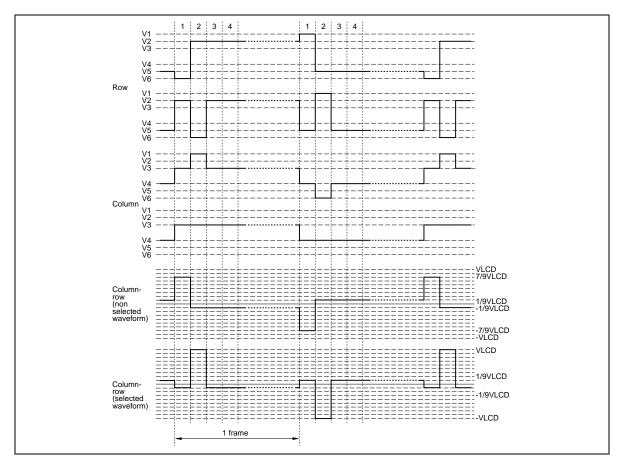

There are 6 levels of LCD driving voltages ranging from V1 to V6; V1 is the highest and V6 is the lowest. As shown in Figure 20, column output waveform is made up of a combination of V1, V3, V4, and V6 while row output waveform is made up of V1, V2, V5, and V6. This means that V1 and V6 are common to both waveforms while mid-voltages are different.

To accommodate this situation, each block of the HD66108T is provided with power supply pins for mid-voltages as shown in Figure 21. Each pair of V1R and V1L and V6R and V6L are internally connected and must be applied the same level of voltage. Block B is fixed for column output and must be applied V3 and V4 as mid-voltages. The other blocks must be applied different levels of voltages according to the function of their LCD driving output pins; if the LCD driving output pins are set for row output, VMHn and VMLn must be applied V2 and V5, respectively, while they must be applied V3 and V4, respectively, if the pins are set for column output (n = 1 to 3).

Table 3 Relationship between FCR Settings and LCD Driving Voltages

#### Control Register (FCR)

#### **LCD Driving Voltage Pins**

| ROS | S4 ROS | S3 Mode      | VIR/VII | _ V3 | V4 | VMH1 | VML1 | VMH2 | VML2 | VMH3 | VML3 | V6R/V6L |

|-----|--------|--------------|---------|------|----|------|------|------|------|------|------|---------|

| 0   | 0      | 165-column   | V1      | V3   | V4 | V3   | V4   | V3   | V4   | V3   | V4   | V6      |

| 0   | 1      | 65-row (R)   | V1      | V3   | V4 | V3   | V4   | V2   | V5   | V2   | V5   | V6      |

| 1   | 0      | 65-row (L/R) | V1      | V3   | V4 | V2   | V5   | V3   | V4   | V2   | V5   | V6      |

| 1   | 1      | 33-row (R)   | V1      | V3   | V4 | V3   | V4   | V3   | V4   | V2   | V5   | V6      |

65-row (R): 65-row-output mode from the right side

65-row (L/R): 65-row-output mode from the left and right sides

33-row (R): 33-row-output mode from the right side

Figure 20 LCD Driving Voltage Waveforms

#### 5. Multiplexing Duty Ratio and LCD Driving Waveform Settings

A multiplexing duty ratio and LCD driving waveform can be selected via internal registers.

A multiplexing duty ratio of 1/32, 1/34, 1/36, 1/48, 1/50, 1/64, or 1/66 can be selected according to the LCD panel used. However, since there are only 65 row-output pins, only 65 lines will be displayed even if 1/66 multiplexing duty ratio is selected.

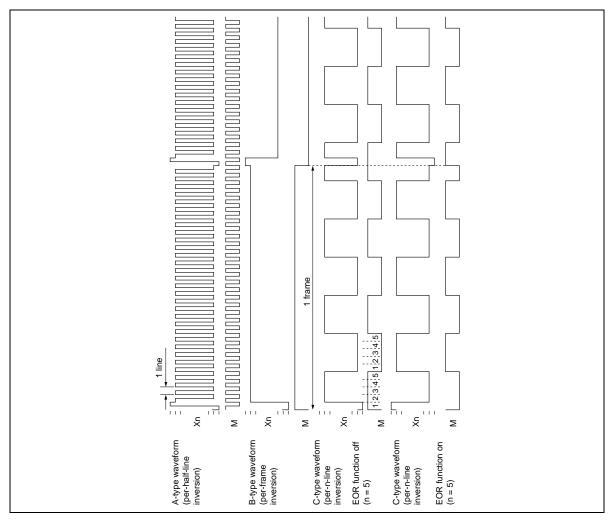

There are three types of LCD driving waveforms, as shown in Figure 22: A-type waveform, B-type waveform, and C-type waveform.

The A-type waveform is called per-half-line inversion. Here, the waveforms of M signal and CL1 signal are the same and alternate every LCD line.

The B-type waveform is called per-frame inversion; in this case, the M signal inverts its polarity every frame so as to alternate every two LCD frames. This is the most common type.

The C-type waveform is called per-n-line inversion and inverts its polarity every n lines (n can be set as needed within 1 to 31 via the internal registers). The C-type waveform combines the advantages of the A- and B-types of waveforms. However, some lines will not be alternated depending on the multiplexing duty ratio and n. To avoid this, another C-type waveform is available which is generated from the EOR of the C-type waveform M signal mentioned above and the B-type waveform M signal. Since the relationship between n and display quality usually depends on the LCD panel, n must be determined by observing actual display results.

The B-type waveform should be used if the LCD panel specifies no particular type of waveform. However, in some cases, the C-type waveform may create a better display.

Figure 21 Relationship between Blocks and LCD Driving Voltages

Figure 22 LCD Driving Waveforms (Row Output with a 1/32 Multiplexing Duty Ratio)

#### 6. Clock and Frame Frequency

An input clock with a 200-kHz to 4-MH frequency can be used for the HD66108T. Note that raising clock frequency increases current consumption although it reduces busy time and enables high-speed operations. An optimum system clock frequency should thus be selected within 200 kHz to 4 MHz.

The clock frequency driving the LCD panel (= frame frequency) is usually 70 Hz to 90 Hz. Accordingly, the HD66108T is so designed that the frequency-division ratio of the input clock can be selected. The HD66108T generates around 80-Hz LCD frame frequency if the frequency-division ratio is 1. The frequency-division ratio can be obtained from the following equation.

$$Ni = \frac{f_F}{f_{CLK}} \times \frac{500}{80} \times D1$$

Ni: Frequency-division ratio

f<sub>F</sub>: Frame frequency required for the LCD panel (Hz)

f<sub>CLK</sub>: Input clock frequency (kHz)

D1: Duty correction value 1

D1 = 1 when multiplexing duty ratio is 1/32, 1/48 or 1/64

D1 = 32/34 when multiplexing duty ratio is 1/34

D1 = 32/36 when multiplexing duty ratio is 1/36

D1 = 48/50 when multiplexing duty ratio is 1/50

D1 = 64/66 when multiplexing duty ratio is 1/66

The frequency-division ratio nearest the value obtained from the above equation must be selected; selectable frequency-division ratios by internal registers are 2, 1, 1/2, 1/3, 1/4, 1/6, and 1/8.

#### 7. Display Off Function

The HD66108T has a display off function which turns off display by rewriting the contents of the internal register. This prevents random display at power-on until display memory is initialized.

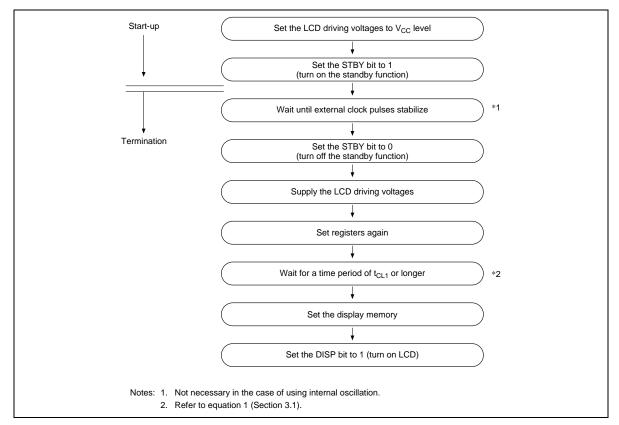

#### 8. Standby Function

The HD66108T has a standby function providing low-power dissipation. Writing a 1 to bit 6 of the address register starts up the standby function.

The LCD driving voltages, ranking from V1 to V6, must be set to  $V_{cc}$  to prevent DC voltage from being applied to an LCD panel during standby state.

The HD66108T operates as follows in standby mode.

- (1) Stops oscillation and external clock input

- (2) Resets all registers to 0's except the STBY bit

Here, note that the display memory will not preserve data if the standby function is turned on; the display memory as well as registers must be set again after the standby function is terminated. V1 to V6 terminals must be connected to  $V_{CC}$  to prevent DC voltage being supplied during stand by.

Table 4 shows the standby status of pins and Table 5 shows the status of registers after standby function termination.

Writing a 0 to bit 6 of the address register terminates the standby function. Writing values into the DISP and Register No. bits at this time is ignored; these bits need to be set after the standby function has been completely terminated.

Figure 23 shows the flow for start-up and termination of the standby function and related operations.

**Table 4** Standby Status of Pins

| Pin  | Status                                           |

|------|--------------------------------------------------|

| OSC2 | High                                             |

| СО   | Low                                              |

| CL1  | Low (master chip) or high-impedance (slave chip) |

| FLM  | Low (master chip) or high-impedance (slave chip) |

| M    | Low (master chip) or high-impedance (slave chip) |

| Xn   | V4 (column output pins)                          |

| Xn'  | V5 (row output pins)                             |

Table 5

Register Status after Standby Function Termination

| Register Name      | Status after Standby Function Termination |

|--------------------|-------------------------------------------|

| Address register   | Reset to 0's except for the STBY bit      |

| X address register | Reset to 0's                              |

| Y address register | Reset to 0's                              |

| Control register   | Reset to 0's                              |

| Mode register      | Reset to 0's                              |

| C select register  | Reset to 0's                              |

| Display memory     | Data not preserved                        |

Figure 23 Start-Up and Termination of Standby Function and Related Operations

#### 9. Multi-Chip Operation

Using multiple HD66108T chips (= multi-chip operation) provides the means for extending the number of display dots. Note the following items when using the multi-chip operation.

- (1) The master chip and the slave chips must be determined; the  $\overline{M}/S$  pin of the master chip must be set low and the  $\overline{M}/S$  pin of the slave chips must be set high.

- (2) All the HD66108T chips will be slave chips if HD61203 or its equivalent is used as a row driver.

- (3) The master chip supplies the FLM, CL1, and M signals to the slave chips via the corresponding pins, which synchronizes the slave chips with the master chip.

- (4) Since a master chip outputs synchronization signals, all data registers must be set.

- (5) The following bits for slave chips must always be set:

- INC, WLS, PON, and ROS (control register) FFS (mode register)

- It is not necessary to set the control register's DUTY bits, the mode register's DWS bits, or the C select register. For other registers' settings, refer to Table 6.

- (6) All chips must be set to LCD off in order to turn off the display.

- (7) The standby function of slave chips must be started up first while that of the master chip must be terminated first.

Figure 24 to 26 show the connections of the synchronization signals for different system configurations and Table 6 lists the differences between master mode and slave mode.

Table 6 Comparison between Master and Slave Mode

| Item      |             | Master Mode                                                  | Slave Mode                     |

|-----------|-------------|--------------------------------------------------------------|--------------------------------|

| Pin:      | M/S         | Must be set low                                              | Must be set high               |

|           | OSC1, OSC2  | Oscillation is possible                                      | Oscillation is possible        |

|           | CO          | = OSC1                                                       | = OCS1                         |

|           | FLM, CL1, M | Output signals                                               | Input signals                  |

| Register: | AR          | Valid                                                        | Valid                          |

|           | XAR         | Valid                                                        | Valid                          |

|           | YAR         | Valid                                                        | Valid                          |

|           | FCR         | Valid                                                        | Valid except for the DUTY bits |

|           | MDR         | Valid                                                        | Valid except for the DWS bits  |

|           | CSR         | Valid (only if the DWS bits are set for the C-type waveform) | Invalid                        |

Notes: Valid: Needs to be set Invalid: Needs not be set

Figure 24 Configuration Using Two HD66108T Chips (1)

Figure 25 Configuration Using Two HD66108T Chips (2)

Figure 26 Configuration Using One HD66108T Chip with Another Row Driver (HD61203U)

## **Internal Registers**

All HD66108T's registers can be read from and written into. However, the BUSY FLAG and invalid bits cannot be written to and reading invalid bits or registers returns 0's.

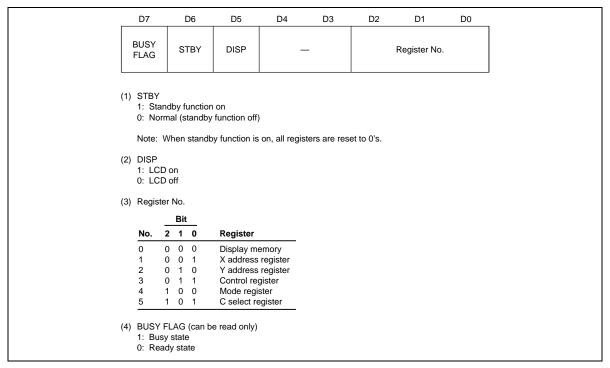

#### 1. Address Register (AR) (Accessed with RS = 0)

This register (Figure 27) contains Register No. bits, BUSY FLAG bit, STBY bit, and DISP bit. Register No. bits select one of the data registers according to the register number written. The BUSY FLAG bit indicates the internal operation state if read. The STBY bit activates the standby function. The DISP bit turns the display on or off. This register is selected when RS pin is 0.

Bits D4 and D3 are invalid.

Figure 27 Address Register

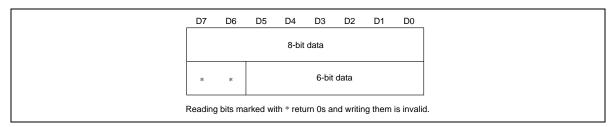

#### 2. Display Memory (DRAM) (Accessed with RS = 1, Register Number = (B'000)

Although display memory (Figure 28) is not a register, it can be handled as one. 8- or 6-bit data can be selected by the control register WLS bit according to the character font in use. If 6-bit data is selected, D7 and D6 bits are invalid.

#### 3. X Address Register (XAR) (Accessed with RS = 1, Register Number = (B'001)

This register (Figure 29) contains 3 invalid bits (D7 to D5) and 5 valid bits (D4 to D0). It sets X addresses and confirms X addresses after writing or reading to or from the display memory.

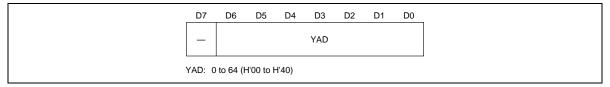

#### 4. Y Address Register (YAR) (Accessed with RS = 1, Register Number = (B'010)

This register (Figure 30) contains 1 invalid bit (D7) and 7 valid bits (D6 to D0). It sets Y addresses and confirms Y addresses after writing or reading to or from the display memory.

Figure 28 Display Memory

Figure 29 X Address Register

Figure 30 Y Address Register

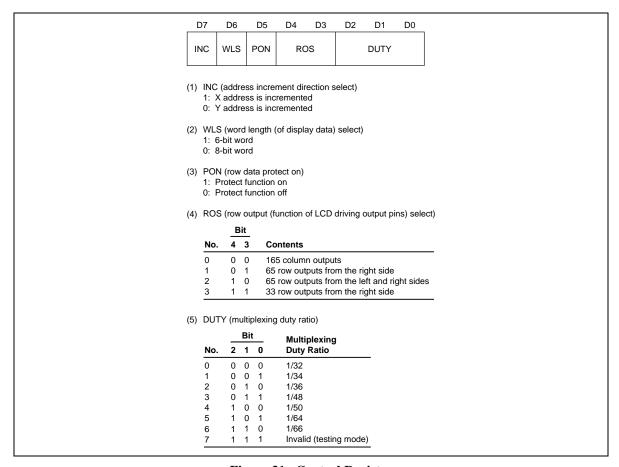

#### 5. Control Register (FCR) (Accessed with RS = 1, Register Number = (B'011)

This register (Figure 31), containing eight bits, has a variety of functions such as specifying the method for accessing RAM, determining RAM valid area, and selecting the function of the LCD driving signal output pins. It must be initialized as soon as possible after power-on since it determines the overall operation of the HD66108T. The PON bit may have to be reset afterwards. If the DUTY bits are rewritten after initialization at power-on (if values other than the initial values are desired), the display memory will not preserve data; the display memory must be set again after a time period of  $t_{CLI}$  or longer. For determining  $t_{CLI}$ , refer to equation 1 (Section 3.1).

Figure 31 Control Register

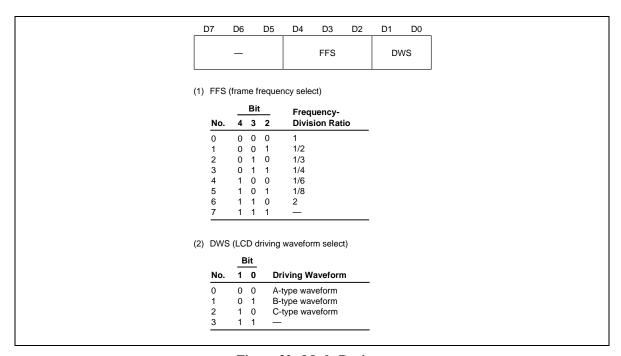

### 6. Mode Register (MDR) (Accessed with RS = 1, Register Number = (B'100)

This register (Figure 32), containing 3 invalid bits (D7 to D5) and 5 valid bits (D4 to D0), selects a system clock and type of LCD driving waveform. It must also be initialized after power-on since it determines overall HD66108T operation like the FCR register. If the FFS bits are rewritten after initialization at power-on (if values other than the initial values are desired), the display memory will not preserve data; the display memory must be set again after a time period of  $t_{CLI}$  or longer. For determining  $t_{CLI}$ , refer to equation 1 in section 3.1).

Figure 32 Mode Register

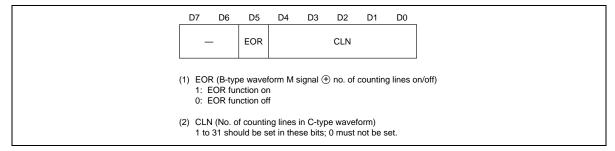

## 7. C Select Register (CSR) (Accessed with RS = 1, Register Number = (B'101)

This register (Figure 33) contains 2 invalid bits (D7 and D6) and 5 valid bits (D5 to D0). It controls C-type waveforms and is activated only when MDR register's DWS bits are set for this type of waveform.

Figure 33 C Select Register

### **Reset Function**

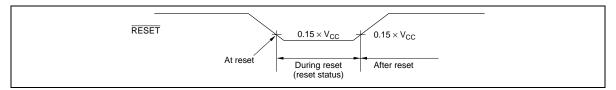

The  $\overline{RESET}$  pin starts the HD66108T after power-on. A  $\overline{RESET}$  signal must be input via this pin for at least 20  $\mu$ s to prevent system failure due to excessive current created after power-on. Figure 34 shows the reset definition.

### (1) The Status of Pins during Reset

Table 7 shows the reset status of output pins. The pins return to normal operation after reset.

Table 7 The Status of Pins during Reset

| Pin  | Status                                           |

|------|--------------------------------------------------|

| OSC2 | Outputs clock pulses or oscillates               |

| СО   | Outputs clock pulses                             |

| CL1  | Low (master chip) or high-impedance (slave chip) |

| FLM  | Low (master chip) or high-impedance (slave chip) |

| M    | Low (master chip) or high-impedance (slave chip) |

| Xn   | V4 (column output pins)                          |

| Xn'  | V5 (row output pins)                             |

Figure 34 Reset Definition

### (2) The Status of Registers during Reset

The  $\overline{RESET}$  signal has no effect on registers or register bits except for the address register's STBY bit and the X and Y address registers, which are reset to 0's by the signal. Table 8 shows the reset status of registers.

### (3) Status after Reset

The display memory does not preserve data which has been written to it before reset; it must be set again after reset.

A RESET signal terminates the standby mode.

Table 8 The Status of Registers during Reset

| Register           | Status                                        |

|--------------------|-----------------------------------------------|

| Address register   | Pre-reset status with the STBY bit reset to 0 |

| X address register | Reset to 0's                                  |

| Y address register | Reset to 0's                                  |

| Control register   | Pre-reset status                              |

| Mode register      | Pre-reset status                              |

| C select register  | Pre-reset status                              |

| Display memory     | Preserves no pre-reset data                   |

#### **Precautionary Notes When Using the HD66108T**

- (1) Install a 0.1- $\mu$ F bypass capacitor as close to the LSI as possible to reduce power supply impedance ( $V_{CC}$ -GND and  $V_{CC}$ - $V_{FF}$ ).

- (2) Do not leave input pins open since the HD66108T is a CMOS LSI; refer to "Pin Functions" on how to deal with each pin.

- (3) When using the internal oscillation clock, attach an oscillation resistor as close to the LSI as possible to reduce coupling capacitance.

- (4) Make sure to input the reset signal at power-on so that internal units operate as specified.

- (5) Maintain the LCD driving power at  $V_{cc}$  during standby state so that DC is not applied to an LCD, in which Xn pins are fixed at V4 or V5 level.

#### **Programming Restrictions**

- (1) After busy time is terminated, an X or Y address is not incremented until 0.5-clock time has passed. If an X or Y address is read during this time period, non-updated data will be read. (The addresses are incremented even in this case.) In addition, the address increment direction should not be changed during this time since it will cause malfunctions.

- (2) Although the maximum output rows is 33 when 33-row-output mode from the right side is specified, any multiplexing duty ratio can be specified. Therefore, row output data sufficient to fill the specified duty must be input in the Y direction. Figure 35 shows how to set row data in the case of 1/34 multiplexing duty ratio. In this case, 0s must be set in Y33 since data for the 34th row (Y33) are not output.

- (3) Do not set the C select register's CLN bits to 0 for the M signal of C-type waveform.

Figure 35 How to Set Row Data for 33-Row Output from the Right Side

## **Absolute Maximum Ratings**

| Item                     | Symbol                               | Ratings                  | Unit |  |

|--------------------------|--------------------------------------|--------------------------|------|--|

| Power supply voltage (1) | V <sub>cc1</sub> to V <sub>cc3</sub> | -0.3 to +7.0             | V    |  |

| Power supply voltage (2) | V <sub>cc</sub> -V <sub>EE</sub>     | -0.3 to +16.5            | V    |  |

| Input voltage            | Vin                                  | $-0.3$ to $V_{cc}$ + 0.3 | V    |  |

| Operating temperature    | T <sub>op</sub>                      | –20 to +75               | °C   |  |

| Storage temperature      | T <sub>stg</sub>                     | -40 to +125              | °C   |  |

- Notes: 1. Permanent LSI damage may occur if the maximum ratings are exceeded. Normal operation should be under recommended operating conditions ( $V_{cc}$  = 2.7 to 6.0V, GND = 0V, Ta = -20 to +75°C). If these conditions are exceeded, LSI malfunctions could occur.

- 2. Power supply voltages are referenced to GND = 0V. Power supply voltage (2) indicates the difference between  $V_{cc}$  and  $V_{ee}$ .

## **Electrical Characteristics**

DC Characteristics (1) ( $V_{\rm CC}$  = 5V ±20%, GND = 0V,  $V_{\rm CC}$  –  $V_{\rm EE}$  = 6.0 to 15V, Ta = –20 to +75°C, unless otherwise noted)

| Item                         |                                              | Symbol                | Min                  | Тур | Max                   | Unit | Test Conditions                                      | Note<br>s |

|------------------------------|----------------------------------------------|-----------------------|----------------------|-----|-----------------------|------|------------------------------------------------------|-----------|

| Input high                   | OSC1                                         | V <sub>IH1</sub>      | $0.8 \times V_{cc}$  | _   | V <sub>cc</sub> + 0.3 | V    |                                                      |           |

| voltage                      | M/S, CL1, FLM, M, TEST1, TEST2               | $V_{_{\mathrm{IH2}}}$ | $0.7 \times V_{cc}$  | _   | V <sub>cc</sub> + 0.3 | V    |                                                      |           |

|                              | RESET                                        | V <sub>IH3</sub>      | $0.85 \times V_{cc}$ | _   | V <sub>cc</sub> +0.3  | V    |                                                      |           |

|                              | The other inputs                             | $V_{IH4}$             | 2.0                  | _   | V <sub>cc</sub> + 0.3 | V    | V <sub>cc</sub> = 5V ±10%                            | 5         |

| Input low                    | OSC1                                         | V <sub>IL1</sub>      | -0.3                 | _   | $0.2 \times V_{cc}$   | V    |                                                      |           |

| voltage                      | M/S, CL1, FLM, M, TEST1, TEST2               | $V_{_{\rm IL2}}$      | -0.3                 | _   | $0.3 \times V_{cc}$   | V    |                                                      |           |

|                              | RESET                                        | V <sub>IL3</sub>      | -0.3                 | _   | $0.15 \times V_{cc}$  | V    |                                                      |           |

|                              | The other inputs                             | V <sub>IL4</sub>      | -0.3                 | _   | 0.8                   | V    | V <sub>cc</sub> = 5V ±10%                            | 6         |

| Output high voltage          | CO, CL1, FLM,<br>M                           | $V_{OH1}$             | $0.9 \times V_{cc}$  | _   | _                     | V    | -I <sub>OH</sub> = 0.1 mA                            |           |

|                              | DB7-DB0                                      | $V_{\text{OH2}}$      | 2.4                  | _   | _                     | V    | $-I_{OH} = 0.2 \text{ mA}$<br>$V_{CC} = 5V \pm 10\%$ | 7         |

| Output low voltage           | CO, CL1, FLM,<br>M                           | $V_{OL1}$             | _                    | _   | $0.1 \times V_{cc}$   | V    | I <sub>OL</sub> = 0.1 mA                             |           |

|                              | DB7-DB0                                      | $V_{OL2}$             | _                    | _   | 0.4                   | V    | $I_{oL} = 1.6 \text{ mA}$<br>$V_{cc} = 5V \pm 10\%$  | 8         |

| Input<br>leakage<br>current  | All except<br>DB7-DB0,<br>CL1, FLM, M        | I <sub>IIL</sub>      | -2.5                 | _   | 2.5                   | μΑ   | Vin = 0 to V <sub>cc</sub>                           |           |

| Tri-state leakage current    | DB7-DB0, CL1,<br>FLM, M                      | I <sub>TSL</sub>      | -10                  | _   | 10                    | μΑ   | $Vin = 0 \text{ to } V_{cc}$                         |           |

| V pins<br>leakage<br>current | V1L, V1R, V3, V4,<br>V6L, V6R,<br>VMHn, VMLn | I <sub>VL</sub>       | -10                  | _   | 10                    | μΑ   | $Vin = V_{EE} \text{ to } V_{CC}$                    |           |

| Current consumption          | During display                               | I <sub>CC1</sub>      | _                    | _   | 400                   | μΑ   | External clock<br>f <sub>osc</sub> = 500 kHz         | 1         |

|                              |                                              | I <sub>CC2</sub>      | _                    | _   | 1.0                   | mA   | Internal oscillation $R_f = 91 \text{ k}\Omega$      | 1         |

|                              | During standby                               | I <sub>SB</sub>       | _                    | _   | 10                    | μΑ   |                                                      | 1, 2      |

| Item                                  |         | Symbol           | Min | Тур | Max | Unit | <b>Test Conditions</b>                           | Notes |

|---------------------------------------|---------|------------------|-----|-----|-----|------|--------------------------------------------------|-------|

| ON resistance<br>between<br>Vi and Xj | X0-X164 | R <sub>on</sub>  | _   | _   | 10  | kΩ   | $\pm I_{LD} = 50 \mu A$ $V_{CC} - V_{EE} = 10 V$ | 3     |

| V pins voltage rai                    | nge     | ÆV               | _   | _   | 35  | %    |                                                  | 4     |

| Oscillating frequency                 |         | f <sub>osc</sub> | 315 | 450 | 585 | kHz  | $R_f = 91 \text{ k}\Omega$                       |       |

- Notes: 1. When voltage applied to input pins is fixed to V<sub>cc</sub> or to GND and output pins have no load capacity.

- 2. When the LSI is not exposed to light and Ta = 0 to 40°C with the STBY bit = 1. If using external clock pulses, input pins must be fixed high or low. Exposing the LSI to light increases current consumption.

- 3.  $I_{LD}$  indicates the current supplied to one measured pin.

- 4.  $\not$ EV = 0.35  $\times$  (V<sub>cc</sub>-V<sub>EE</sub>). For levels V1, V2, and V3, the voltage supplied should be between the V<sub>cc</sub> and the  $\not$ EV and for levels V4, V5, and V6, the voltage supplied should be between the V<sub>EE</sub> and the  $\not$ EV (Figure 36).

- 5.  $V_{IH4}$  (min) = 0.7 ×  $V_{CC}$  when used under conditions other than  $V_{CC}$  = 5V ±10%.

- 6.  $V_{IL4}$  (max) = 0.15 ×  $V_{cc}$  when used under conditions other than  $V_{cc}$  = 5V ±10%.

- 7.  $V_{OH2}$  (min) =  $0.9 \times V_{CC}$  ( $-I_{OH}$  = 0.1 mA) when used under conditions other than  $V_{CC}$  =  $5V \pm 10\%$ .

- 8.  $V_{OL2}$  (max) = 0.1 ×  $V_{CC}$  ( $I_{OL}$  = 0.1 mA) when used under conditions other than  $V_{CC}$  = 5V ±10%.

DC Characteristics (2) ( $V_{cc}$  = 2.7 to 4.0V, GND = 0V,  $V_{cc}$ – $V_{EE}$  = 6.0 to 15V, Ta = -20 to +75°C, unless otherwise noted)

| Item                                  |                                                 | Symbol           | Min                  | Тур | Max                   | Unit | Test Conditions                                  | Notes |

|---------------------------------------|-------------------------------------------------|------------------|----------------------|-----|-----------------------|------|--------------------------------------------------|-------|

| Input high                            | RESET                                           | V <sub>IH1</sub> | $0.85 \times V_{cc}$ | _   | V <sub>cc</sub> + 0.3 | V    |                                                  |       |

| voltage                               | The other inputs                                | V <sub>IH2</sub> | $0.7 \times V_{cc}$  | _   | V <sub>cc</sub> + 0.3 | V    |                                                  |       |

| Input low voltage                     | M/S, OSC1,<br>CL1, FLM,<br>TEST1,<br>TEST2, M   | V <sub>IL1</sub> | -0.3                 |     | 0.3 × V <sub>cc</sub> | V    |                                                  |       |

|                                       | The other inputs                                | $V_{\rm IL2}$    | -0.3                 | _   | $0.15 \times V_{cc}$  | V    |                                                  |       |

| Output high voltage                   |                                                 | V <sub>OH1</sub> | $0.9 \times V_{cc}$  | _   | _                     | V    | -I <sub>OH</sub> = 50 μA                         |       |

| Output low voltage                    |                                                 | V <sub>OL1</sub> | _                    | _   | $0.1 \times V_{cc}$   | V    | I <sub>oL</sub> = 50 μA                          |       |

| Input leakage current                 | All except<br>DB7–DB0,<br>CL1, FLM, M           | I <sub>IIL</sub> | -2.5                 | _   | 2.5                   | μA   | Vin = 0 to V <sub>cc</sub>                       |       |

| Tri-state<br>leakage<br>current       | DB7-DB0,<br>CL1, FLM, M                         | I <sub>TSL</sub> | <b>-10</b>           | _   | 10                    | μA   | Vin = 0 to V <sub>cc</sub>                       |       |

| V pins<br>leakage<br>current          | V1L, V1R,<br>V3, V4,<br>V6L, V6R,<br>VMHn, VMLn | I <sub>VL</sub>  | -10                  |     | 10                    | μA   | $Vin = V_{EE} \text{ to } V_{CC}$                |       |

| Current consumption                   | During display                                  | I <sub>CC1</sub> | _                    | _   | 260                   | μA   | External clock<br>f <sub>osc</sub> = 500 kHz     | 1     |

|                                       |                                                 | I <sub>CC2</sub> | _                    | _   | 700                   | μA   | Internal oscillation $R_f = 75 \text{ k}\Omega$  | 1     |

|                                       | During standby state                            | I <sub>SB</sub>  | _                    | _   | 10                    | μA   |                                                  | 1, 2  |

| ON resistance<br>between<br>Vi and Xj | X0-X164                                         | R <sub>on</sub>  | _                    | _   | 10                    | kΩ   | $\pm I_{LD} = 50 \mu A$ $V_{CC} - V_{EE} = 10 V$ | 3     |

| V pins voltage r                      | ange                                            | ÆV               | _                    | _   | 35                    | %    |                                                  | 4     |

| Oscillating frequency                 | uency                                           | f <sub>osc</sub> | 315                  | 450 | 585                   | kHz  | $R_f = 75 \text{ k}\Omega$                       |       |

|                                       | -                                               |                  |                      | _   |                       | _    |                                                  |       |

Notes: 1. When voltage applied to input pins is fixed to V<sub>cc</sub> or to GND and output pins have no load capacity. Exposing the LSI to light increases current consumption.

<sup>2.</sup> When the LSI is not exposed to light and Ta = 0 to 40°C with the STBY bit = 1. If using external clock pulses, input pins must be fixed high or low.

<sup>3.</sup>  $\rm\,I_{\tiny LD}$  indicates the current supplied to one measured pin.

<sup>4.</sup>  $\not$ EV = 0.35 × ( $V_{cc}$ - $V_{ee}$ ). For levels V1, V2, and V3, the voltage supplied should be between the  $V_{cc}$  and the  $\not$ EV and for levels V4, V5, and V6, the voltage supplied should be between the  $V_{ee}$  and the  $\not$ EV (Figure 36).

Figure 36 Driver Output Waveform and Voltage Levels

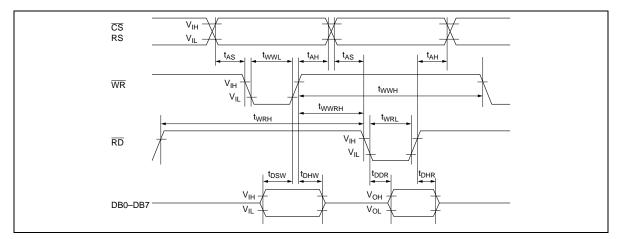

AC Characteristics (1) ( $V_{\rm cc}$  = 4.5 to 6.0V, GND = 0V, Ta = -20 to +75°C, unless otherwise noted)

### 1. CPU Bus Timing (Figure 37)

| Item                                  | Symbol                                | Min  | Max | Unit |      |

|---------------------------------------|---------------------------------------|------|-----|------|------|

| RD high-level pulse width             | t <sub>wrh</sub>                      | 190  | _   | ns   |      |

| RD low-level pulse width              | t <sub>wrl</sub>                      | 190  | _   | ns   |      |

| WR high-level pulse width             | t <sub>wwн</sub>                      | 190  |     | ns   |      |

| WR low-level pulse width              | t <sub>wwL</sub>                      | 190  | _   | ns   |      |

| WR-RD high-level pulse width          | t <sub>wwr</sub>                      | 190  | _   | ns   |      |

| CS, RS setup time                     | t <sub>AS</sub>                       | 0    | _   | ns   |      |

| CS, RS hold time                      | t <sub>AH</sub>                       | 0    | _   | ns   |      |

| Write data setup time                 | t <sub>DSW</sub>                      | 100  | _   | ns   |      |

| Write data hold time                  | t <sub>DHW</sub>                      | 0    |     | ns   |      |

| Read data output delay time           | t <sub>DDR</sub>                      | _    | 150 | ns   | Note |

| Read data hold time                   | $\mathbf{t}_{\scriptscriptstyle DHR}$ | 20   |     | ns   | Note |

| External clock cycle time             | t <sub>cyc</sub>                      | 0.25 | 5.0 | μs   |      |

| External clock high-level pulse width | $\mathbf{t}_{wch}$                    | 0.1  |     | μs   |      |

| External clock low-level pulse width  | t <sub>wcL</sub>                      | 0.1  | _   | μs   |      |

| External clock rise and fall time     | $t_r$ , $t_f$                         | _    | 20  | ns   |      |

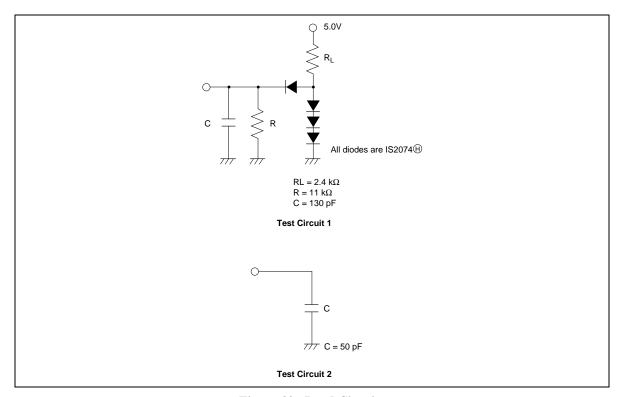

Note: Measured by test circuit 1 (Figure 39).

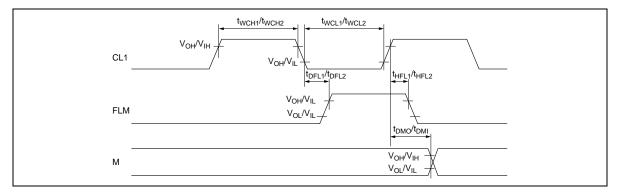

## 2. LCD Interface Timing (Figure 38)

| Item                 |                            | Symbol            | Min                        | Max                         | Unit | Notes |

|----------------------|----------------------------|-------------------|----------------------------|-----------------------------|------|-------|

| $\overline{M}/S = 0$ | CL1 High-level pulse width | t <sub>wcH1</sub> | 35                         | _                           | μs   | 1, 4  |

|                      | CL1 Low-level pulse width  | t <sub>wcL1</sub> | 35                         | _                           | μs   | 1, 4  |

|                      | FLM Delay time             | t <sub>DFL1</sub> | -2.0                       | +2.0                        | μs   | 4     |

|                      | FLM Hold time              | t <sub>HFL1</sub> | -2.0                       | +2.0                        | μs   | 4     |

|                      | M output delay time        | t <sub>DMO1</sub> | -2.0                       | +2.0                        | μs   | 4     |

| $\overline{M}/S = 1$ | CL1 High-level pulse width | t <sub>wcH2</sub> | 35                         | _                           | μs   | 4     |

|                      | CL1 Low-level pulse width  | t <sub>wcl2</sub> | $11 \times t_{\text{CYC}}$ | _                           | μs   | 2, 4  |