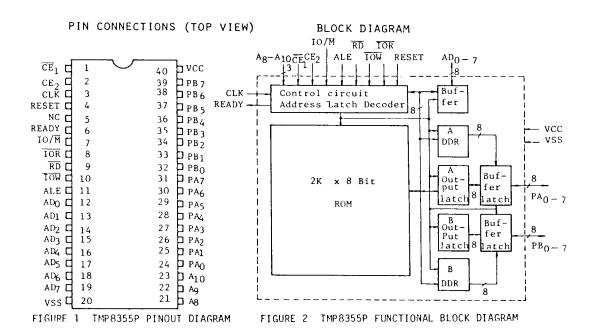

16,384 BIT ROM WITH I/O PORTS

## GENERAL DESCRIPTION

The TMP8355P is a ROM and I/O chip to be used in the TLCS-85A microcomputer system. The ROM portion is organized as 2,048 words by 8 bits. The I/O portion consists of 2 general purpose I/O ports. Each I/O port has 8 port lines, and each I/O port line is individually programmable as input or output.

## **FEATURES**

- · 2048 words x 8 bits ROM

- · Single + 5V Power Supply

- · Internal Address Latch

- · 2 General Purpose 8-Bit I/O Ports

- · Access Time : 400 ns (MAX.)

- · Each I/O Port Line Individually Programmable as Input or Output

- · Multiplexed Address and Data Bus

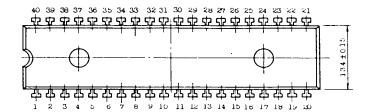

- · 40 pin DIP

- · Compatible with Inptel's 8355

## PIN NAMES AND PIN DESCRIPTION

## ALE (INPUT)

When Address Latch Enable goes high,  $AD_{0-7}$ , IO/M,  $A_{8-10}$ ,  $CE_2$ , and  $\overline{CE}_1$ , enter the address latches. The signals ( $AD_{0-7}$ , IO/M,  $A_{8-10}$ ,  $CE_2$ ,  $\overline{CE}_1$ ) are latched in at the trailing edge of ALE.

## $AD_{0-7}$ (INPUT/OUTPUT, 3-STATE)

Bi-directional Address/Data bus. The lower 8-bits of the ROM or I/O address are applied to the bus lines when ALE is high. During an 1/O cycle, Port A or B are selected based on the latched value of  $AD_0$ . If RD or  $\overline{10R}$  is low when the latched Chip Enables are active, the output buffers present data on the bus.

## $A_{8-10}$ (INPUT)

These are the high order bits of the ROM address. They do not affect  $\ensuremath{\mathrm{I}}/0$  operations.

## CE1, CE2 (INPUT)

CHIP ENABLE INPUTS:  $\overline{\text{CE}}_1$  is active low and  $\text{CE}_2$  is active high. Both chip enables must be active to permit accessing the ROM.

## IO/M (INPUT)

If the latched  $IO/\overline{M}$  is high when  $\overline{RD}$  is low, the output data comes from an I/O port. If it is low the output data comes from the ROM.

## RD (INPUT)

If the latched Chip Enables are active when  $\overline{\text{RD}}$  goes low, the AD $_{0-7}$  output buffers are enabled and output either the selected ROM location or I/O port. When both  $\overline{\text{RD}}$  and  $\overline{\text{IOR}}$  are high, the AD $_{0-7}$  output buffers are 3-stated.

## TOW (INPUT)

If the latched Chip Enables are active, a low on  $\overline{\text{low}}$  causes the output port pointed to by the latched value of  $\text{AD}_0$  to be written with the data on  $\text{AD}_{0-7}$ . The state of IO/M is ignored.

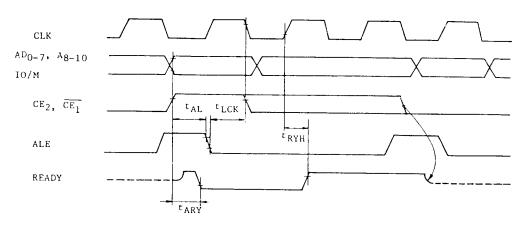

## CLK (INPUT)

The CLK is used to force the READY into its high state after it has been forced low by  $\overline{\text{CE}}_1$  loW, CE2 high, and ALE high.

## READY (OUTPUT, 3-STATE)

READY is a 3-state output controlled by  $\overline{\text{CE}}_1$ ,  $\text{CE}_2$ , ALE and CLK. READY is forced low when the Chip Enables are active during the time ALE is high, and remains low until the rising edge of the next CLK.

## PAO - PA7 (INPUT/OUTPUT, 3-STATE)

These are general purpose I/O pins. Their input/output direction is determined by the contents of Data Direction Register (DDR). Port A is selected for write operations when the Chip Enables are active, and  $\overline{10W}$  is low and a 0 was previously latched from AD $_0$ .

Read operation is selected by either  $\overline{10R}$  low, active Chip Enables and ADO low, or IO/M high,  $\overline{RD}$  low, active Chip Enables, and ADO low.

## PBO - PB7 (INPUT/OUTPUT, 3-STATE)

This general purpose I/O port is identical to Port A except that it is selected by a 1 latched from  $AD_{O}$ .

## RESET (INPUT)

In normal operation, an input high on RESET causes all pins in Ports A and B to assume input mode (clear DDR register).

## IOR (INPUT)

When the Chip Enables are active, a low on  $\overline{10R}$  will output the selected I/O port onto the AD bus.  $\overline{10R}$  low performs the same function as the combination of IO/M high and  $\overline{RD}$  low. When  $\overline{10R}$  is not used in a system,  $\overline{10R}$  should be tied to  $V_{CC}$  "1".

VCC (POWER)

+5 volt supply.

VSS (POWER)

Ground Reference

FUNCTIONAL DESCRIPTION

## ROM SECTION

The TMP8355P contains an 8-bit address latch which allows it to interface cirectly to TLCS-85A microcomputer system without additional hardware. The ROM portion of the chip is addressed by the 11-bit address (A8-10, AD<sub>0-7</sub>) and CE. The address,  $10/\overline{\text{M}}$ ,  $\text{CE}_2$  and  $\overline{\text{CE}}_1$  are latched into the address latches on falling edge of ALE. If the Chip Enables ( $\text{CE}_2$  and  $\overline{\text{CE}}_1$ ) are active and  $10/\overline{\text{M}}$  is low when  $\overline{\text{RD}}$  goes low, the contents of the ROM location addressed by the latched address are put out on the AD<sub>0-7</sub> lines.

## I/O SECTION

The I/O port portion consits of two 8-bit I/O ports and two 8-bit Data Direction Registers (DDR). The I/O portion of the chip is addressed by the latched value of ADO and ADO. Contents of Port A and Port B can be read and written, but the contents of DDR's cannot be read. The contents of the selected I/O port can be read out when the latched Chip Enable are active and either  $\overline{\text{RD}}$  goes low with  $\overline{\text{IO/M}}$  high, or  $\overline{\text{IOR}}$  goes low.

The two 8-bit DDR's (DDRA and DDRB) are used to determine the input/output status of each pin in the corresponding port.

A '0' specifies an input mode and a '1' specifies an output mode. The two 8-bit DDR's are cleared by RESET signal. The table 1 summarize Port and DDR designation.

TABLE 1, SELECTION OF PORT AND DDR DESIGNATION

| AD <sub>1</sub> | AD <sub>O</sub> | Selection                              |

|-----------------|-----------------|----------------------------------------|

| 0               | 0               | Port A                                 |

| 0               | 1               | Port B                                 |

| 1               | 0               | Port A Data Direction Register (DDR A) |

| 1               | 1               | Port B Data Direction Register (DDR B) |

## ABSOLUTE MAXIMUM RATINGS

| Symbol           | Item                                                           | Rating          |  |

|------------------|----------------------------------------------------------------|-----------------|--|

| v <sub>cc</sub>  | V <sub>CC</sub> Supply Voltage with Respect to V <sub>SS</sub> | -0.5V to 7.0V   |  |

| иIA              | Input Voltage with Respect to ${ m V}_{ m SS}$                 | -0.5V to 7.0V   |  |

| v <sub>out</sub> | Output Voltage with Respect to V <sub>SS</sub>                 | -0.5V to 7.0V   |  |

| P <sub>D</sub>   | Power Dissipation                                              | 1.5W            |  |

| TSOLDER          | Soldering Temperature (Soldering Time 10sec.)                  | 260°C           |  |

| TSTG             | Storage Temperature                                            | -55°C to+150°C. |  |

| TOPR             | Operating Temperature                                          | 0°C to+70°C     |  |

## D.C. CHARACTERISTICS

$T_A = 0$ °C to 70°C,  $V_{CC} = 5V + 5\%$

| Symbol          | Parameter                      | Test Conditions               | Min. | Тур. | Max.                 | Units |

|-----------------|--------------------------------|-------------------------------|------|------|----------------------|-------|

| v <sub>IL</sub> | Input Low Voltage              |                               | -0.5 |      | 0.8                  | V     |

| VIH             | Input High Voltage             |                               | 2.0  |      | v <sub>CC</sub> +0.5 | V     |

| $v_{OL}$        | Output Low Voltage             | $I_{OL} = 2mA$                |      |      | 0.45                 | V     |

| v <sub>OH</sub> | Output High Voltage            | I <sub>OH</sub> = -400μA      | 2.4  |      |                      | v     |

| IIL             | Input Leakage Current          | $V_{IN} = V_{CC}$ to $0V$     |      |      | ± 10                 | μA    |

| I <sub>LO</sub> | Output Leakage Current         | 0.45 ≤ Vout ≤ V <sub>CC</sub> |      |      | ± 10                 | μА    |

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current |                               |      |      | 180                  | πA    |

## A.C. CHARACTERISTICS

$T_A = 0$ °C to 70°C,  $V_{CC} = 5V \pm 5\%$

| Symbol           | Parameter                          | Test<br>Conditions | Min. | Тур.     | Max. | Units |

|------------------|------------------------------------|--------------------|------|----------|------|-------|

| t <sub>CYC</sub> | Clock Cycle Time                   |                    | 320  |          |      | ns    |

| t <sub>L</sub>   | CLK Low Width                      | 1                  | 80   |          |      | ns    |

| t <sub>H</sub>   | CLK High Width                     | ]                  | 120  |          |      | ns    |

| tr,tf            | CLK Rise and Fall Time             |                    |      |          | 30   | ns    |

| t <sub>AL</sub>  | Address to Latch Set Up Time       |                    | 50   |          |      | ns    |

| t <sub>LA</sub>  | Address Hold Time after Latch      |                    | 80   |          |      | ns    |

| <sup>t</sup> LC  | Latch to READ/WRITE Control        |                    | 100  |          |      | ns    |

| t <sub>RD</sub>  | Valid Data Out Delay from          | 150pF              |      |          | 170  | ns    |

|                  | READ Control                       |                    |      | <u> </u> |      |       |

| t <sub>AD</sub>  | Address Stable to Data Out Valid   | Load               |      |          | 400  | ns    |

| tLL              | Latch Enable Width                 |                    | 100  |          |      | ns    |

| t <sub>RDF</sub> | Data Bus Float after READ          | 1                  | 0    |          | 100  | ns    |

| t <sub>CL</sub>  | READ/WRITE Control to Latch Enable |                    | 20   |          |      | ns    |

| <sup>t</sup> CC  | READ/WRITE Control Width           |                    | 250  |          |      | ns    |

| t <sub>DW</sub>  | Data In to WRITE Set Up Time       | ]                  | 150  |          |      | ns    |

| tWD              | Data In Hold Time after WRITE      | ]                  | 10   |          |      | ns    |

| twp              | WRITE to Port Output               | ]                  |      |          | 400  | ns    |

| t <sub>PR</sub>  | Port Input Set Up Time             | ]                  | 50   |          |      | ns    |

| t <sub>RP</sub>  | Port Input Hold Time               | ]                  | 50   |          |      | ns    |

| tRYH             | READY Hold Time                    |                    | 0    |          | 160  | ns    |

| tARY             | ADDRESS (CE) to READY              |                    |      |          | 160  | ns    |

| t <sub>RV</sub>  | Recovery Time between Controls     | 1                  | 300  |          |      | ns    |

| t <sub>RDE</sub> | Data Out Delay from READ Controls  |                    | 10   |          |      | ns    |

| <sup>t</sup> LCK | ALE Low during CLK High            |                    | 100  |          |      | ns    |

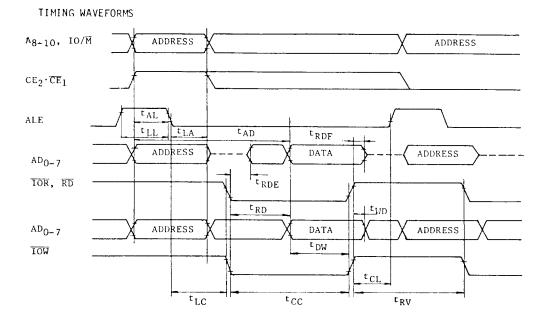

FIGURE 3 PROM READ, I/O READ, AND WRITE TIMING

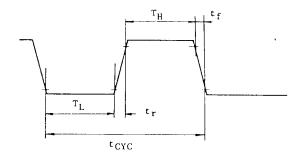

FIGURE 4 CLOCK SPECIFICATION FOR TMP8355P

FIGURE 5 WAIT STATE TIMING (READY = 0)

# A. INPUT MODE RD, TOR PORT INPUT ADO-7 B. OUTPUT MODE TOW PORT OUTPUT ADO-7

FIGURE 6 I/O PORT TIMING

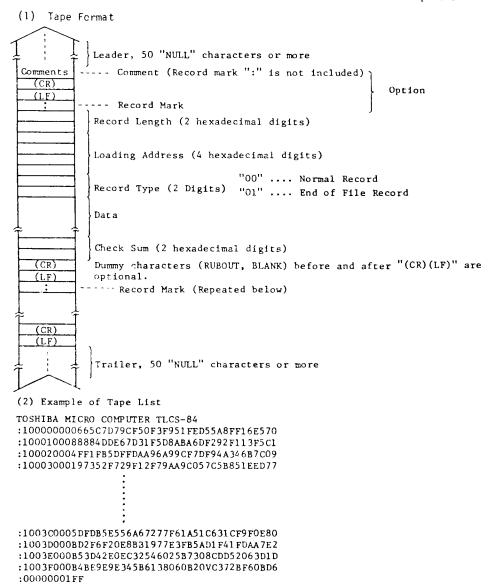

## PROGRAM TAPE FORMAT

TMP8355P programs are delivered in the form of punched paper tape or the 8755A from which to copy. In case of the 8755A, Toshiba needs two pieces.

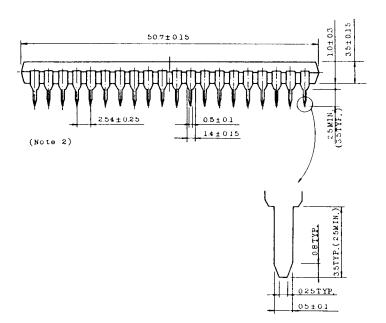

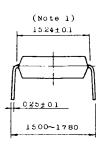

OUTLINE DRAWING

Unit in mm

- Note: 1. This dimension is measured at the center of bending point of leads.

- 2. Each lead pitch is 2.54mm, and all the leads are located within  $\pm 0.25$ mm from their theoritical positions with respect to No.1 and No.40 leads.