# 128KB SECONDARY CACHE MODULE FOR THE INTEL<sup>TM</sup> i486<sup>TM</sup>

PRELIMINARY IDT7MB6091

#### **FEATURES:**

- Pin compatible with the Intel 485Turbocache™ 82485MB

- 128KB direct mapped, write-through, non-sectored, zero wait-state secondary cache module

- Ideal for use with i486-based systems with an Intel 485Turbocache socket

- Uses the IDT71589 32K x 9 CacheRAM™ with burst counter and self-timed write and the IDT71B74 cache-tag RAM

- · Operates with external i486 speeds of up to 33MHz

- · Concurrent snooping is supported

- 485Turbocache write protect strap feature is not supported

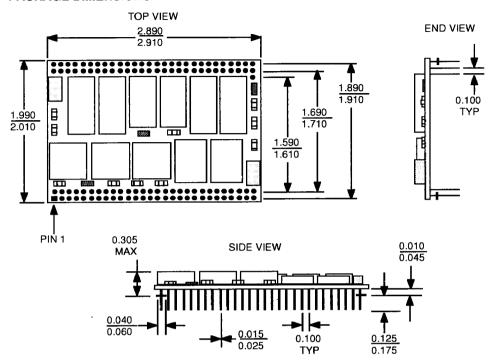

- 113 lead FR-4 QIP (Quad in-Line Package)

- · Single 5V (±5%) power supply

- Multiple GND pins and decoupling capacitors for maximum noise immunity

- · Inputs/outputs directly TTL compatible

#### DESCRIPTION:

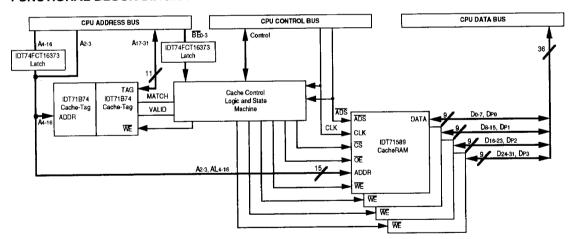

The IDT7MB6091 is a pin compatible replacement for the Intel 485Turbocache™ 82485MB. The module is a 128KB direct mapped, write-through, non-sectored, zero wait-state secondary cache and is ideal for use with many i486-based systems that have an Intel 485Turbocache socket. The IDT7MB6091 uses four IDT71589 32K x 9 CacheRAMs, two IDT71B74 8K x 8 cache-tag RAMs and two IDT74FCT16373 Double-Density™ 16-bit latches in plastic surface mount packages mounted on a multilayer epoxy laminate (FR-4) board along with logic for cache control. Extremely high speeds are achieved using IDT's high performance, high reliability BiCEMOS™ and CEMOS™ technologies.

An internal burst address counter accepts the first cycle address from the processor and then cycles through the adjacent four locations using the i486's burst refill sequence on appropriate rising edges of the system clock.

The quad in-line package (QIP) package configuration allows 113 leads to be placed on a package 2.9 inches long by 2.0 inches wide and 0.25 inches tall. All inputs and outputs of the IDT7MB6091 are TTL compatible and operate from a single 5V power supply.

#### **FUNCTIONAL BLOCK DIAGRAM**

2844 drw 01

BiCEMOS, CEMOS, CacheRAM and Double-Density are trademarks of Integrated Device Technology, Inc. Intel, 485Turbocache and i486 are trademarks of Intel Corp.

COMMERCIAL TEMPERATURE RANGE

**APRIL 1992**

DSC-7100/-

@1992 Integrated Device Technology, Inc.

1-37-1

### PIN CONFIGURATION(1)

| GND         | A1 e  |   | A2         | RESET       |      |       | <del>CS</del> | A4  | • | • | <b>A</b> 5 | GND              |

|-------------|-------|---|------------|-------------|------|-------|---------------|-----|---|---|------------|------------------|

| CLK         | B1 e  | • | B2         | M/ĪŌ        |      |       | CRDY          | B4  | • | • | B5         | CKEN             |

| RESV        | C1 (  | • | C2         | FLUSH       |      | ਟ     | BRDY          | C4  | • | • | C5         | BRDYO            |

| BLAST       | D1 (  | • | D2         | EADS        |      |       | Vcc           | D4  | • | • | D5         | SKEN             |

| BOFF        | E1 (  | • | E2         | <b>V</b> cc |      |       | WP            | E4  | • | • | E5         | START            |

| ADS         | F1 e  | • | F2         | W/R         |      |       | Do            | F4  | • | • | F5         | GND              |

| GND         | G1 (  |   | G2         | NC (2)      |      |       | D2            | G4  | • | • | G5         | D <sub>1</sub>   |

| BE₀         | H1 e  | • | H2         | BE₁         |      |       | GND           | H4  | • | • | H5         | D3               |

| BE₂         | i1 e  | • | 12         | BE₃         |      |       | D5            | 14  | • | • | 15         | D4               |

| <b>A</b> 2  | J1 6  | • | J2         | GND         |      |       | D7            | J4  | • | • | J5         | D6               |

| Vcc         | K1 (  | • | K2         | Аз          |      |       | Dв            | K4  | • | • | K5         | GND              |

| A4          | L1 (  | • | L2         | <b>A</b> 5  |      |       | D10           | L4  | • | • | L5         | D9               |

| <b>A</b> 6  | M1 (  | • | M2         | <b>A</b> 7  |      |       | Vcc           | M4  | • | • | M5         | D11              |

| <b>A</b> 9  | N1 (  | • | N2         | <b>A</b> 8  |      |       | D13           | N4  | • | • | N5         | D12              |

| <b>A</b> 10 | 01 (  | • | 02         | <b>V</b> cc |      |       | D15           | 04  | • | • | O5         | D14              |

| GND         | P1 (  | • | P2         | <b>A</b> 11 |      |       | DPo           | P4  | • | • | P5         | GND              |

| <b>A</b> 31 | Q1 e  | • | Q2         | <b>A</b> 12 |      |       | D16           | Q4  | • | • | Q5         | DP1              |

| A14         | R1 e  | • | R2         | <b>A</b> 13 |      |       | GND           | R4  | • | • | R5         | D <del>1</del> 7 |

| A15         | S1 (  | • | S2         | GND         |      |       | D19           | S4  | • | • | S5         | D18              |

| <b>A</b> 17 | T1 (  | • | T2         | <b>A</b> 16 |      |       | D21           | T4  | • | • | T5         | D20              |

| A19         | U1 (  | • | U2         | <b>A</b> 18 |      |       | D22           | U4  | • | • | U5         | Vcc              |

| Vcc         | V1 (  | • | V2         | <b>A</b> 20 |      |       | D24           | V4  | • | • | V5         | D23              |

| <b>A</b> 22 | W1 €  | • | W2         | <b>A</b> 21 |      |       | GND           | W4  | • | • | W5         | D25              |

| A23         | X1 e  | • | X2         | Vcc         |      |       | D27           | X4  | • | • | X5         | D26              |

| A25         | Y1 (  | • | Y2         | <b>A</b> 24 |      |       | D29           | Y4  | • | • | Y5         | D28              |

| <b>A</b> 27 | Z1 (  | • | <b>Z</b> 2 | <b>A</b> 26 |      |       | <b>D</b> 30   | Z4  | • | • | <b>Z</b> 5 | D31              |

| <b>A</b> 29 | AA1 e | • | AA2        | <b>A</b> 28 |      |       | DP2           | AA4 | • | • | AA5        | DРэ              |

| GND         | BB1 ( | • | BB2        | <b>A</b> 30 | PRSN | ВВЗ 🕳 | Vcc           | BB4 | • | • | BB5        | GND              |

| -           |       |   |            |             |      |       |               |     |   |   |            |                  |

|             |       |   |            |             |      |       |               |     |   |   |            |                  |

NOTE:

QIP TOP VIEW

2844 drw 02

1.Pin G2 is WPSTRP on the Intel 485Turbocache. This signal is not used by the IDT7MB6091 and is N.C. (No Connect).

#### **PIN NAMES**

| Symbol | Parameter            | Туре   | Active | Description                                                                                                                                                                                                  |

|--------|----------------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK    | CLOCK                | Input  | N/A    | This input is the timing reference for all of the IDT7MB6091's functions. It is the same as the i486 CLK input.                                                                                              |

| RESET  | RESET CACHE          | Input  | High   | A synchronous positive-true reset input, which invalidates all cache locations and resets the cache control logic.                                                                                           |

| ADS    | ADDRESS STROBE       | Input  | Low    | ADS is connected to the ADS# pin of the i486 CPU. It is used by the IDT7MB6091 to start any read or write cycle. $\overline{\text{CS}}$ must be asserted for $\overline{\text{ADS}}$ to be recognized.       |

| M/IO   | MEMORY/IO            | Input  | N/A    | This pin is used by the i486 to indicate whether the current cycle is a memory or I/O cycle. I/O cycles are not cacheable by the IDT7MB6091.                                                                 |

| W/R    | WRITE/READ           | Input  | N/A    | Write cycles are indicated by a high level on this pin, and read cycles are indicated by a low level.                                                                                                        |

| START  | MEMORY START         | Output | Low    | During a cache read miss cycle or a write cycle, the START pin signals that the main memory system should service the current access.                                                                        |

| BRDYO  | BURST READY OUT      | Output | Low    | This the IDT7MB6091's means of signaling to the i486 that cache data is ready to be sampled.                                                                                                                 |

| CBRDY  | CACHE BURST READY IN | Input  | Low    | This is the system input to the IDT7MB6091 to let the cache know that a main memory cache word is ready to be sampled by the CPU and the IDT7MB6091 during a burst access.                                   |

| CRDY   | CACHE READY IN       | Input  | Low    | CRDY signals to the IDT7MB6091 and the i486 that the main memory data is valid during a non-burst access. Another ADS must be generated by the CPU to fetch other words of that cache line from main memory. |

2844 tbl 01

| BLAST   | BURST LAST             | Input  | Low  | This i486 output indicates to the IDT7MB6091 cache control logic that the current cycle is the last cycle of a cache burst.                                                                                                                |

|---------|------------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOFF    | BACKOFF                | Input  | Low  | This signal is used to stall the IDT7MB6091. The IDT7MB6091 will also put its data bus into a high-impedance state. The IDT7MB6091 will only recognize invalidation cycles when BOFF is asserted.                                          |

| PRSN    | PRESENCE               | Output | Low  | This pin is hardwired to ground. It tells the system logic that the IDT7MB6091 is plugged into the system.                                                                                                                                 |

| A2-A31  | PROCESSOR ADDRESSES    | Input  | N/A  | These are the address inputs to the IDT7MB6091.                                                                                                                                                                                            |

| BEo-BE  | BYTE ENABLE            | Input  | Low  | The byte enable inputs are sampled only during CPU write cycles and are only used to control byte writes to valid cache lines during write hit cycles. The timing is the same as for the address input pins.                               |

| CS      | CHIP SELECT            | Input  | Low  | Chip select can be used for depth expansion. CS must be low for EADS or ADS to be recognized by the IDT7MB6091.                                                                                                                            |

| Do-D31  | PROCESSOR DATA LINES   | 1/0    | N/A  | These are the data inputs from either the i486 or the system memory. Do-<br>D7 define the least significant byte while D24-D31 define the most signifi-<br>cant byte.                                                                      |

| DP0-DP3 | DATA PARITY            | 1/0    | N/A  | These are the parity bits from either the i486 or the system memory. The timing requirements are the same as the data lines.                                                                                                               |

| CKEN    | CACHE ENABLE TO CPU    | Output | Low  | This signal is the cache enable signal generated by the IDT7MB6091. The IDT7MB6091 will always assert CKEN during T1 cycles and during read hit cycles before the last BRDYO. The IDT7MB6091 will not assert CKEN during read miss cycles. |

| SKEN    | SYSTEM CACHE ENABLE    | Input  | Low  | This signal is generated by the system to indicate that a line is cacheable. The IDT7MB6091 will look for SKEN to be active during the cycle before the first word transfer and the cycle before the last word transfer of a line fill.    |

| FLUSH   | FLUSH CACHE            | Input  | Low  | This signal causes the IDT7MB6091 to invalidate its entire cache contents.                                                                                                                                                                 |

| WP      | WRITE PROTECT          | input  | High | The write protect input is only sampled during write cycles. If this signal is asserted during a write hit cycle, the current cache data will not be overwritten.                                                                          |

| WPSTRP  | WRITE PROTECT STRAP    | N/A    | N/A  | This signal is not used by the IDT7MB6091.                                                                                                                                                                                                 |

| EADS    | VALID EXTERNAL ADDRESS | Input  | Low  | This signal indicates that an invalidation address is present on the IDT7MB6091 address bus. CS must be low for EADS to be recognized by the IDT7MB6091.                                                                                   |

#### FUNCTIONAL DESCRIPTION:

#### BASIC OPERATION

The IDT7MB6091 is a complete secondary cache subsystem designed to replace the Intel Turbocache485. The IDT7MB6091 is designed to support zero wait state line reads, i.e. four words of data in five clocks. The IDT7MB6091 supports all of the following bus cycles: read hit, read miss, write hit, write miss, invalidation and backoff. The IDT7MB6091 also features single pin reset and cache flush capabilities.

The IDT7MB6091 latches the address at the input of the module at the beginning of any read, write or invalidation cycle. The address remains latched for one cycle after the initiation of a read or write, and the address remains latched for two cycles after the initiation of an invalidation.

#### RESET

The IDT7MB6091 is reset when RESET is asserted. Asserting RESET will invalidate the entire contents of the cache, and reset the control logic of the cache. The cache will be reset regardless of the state of other control signals when RESET is asserted.

#### FLUSH

The entire cache contents of the IDT7MB6091 is invalidated when the FLUSH input is asserted. The cache will be invalidated regardless of the state of other control signals when FLUSH is asserted. FLUSH will not reset the state of the cache control logic.

#### READ

The IDT7MB6091 recognizes the initiation of a read cycle when both  $\overline{ADS}$  and  $\overline{CS}$  are sampled low with  $M/\overline{O}$  high and  $W/\overline{R}$  low. As soon as the address is valid at the input of the module, the IDT7MB6091 begins its tag look-up. If the input address is not contained in the cache, then a miss has occurred and the IDT7MB6091 will wait for the main memory system to service the current access. If the input address is present in the cache, then a hit has occurred and the IDT7MB6091 will burst back a line of data to the CPU.

If a read miss occurs the IDT7MB6091 asserts START in the first T2 cycle and then waits for the memory system to provide data. The IDT7MB6091 will consider the data returned from the memory system as cacheable if SKEN is sampled low at least one cycle before CBRDY or CRDY is first

asserted. The IDT7MB6091 will load the data word returned from the memory system into the cache each time  $\overline{CBRDY}$  or  $\overline{CRDY}$  is sampled low. However, the IDT7MB6091 will only validate the line of data returned from the memory system if  $\overline{SKEN}$  is sampled low the cycle before the last data word is transferred from the memory system, i.e. the fourth time that  $\overline{CBRDY}$  or  $\overline{CRDY}$  is sampled low. The line fill is aborted if  $\overline{BLAST}$  is sampled low concurrent with  $\overline{CBRDY}$  or  $\overline{CRDY}$  being sampled low prior to the last data word transfer.

The IDT7MB6091 will consider the data returned as non-cacheable if CBRDY or CRDY is sampled low before or concurrently with SKEN. Therefore, to avoid a potential performance penalty, SKEN should not be asserted prior to CBRDY or CRDY if the data is considered non-cacheable, since the IDT7MB6091 will invalidate a line of data if SKEN is sampled low before CBRDY or CRDY is sampled low during a read miss.

The IDT7MB6091 requires that the read miss address (i.e. the address that was valid at the beginning of the read cycle) is present when SKEN is sampled low at the beginning of a line fill and again when SKEN is sampled at the end of a line fill. The address must be valid because it is latched at these times to invalidate a line at the beginning of the fill and then to validate the line at the end of the line fill. When the address is latched at the end of the line fill, it will remain latched until the last data word of the line is written to the cache.

If the IDT7MB6091 detects that the input address is contained in the cache, the IDT7MB6091 will supply data to the CPU. The IDT7MB6091 starts bursting data back to the CPU in the first T2 cycle. The IDT7MB6091 then transfers a new data word in each subsequent T2 cycle until BLAST is asserted to the cache. The IDT7MB6091 also forces START high and BRDYO low in the first T2 cycle. ČKEN is asserted during the T1 cycle and again in the second and subsequent T2 cycles during a read hit.

#### WRITE

The IDT7MB6091 recognizes the initiation of a write cycle

when both  $\overline{ADS}$  and  $\overline{CS}$  are sampled low with  $M/\overline{IO}$  high and  $W/\overline{R}$  high. As soon as the address is valid at the input of the module, the IDT7MB6091 begins its tag look-up. If the input address is contained in the cache then a write hit has occurred, and the cache contents are updated in the first T2 cycle if the WP input is low. If the WP input is high during a write hit, the line is seen as write protected and the write is ignored. If the input address is not contained in the cache then a write miss has occurred, the IDT7MB6091 ignores the write and the cache contents are not updated.

#### INVALIDATION

An invalidation is initiated by the simultaneous assertion of EADS and CS. If EADS and ADS are asserted simultaneously. ADS is ignored since invalidations have priority. At the initiation of an invalidation, the IDT7MB6091 begins its tag look-up. If the line is found in the cache, the line will be invalidated. The IDT7MB6091 requires two cycles after the assertion of EADS to invalidate a line; therefore, invalidations can only occur every third cycle. The IDT7MB6091 ignores invalidations only if an address is currently latched in the address latch. Therefore, the IDT7MB6091 ignores invalidations at the following times: the cycle after the initiation of a read or write cycle, the cycle after SKEN is first sampled low during a line fill, the cycle(s) after sampling SKEN low concurrent with (or after) the third word transfer and prior to the fourth word transfer of a line fill, and the two cycles following a previous invalidation.

#### **BACKOFF**

A cache backoff is initiated by the assertion of BOFF. BOFF interrupts any other cache cycle that the IDT7MB6091 is servicing. The cycle after BOFF is sampled low, the IDT7MB6091 will float its data bus, and the output control signals are driven to their idle levels, i.e. CKEN low, START high and BRDYO high. When BOFF is asserted, the IDT7MB6091 ignores all cache cycles except for invalidations; however, the IDT7MB6091 will still recognize the assertion of RESET or FLUSH when BOFF is asserted.

#### ABSOLUTE MAXIMUM RATINGS

| Symbol | Rating                               | Value        | Unit |

|--------|--------------------------------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | ٧    |

| TA     | Operating Temperature                | 0 to +70     | °C   |

| Teias  | Temperature Under Bias               | -10 to +85   | ∘c   |

| Тѕтс   | Storage Temperature                  | -55 to +125  | °C   |

| lout   | DC Output Current                    | 50           | mΑ   |

NOTE:

NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## RECOMMENDED DC OPERATING CONDITIONS

| Symbol | Parameter         | Min.    | Тур. | Max. | Unit |

|--------|-------------------|---------|------|------|------|

| Vcc    | Supply Voltage    | 4.75    | 5.0  | 5.25 | >    |

| GND    | Supply Voltage    | 0       | 0    | 0.0  | ٧    |

| ViH    | Input High Votage | 2.2     |      | 6.0  | ٧    |

| VIL    | Input Low Voltage | -0.5(1) | _    | 0.8  | ٧    |

NOTE:

1. VIL = -3.0V for pulse width less than 5ns.

2844 tbl 04

## RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Ambient Temperature | GND | Vcc       |

|------------|---------------------|-----|-----------|

| Commercial | 0°C to +70°C        | οV  | 5.0V ± 5% |

2844 tbl 05

4

#### DC ELECTRICAL CHARACTERISTICS

$(Vcc = 5.0V \pm 5\%, TA = 0^{\circ}C \text{ to } 70^{\circ}C)$

| Symbol | Parameter                                           | Test Condition                                  | Min. | Max. | Unit |

|--------|-----------------------------------------------------|-------------------------------------------------|------|------|------|

| lu     | Input Leakage Current<br>(A2 - A3)                  | Vcc = Max, Vin = GND to Vcc                     | _    | 30   | μА   |

| llul   | Input Leakage Current<br>(Data, A2 - A3, BEo - BE3) | Vcc = Max, Vin = GND to Vcc                     | -    | 10   | μΑ   |

| Ital   | Input Leakage Current<br>(CLK, ADS)                 | Vcc = Max, ViN = GND to Vcc                     | _    | 50   | μА   |

| [liH]  | Input High Current (Control)                        | Vcc = Max, Vin = Vcc                            | _    | 1.0  | mA   |

| liul   | Input Low Current (Control)                         | Vcc = Max, Vin = GND                            | -    | 260  | μA   |

| lLO    | Output Leakage Current                              | Vout = 0V to Vcc, Vcc = Max.                    | -    | 10   | μΑ   |

| Vold   | Output Low Voltage (Data)                           | 1oL = 8mA, Vcc = Min.                           | _    | 0.4  | ٧    |

| Volc   | Output Low Voltage (Control)                        | loL = 12mA, Vcc = Min.                          |      | 0.5  | V    |

| Vohd   | Output High Voltage (Data)                          | loн = -4mA, Vcc = Min.                          | 2.4  |      | ٧    |

| Vонс   | Output High Voltage (Control)                       | loн = -2mA, Vcc = Min.                          | 2.4  |      | V    |

| lcc    | Operating Power Supply Current                      | Vcc = Max., CS ≤ ViL,<br>f = fмax, Outputs Open |      | 1900 | mA   |

2844 tbl 06

#### CAPACITANCE(1)

$(TA = +25^{\circ}C, f = 1.0 \text{ MHz})$

| Symbol | Parameter <sup>(1)</sup>                     | Condition | Max. | Unit |

|--------|----------------------------------------------|-----------|------|------|

| CIN    | Input Capacitance                            | VIN == OV | 35   | pF   |

|        | (A2 - A3)                                    | _         |      |      |

| Cin    | Input Capacitance<br>(Data, A2 - 3, BEo - 3) | VIN = 0V  | 15   | рF   |

| CIN    | Input Capacitance<br>(Control)               | VIN = 0V  | 25   | pF   |

| Cin    | Input Capacitance<br>( ADS, CLK)             | VIN = 0V  | 45   | pF   |

| Соит   | Output Capacitance<br>(BRDYO)                | VIN = 0V  | 40   | pF   |

| Соит   | Output Capacitance<br>(START, SKEN)          | Vin = 0V  | 15   | pF   |

| Ci/O   | Data I/O Capacitance                         | Vout = 0V | 10   | ρF   |

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise/Fall Times         | 5ns               |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

| Output Load                   | See Figures 1 & 2 |

2844 tbl 08

NOTE:

1. These parameters are guaranteed by design but not tested.

2844 tbi 07

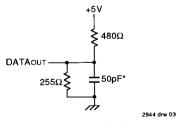

Figure 1. Output Load

Figure 2. Output Load (for tonz, tchz, tolz and tclz)

\*including scope and jig

2844 drw 04

#### **AC ELECTRICAL CHARACTERISTICS**

$(VCC = 5.0V \pm 5\%, TA = 0^{\circ} to +70^{\circ}C)$

|             |                                  | 7MB6091SxxK |          |      |      |      |

|-------------|----------------------------------|-------------|----------|------|------|------|

|             |                                  | 33 M        | lHz      | 25 N | 1Hz  |      |

| Symbol      | Name                             | Min.        | Max.     | Min. | Max. | Unit |

| t1          | Clock Period                     | 30          |          | 40   |      | ns   |

| t2          | Clock High Time                  | 11          |          | 14   |      | ns   |

| <b>t</b> 3  | Clock Low Time                   | 11          |          | 14   | _    | ns   |

| t4          | A2-A31, BED-BE3 Setup Time       | 13          |          | 17   |      | ns   |

| t5          | A2-A31, BE0-BE3 Hold Time        | 10          |          | 10   |      | ns   |

| <b>t</b> 6  | A4-A31 Line Fill Setup Time      | 5           |          | 5    |      | ns   |

| <b>t</b> 7  | ADS, M/IO, W/R Setup Time        | 13          |          | 20   |      | ns   |

| <b>t</b> 8  | ADS, M/ĪO, W/R Hold Time         | 3           |          | 3    |      | ns   |

| <b>t</b> 9  | BLAST Setup Time                 | 9           | <u> </u> | 10   |      | ns   |

| <b>t</b> 10 | BLAST Hold Time                  | 3           |          | 3    |      | ns   |

| <b>t</b> 11 | CRDY, CBRDY Setup Time           | 11          |          | 11   |      | ns   |

| <b>t</b> 12 | CRDY, CBRDY Hold Time            | 3           |          | 3    |      | ns   |

| t13         | SKEN Setup Time                  | 9           | _        | 9    |      | ns   |

| t14         | SKEN Hold Time                   | 3           | _        | 3    |      | ns   |

| t15         | Do-D31, DPo-DP3 Setup Time       | 5           | _        | 5    |      | ns   |

| t16         | Do-D31, DPo-DP3 Hold Time        | 3           | _        | 3    |      | ns   |

| <b>t</b> 17 | EADS Setup Time                  | 9           | <b>—</b> | 9    |      | ns   |

| t18         | EADS Hold Time                   | 3           | _        | 3    |      | ns   |

| t19         | A4-A31 Setup Time (Snoop)        | 6           | _        | 6    | _    | ns   |

| t20         | A4-A31 Hold Time (Snoop)         | 10          | _        | 10   |      | ns   |

| <b>t</b> 21 | RESET, FLUSH Setup Time          | 9           |          | 9    |      | ns   |

| t22         | RESET, FLUSH Hold Time           | 3           |          | 3    |      | ns   |

| t23         | RESET, FLUSH Pulse Width         | 80          |          | 80   |      | ns   |

| t24         | BRDYO Valid                      |             | 16       |      | 22   | ns   |

| t25         | ČKEN Valid                       | _           | 15       |      | 18   | ns   |

| <b>t</b> 26 | START Valid                      |             | 16       |      | 22   | ns   |

| <b>t</b> 27 | Do-D31, DPo-DP3 Valid (Read Hit) |             | 24       |      | 30   | ns   |

| <b>t</b> 28 | WP Setup Time                    | 15          | _        | 15   | _    | ns   |

| t29         | WP Hold Time                     |             | 3        | _    | 3    | ns   |

| t30         | BOFF Setup Time                  | 9           | _        | 10   |      | ns   |

| t31         | BOFF Hold Time                   | 3           | _        | 3    |      | ns   |

NOTE:

1. The address, M/TO and W/R inputs to the IDT7MB6091 must be held valid for the duration of the read, write or invalidation cycle.

2844 tbl 09

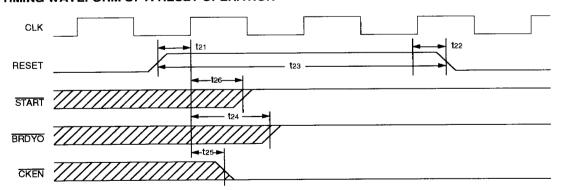

#### TIMING WAVEFORM OF A RESET OPERATION

2844 drw 06

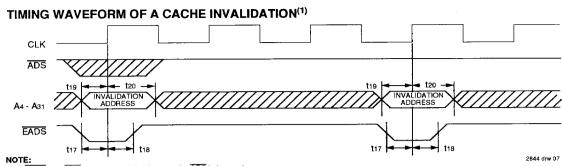

If EADS and ADS are asserted simultaneously, ADS is ignored.

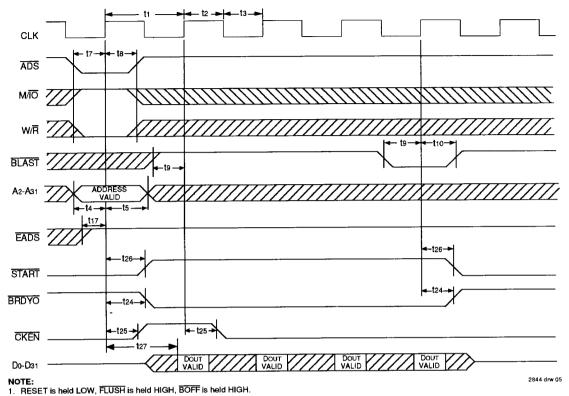

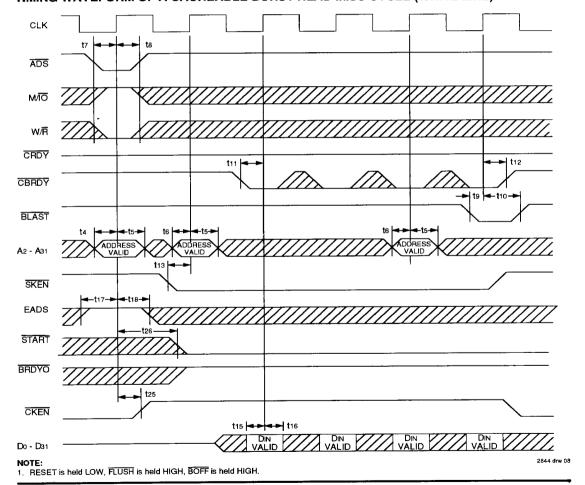

## TIMING WAVEFORM OF A CACHEABLE BURST READ MISS CYCLE (WRITE LINE)(1)

1-37-8

1. RESET is held LOW, FLUSH is held HIGH, BOFF is held HIGH.

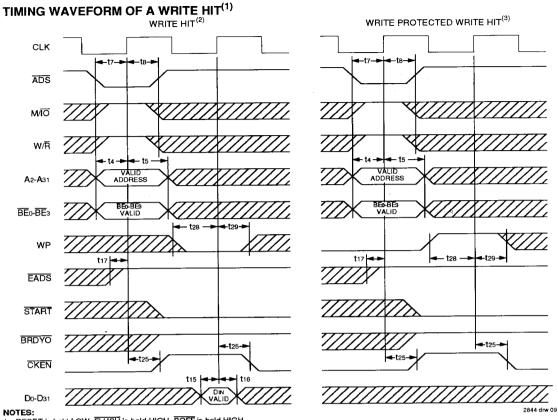

- 2. For a write hit, data in the IDT7MB6091 is updated.

- 3. For a write protected write hit, the data in the IDT7MB6091 is not updated.

# TIMING WAVEFORM OF A BACKOFF OPERATION CLK **t**30 **BOFF** 2844 drw 10

9

#### **PACKAGE DIMENSIONS**

2844 drw 11