# silicon systems\*

# SSI 34P570 2-Channel Floppy Disk Read/Write Device

July, 1990

### DESCRIPTION

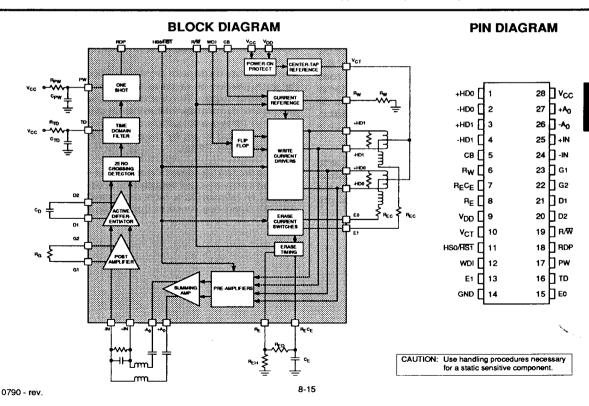

The SSI 34P570 is an integrated circuit which performs the functions of generating write signals, amplifying and processing read signals required for a double-sided floppy disk drive. The write data circuitry includes switching differential current drivers and the erase head drive with programmable delay and hold times. The read data circuitry includes low noise amplifiers for each channel as well as a programmable gain stage and necessary equalization and filtering capability using external passive components. All logic inputs and outputs are TTL compatible and all timing is externally programmable for maximum design flexibility. The circuit operates on +12 volt and +5 volt power supplies and is available in 28-pin plastic DIP and PLCC packages.

## **FEATURES**

- Single-chip read/write amplifier and read data processing function

- Compatible with 8", 5 1/4" and 3 1/2" drives

- Internal write and erase current sources, externally set

- Control signals are TTL compatible

- Schmitt trigger inputs for higher noise immunity on bussed control signals

- TTL selectable write current boost

- Operates on +12 volt and +5 volt power supplies

- High gain, low noise, low peak shift (0.3% typical) read processing circuits

Powered by ICminer.com Electronic-Library Service CopyRight 2003

#### **FUNCTIONAL DESCRIPTION**

#### WRITE MODE CIRCUITRY

In Write Mode (R/W low), the circuit provides controlled write and erase currents to either of two magnetic heads. The write-erase circuitry consists of two differential write current drivers, a center tap voltage reference, two erase current switches and control circuits for head selection and erase timing.

Write current is toggled between opposing sides of the head on each negative transition of the write data input (WDI) and is set externally by a single resistor, Rw connected between the Rw terminal and ground. Since driver output impedance is large, proper damping resistors must be provided across each head. A signal at the CB terminal provides write current boost.

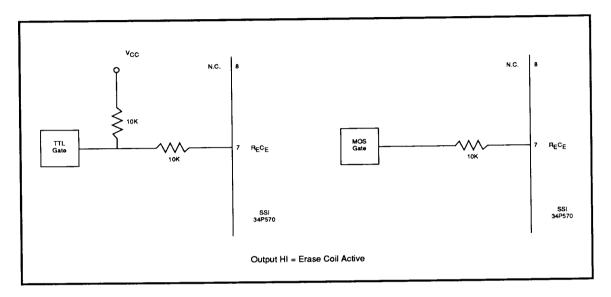

Erase current is also set externally through resistors REC connected in series with each erase coil. Erase can be activated by, but delayed from, selection of the write mode, and is held active after mode deselection. The turn-on delay is determined by the charging of CE through RED, while the hold time is determined by the discharge of CE through the series combination of RED and REH(see connection diagram). The RECE node may be driven directly by a logic gate, with external resistors per Figure 4, if the erase period is to be controlled separately from the write mode selection. For applications where no delays are required, CE is omitted.

The Center Tap Voltage Reference supplies both write and erase currents. A power turn-on protection circuit prevents undesired writing or erasure by holding the voltage reference off until the supply voltages are within their operating ranges.

#### READ MODE CIRCUITRY

In the Read Mode (R/W high), the circuit performs the functions of amplifying and detecting the selected head output pulses which correspond to magnetic transitions in the media. The read circuitry consists of two differential preamplifiers, a summing amplifier, a postamplifier, an active differentiator, a zero-crossing detector, a time domain filter, and an output one-shot.

The selected preamplifier drives the summing amplifier whose outputs are AC coupled to the postamplifier through an external filter network. The postamplifier adjusts signal amplitudes prior to application of signals to the active differentiator. Postamplifier gain is set as required by connecting a resistor across the gain terminals, G1 and G2. If desired, an additional frequency/phase compensation network may also be connected across these gain terminals.

The differentiator, driven by the postamplifier, provides zero-crossing output voltages in response to input signal peaks. Differentiator response characteristics are set by an external capacitor or more complex series network connected between the D1 and D2 terminals.

The zero-crossing detector provides a unipolar output for each positive or negative zero-crossing of the differentiator output. To enhance signal peak detection the time domain filter inhibits the detection of zero-crossings if they are not sufficiently separated in time. The filter period is set by an external RC network connected to the TD pin.

The time domain filter drives the output one-shot which generates uniform output data pulses. The pulse width is set by an external RC network connected to the PW pin. The output one-shot is inhibited while in the write mode.

8-16

**ELECTRICAL CHARACTERISTIC** Unless otherwise specified, 4.75 V  $\leq$ Vcc  $\leq$ 5.25 V; 11.4 V  $\leq$ VDD $\leq$ 12.6; 0°C $\leq$ Ta $\leq$ 70°C; Rw = 430  $\Omega$ ; Red = 62 k $\Omega$ ; Ce = 0.012  $\mu$ F; Reh = 62 k $\Omega$ ; Rec = 220  $\Omega$

## ABSOLUTE MAXIMUM RATINGS (Operating above absolute maximum ratings may damage the device.)

| PARAMETER                             | RATING          | UNIT |

|---------------------------------------|-----------------|------|

| 5 V Supply Voltage, Vcc               | 7               | V    |

| 12 V Supply Voltage, Vpp              | 14              | V    |

| Storage Temperature                   | 65 to +130      | °C   |

| Junction Operating Temperature        | 130             | °C   |

| Logic Input Voltage                   | -0.5 V to 7.0 V | dc   |

| Lead Temperature (Soldering, 10 sec.) | 260             | °C   |

| Power Dissipation                     | 800             | mW   |

#### **POWER SUPPLY CURRENTS**

| PARAMETER                 | CONDITIONS                                       | MIN | МОМ | MAX | UNIT |

|---------------------------|--------------------------------------------------|-----|-----|-----|------|

| Icc - 5 V Supply Current  | Read Mode                                        |     |     | 35  | mA   |

|                           | Write Mode                                       |     |     | 38  | mA   |

| loo - 12 V Supply Current | Read Mode                                        |     |     | 26  | mA   |

|                           | Write Mode (excluding<br>Write & Erase currents) |     |     | 24  | mA   |

## LOGIC SIGNALS - READ/WRITE (R/W), CURRENT BOOST (CB)

| PARAMETER                | CONDITIONS  | MIN | МОМ | MAX  | UNIT |

|--------------------------|-------------|-----|-----|------|------|

| Input Low Voltage (VIL)  |             |     |     | 0.8  | ٧    |

| Input Low Current (IIL)  | VIL = 0.4 V |     |     | -0.4 | mA   |

| Input High Voltage (Vін) |             | 2.0 |     |      | v    |

| Input High Current (Ін)  | VH = 2.4 V  |     |     | 20   | μА   |

0790 - rev. 8-17

## LOGIC SIGNALS - WRITE DATA INPUT (WDI), HEAD SELECT (HSO/HS1)

| PARAMETER                                   | CONDITIONS | MIN | NOM | MAX  | UNIT |

|---------------------------------------------|------------|-----|-----|------|------|

| Threshold Voltage, VT+<br>Positive - going  |            | 1.4 |     | 1.9  | ٧    |

| Threshold Voltage, VT -<br>Negative - going |            | 0.6 |     | 1.1  | ٧    |

| Hysteresis, VT + to VT-                     |            | 0.4 |     |      | V    |

| Input High Current, Ін                      | VIH = 2.4V |     |     | 20   | μА   |

| Input Low Current, IIL                      | ViL = 0.4V |     |     | -0.4 | mA   |

#### CENTER TAP VOLTAGE REFERENCE

| PARAMETER              | CONDITIONS               | MIN      | МОМ | MAX  | UNIT        |

|------------------------|--------------------------|----------|-----|------|-------------|

| Output Voltage (Vст)   | lwc + IE = 3 mA to 60 mA | VDD -1.5 |     | VDD5 | <b>v</b>    |

| Vcc Turn-Off Threshold | (See Note 1)             | 4.0      |     |      | ٧           |

| VDD Turn-Off Threshold | (See Note 1)             | 9.6      |     |      | ٧           |

| Vст Disabled Voltage   |                          |          |     | 1.0  | <b>&gt;</b> |

NOTE1: Voltage below which center tap voltage reference is disabled.

## **ERASE OUTPUTS (E1,E0)**

| PARAMETER                    | CONDITIONS        | MIN | NOM | MAX | UNIT |

|------------------------------|-------------------|-----|-----|-----|------|

| Unselected Head Leakage      | VEO, VE1 = 12.6 V |     |     | 100 | μА   |

| Output on Voltage (VE1, VE0) | IE = 50 mA        |     |     | 0.5 | ٧    |

#### WRITE CURRENT

| PARAMETER                       | CONDITIONS                                 | MIN      | МОМ | MAX      | UNIT |

|---------------------------------|--------------------------------------------|----------|-----|----------|------|

| Unselected Head Leakage         | VE1, VE0 = 12.6 V                          |          |     | 25       | μΑ   |

| Write Current Range             | Rw = 820 $\Omega$ to 180 $\Omega$          | 3        |     | 10       | mA   |

| Current Reference Accuracy      | lwc = 2.3/Rw<br>VcB(current boost) = 0.5 V | -5       |     | +5       | %    |

| Write Current Unbalance         | lwc = 3 mA to 10 mA                        |          |     | 1.0      | %    |

| Differential Head Voltage Swing | Δ lwc ≤ 5%                                 | 12.8     |     |          | Vpk  |

| Current Boost                   | VcB = 2.4 V                                | 1.25 lwc |     | 1.35 lwc |      |

#### **ERASE TIMING**

| PARAMETER                                              | CONDITIONS                                                                                             | MIN | МОМ | MAX | UNIT |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Erase Delay Range                                      | RED = 39 kΩ to 82 kΩ<br>CE= 0.0015 μF to 0.043 μF                                                      | 0.1 |     | 1.0 | msec |

| Erase Delay Accuracy  Δ <sup>T</sup> ED  TED           | TED = 0.69 RED CE RED = 39 kΩ to 82 kΩ; CE = 0.0015 μF to 0.043 μF                                     | -15 |     | +15 | %    |

| Erase Hold Range                                       | ReH + ReD = 78 kΩ to 164 kΩ;<br>CE = 0.0015 μF to 0.043 μF                                             | 0.2 |     | 2.0 | msec |

| Erase Hold Accuracy  Δ <sup>T</sup> EH <sup>T</sup> EH | Тен= 0.69 (Reн + Red) Се<br>Reн + Red = 78 k $\Omega$ to 164 k $\Omega$ ;<br>Ce= 0.0015 μF to 0.043 μF | -15 |     | +15 | %    |

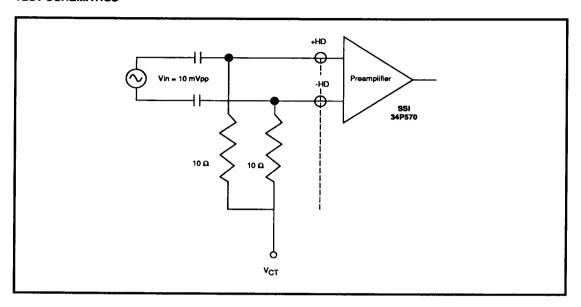

**ELECTRICAL CHARACTERISTICS** (Unless otherwise specified: Vin (Preamplifier) = 10 mVpp sine wave, dc coupled to center tap. (See Figure 1.) Summing Amplifier Load =  $2 \text{ k}\Omega$  line-line, ac coupled. Vin (Postamplifier) = 0.2 Vpp sine wave, ac coupled; Rg = open; Data Pulse Load =  $1 \text{ k}\Omega$  to Vcc; Cp = 240 pF; CTp = 100 pF; RTp =  $7.5 \text{ k}\Omega$ ; CPw = 47 pF; RPw=  $7.5 \text{ k}\Omega$ .)

#### **READ MODE**

#### **PREAMPLIFIER - SUMMING AMPLIFIER**

| PARAMETER                                      | CONDITIONS                                                                                 | MIN | МОМ | МАХ  | UNIT |

|------------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|------|------|

| Differential Voltage Gain                      | Freq. = 250 kHz                                                                            | 85  |     | 115  | V/V  |

| Bandwidth (-3 dB)                              |                                                                                            | 3   |     |      | MHz  |

| Gain Flatness                                  | Freq. = dc to 1.5 MHz                                                                      |     | -   | ±1.0 | dB   |

| Differential Input Impedance                   | Freq. = 250 kHz                                                                            | 20  |     |      | kΩ   |

| Max Differential Output<br>Voltage Swing       | Vın = 250 kHz sine wave,<br>THD ≤ 5%                                                       | 2.5 |     |      | Vpp  |

| Small Signal Differential<br>Output Resistance | lo ≤ 1.0 mApp                                                                              |     |     | 75   | Ω    |

| Common Mode Rejection Ratio                    | Vin = 300 mVpp<br>@ 500 kHz Inputs Shorted                                                 | 50  |     |      | dB   |

| Power Supply Rejection Ratio                   | $\Delta$ VDD = 300 mVpp @500 kHz Inputs shorted to VCT.                                    | 50  |     |      | dB   |

| Channel Isolation                              | Unselected Channel VIN<br>100 mVpp @ 500 kHz<br>Selected channel input<br>connected to Vct | 40  |     |      | dB   |

0790 - rev. 8-19

## PREAMPLIFIER - SUMMING AMPLIFIER (cont'd.)

| PARAMETER               | CONDITIONS                                        | MIN   | МОМ | MAX | UNIT  |

|-------------------------|---------------------------------------------------|-------|-----|-----|-------|

| Equivalent Input Noise  | Power BW = 10 kHz to 1 MHz Inputs shorted to VCT. |       |     | 10  | μVrms |

| Center Tap Voltage, Vст |                                                   | - 102 | 1.5 |     | ٧     |

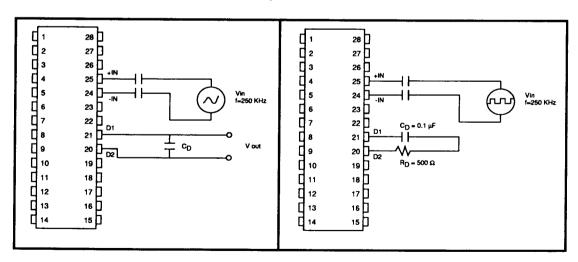

## POSTAMPLIFIER - ACTIVE DIFFERENTIATOR

| PARAMETER                                                      | CONDITIONS                                                                                                                                                                                                                                           | MIN | NOM | MAX  | UNIT       |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------------|

| Ao, Differential Voltage Gain<br>+ IN, -IN to D1, D2           | Freq. = 250 kHz<br>(See Figure 2)                                                                                                                                                                                                                    | 8.5 |     | 11.5 | V/V        |

| Bandwidth (-3 dB)<br>+ IN< -IN to D1, D2                       | $C_D = 0.1 \mu F$ , $R_D = 2.5 kΩ$                                                                                                                                                                                                                   | 3   |     |      | MHz        |

| Gain Flatness<br>+ IN, -IN to D1, D2                           | Freq. = dc to 1.5 MHz $C_D$ = 0.1 $\mu$ F, $R_D$ = 2.5 $k\Omega$                                                                                                                                                                                     |     |     | ±1.0 | dB         |

| Max Differential Output<br>Voltage Swing                       | VIN = 250 kHz sine wave,<br>ac coupled. ≤ 5% THD in<br>voltage across Cb.<br>(See Figure 2)                                                                                                                                                          | 5.0 |     |      | Vpp        |

| Max Differential Input Voltage                                 | VIN = 250 kHz sine wave,<br>ac coupled. $\leq$ 5% THD in<br>voltage across Cp.<br>RG = 1.5 k $\Omega$                                                                                                                                                | 2.5 |     |      | 2.5<br>Vpp |

| Differential Input Impedance                                   |                                                                                                                                                                                                                                                      | 10  |     |      | kΩ         |

| Gain Control Accuracy $\frac{\Delta^{A}R}{A_{R}} \times 100\%$ | An = AoRg/(8 x $10^3$ + Rg)<br>Rg = 2 k $\Omega$                                                                                                                                                                                                     | -25 |     | +25  | %          |

| Threshold Differential<br>Input Voltage. (See Note 2)          | Min differential input voltage at post amp that results in a change of state at RDP VIN = 250 kHz square wave, CD = 0.1 $\mu$ F, RD = 500 $\Omega$ , TR, TF $\leq$ 0.2 $\mu$ sec No overshoot; Data Pulse from each VIN . transition. (See Figure 3) |     |     | 3.7  | mVpp       |

| Peak Differentiator Network<br>Current                         |                                                                                                                                                                                                                                                      | 1.0 |     |      | mA         |

NOTE 2: Threshold Differential Input Voltage can be related to peak shift by the following formula:  $\frac{\text{Peak Shift}}{\pi \text{Vin}} \times 100\%$

where Vin = peak to peak input voltage at post amplifier. Note that this formula demonstrates an inverse relationship between the input amplitude and the Peak Shift.

## TIME DOMAIN FILTER

| PARAMETER                                                 | CONDITIONS                                                                                                                                                                                                             | MIN | МОМ | MAX  | UNIT |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Delay Accuracy $\frac{\Delta^{T}TD}{T_{TD}} \times 100\%$ | TTD = 0.58 RTD x (CTD + 10 <sup>-11</sup> ) +50 nsec, RTD = 5 kΩ, to 10 kΩ CTD ≥ 56 pF. VIN = 50 mVpp @ 250 kHz square wave, TR, TF ≤ 20 nsec, ac coupled. Delay measured from 50% input amplitude to 1.5 V Data Pulse | -15 |     | +15  | %    |

| Delay Range                                               | TTD = 0.58 RTD x (CTD + $10^{-11}$ ) + 50 nsec, RTD = 5 k $\Omega$ to 10 k $\Omega$ , CTD = 56 pF to 240 pF                                                                                                            | 240 |     | 2370 | ns   |

## DATA PULSE

| PARAMETER                       | CONDITIONS                                                                                                                                     | MIN | мом | MAX  | UNIT |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Width Accuracy  ATPW TPW x 100% | TPW = 0.58 RPW x (CPW +8 x 10 <sup>-12</sup> ) + 20 nsec.<br>RPW = 5 kΩ to 10 kΩ<br>CPW = $\geq$ 36 pF<br>width measured at 1.5V<br>amplitudes | -20 |     | +20  | %    |

| Active Level Output Voltage     | loн = 400 μA                                                                                                                                   | 2.7 |     |      | V    |

| Inactive Level Output Leakage   | loL =4 mA                                                                                                                                      |     |     | 0.5  | ٧    |

| Pulse Width                     | TPW = 0.58 RPW x (CPW +8 x10-12) + 20 nsec.<br>RPW = 5 kΩ to 10 kΩ<br>CPW = 36 pF to 200 pF                                                    | 145 |     | 1225 | ns   |

8-21

0790 - rev.

## **TEST SCHEMATICS**

FIGURE 1: Preamplifier Characteristics

FIGURE 2: Postamplifier Differential Output Voltage Swing and Voltage Gain

FIGURE 3:

Postamplifier Threshold Differential

Input Voltage

0790 - rev.

FIGURE 4: External Erase Control Connections

0790 - rev. 8-23

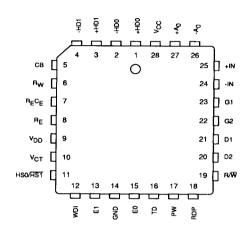

## PACKAGE PIN DESIGNATIONS

(TOP VIEW)

| THERMAL | CHARACTERISTICS: | Ø ja |

|---------|------------------|------|

|---------|------------------|------|

| 28-Pin | DIP  | 55°C/W |

|--------|------|--------|

| 28-Pin | PLCC | 65°C/W |

28-Pin PLCC

#### ORDERING INFORMATION

| PART DESCRIPTION       | ORDER NO.     | PKG. MARK |

|------------------------|---------------|-----------|

| SSI 34P570 28-Pin DIP  | SSI 34P570-CP | 34P570-CP |

| SSI 34P570 28-Pin PLCC | SSI 34P570-CH | 34P570-CH |

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680, (714) 731-7110, FAX: (714) 731-5457