### Freescale Semiconductor Product Brief

Document Number: MC56F8037PB Rev. 0, 09/2006

# 56F8037 Digital Signal Controller Product Brief

# 1 56F8037 Description

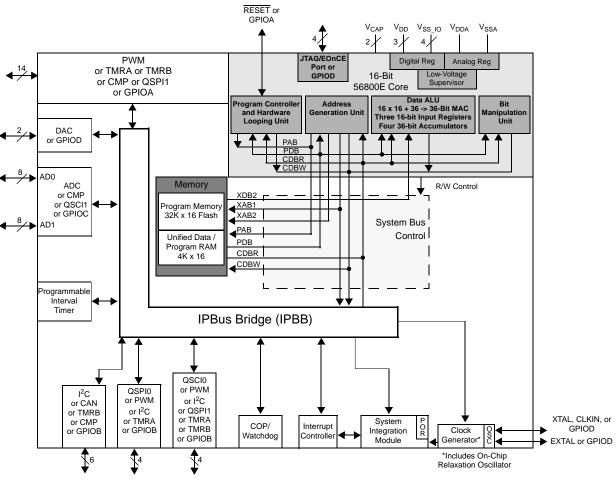

The 56F8037 is a member of the 56800E core-based family of Digital Signal Controllers (DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F8037 is well-suited for many applications. The 56F8037 includes many peripherals that are especially useful for industrial control, motion control, home appliances, general purpose inverters, smart sensors, fire and security systems, power management, and medical monitoring applications.

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

• Preliminary—Subject to Change Without Notice

### Contents

| 1 | 56F8037 Description              |

|---|----------------------------------|

| 2 | Digital Signal Controller Core   |

| 3 | Memory                           |

| 4 | Peripheral Circuits for 56F8037  |

| 5 | Recommended Operating Conditions |

| 6 | Product Documentation7           |

| 7 | 56F8037 Package and Pin-Out      |

| 8 | 56F8037 Mechanical Outline 10    |

### 56F8037 Description

The 56F8037 supports program execution from internal memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. The 56F8037 also offers up to 53 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F8037 Digital Signal Controller includes 64KB of Program Flash and 8KB of Unified Data/Program RAM. Program Flash memory can be independently bulk erased or erased in pages. Program Flash page erase size is 512 Bytes (256 Words).

A full set of programmable peripherals—PWM, ADCs, QSCIs, QSPIs, I2C, PITs, Quad Timers, DACs, and analog comparators—supports various applications. Each peripheral can be independently shut down to save power. Any pin in these peripherals can also be used as General Purpose Input/Outputs (GPIOs).

Figure 1. 56F8037 Block Diagram

### 2 Digital Signal Controller Core

- Efficient 16-bit 56800E family Digital Signal Controller (DSC) engine with dual Harvard architecture

- As many as 32 Million Instructions Per Second (MIPS) at 32MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

# 3 Memory

- Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security and protection that prevent unauthorized users from gaining access to the internal Flash

- On-chip memory:

- 64KB of Program Flash

- 8KB of Unified Data/Program RAM

- EEPROM emulation capability using Flash

## 4 Peripheral Circuits for 56F8037

- One multi-function six-output Pulse Width Modulator (PWM) module

- Up to 96MHz PWM operating clock

- 15 bits of resolution

- Center-aligned and Edge-aligned PWM signal mode

- Four programmable fault inputs with programmable digital filter

- Double-buffered PWM registers

### Peripheral Circuits for 56F8037

- Each complementary PWM signal pair allows selection of a PWM supply source from:

- PWM generator

- External GPIO

- Internal timers

- Analog comparator outputs

- ADC conversion result which compares with values of ADC high- and low-limit registers to set PWM output

- Two independent 12-bit Analog-to-Digital Converters (ADCs)

- 2 x 8 channel inputs

- Supports both simultaneous and sequential conversions

- ADC conversions can be synchronized by both PWM and timer modules

- Sampling rate up to 2.67MSPS

- 16-word result buffer registers

- ADC Smart Power Management (Auto-standby, auto-powerdown)

- Two 12-bit Digital-to-Analog Converters (DACs)

- 2 microsecond settling time when output swing from rail to rail

- Automatic waveform generation generates square, triangle and sawtooth waveforms with programmable period, update rate, and range

- Two 16-bit multi-purpose Quad Timer modules (TMRs)

- Up to 96MHz operating clock

- Eight independent 16-bit counter/timers with cascading capability

- Each timer has capture and compare capability

- Up to 12 operating modes

- Two Queued Serial Communication Interfaces (QSCIs) with LIN Slave functionality

- Full-duplex or single-wire operation

- Two receiver wake-up methods:

- Idle line

- Address mark

- Four-bytes-deep FIFOs are available on both transmitter and receiver

- Two Queued Serial Peripheral Interfaces (QSPIs)

- Full-duplex operation

- Master and slave modes

- Four-words-deep FIFOs available on both transmitter and receiver

- Programmable Length Transactions (2 to 16 bits)

- One Inter-Integrated Circuit (I<sup>2</sup>C) port

- Operates up to 400kbps

- Supports both master and slave operation

- Supports both 10-bit address mode and broadcasting mode

4

#### Peripheral Circuits for 56F8037

- One Freescale scalable controller area network (MSCAN) module

- Fully compliant with CAN protocol Version 2.0 A/B

- Supports standard and extended data frames

- Supports data rate up to 1Mbps

- Five receive buffers and three transmit buffers

- Three 16-bit Programmable Interval Timers (PITs)

- Two analog Comparators (CMPs)

- Selectable input source includes external pins, DACs

- Programmable output polarity

- Output can drive Timer input, PWM fault input, PWM source, external pin output and trigger ADCs

- Output falling and rising edge detection able to generate interrupts

- Computer Operating Properly (COP)/Watchdog timer capable of selecting different clock sources

- Up to 53 General-Purpose I/O (GPIO) pins with 5V tolerance

- Integrated Power-On Reset and Low-Voltage Interrupt Module

- Phase Lock Loop (PLL) provides a high-speed clock to the core and peripherals

- Clock Sources:

- On-chip relaxation oscillator

- External clock:

- Crystal oscillator

- Ceramic resonator

- External clock source

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- JTAG/EOnCE debug programming interface for real-time debugging

**Recommended Operating Conditions**

# 5 Recommended Operating Conditions

### Table 1. Recommended Operating Conditions

$(V_{REFL x} = 0V, V_{SSA} = 0V, V_{SS} = 0V)$

| Characteristic                                                                                                                                        | Symbol                               | Notes                              | Min                           | Тур | Max                                              | Unit   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------|-------------------------------|-----|--------------------------------------------------|--------|

| Supply voltage                                                                                                                                        | V <sub>DD,</sub><br>V <sub>DDA</sub> |                                    | 3                             | 3.3 | 3.6                                              | V      |

| ADC Reference Voltage High                                                                                                                            | V <sub>REFHx</sub>                   |                                    | 3.0                           |     | V <sub>DDA</sub>                                 | V      |

| Voltage difference $V_{DD\_IO}$ to $V_{DDA}$                                                                                                          | $\Delta V_{DD}$                      |                                    | -0.1                          | 0   | 0.1                                              | V      |

| Voltage difference $V_{\mbox{SS}\mbox{IO}}$ to $V_{\mbox{SSA}}$                                                                                       | $\Delta V_{SS}$                      |                                    | -0.3                          | 0   | 0.3                                              | V      |

| Device Clock Frequency<br>Using relaxation oscillator<br>Using external clock source                                                                  | FSYSCLK                              |                                    | 1<br>0                        |     | 32<br>32                                         | MHz    |

| Input Voltage High (digital inputs)                                                                                                                   | V <sub>IH</sub>                      | Pin Groups 1, 2                    | 2.0                           |     | 5.5                                              | V      |

| Input Voltage Low (digital inputs)                                                                                                                    | V <sub>IL</sub>                      | Pin Groups 1, 2                    | -0.3                          |     | 0.8                                              | V      |

| Oscillator Input Voltage High<br>XTAL not driven by an external clock<br>XTAL driven by an external clock source                                      | V <sub>IHOSC</sub>                   | Pin Group 5                        | V <sub>DDA</sub> - 0.8<br>2.0 |     | V <sub>DDA</sub> + 0.3<br>V <sub>DDA</sub> + 0.3 | V      |

| Oscillator Input Voltage Low                                                                                                                          | V <sub>ILOSC</sub>                   | Pin Group 5                        | -0.3                          |     | 0.8                                              | V      |

| Analog Input Voltage                                                                                                                                  | V <sub>IA</sub>                      | Pin Group 3                        | 0.0                           |     | V <sub>DDA</sub>                                 | V      |

| DAC Output Load Resistance                                                                                                                            | RLD                                  |                                    | ЗK                            |     | —                                                | ohms   |

| DAC Output Load Capacitance                                                                                                                           | CLD                                  |                                    | —                             |     | 400                                              | pF     |

| Output Source Current High at $V_{OH}$ min.) <sup>1</sup><br>When programmed for low drive strength<br>When programmed for high drive strength        | I <sub>ОН</sub>                      | Pin Group 1<br>Pin Group 1         |                               |     | -4<br>-8                                         | mA     |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>1</sup><br>When programmed for low drive strength<br>When programmed for high drive strength | I <sub>OL</sub>                      | Pin Groups 1, 2<br>Pin Groups 1, 2 |                               |     | 4<br>8                                           | mA     |

| Ambient Operating Temperature (Automotive)                                                                                                            | Τ <sub>Α</sub>                       |                                    | -40                           |     | 125                                              | °C     |

| Ambient Operating Temperature<br>(Extended Industrial)                                                                                                | Τ <sub>Α</sub>                       |                                    | -40                           |     | 105                                              | °C     |

| Flash Endurance<br>(Program Erase Cycles)                                                                                                             | N <sub>F</sub>                       | T <sub>A</sub> = -40°C to<br>125°C | 10,000                        |     | _                                                | cycles |

| Flash Data Retention                                                                                                                                  | Τ <sub>R</sub>                       | T <sub>J</sub> <= 70°C<br>average  | 15                            |     | —                                                | years  |

<sup>1</sup> Total chip source or sink current cannot exceed 75mA

# 6 **Product Documentation**

The documents listed in **Table 2** are required for a complete description and proper design with the 56F8037. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, Freescale Literature Distribution Centers, or online at: **http://www.freescale.com**

| Торіс                                                                                         | Description                                                                                                                 | Order Number |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

| DSP56800E<br>Reference Manual                                                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |              |  |  |

| 56F802X and 56F803X<br>Peripheral Reference<br>Manual                                         | Detailed description of peripherals of the 56F802x and 56F803x family of devices                                            | MC56F80XXRM  |  |  |

| 56F802X and 56F803X<br>Serial Bootloader User<br>Guide                                        | Detailed description of the Serial Bootloader in the 56F802x and 56F803x family of devices                                  | 56F80XXBLUG  |  |  |

| 56F8037<br>Technical Data Sheet                                                               | Electrical and timing specifications, pin descriptions, and package descriptions (this document)                            | MC56F8037    |  |  |

| 56F8037         Details any chip issues that might be present           Errata         Errata |                                                                                                                             | MC56F8037E   |  |  |

### Table 2. 56F8037 Chip Documentation

56F8037 Digital Signal Controller Product Brief, Rev. 0

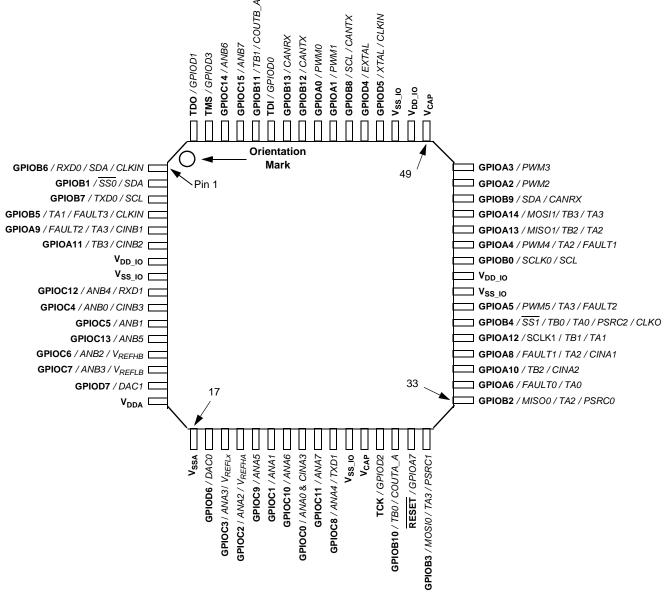

56F8037 Package and Pin-Out

Figure 2. Top View, 56F8037 64-Pin LQFP Package

Peripheral pins in bold identify the reset state in Table 3.

| Pin<br># | Signal Name                                | Pin<br># | Signal Name                                | Pin<br># | Signal Name                                        | Pin<br># | Signal Name                     |

|----------|--------------------------------------------|----------|--------------------------------------------|----------|----------------------------------------------------|----------|---------------------------------|

| 1        | <b>GPIOB6</b><br>RXD0 / SDA / CLKIN        | 17       | V <sub>SSA</sub>                           | 33       | <b>GPIOB2</b><br>MISO0 / TA2 / PSRC0               | 49       | V <sub>CAP</sub>                |

| 2        | GPIOB1<br>SS0 / SDA                        | 18       | GPIOD6<br>DAC0                             | 34       | <b>GPIOA6</b><br>FAULT0 / TA0                      | 50       | V <sub>DD_IO</sub>              |

| 3        | <b>GPIOB7</b><br>TXD0 / SCL                | 19       | <b>GPIOC3</b><br>ANA3 / V <sub>REFLA</sub> | 35       | <b>GPIOA10</b><br>TB2 / CINA2                      | 51       | V <sub>SS_IO</sub>              |

| 4        | <b>GPIOB5</b><br>TA1 / FAULT3 / CLKIN      | 20       | <b>GPIOC2</b><br>ANA2 / V <sub>REFHA</sub> | 36       | <b>GPIOA8</b><br>FAULT1 / TA2 / CINA1              | 52       | <b>GPIOD5</b><br>XTAL / CLKIN   |

| 5        | <b>GPIOA9</b><br>FAULT2 / TA3 / CINB1      | 21       | GPIOC9<br>ANA5                             | 37       | <b>GPIOA12</b><br>SCLK1 / TB1 / TA1                | 53       | <b>GPIOD4</b><br>EXTAL          |

| 6        | <b>GPIOA11</b><br>TB3 / CINB2              | 22       | GPIOC1<br>ANA1                             | 38       | <b>GPIOB4</b><br>SS1 / TB0 / TA0 /<br>PSRC2 / CLKO | 54       | <b>GPIOB8</b><br>SCL / CANTX    |

| 7        | VDD_IO                                     | 23       | GPIOC10<br>ANA6                            | 39       | <b>GPIOA5</b><br>PWM5 / TA3 / FAULT2               | 55       | <b>GPIOA1</b><br>PWM1           |

| 8        | VSS_IO                                     | 24       | GPIOC0<br>ANA0 & CINA3                     | 40       | V <sub>SS_IO</sub>                                 | 56       | <b>GPIOA0</b><br><i>PWM0</i>    |

| 9        | <b>GPIOC12</b><br>ANB4 / RXD1              | 25       | GPIOC11<br>ANA7                            | 41       | V <sub>DD_IO</sub>                                 | 57       | GPIOB12<br>CANTX                |

| 10       | GPIOC4<br>ANB0 & CINB3                     | 26       | <b>GPIOC8</b><br>ANA4 / TXD1               | 42       | <b>GPIOB0</b><br>SCLK0 / SCL                       | 58       | GPIOB13<br>CANRX                |

| 11       | GPIOC5<br>ANB1                             | 27       | V <sub>SS_IO</sub>                         | 43       | <b>GPIOA4</b><br><i>PWM4 / TA2 / FAULT1</i>        | 59       | <b>TDI</b><br>GPIOD0            |

| 12       | GPIOC13<br>ANB5                            | 28       | V <sub>CAP</sub>                           | 44       | <b>GPIOA13</b><br>MISO1 / TB2 / TA2                | 60       | <b>GPIOB11</b><br>TB1 / COUTB_A |

| 13       | <b>GPIOC6</b><br>ANB2 / V <sub>REFHB</sub> | 29       | TCK<br>GPIOD2                              | 45       | <b>GPIOA14</b><br>MOSI1 / TB3 / TA3                | 61       | GPIOC15<br>ANB7                 |

| 14       | <b>GPIOC7</b><br>ANB3 / V <sub>REFLB</sub> | 30       | <b>GPIOB10</b><br>TB0 / COUTA_A            | 46       | <b>GPIOB9</b><br>SDA / CANRX                       | 62       | GPIOC14<br>ANB6                 |

| 15       | <b>GPIOD7</b><br>DAC1                      | 31       | RESET<br>GPIOA7                            | 47       | GPIOA2<br>PWM2                                     | 63       | TMS<br>GPIOD3                   |

| 16       | V <sub>DDA</sub>                           | 32       | <b>GPIOB3</b><br>MOSI0 / TA3 /<br>PSRC1    | 48       | GPIOA3<br>PWM3                                     | 64       | <b>TDO</b><br>GPIOD1            |

56F8037 Digital Signal Controller Product Brief, Rev. 0

Freescale Semiconductor

56F8037 Mechanical Outline

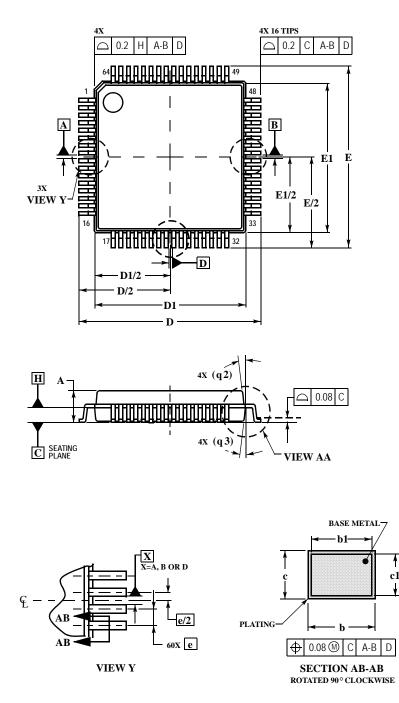

8 56F8037 Mechanical Outline

$(S) \rightarrow (Q) \rightarrow (Q)$

0.05 (\$

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

DATUM PLANE DATUM HIS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM

- OF THE PARTING LINE. 4. DATUMS A, B AND D TO BE DETERMINED AT DATUM DI ANE DATUM C

- DATUMS A, DAND D TO BE DETERMINED AT ST. PLANE DATUM C.

DIMENSIONS D AND E TO BE DETERMINED AT SEATING PLANE DATUM C.

- DIMENSIONS DANCE TO BE DE LERVINGED AT SEATING PLANE DATUM C.

DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 PER SIDE

- SIDE. 5. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE & DIMENSION TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   |             | 1.60 |  |  |

| A1  | 0.05        | 0.15 |  |  |

| A2  | 1.35        | 1.45 |  |  |

| b   | 0.17        | 0.27 |  |  |

| b1  | 0.17        | 0.23 |  |  |

| С   | 0.09        | 0.20 |  |  |

| c1  | 0.09        | 0.16 |  |  |

| D   | 12.00 BSC   |      |  |  |

| D1  | 10.00 BSC   |      |  |  |

| е   | 0.50 BSC    |      |  |  |

| E   | 12.00 BSC   |      |  |  |

| E1  | 10.00 BSC   |      |  |  |

| L   | 0.45        | 0.75 |  |  |

| L1  | 1.00        | REF  |  |  |

| L2  | 0.50        | REF  |  |  |

| R1  | 0.10        | 0.20 |  |  |

| S   | 0.20        | REF  |  |  |

| q   | 0 0         | 7 °  |  |  |

| q 1 | 00          |      |  |  |

| q 2 |             | REF  |  |  |

| q 3 | 12° REF     |      |  |  |

### Figure 3. 56F8037 64-Pin LQFP Mechanical Information

Please see www.freescale.com for the most current case outline.

56F8037 Digital Signal Controller Product Brief, Rev. 0

THIS PAGE IS INTENTIONALLY BLANK

56F8037 Digital Signal Controller Product Brief, Rev. 0

Freescale Semiconductor

### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH

Freescale Habileter Deutschland Gmb Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MC56F8037PB Rev. 0 09/2006 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Preliminary—Subject to Change Without Notice