# P1480

# LAN CAM 1KX64-BIT CMOS CONTENT-ADDRESSABLE MEMORY

(SUPERSEDES SEPTEMBER 1993 EDITION - VERSION 2)

The P1480 LAN CAM is a 1K X 64-bit fixed-width CMOS Content-addressable Memory (CAM) aimed at address filtering applications in Local-area Network (LAN) bridges and routers. The architecture of the LAN CAM allows a network station list of any length to be searched in a single memory transaction. This device is also well-suited for other applications that require high-speed data searching such as optical and magnetic disk caches and data base accelerators.

Although the internal data path of the P1480 is 64-bits wide, the external interface is multiplexed four ways to allow communication with the device over a 16-bit bus. Vertical cascading and system flag generation require no external logic. The LAN CAM is synchronously controlled by four wires in much the same way as standard memories are controlled. A powerful instruction set increases the control flexibility and minimizes software overhead in typical systems. A data translation facility converts between IEEE 802.3 (CSMA/CD) and 802.5 (Token Ring) address formats on command. Both random access and associative operations are supported by this device. Flexible bit- and word-masking facilities enhance the associative operations. These and other features make the P1480 a powerful, yet easy to use, associative memory which drastically reduces data search delays.

# **FEATURES**

- 1K X 64-bit CMOS Content-addressable Memory (CAM)

- 64-bit internal data path multiplexed four ways over a 16-bit I/O interface

- Simple four-wire synchronous control directly usable in conventional memory subsystems

- Extensive instruction set adds control flexibility Memory Array width can be configured as a mixture of CAM and RAM on 16-bit boundaries

- Memory operations allow random access, associative access, and write-at-next-freeaddress cycles

- Vertical cascading and system flag generation require no external logic

- Two Mask registers allow masking of individual bits for both writing and comparing

- Priority encoder returns highest-priority match address

- Device gives status information after each operation

- Two validity bits per location provide a word masking facility and valid or empty information

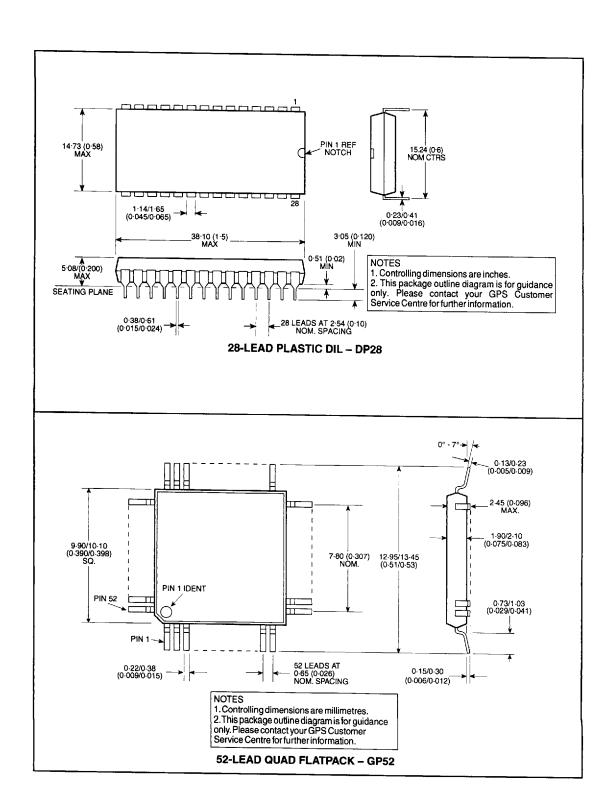

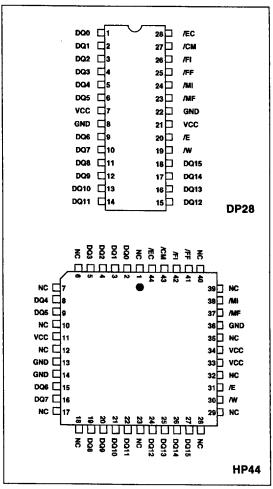

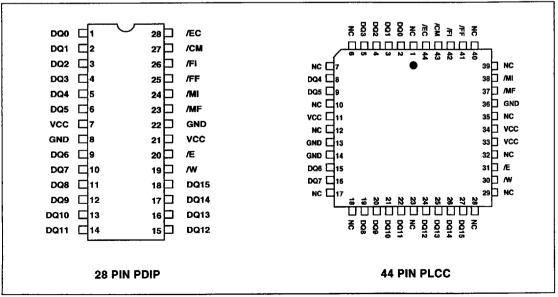

Fig.1 Pin connections (top view)

- Programmable data translation facility converts between IEEE 802.3 and 802.5 formats

- Manufactured in CMOS technology with TTLcompatible inputs and outputs

- Packaged in industry-standard 28-pin PDIP and 44-pin PLCC packages

### ORDERING INFORMATION

| PART NUMBER    | CYCLE TIME | PACKAGE     | TEMPERATURE RANGE |

|----------------|------------|-------------|-------------------|

| P1480-12CGDPAS | 120ns      | 28-PIN PDIP | 0-70°C            |

| P1480-12CGHPAS | 120ns      | 44-PIN PLCC | 0-70°C            |

| P1480-15CGDPAS | 150ns      | 28-PIN PDIP | 0-70°C            |

| P1480-15CGHPAS | 150ns      | 44-PIN PLCC | 0-70°C            |

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage            | -0.5 to 7.0 Volts                                                                    |

|---------------------------|--------------------------------------------------------------------------------------|

| Voltage on all Other Pins | -0.5 to V <sub>CC</sub> +0.5 Volts (-2.0 Volts for 10 ns, measured at the 50% point) |

| Temperature Under Bias    | -40°C to +85°C                                                                       |

| Storage Temperature       | -55°C to +125°C                                                                      |

| DC Output Current         | 20 mA (per Output, one at a time, one second duration)                               |

2. All voltages are referenced to GND.

# **OPERATING CONDITIONS**

| Symbol          | Parameter                     | Min  | Тур | Max                  | Units | Conditions              |

|-----------------|-------------------------------|------|-----|----------------------|-------|-------------------------|

| vcc             | Operating Supply Voltage      | 4.5  | 5.0 | 5.5                  | Volts |                         |

| V <sub>IH</sub> | Input Voltage Logic "1"       | 2.0  |     | V <sub>CC</sub> +0.5 | Volts |                         |

| VIL             | Input Voltage Logic "0"       | -0.5 |     | 0.8                  | Volts | see notes 2 and 3 below |

| TA              | Ambient Operating Temperature | 0    |     | 70                   | °C    | Still Air               |

### Notes

- All voltages referenced to GND at the device pin.

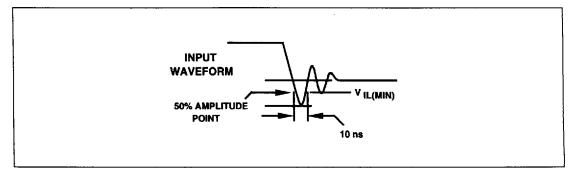

-1.0V for a duration of 10ns measured at 50% amplitude for Input-only lines (see Fig.9).

- 3. Common I/O lines are clamped so that signal transients cannot fall below -0.5V.

### **ELECTRICAL CHARACTERISTICS**

| Symbol          | Parameter                    | Min | Max | Units | Conditions                                                       |

|-----------------|------------------------------|-----|-----|-------|------------------------------------------------------------------|

| lcc             | Average Power Supply Current |     | 200 | mA    |                                                                  |

| v <sub>OH</sub> | Output Voltage Logic "1"     | 2.4 |     | Volts | <sup>1</sup> OH = -2.0 mA                                        |

| V <sub>OL</sub> | Output Voltage Logic "0"     |     | 0.4 | Volts | I <sub>OL</sub> = 4.0 mA                                         |

| ΙιΖ             | Input Leakage Current        | -2  | 2   | μА    | V <sub>SS≤</sub> VIN ≤ VCC                                       |

| loz             | Output Leakage Current       | -10 | 10  | μА    | V <sub>SS</sub> ≤ VIN ≤ VCC;<br>DQ <sub>n</sub> = High Impedance |

# **CAPACITANCE**

| Symbol | Parameter          | Max | Units | Conditions       |

|--------|--------------------|-----|-------|------------------|

| cIN    | Input Capacitance  | 6   | pF    | f=1MHz, VIN=0V.  |

| °OUT   | Output Capacitance | 7   | pF    | f=1MHz, VIN=0 V. |

<sup>1.</sup> Stresses exceeding those listed under Absolute Maximum Ratings may induce failure. Exposure to absolute maximum ratings for extended periods may reduce reliability. Functionality at or above these conditions is not implied.

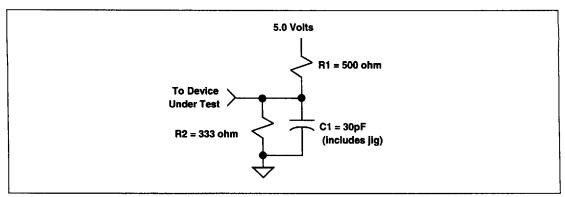

#### **AC TEST CONDITIONS**

| Input Signal Transitions      | 0.0 to 3.0 volts |

|-------------------------------|------------------|

| Input Signal Rise Time        | < 3 ns           |

| Input Signal Fall Time        | < 3 ns           |

| Input Timing Reference Level  | 1.5 volts        |

| Output Timing Reference Level | 0.8 to 2.4 volts |

### PIN DESCRIPTIONS

### DQ0-DQ15 (Data Bus, Common VO, TTL)

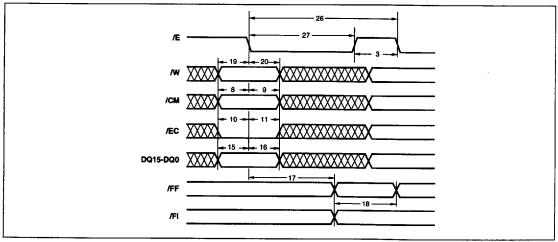

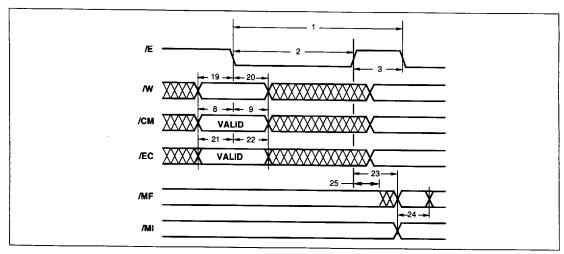

The DQ0-DQ15 lines convey data, commands and status to and from the P1480. The direction and nature of the information that flows to or from the device is controlled by the states of /CM and /W.

### /E (Chip Enable, Input, TTL)

The /E input, the main clock control, enables the LAN CAM while LOW, latches the control signals /W, /CM, /EC on its falling edge and releases them on the rising edge, and clocks the Destination or Source Segment counter on its rising edge.

# /W (Write Enable, Input, TTL)

The /W input selects the direction of data flow during a memory cycle. /W LOW selects a Write cycle, and /W HIGH selects a Read cycle.

### /CM (Data/Command Select, Input, TTL)

The /CM input selects whether the inputs on the DQ0-DQ15 lines are data or commands. /CM LOW selects Command cycles and /CM HIGH Data cycles.

### /EC (Enable Comparison, Input, TTL)

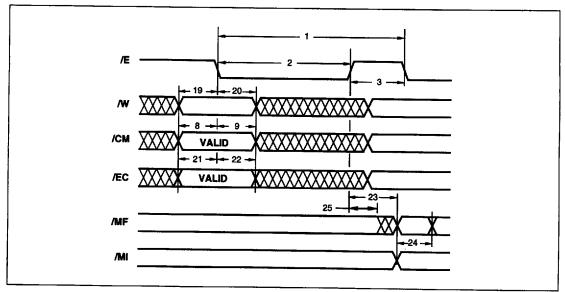

The /EC input enables the /MF output to show the results of a comparison. If /EC is LOW at the falling edge of /E in a given cycle, the /MF output is enabled. Otherwise, the /MF output is held HIGH.

### /MF (Match Flag, Output, TTL)

The /MF output goes LOW when a valid match occurs during a Comparison cycle if the /EC line was latched LOW by the falling edge of /E at the start of the cycle.

### /MI (Match Input, Input, TTL)

The /MI input is used in vertically cascaded systems to prioritize devices. In a daisy-chained system, the /MF output of one device is connected to the /MI input of the next lower-priority device in the chain.

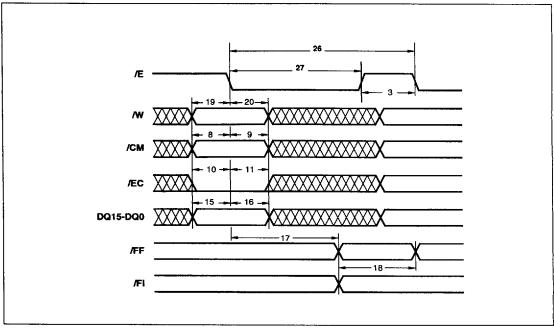

### /FF (Full Flag, Output, TTL)

The /FF output indicates that all the memory locations within the device contain valid contents. /FF LOW indicates the Full condition.

### /FI (Full Input, Input, TTL)

The /FI input is used in vertically cascaded systems to generate CAM Memory System Full indication. In a daisy-chained system, the /FF output of one device is connected to the /FI input of the next-lower priority device in the chain.

### V<sub>cc</sub>, GND (Positive Power Supply and Ground)

These pins are the main power supply connections to the P1480. VCC must be held at +5V + 10% relative to the GND pin, which is at 0V (system reference potential), for correct operation of the device.

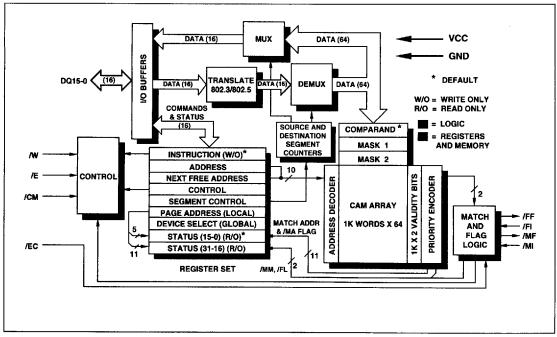

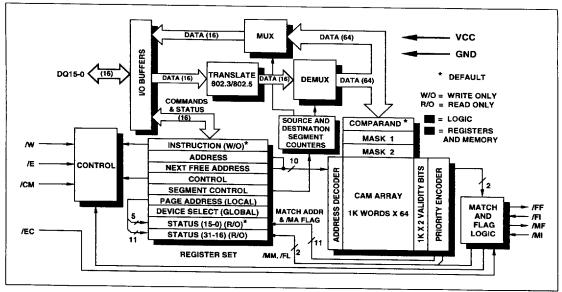

Fig.2 Block Diagram

### **FUNCTIONAL DESCRIPTION**

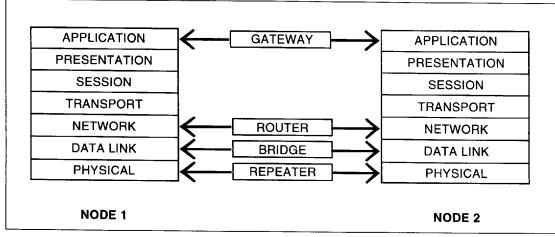

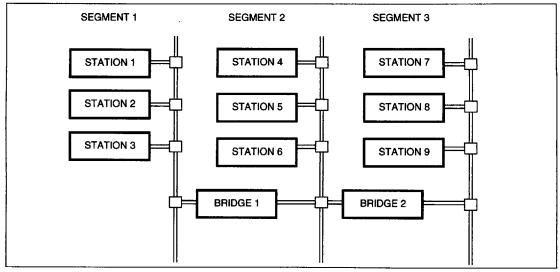

The GEC Plessey Semiconductors' P1480 is a 1K x 64-bit CAM targeted at address filtering applications in Localarea Network (LAN) Bridges and Routers. The device is designed to hold the station list in the Bridge, allowing single-transaction decisions on whether to pass a data packet from one segment across the Bridge to another.

The P1480 is designed to minimize the external logic needed for expansion and control. It is controlled via four synchronous control signals and by commands loaded into an Instruction register. One of the control signals is used to indicate whether information present on the 16-bit input bus is to be interpreted as a Data or a Command field. During a Random Access cycle, the Address field is loaded into the Instruction Address register during a second Command Write cycle.

The data inputs and outputs of the P1480 are multiplexed four ways over a 16-bit I/O bus. This multiplexing increases the transaction time but allows the device to reside in a 28-pin package. The speed penalty related to the multiplexing is insignificant in the LAN Bridge environment because the address bits to be compared in the CAM are received serially from the network, so the loading is pipelined.

The P1480 contains 65,536 bits of static CAM, organized as 1024 64-bit Data fields. Each Data field can be partitioned into a CAM and a RAM subfield on 16-bit boundaries. In LAN Bridges, the RAM subfield could hold port-address and time-out information, or other data associated with the Destination Address held in the CAM subfield of the location.

Appended to each 64-bit data field are two bits of CAM storage to indicate the validity of the location. These two bits are encoded to render four validity conditions: Valid data, Skip, Empty and Random access only.

The contents of the memory can be randomly accessed or associatively accessed. During a Data Comparison cycle, data is assembled in a Comparand register and is compared with the CAM section of the memory array. Only the locations whose Validity bits are set Valid will enter into comparison with the Comparand. Comparisons can also be done on the Validity bits themselves. Random access to the memory array, using an address to define a unique location, is independent of the state of the Validity bits.

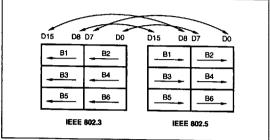

The station list can be held in either the IEEE 802.3 or IEEE 802.5 format. When data is received from the network in other than the selected default storage format, the data bits can be translated during the loading process. This facility simplifies bridging between CSMA/CD and Token Ring networks.

Two Mask registers on the device can be selected to mask comparison or data writes. For comparison masking, data held in the selected Mask register determines which bits of the Comparand are compared against the valid contents. During a Write cycle, data in the designated Mask register selects which bits in the destination are written.

The Match line associated with each location is fed into a Priority encoder where multiple responses are resolved and the address of the highest-priority responder (lowest numbered physical address) is generated. In the LAN Bridge application a multiple response might indicate the existence of an error, whereas, in other applications, the existence of multiple responders may be a valid condition.

After a Comparison cycle, the Status register contains the address of the highest-priority responding location, along with flags indicating Match, Multiple Match and Full. The Match and Full flags are also available directly as output signals. These flags can be daisy-chained independently to provide system Match and Full indication without external logic.

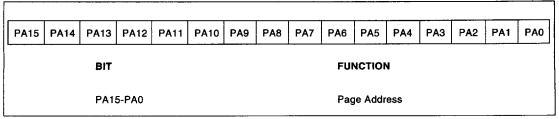

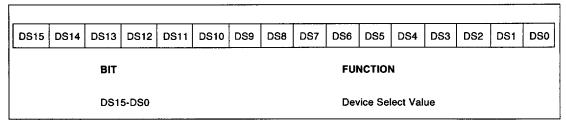

A Page Address register simplifies vertical expansion in systems using more than one P1480. This register is loaded with upper-order address information during system initialization. During a Comparison cycle, the lower-order 10 bits of the Match address are fed to the Status register from the Priority encoder and are concatenated with the upper-order address bits from the Page Address register. The Device Select register is used to access a particular device in a vertically cascaded LAN CAM array. The address of the desired device is broadcast to all Device Select registers. Only the device whose Page Address register contains this address will respond to subsequent transactions.

A Control register sets up operating conditions within the P1480, such as Reset, enable or disable Match Flag, enable or disable Full Flag, set default data translation, CAM/RAM partitioning, disable or select masking condition, and disable or select address auto-increment or auto-decrement.

Source and Destination Segment counters within the P1480 control reading and writing 64-bit data. A Segment Control register sets the count limits for the Source and Destination Segment counters, and allows loading of values into each respective counter.

The P1480 is controlled by a combination of hardware signals and instructions loaded into the Instruction register. The instruction set offers a powerful, symmetrical control mechanism for causing the LAN CAM to perform the tasks commonly encountered in LAN Bridges and Routers. To facilitate the repetitive operations that are often desired, several instructions have persistent sources and/or destinations. In this way much of the software overhead that would otherwise be suffered is removed because operations done in a batch can be set up once and left in a given configuration until changed.

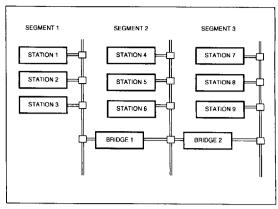

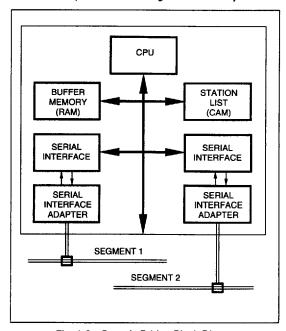

Larger LANs are commonly divided into more manageable segments that are joined by a Bridge to prevent excessive local traffic from degrading the overall network performance as shown in Fig.3 below. Segments can all be of the same protocol or can be of mixed protocols. The two major protocols of interest are IEEE 802.3 (Ethernet) and IEEE 802.5 (Token Ring).

Fig.3 - LAN segments connected by bridges

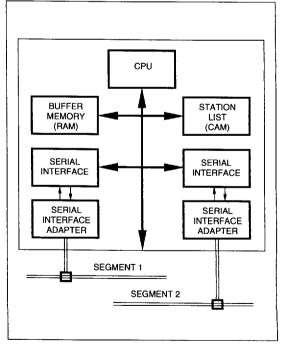

The Bridge monitors the traffic on all of its segments to determine to which port a particular packet is aimed. This determination requires searching the destination address field (six bytes) in the packet and comparing it to those stored in the station list. A match provides associated information which the Bridge uses to route the packet correctly. A generic block diagram of a Bridge which would utilize one or more LAN CAMs to store and search the station list is shown in Fig.4. Using the LAN CAM radically reduces the search time and improves the Bridge's performance.

Fig.4 - Generic bridge block diagram

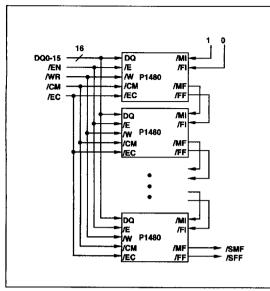

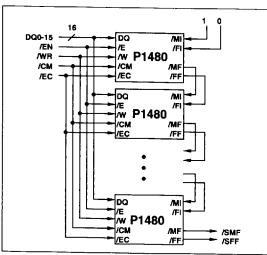

Fig.5 - Vertically cascading the LAN CAM

One P1480 can contain up to 1024 station list entries. For applications that require a larger station list, the LAN CAM is easily cascaded vertically without the need for external logic. Fig.5 below shows the connection scheme. Note that the flags are daisy-chained to generate the system flags without the need for external logic. Further, the Page register facility on the LAN CAM allows each device in the vertically cascaded chain to attach its own address in the event of a match in that device. This feature removes the need to construct an external priority encoder to calculate the complete match address. The fullness indication is also daisy-chained to permit the use of Associative writes which do not require a specific address. The P1480 can be instructed to Write at Next Free Address, even in a cascaded environment.

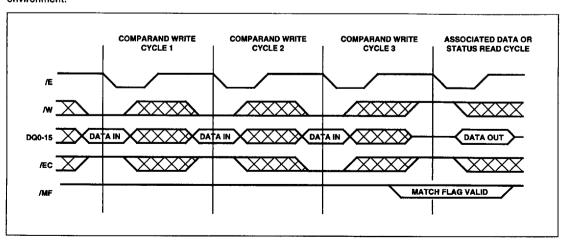

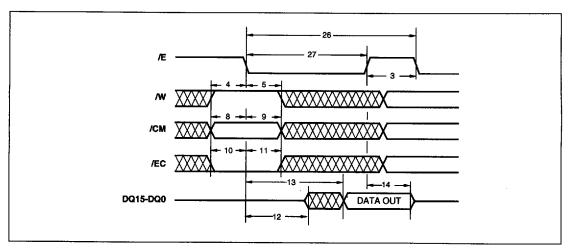

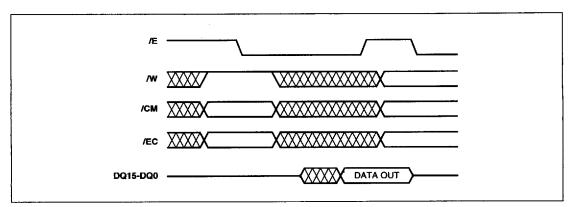

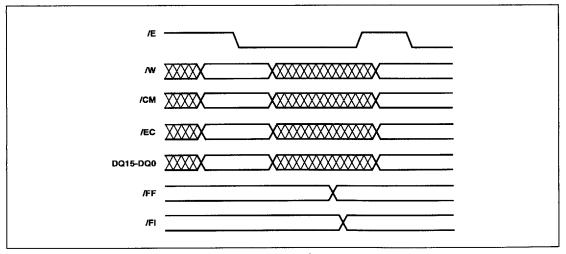

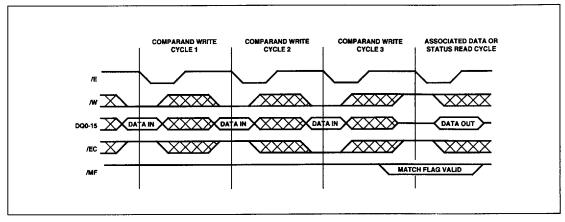

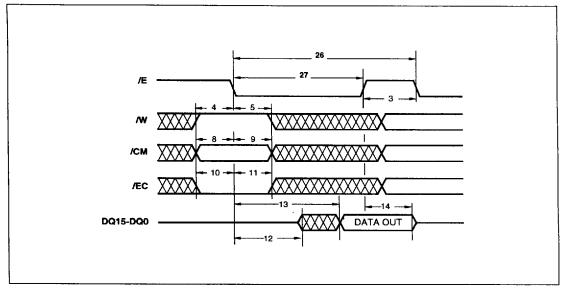

Table 1 illustrates the flow of a simple Compare operation assuming the LAN CAM is configured as 48 bits of CAM and 16 bits of RAM, any masking on the Compare and the Segment counters is already set up, Associated data is to be read back, and the Match address and the Match flag are to be read back through the Status register (the Associated Data and Status reads are optional and can be in either order). This search operation takes 270 ns to get a hardware flag indication and 450 ns to obtain both a Match address and Associated data, regardless of the length of the Station List. Fig.6 shows the cycle-to-cycle timing with the Match flag valid at the end of the third load cycle if /EC is LOW at the start of the third cycle. The fourth cycle reads status or associated data, depending on the state of /CM.

| Duration | Operation             |      | ontroi<br>/CM |        | l Flag<br>/MF |

|----------|-----------------------|------|---------------|--------|---------------|

| 90ns     | Load S1 COMPARAND     | L    | Н             | Н      | Н             |

| 90ns     | Load S2 COMPARAND     | L    | н             | Н      | Н             |

| 90ns     | Load S3 COMPARAND     | L    | Н             | L      | L             |

| 90ns     | Read Associated Data* | Н    | н             | Н      | Н             |

| 90ns     | Read Status Register* | Н    | L             | Н      | Н             |

| 450ns    | Total                 | sequ | ence          | is arb | itrary        |

Table 1 - Station list search flow chart

Fig.6 - Cycle-to-cycle timing

# **INSTRUCTION SET DESCRIPTIONS**

A more complete description of the Instruction Set can be obtained in the P1480 LAN CAM Handbook (3113-1.3).

### SELECT PERSISTENT SOURCE (SPS)

Binary Op Code

0000 f000 0000 0sss Address Field Flag Selected Source

The SPS instruction selects a source for Data Reads. After instruction execution, the selected source persistently remains the source for Data Reads until another SPS instruction is executed or until a Reset occurs. The Comparand register is the default persistent source after power up or Reset.

# **SELECT PERSISTENT DESTINATION (SPD)**

**Binary Op Code**

0000 f001 mmdd dvvv Address Flag

mm

...

Mask Register Select

ddd

Selected Destination

Validity Setting if destination

is a memory location

The SPD instruction selects a destination for Data Writes. Once this instruction is executed, the selected destination persistently remains the destination for Data Writes until another SPD instruction is executed or until a Reset. The Comparand register is the default destination for Data Writes.

When the selected destination is the Comparand register or the Memory array, the writing of data may be masked by the selected Mask register, Mask Register 1 or Mask Register 2. When the writing of data is masked, only those bits in the destination that correspond to bits containing 0's in the selected Mask register will be modified. Bits in the destination corresponding to bits containing 1's in the selected Mask register will remain unchanged.

Writing to the Comparand register or a Mask register causes a comparison to occur. Writing to the Memory array does not cause a comparison to occur. The next free address is generated when any instruction that could potentially affect the Validity bits is executed.

### **TEMPORARY COMMAND OVERIDE (TCO)**

Binary Op-Code ddd

0000 0010 00dd d000 Register selected as sourceor

destination for only the

next Command Read or Write cycle.

When a TCO instruction is executed, the temporarily selected register becomes the source or destination for only the next Command Read or Write cycle, respectively. Once either of those cycles occurs, subsequent Command Read or Write cycles revert to reading the Status register and writing the Instruction register during Command Reads or Writes. The special TCO PS or TCO PD instructions allow the user to read which persistent source or destination has been selected in the next Command Read cycle. If either of these instructions is followed by a Command Write cycle, no actionooccurs. Note that the TCO instruction permits access to the Instruction Address register for diagnostic purposes. Also, the Next Free Address register is Read Only, and Writes to the Page Address register invalidate the contents of the Status register.

### **DATA MOVE (MOV)**

**Binary Op-code**

0000 f011 mmdd dsss or 0000 f011 mmdd dvss

Address Field Flag Mask Register select

ddd sss

mm

Destination of Data Source of Data

555

Validity setting if destination is a

memory location

The MOV instruction transfers the data in the selected source to the selected destination. Data transfers between the Memory array and the Comparand register may be masked by the selected Mask register, Mask Register 1 or Mask Register 2. If the transfer is masked, only those bits in the destination which correspond to bits containing 0's in the selected Mask register will be altered. Destination bits which correspond to bits containing 1's in the selected Mask register will remain unchanged.

The Validity bits of a Memory location used as a destination for a MOV instruction will be set to the Valid state or left unchanged, depending on the nature of the operation. If the source and destination are selected to be the same register in register-to-register operations, no net change to the state of the LAN CAM occurs. This operation would be equivalent to a NOOP.

### **VALIDITY BIT CONTROL (VBC)**

Binary Op-code

0000 f100 00dd dvvv Address Field Flag

ddd

Destination of data

VVV

Validity setting for Memory location

The VBC instruction sets the Validity bits to the selected state at the selected Memory location or locations. Validity bits can be accessed randomly or associatively. The VBC instruction can be used in conjunction with the appropriate Compare instruction to compare on any Validity condition. Hence, skipped locations can be returned to the Valid state after processing multiple matches by repeating the Compare operation using the Skip condition as the Validity field search criterion.

### COMPARE (CMP)

Binary Op-code

0000 0101 0000 0vvv Validity condition

The CMP instruction forces a Comparison after a cycle, such as a Memory Write cycle, which does not automatically result in a Comparison. Destinations to which Write cycles cause an automatic Comparison are the Comparand register, the Mask registers, the Control register.

The CMP E instruction forces the generation of the next free address. The Memory array at the next free address does not need to be a Persistent Destination. The CMP S instruction is used in conjunction with the VBC instruction to return all skipped locations to the Valid state after processing multiple matches. The CMP R instruction permits associative access to any Random-access-only Memory locations.

# SET FULL FLAG (SFF)

Binary Op-code 0000 0111 0000 0000

The SFF instruction is a special instruction used to force the Full flag LOW for a device whose /FI input is LOW, but whose /FF output is HIGH. SFF is used in vertically cascaded systems for selecting each device in turn to initialize the Page Address register.

# INSTRUCTION SET SUMMARY

# MNEMONIC FORMAT: INS dst,src[msk],val

INS: Instruction mnemonic.

dst: Destination of the data.

src: Source of the data.

msk: Mask register used.

val: Validity condition set at the location written.

### SELECT PERSISTANT SOURCE

| Operation                        | Mnemonic    | Op Code |

|----------------------------------|-------------|---------|

| Comparand Register               | SPS CR      | 0000Н   |

| Mask Register 1                  | SPS MR1     | 0001H   |

| Mask Register 2                  | SPS MR2     | 0002H   |

| Memory Array at Address Reg      | SPS MO [AR] | 0004H   |

| Memory Array at Address          | SPS M@aaaH  | 0804H   |

| Memory at Highest-priority Match | SPS MOHM    | 0005H   |

# **TEMPORARY COMMAND OVERIDE**

| Operation                    | Mnemonic | Op Code |

|------------------------------|----------|---------|

| Control Register             | TCO CT   | 0200H   |

| Page Address Register        | TCO PA   | 0208H   |

| Segment Control Register     | TCO SC   | 0210H   |

| Next Free Address Register   | TCO NF   | 0218H   |

| Instruction Address Register | TCO AR   | 0220H   |

| Device Select Register       | TCO DS   | 0228H   |

| Read Persistent Source       | TCO PS   | 0230H   |

| Read Persistent Destination  | TCO PD   | 0238H   |

### **VALIDITY BIT CONTROL**

| Operation                             | Mnemonic   | Op Code |

|---------------------------------------|------------|---------|

| Set Validity bits at Address          |            |         |

| Register                              |            | 1       |

| Set Valid                             | VBC [AR],V | 0424H   |

| Set Empty                             | VBC [AR],E | 0425H   |

| Set Skip                              | VBC [AR],S | 0426H   |

| Set Random Access                     | VBC [AR],R | 0427H   |

| Set Validity bits at Address          |            |         |

| Set Valid                             | VBC aaaH,V | 0C24H   |

| Set Empty                             | VBC aaaH,E | 0C25H   |

| Set Skip                              | VBC aaaH,S | 0C26H   |

| Set Random Access                     | VBC aaaH,R | 0C27H   |

| Set Validity bits at Highest-priority |            |         |

| Match                                 | į          |         |

| Set Valid                             | VBC HM,V   | 042CH   |

| Set Empty                             | VBC HM.E   | 042DH   |

| Set Skip                              | VBC HM.S   | 042EH   |

| Set Random Access                     | VBC HM,R   | 042FH   |

| Set Validity bits at All Matching     |            |         |

| Locations                             |            |         |

| Set Valid                             | VBC ALM,V  | 043CH   |

| Set Empty                             | VBC ALM,E  | 043DH   |

| Set Skip                              | VBC ALM.S  | 043EH   |

| Set Random Access                     | VBC ALM.R  | 043FH   |

### SELECT PERSISTANT DESTINATION

| Comparand Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Oppode 100H 140H 180H 10H 124H 164H 165H 167H 167H 164H 164H 165H 165H 165H 165H 165H 165H 165H 165                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Masked by MR1 Masked by MR2  Mask Register 1 MaskRegister 2 Memory at Address Reg set Valid Masked by MR1 Masked by MR2  Memory at Address Reg set Empty Masked by MR1 Masked by MR2  Memory at Address Reg set Skip Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address Reg set Random Masked by MR1 Masked by MR2  Memory at Address Reg set Random Masked by MR1 Masked by MR2  Memory at Address Set Valid Masked by MR2  Memory at Address set Valid Masked by MR1 Masked by MR2  Memory at Address set Valid Masked by MR2  Memory at Address set Valid Masked by MR2  Memory at Address set Valid Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Empty Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR2  Memory at Address set Random Masked by MR1 Masked by | 40H<br>80H<br>10H<br>10H<br>24H<br>64H<br>A4H<br>25H<br>66H<br>A6H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H<br>65H |

| Masked by MR1         SPD CR[MR1]         01           Mask Register 1         SPD MR1         01           MaskRegister 2         SPD MR1         01           Memory at Address Reg set Valid Masked by MR1         SPD M@AR[MR1], V SPD M@AR[MR2], V         01           Memory at Address Reg set Empty Masked by MR1         SPD M@[AR][MR1], E SPD M@[AR][MR1], E SPD M@[AR][MR2], E         01           Memory at Address Reg set Skip Masked by MR1         SPD M@[AR][MR2], E         01           Memory at Address Reg set Skip Masked by MR1         SPD M@[AR][MR1], SPD M@[AR][MR2], SPD M@[AR][MR                                                                                                                                                                                                                                                                                                         | 40H<br>80H<br>10H<br>10H<br>24H<br>64H<br>A4H<br>25H<br>66H<br>A6H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H<br>65H |

| Masked by MR2         SPD CR[MR2]         01           Mask Register 1         SPD MR1         01           MaskRegister 2         SPD MR2         01           Memory at Address Reg set Valid Masked by MR1         SPD M@AR[MR1],V         01           Memory at Address Reg set Empty Masked by MR1         SPD M@[AR][MR1],E         01           Memory at Address Reg set Skip Masked by MR1         SPD M@[AR][MR1],S         01           Memory at Address Reg set Random Masked by MR1         SPD M@[AR][MR1],S         01           Memory at Address Reg set Random Masked by MR1         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR2         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR1         SPD M@aaaH[MR1],V         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH[MR1],V         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH[MR1],C         09           Memory at Address set Skip Masked by MR1         SPD M@aaaH[MR1],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH[MR1],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH[MR1],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH[MR1],R         09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80H<br>10H<br>10H<br>24H<br>64H<br>65H<br>25H<br>66H<br>66H<br>67H<br>67H<br>24H<br>64H<br>64H<br>64H<br>25H<br>65H        |

| MaskRegister 2         Memory at Address Reg set Valid Masked by MR1         SPD M@AR,V SPD M@AR[MR1],V SPD M@AR[MR2],V SPD M@AR[MR2],E SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR2],S SPD M@[AR][MR1],S SPD M@[AR][MR2],R SPD M@[AR][MR2],R SPD M@[AR][MR2],R SPD M@ARAH[MR2],V SPD M@ARAH[MR2],V SPD M@ARAH[MR2],V SPD M@ARAH[MR2],V SPD M@ARAH[MR2],C SPD M@ARAH[MR2],C SPD M@ARAH[MR2],C SPD M@ARAH[MR2],S SPD M@ARAH[MR2],S SPD M@ARAH[MR2],S SPD M@ARAH[MR2],S SPD M@ARAH[MR2],S SPD M@ARAH[MR2],S SPD M@ARAH[MR1],R SPD M@ARA                                          | 10H<br>24H<br>64H<br>A4H<br>25H<br>65H<br>A5H<br>26H<br>66H<br>A6H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H<br>65H |

| Memory at Address Reg set Valid Masked by MR1 Masked by MR2  Memory at Address Reg set Empty Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address Reg set Skip Masked by MR1 Masked by MR2  Memory at Address Reg set Random Masked by MR1 Masked by MR2  Memory at Address set Valid Masked by MR1 Masked by MR2  Memory at Address set Skip SPD M@aaaH, MR2, E SPD M@aaaH, MR1, SPD M@aaaH, SSPD M@aaaH, MR1, SPD M@aaaH, MR1, RD M@aaaH, MR1, RD M@aaaH, RD M@aaAH | 24H<br>64H<br>25H<br>65H<br>A5H<br>26H<br>66H<br>A6H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H<br>65H               |

| Masked by MR1         SPD M ⊕ AR[MR1], V SPD M ⊕ AR[MR1], V SPD M ⊕ AR[MR2], V O1         O1           Memory at Address Reg set Empty Masked by MR1 Masked by MR2         SPD M ⊕ [AR][MR1], E SPD M ⊕ [AR][MR2], S SPD M ⊕ [AR][MR1], S SPD M ⊕ [AR][MR1], R SPD M ⊕ [AR][                                                                              | 64H<br>A4H<br>25H<br>65H<br>A5H<br>26H<br>66H<br>A7H<br>27H<br>64H<br>A4H<br>25H<br>65H                                    |

| Masked by MR2         SPD M@AR[MR2],V         01           Memory at Address Reg set Empty Masked by MR1         SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR2],E         01           Memory at Address Reg set Skip Masked by MR1         SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR2],S         01           Memory at Address Reg set Random Masked by MR1         SPD M@[AR][MR1],R SPD M@[AR][MR2],R         01           Memory at Address set Valid Masked by MR2         SPD M@[AR][MR2],R         01           Memory at Address set Valid Masked by MR2         SPD M@aaaH,[MR2],V         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH,E SPD M@aaaH,E SPD M@aaaH,[MR1],E SPD M@aaaH,[MR1],E SPD M@aaaH,[MR1],E SPD M@aaaH,[MR1],S SPD M@aaaH,[MR2],S O9         09           Memory at Address set Skip Masked by MR1         SPD M@aaaH,MR2],S O9         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,MR1],S O9         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,MR1],R O9         09           Memory at Highest-prio. Match,Valid Masked by MR1         SPD M@aaaH,MR2],R O9         09           Memory at Highest-prio. Match,Valid Masked by MR1         SPD M@aaaH,MR1],R O9         09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25H<br>65H<br>26H<br>66H<br>26H<br>66H<br>27H<br>67H<br>24H<br>64H<br>84H<br>25H<br>65H                                    |

| Memory at Address Reg set Empty Masked by MR1 Masked by MR2         SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR1],E SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR2],R SPD M@[AR][MR2],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR1],S SPD M@[AR][MR1],R SP                                 | 25H<br>65H<br>26H<br>66H<br>66H<br>67H<br>67H<br>47H<br>24H<br>64H<br>25H<br>65H                                           |

| Masked by MR1         SPD M@[AR][MR1],E         01           Memory at Address Reg set Skip Masked by MR1         SPD M@[AR][MR1],S         01           Memory at Address Reg set Random Masked by MR1         SPD M@[AR][MR1],S         01           Memory at Address Reg set Random Masked by MR2         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR2         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR1         SPD M@aaaH,[MR2],R         09           Memory at Address set Empty Masked by MR2         SPD M@aaaH,E         09           Memory at Address set Empty Masked by MR2         SPD M@aaaH,E         09           Memory at Address set Skip Masked by MR2         SPD M@aaaH,[MR1],E         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,[MR2],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,[MR1],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@aaaH,MR2],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@hM,V         012           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@hM,V         012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65H<br>A5H<br>26H<br>66H<br>A6H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H                                                  |

| Masked by MR2         SPD M@[AR][MR2],E         01           Memory at Address Reg set Skip Masked by MR1 Masked by MR2         SPD M@[AR][MR1],S SPD M@[AR][MR1],S SPD M@[AR][MR2],S         01           Memory at Address Reg set Random Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR2         SPD M@[AR][MR1],R SPD M@[AR][MR1],R SPD M@[AR][MR2],R SPD M@[AR][MR2],S SPD M@[AR][MR2],R SPD M@[AR                                                                                                                          | 26H<br>66H<br>66H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H                                                                |

| Memory at Address Reg set Skip Masked by MR1 Masked by MR2  Memory at Address Reg set Random Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address Set Valid Masked by MR1 Masked by MR2  Memory at Address set Skip Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR2  Memory at Highest-prio. Match, Valid Masked by MR1 Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  SPD M@aaaH, MR2, R  O92  Memory at Highest-prio. Match, Valid Masked by MR1  SPD M@hM, V  SPD | 26H<br>66H<br>A6H<br>27H<br>67H<br>A7H<br>24H<br>64H<br>A4H                                                                |

| Masked by MR1         SPD M@[AR][MR1],S         01           Masked by MR2         SPD M@[AR][MR2],S         01           Memory at Address Reg set Random Masked by MR1         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR1         SPD M@aaaH,V         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH,E         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH,E         09           Memory at Address set Skip Masked by MR2         SPD M@aaaH,E         09           Memory at Address set Skip Masked by MR1         SPD M@aaaH,S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,[MR1],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,[MR1],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@aaaH,MR2],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@hM,V         012           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@hM,V         012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H<br>65H                                                                       |

| Masked by MR2         SPD M@[AR][MR2],S         01           Memory at Address Reg set Random Masked by MR1         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR1         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR1         SPD M@aaaH,W         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH,E         09           Memory at Address set Empty Masked by MR2         SPD M@aaaH,E         09           Memory at Address set Skip Masked by MR2         SPD M@aaaH,[MR1],E         09           Memory at Address set Random Masked by MR1         SPD M@aaaH,[MR2],S         09           Memory at Address set Random Masked by MR1         SPD M@aaaH,[MR1],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@aaaH,N         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@hM,V         012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H                                                                              |

| Memory at Address Reg set Random Masked by MR1 Masked by MR2  Memory at Address set Valid Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Skip Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR2  Memory at Address set Random Masked by MR1 Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Masked by MR1  Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  VPD M@HM[MR1], V  O12  O15  O16  O17  O17  O17  O18  O18  O18  O18  O18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27H<br>67H<br>A7H<br>24H<br>64H<br>A4H<br>25H                                                                              |

| Masked by MR1         SPD M@[AR][MR1],R         01           Memory at Address set Valid Masked by MR1         SPD M@[aaaH,V         09           Memory at Address set Empty Masked by MR2         SPD M@aaaH[MR1],V         09           Memory at Address set Empty Masked by MR1         SPD M@aaaH[MR2],E         09           Memory at Address set Skip Masked by MR2         SPD M@aaaH[MR2],E         09           Memory at Address set Skip Masked by MR1         SPD M@aaaH[MR1],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH,MR2],S         09           Memory at Address set Random Masked by MR1         SPD M@aaaH[MR1],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@aaaH[MR1],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@hM,V         012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67H<br>A7H<br>24H<br>64H<br>A4H<br>25H<br>65H                                                                              |

| Masked by MR2         SPD M@[AR][MR2],R         01           Memory at Address set Valid Masked by MR1         SPD M@aaaH,V SPD M@aaaH[MR1],V SPD M@aaaH[MR2],V SPD M@aaaH[MR2],V SPD M@aaaH[MR2],V SPD M@aaaH[MR2],E         09           Memory at Address set Empty Masked by MR1 Masked by MR2         SPD M@aaaH[MR1],E SPD M@aaaH[MR2],E SPD M@aaaH[MR2],E SPD M@aaaH[MR2],S SPD M@aaaH[MR2],S SPD M@aaaH[MR2],S SPD M@aaaH[MR2],S SPD M@aaaH[MR2],S SPD M@aaaH[MR2],R SPD M@aaaH[MR2],R SPD M@aaaH[MR2],R SPD M@aaaH[MR2],R SPD M@aaaH[MR2],R SPD M@aaaH[MR1],R SPD M@AABAH[MR1],R SPD M@AAABH[MR1],R SPD M@AA                                                                                                                         | 24H<br>64H<br>A4H<br>25H<br>65H                                                                                            |

| Memory at Address set Valid Masked by MR1 Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR2  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  SPD M@aaaH, MR2, R0  SPD M@aaaH, MR1, R0  SPD M@aaaH, MR2, R0  SPD M@aaaH, R0  SPD  | 24H<br>64H<br>A4H<br>25H<br>65H                                                                                            |

| Masked by MR1         SPD M@aaaH[MR1],V         09           Memory at Address set Empty         SPD M@aaaH[MR2],V         09           Memory at Address set Empty         SPD M@aaaH[MR1],E         09           Memory at Address set Skip         SPD M@aaaH[MR2],E         09           Masked by MR1         SPD M@aaaH[MR1],S         09           Masked by MR2         SPD M@aaaH[MR2],S         09           Memory at Address set Random         SPD M@aaaH[MR2],S         09           Masked by MR1         SPD M@aaaH[MR1],R         09           Memory at Highest-prio. Match,Valld Masked by MR1         SPD M@hM,V         09           Memory at Highest-prio. Match,Valld Masked by MR1         SPD M@hM,V         012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64H<br>A4H<br>25H<br>65H                                                                                                   |

| Masked by MR2  Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Skip Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR2  Memory at Highest-prio. Match, Valld Masked by MR1  Memory at Highest-prio. Match, Valld Masked by MR1  Memory at Highest-prio. Match, Valld Masked by MR1  SPD M@aaaH[MR2], R  SPD M@aaaH[MR2], R  SPD M@aaaH[MR1], R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25H<br>65H                                                                                                                 |

| Memory at Address set Empty Masked by MR1 Masked by MR2  Memory at Address set Skip Masked by MR1 Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address set Skip Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR2  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  SPD M@aaaH,R SPD M | 25H<br>65H                                                                                                                 |

| Masked by MR1         SPD M@aaaH[MR1],E         09           Masked by MR2         SPD M@aaaH[MR2],E         09           Memory at Address set Skip Masked by MR1         SPD M@aaaH[MR1],S         09           Memory at Address set Random Masked by MR1         SPD M@aaaH[MR2],S         09           Memory at Address set Random Masked by MR2         SPD M@aaaH[MR1],R         09           Memory at Highest-prio. Match, Valld Masked by MR1         SPD M@aaaH[MR2],R         09           Memory at Highest-prio. Match, Valld Masked by MR1         SPD M@hM,V         012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65H                                                                                                                        |

| Masked by MR2         SPD M@aaaH[MR2],E         09.           Memory at Address set Skip<br>Masked by MR1<br>Masked by MR2         SPD M@aaaH[MR1],S<br>SPD M@aaaH[MR2],S         09.           Memory at Address set Random<br>Masked by MR1<br>Masked by MR2         SPD M@aaaH[MR1],R<br>SPD M@aaaH[MR1],R<br>SPD M@aaaH[MR2],R         09.           Memory at Highest-prio. Match, Valld<br>Masked by MR1         SPD M@HM,V<br>SPD M@HM[MR1],V         012.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| Memory at Address set Skip Masked by MR1 Masked by MR2  Memory at Address set Random Masked by MR1 Masked by MR1  Memory at Address set Random Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  Memory at Highest-prio. Match, Valid Masked by MR1  SPD M@aaaH,MR1,N SPD M@aaaH,MR1,N SPD M@aaaH,MR1,N SPD M@HM,V SPD M@HM,MR1,V SPD M@HM,MR1,V SPD M@HM,MR1,V SPD M@HM,MR1,N SPD M@ABABH,MR1,N SPD M@aaaH,MR1,N SPD M@ABABH,MR1,N SPD MABABH,MR1,N SPD MABABH,MR1,N SPD MABABH,MR1,N SPD MABABH,MR1,N SPD MABABH,MR1,N SPD MABABH,MR1,N SPD MAB | A5H                                                                                                                        |

| Masked by MR1<br>Masked by MR2         SPD M@aaaH[MR1],S<br>SPD M@aaaH[MR2],S         09,009,000,000,000,000,000,000,000,000,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| Masked by MR2         SPD M@aaaH[MR2],S         09.           Memory at Address set Random Masked by MR1         SPD M@aaaH[MR1],R         09.           Memory at Highest-prio. Match, Valld Masked by MR1         SPD M@hM,V SPD M@HM,V SPD M@HM[MR1],V         016.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26H                                                                                                                        |

| Memory at Address set Random Masked by MR1 Masked by MR2  Memory at Highest-prio. Match, Valid Masked by MR1  SPD M@aaaH[MR1],R SPD M@aaaH[MR2],R O9/ SPD M@HM,V SPD M@HM[MR1],V O11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66H                                                                                                                        |

| Masked by MR1         SPD M@aaaH[MR1],R         09           Masked by MR2         SPD M@aaaH[MR2],R         09           Memory at Highest-prio. Match, Valid Masked by MR1         SPD M@HM,V         016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>46</b> H                                                                                                                |

| Masked by MR2 SPD M@aaaHMR2],R 09/ Memory at Highest-prio. Match,Valld SPD M@HM,V O11/ Masked by MR1 SPD M@HM[MR1],V 016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27H                                                                                                                        |

| Memory at Highest-prio. Match, Valid SPD M@HM, V 012 Masked by MR1 SPD M@HM[MR1], V 016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67H                                                                                                                        |

| Masked by MR1 SPD M@HM[MR1], V 016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47H                                                                                                                        |