|                                         |                     |                  |     |      |        |                  |      | RI | EVISI | ONS         |                     |             |              |             |              |          |              |               |           |             |

|-----------------------------------------|---------------------|------------------|-----|------|--------|------------------|------|----|-------|-------------|---------------------|-------------|--------------|-------------|--------------|----------|--------------|---------------|-----------|-------------|

| LTR                                     | ļ                   |                  |     |      | D      | ESCR             | IPTI | ON |       | <del></del> | ·                   |             | D            | ATE         | (YR-MO       | -DA)     |              | APPR          | OVED      |             |

|                                         |                     |                  |     |      |        |                  |      |    |       |             |                     |             |              |             |              |          |              |               |           |             |

| REV                                     |                     |                  |     |      |        |                  |      | ľ  |       |             |                     | - · · · · · |              |             | Γ            | <u> </u> |              |               | <u> </u>  | <u> </u>    |

| SHEET                                   | 35                  |                  |     |      |        |                  |      |    |       |             |                     |             |              |             |              |          |              |               |           |             |

| REV                                     |                     |                  |     |      |        |                  |      |    |       |             |                     |             |              |             |              |          |              |               |           |             |

| SHEET                                   | 15                  | 16               | 17  | 18   | 19     | 20               | 21   | 22 | 23    | 24          | 25                  | 26          | 27           | 28          | 29           | 30       | 31           | 32            | 33        | 34          |

| REV STAT                                |                     |                  |     | RE   | V      |                  |      |    |       |             |                     |             |              |             |              |          |              |               |           |             |

| OF SHEET:                               | S<br>               |                  |     | SH   | EET    |                  | 1    | 2  | 3     | 4           | 5                   | 6           | 7            | 8           | 9            | 10       | 11           | 12            | 13        | 14          |

| PMIC N/A                                |                     |                  |     |      | ARED E |                  | ill  |    |       | DI          | EFENS               |             |              |             | S SU         |          |              | rer           | <u> </u>  | 1           |

|                                         | ARDI<br>ITAF<br>WIN | <b>S</b> Y       |     |      | KED BY |                  |      |    |       |             | <del></del> .       | -           |              |             |              |          |              | <del></del>   |           | <del></del> |

| THIS DRAWIN<br>FOR USE BY A<br>AND AGEN | G IS A<br>ALL DEI   | VAILAE<br>PARTME | NTS | ļ.   | OVED B |                  | ıg   |    |       | 8-I         | CROC<br>BIT<br>LICO | MIC         | JIT,<br>ROPR | DIO<br>OCE: | GITA<br>SSOR | L, 1     | N-CH<br>ONOL | IANNI<br>ITH: | EL,<br>IC |             |

| DEPARTMEN                               | T OF D              | EFENSI           | Ē   | DRAW | ING AP | PROVAL<br>3-06-1 |      |    |       | 675         |                     |             |              |             | Γ -          | ·,       |              |               |           |             |

| AMSC N/A                                |                     |                  |     | REVI | SION L | EVEL             |      |    |       | SIZ<br>A    | ĸ                   |             | 726          |             |              |          | 62-          | 3848          | 30        |             |

| DE00                                    |                     |                  |     |      |        |                  |      |    |       | SHE         | ET                  |             | 1            |             | OI           | =        |              | 35            |           | 1           |

| DESC FORM 193<br>JUL 91                 |                     |                  |     |      |        |                  |      |    |       |             |                     |             |              |             |              |          |              |               |           |             |

<u>DISTRIBUTION STATEMENT A.</u> Approved for public release; distribution is unlimited.

5962-E141-93

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes B, Q, and M) and space application (device classes S and V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

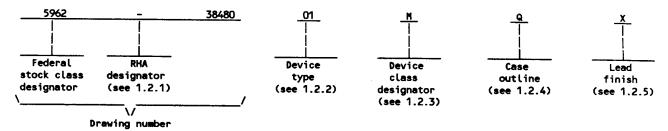

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device classes M, B, and S RHA marked devices shall meet the MIL-M-38510 specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type   | <u>Generic number</u> | Clock frequency | <u>Circuit function</u>                 |

|---------------|-----------------------|-----------------|-----------------------------------------|

| 01            | z08400                | 4.0 MHz         | 8-bit, fixed instruction microprocessor |

| 02            | z08400                | 2.5 MHz         | 8-bit, fixed instruction microprocessor |

| 03 <u>1</u> / | z08400                | 6.0 MHz         | 8-bit, fixed instruction microprocessor |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

| Device class | Device requirements documentation                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------|

| н            | Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883 |

| B or S       | Certification and qualification to MIL-M-38510                                                                          |

| Q or V       | Certification and qualification to MIL-I-38535                                                                          |

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | <u>Descriptive designator</u> | <u>Terminals</u> | Package style                          |

|----------------|-------------------------------|------------------|----------------------------------------|

| Q              | GDIP1-T40 or CDIP2-T40        | 40               | Dual-in-line                           |

| x <u>1</u> /   | CQCC1-N44A                    | 44               | Square leadless chip carrier, option A |

| Y <u>1</u> /   | CQCC1-N44B                    | 44               | Square leadless chip carrier, option B |

$\underline{1}$ / Not available from an approved source of supply.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-38480 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 2    |

| DESC FORM 193A                                                  |           |                |            |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-M-38510 for classes M, B, and S or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference. 1.3 Absolute maximum ratings. 1/ Maximum power dissipation,  $(P_D)$ : 1.0 W 270°C Maximum junction temperature (T<sub>j</sub>) - - - - - - - - - -170°C 2/ Thermal resistance, junction to case  $(\Theta_{JC})$ ------See MIL-STD-1835 1.4 Recommended operating conditions. 4.5 V minimum to 5.5 V maximum Minimum high-level input voltage v<sub>cc</sub> -0.6 v Logic inputs (V<sub>IL</sub>)-----+0.8 V Clock input (VILC) - - - - - - - - - Frequency of operation +0.45 V 0.5 to 4.0 MHz 0.5 to 2.5 MHz 0.5 to 6.0 MHz Case operating temperature range - - - - - - - - - --55°C to +125°C Clock rise time (t<sub>r</sub>) Device types 01 and 02 - - - - - - - - - - - - - -30 ns maximum 20 ns maximum Clock fall time (t<sub>f</sub>)

Fault coverage measurement of manufacturing

1.5 <u>Digital logic testing for device classes Q and V</u>.

logic tests (MIL-STD-883, test method 5012) . . . . . XX percent 3/

Device types 01 and 02 - - - - - - - - - - - - -

Device type 03 - - - - - - - - - - - - - - - - - -

30 ns maximum

20 ns maximum

<sup>3</sup>/ Values will be added when they become available.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-38480 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 3    |

DESC FORM 193A

Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operating at the maximum levels may degrade performance and affect reliability.

<sup>2/</sup> Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening condition per method 5004 of MIL-STD-883.

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specifications, standards, bulletin, and handbook</u>. Unless otherwise specified, the following specifications, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

## **SPECIFICATIONS**

**MILITARY**

MIL-M-38510 - Microcircuits, General Specification for.

MIL-I-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### **STANDARDS**

**MILITARY**

MIL-STD-480 - Configuration Control-Engineering Changes, Deviations and Waivers.

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-1835 - Microcircuit Case Outlines.

## BULLETIN

MILITARY

MIL-BUL-103 - List of Standardized Military Drawings (SMD's).

## HANDBOOK

MILITARY

MIL-HDBK-780 - Standardized Military Drawings.

(Copies of the specifications, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. For device classes B and S, a full electrical characterization table for each device type shall be included in this SMD. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein.

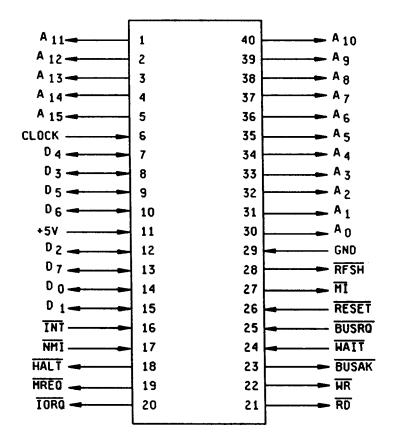

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

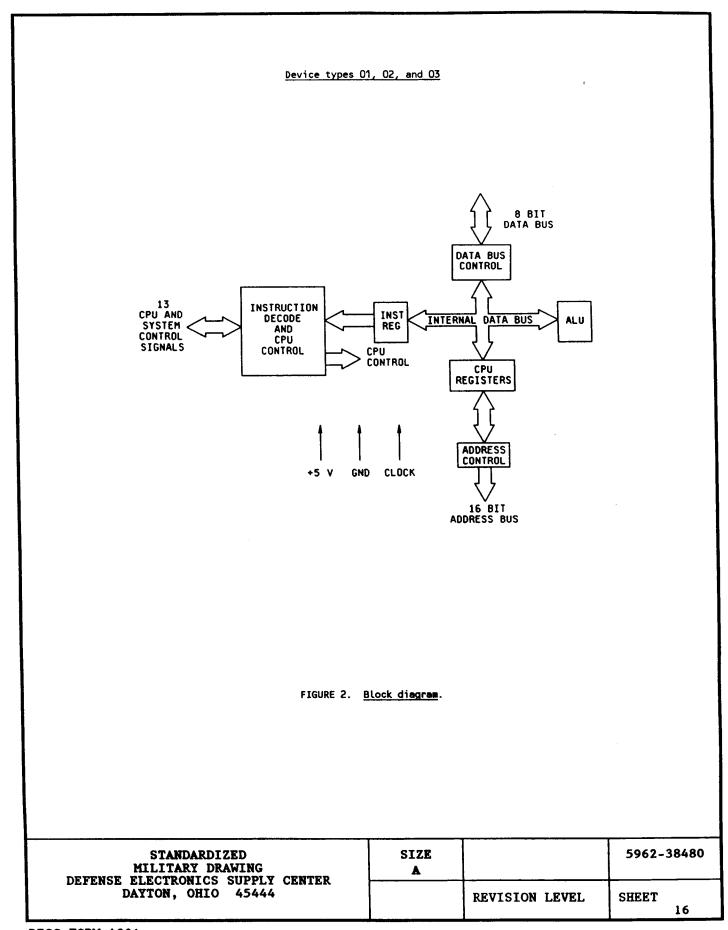

- 3.2.3 Block diagrams. The block diagram shall be as specified on figure 2.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-38480 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>4 |

DESC FORM 193A

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes B and S shall be in accordance with MIL-M-38510. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes B and S shall be a "J" or "JAN" as required in MIL-M-38510. The certification mark for device classes Q and V shall be a "QML" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.3 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.2 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or device classes B and S in MIL-M-38510 or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-480.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device classes M, B, and S</u>. Device classes M, B, and S devices covered by this drawing shall be in microcircuit group number 107 (see MIL-M-38510, appendix E).

- 3.11 <u>Serialization for device class S</u>. All device class S devices shall be serialized in accordance with MIL-M-38510.

- 3.12 PIN supersession information. Pin supersession information shall be as specified in the appendix.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein). For device classes B and S, sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 and the device manufacturer's QM plan.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-38480 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 5    |

| Test                                      | Symbol           | Conditions<br>  -55°C ≤ T <sub>C</sub> ≤ +125°C<br>  unless otherwise specified | Refer.<br>No      | Group A subgroups | Device<br>type | <br>                     | imits                 | Unit        |

|-------------------------------------------|------------------|---------------------------------------------------------------------------------|-------------------|-------------------|----------------|--------------------------|-----------------------|-------------|

|                                           |                  | unless otherwise specified<br>  <u>1</u> / 4.5 ≤ V <sub>CC</sub> ≤ 5.5 V        | <u>2</u> /        | i                 | <br> <br>      | <br>  Min<br>            | Max                   | i<br>       |

| lock input low voltage                    | v <sub>ILC</sub> | V <sub>CC</sub> = 4.5 V                                                         |                   | 1,2,3             | ALL            | -0.3                     | 0.45                  | v           |

| lock input high voltage                   | A <sup>IHC</sup> | V <sub>CC</sub> = 4.5 V                                                         |                   | 1,2,3,            | ALL            | ν <sub>c</sub> ε<br>δ. 6 | V <sub>CG</sub> + 0.3 | V           |

| Input low voltage                         | v <sub>IL</sub>  | <br> V <sub>CC</sub> = 4.5 V                                                    |                   | 1,2,3             | ALL            | -0.3                     | 0.8                   | <br>  V<br> |

| input high voltage                        | V <sub>IH</sub>  | <br> V <sub>CC</sub> = 4.5 V                                                    | <u> </u><br> <br> | 1,2,3,            | ALL            | 2.2                      | v <sub>cc</sub>       | V           |

| Output low voltage                        | VOL              | I <sub>OL</sub> = 1.8 mA V <sub>CC</sub> = 4.5 V                                | <br> <br>         | 1,2,3             | ALL            |                          | 0.4                   | V           |

| Output high voltage                       | V <sub>ОН</sub>  | I <sub>OH</sub> = -250 μA V <sub>CC</sub> = 4.5 V                               |                   | 1,2,3             | ALL            | 2.4                      |                       | v           |

| Power supply current                      | Icc              | v <sub>cc</sub> = 5.5 v                                                         |                   | 1,2,3             | ALL            |                          | 250                   | mA          |

| Input leakage current,<br>low             | I <sub>IL1</sub> | V <sub>IN</sub> = 0.4 V<br> V <sub>CC</sub> = 5.5 V                             |                   | 1,2,3             | ALL            | -10                      | +10                   | μΑ          |

| Input leakage current,<br>high            | I IH1            | V <sub>IN</sub> = 2.4 V<br>V <sub>CC</sub> = 5.5 V                              |                   | 1,2,3             | ALL            | -10                      | +10                   | μ           |

| Tristate output leakage,<br>current, low  | IZL              | V <sub>OUT</sub> = 0.4 V<br>V <sub>CC</sub> = 5.5 V                             |                   | 1,2,3             | ALL            | -10                      | +10                   | μΑ          |

| Tristate output leakage,<br>current, high | IZH              | V <sub>OUT</sub> = 2.4 V<br>  V <sub>CC</sub> = 5.5 V                           |                   | 1,2,3             | ALL            | -10                      | +10                   | μA          |

| Input leakage current,<br>low-data bus    | I <sub>IL2</sub> | V <sub>IN</sub> = 0.4 V<br> V <sub>CC</sub> = 5.5 V                             |                   | 1,2,3             | ALL            | -10                      | <br>  +10<br>         | μA          |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-38480 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>6 |

|                                                                       | Test                    | Symbol            | Conditions<br>  -55°C ≤ T <sub>C</sub> ≤ +125°C                                | Refer.         | Group A<br>subgroups | Device<br>type | Li         | mits       | Unit      |

|-----------------------------------------------------------------------|-------------------------|-------------------|--------------------------------------------------------------------------------|----------------|----------------------|----------------|------------|------------|-----------|

|                                                                       |                         | <br>              | unless otherwise specified<br>  <u>1</u> / 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br> | <u>2</u> /<br> | 1<br> <br>           |                | Min        | Max        |           |

| input leakag<br>nigh-data bu                                          |                         | I IH2             | V <sub>IN</sub> = 2.4 V<br>  V <sub>CC</sub> = 5.5 V                           |                | 1,2,3                | ALL            | -10        | +10        | μА        |

| Clock capaci                                                          | tance                   | cc                | f = 1 MHz,<br> T <sub>C</sub> = +25°C; from input or                           |                | 4                    | ALL            |            | 35         | pF        |

| Input capaci<br>all other                                             |                         | c <sub>I</sub>    | output pin to ground, all other pins at ground see 4.4.1c                      |                | 4                    | ALL            |            | 5          | pF        |

| Output capac<br>all outputs                                           | itance,<br>and data bus | c <sub>o</sub>    | 1<br>1<br>1                                                                    |                | 4                    | ALL            |            | 15         | pF        |

| Functional t                                                          | est                     |                   | <br> see 4.4.1b<br>                                                            |                | 7,8                  | ALL            |            |            | <br> <br> |

| Maximum cloc                                                          | k frequency             | † <sub>MAX</sub>  | V <sub>CC</sub> = 4.5 V                                                        | <u> </u>       | <u> </u>             | 01             | 4.0        | l<br>I     | l         |

|                                                                       | •                       | 1100              | V <sub>CC</sub> = 4.5 V<br>  C <sub>L</sub> = 50 pF ±10%                       | <u> </u><br>   | 9,10,11              | 02             | 2.5        | <br>       | MHz       |

|                                                                       |                         |                   |                                                                                | <u> </u>       | <u> </u>             | 03             | 6.0        | İ          | <u> </u>  |

| Maximum clock frequency                                               |                         | MAX               | V <sub>CC</sub> = 5.5 V<br> C <sub>L</sub> = 50 pF ± 10%                       |                | i                    | 01             | 4.0        | <u> </u>   | i<br>I    |

|                                                                       |                         | <u> </u>          | <b>-</b>                                                                       | <u> </u>       | 9,10,11              | 02             | 2.5        | <u> </u>   | MHz       |

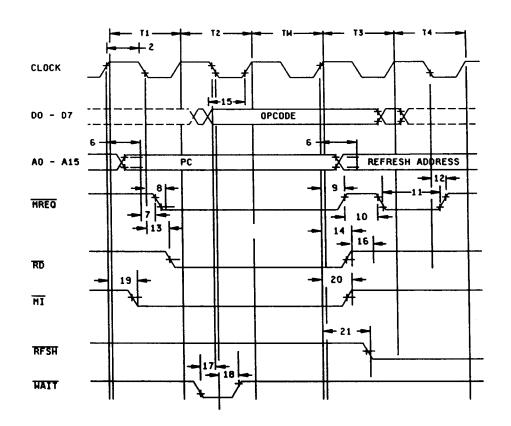

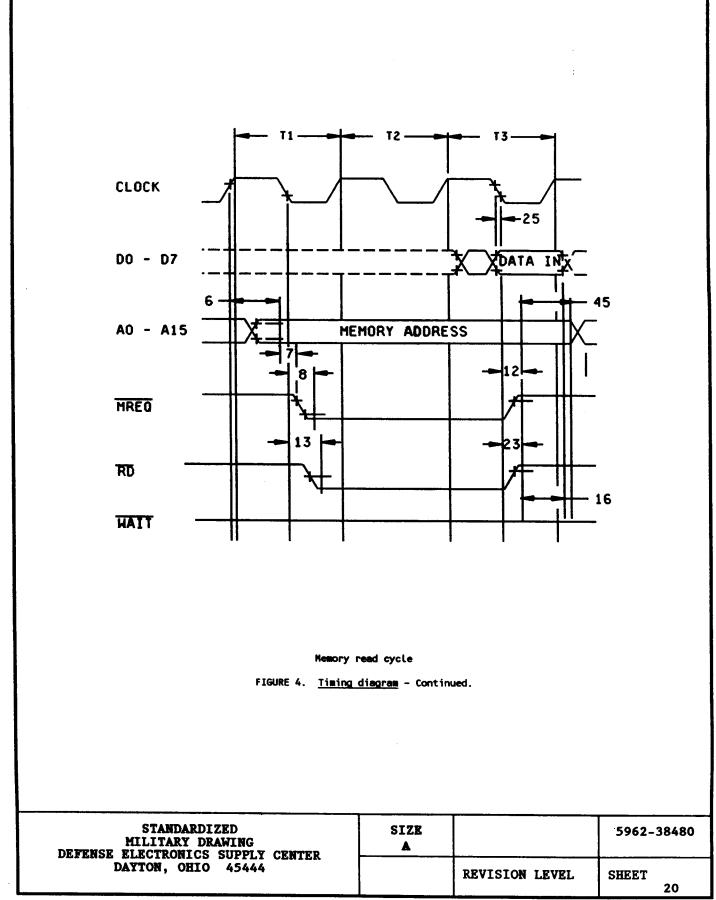

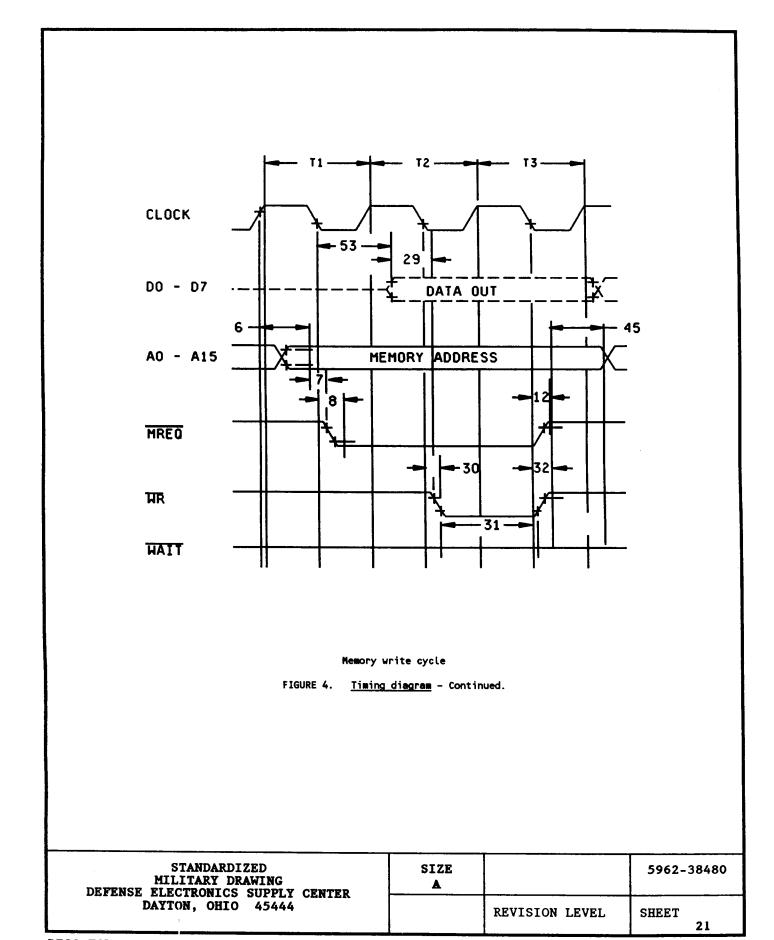

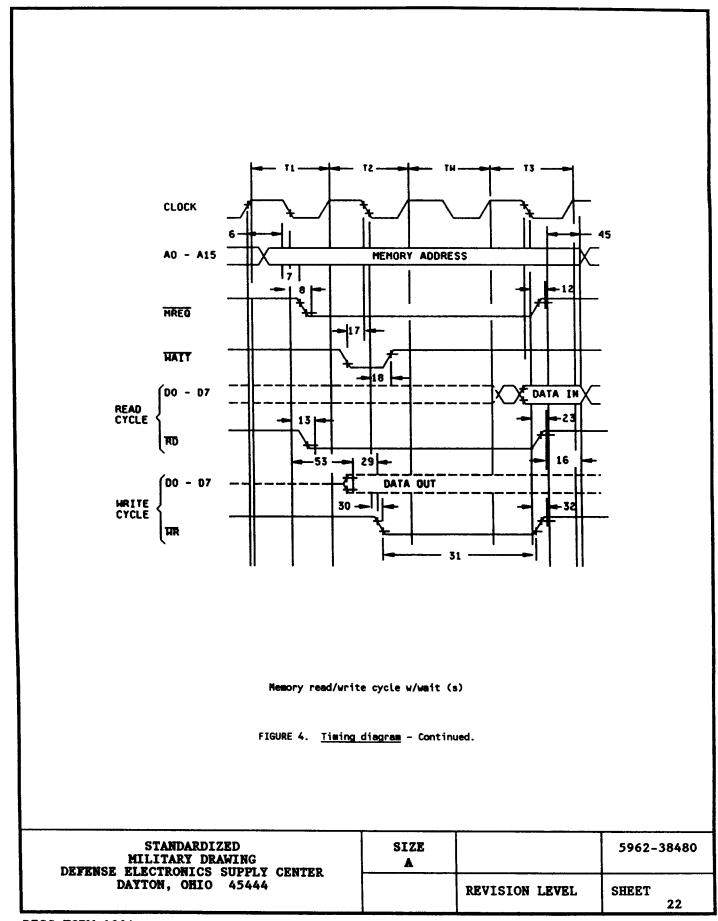

| Clock cycle                                                           | time                    | t <sub>cyc</sub>  | V <sub>00</sub> = 4.5 V                                                        | 1 .            | 1                    | 03             | 6.0<br>250 | <u> </u>   | <u> </u>  |

| •                                                                     |                         | Cyc               | V <sub>CC</sub> = 4.5 V<br> unless otherwise specified;                        |                | į                    | 02             | 400        |            |           |

|                                                                       |                         |                   | C <sub>L</sub> = 140 pF ± 10%<br>see figures 4 and 5                           | 1              | 9,10,11              | 03             | 165        | <u>3</u> / | ns        |

| Clock time                                                            | Rise                    | tr                | -                                                                              | 5              | 9,10,11              | 01,02          |            | 30         | ns        |

|                                                                       |                         | <u> </u>          | _                                                                              | ļ              |                      | 03             |            | 20         | <u> </u>  |

|                                                                       | Fall<br>                | t <sub>f</sub>    |                                                                                | 4              | 9,10,11              | 01,02          |            | 30         | ns        |

| Clock pulse                                                           | 1                       | <del> </del>      | -                                                                              | ļ              | <u> </u>             | 03             | 440        | 20         | <u> </u>  |

| width high                                                            |                         | t <sub>PWH1</sub> | 1                                                                              | 2              | 9,10,11              | 01             | 110<br>180 | 2,000      | -         |

|                                                                       |                         | rwni              | į                                                                              | į              | ' '                  | 03             | 65         | 2,000      | ns        |

| Clock pulse<br>width low                                              |                         | tPWL1             | _                                                                              |                |                      | 01             | 110        | 2,000      |           |

|                                                                       |                         | ļ                 |                                                                                | 3              | 9,10,11              | 02             | 180        | 2,000      | ns        |

|                                                                       |                         |                   |                                                                                |                |                      | 03             | 65         | 2,000      | -         |

| MREQ pulse<br>width high                                              |                         | t <sub>PWH2</sub> |                                                                                | 10             | 9,10,11              | ALL            | <u>4</u> / |            | ns        |

| See foo                                                               | tnotes at end           | of table          | •                                                                              | <u>l</u>       |                      |                | L          |            |           |

|                                                                       | MILIT                   | NDARDI:           | AWING                                                                          | SIZE           |                      |                |            | 596        | 52-3848   |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                         | SUPPLY CENTER -   |                                                                                | REVI           | SION LE              | VEL            | SHEE       | —<br>ЕТ    |           |

| Test                                                                               | Symbol             | Conditions   -55°C ≤ T <sub>C</sub> ≤ +125°C   unless otherwise specified                                        | Refer.<br>  No<br>  <u>2</u> /        | Group A<br>subgroups | Device<br>type       | L                        | imits        | Unit          |

|------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|--------------------------|--------------|---------------|

|                                                                                    | į                  | 1/ 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V                                                                               | =·                                    | <br>                 |                      | Min                      | Max          |               |

| IREQ Pulse<br>vidth low                                                            | tPWL2              | V <sub>CC</sub> = 4.5 V<br> unless otherwise specified;<br> C <sub>L</sub> = 140 pF ±10%<br> see figures 4 and 5 | 11                                    | 9,10,11              | ALL                  | <u>5</u> /               |              | ns            |

| JR pulse width low                                                                 | t <sub>PWL</sub> 3 |                                                                                                                  | 31                                    | 9,10,11              | ALL                  | <u>6</u> /               | <br> <br>    | ns            |

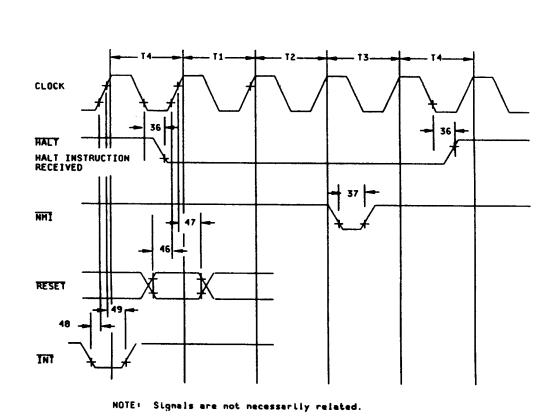

| NMI pulse width low                                                                | tPWL4              |                                                                                                                  | <b>37</b><br>                         | 9,10,11              | 01,02                | <b>80</b><br>70          |              | ns            |

| Data setup to clock †<br>(DO - D7)                                                 | t <sub>szH1</sub>  |                                                                                                                  | 15                                    | 9,10,11              | 01<br>02<br>03       | 35<br>50<br>30           |              | <br> <br>  ns |

|                                                                                    | tszL1              |                                                                                                                  | <u> </u><br>                          |                      | 01<br>02<br>03       | 35<br>50<br>30           |              |               |

| WAIT setup to clock ↓                                                              | t <sub>SLH1</sub>  | :<br> <br> -<br>                                                                                                 | 17                                    | 9,10,11              | 01,02<br>03<br>01,02 | 70<br>60<br>70           |              | ns            |

| Data setup to clock ↓ (DO - D7)                                                    | tszH2              |                                                                                                                  | 25                                    | 9,10,11              | 03 01 02 03          | 60<br>50<br>60<br>40     |              | ns            |

|                                                                                    | tszL2              |                                                                                                                  |                                       |                      | 01<br>02<br>03       | 50<br>60<br>40           | .            | -<br> <br>    |

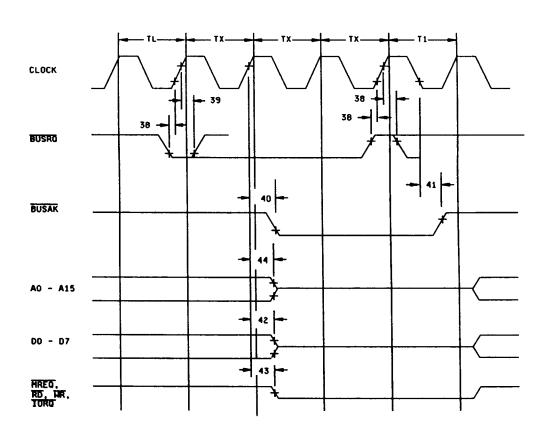

| BUSRQ setup to clock 1                                                             | t <sub>SLH2</sub>  |                                                                                                                  | 38                                    | 9,10,11              | 01<br>02<br>03       | 50<br>80<br>50           |              | ns            |

|                                                                                    | t <sub>SHL2</sub>  |                                                                                                                  |                                       |                      | 01<br>02<br>03       | 50<br>80<br>50           | -            |               |

| RESET setup to clock †                                                             | t <sub>SLH</sub> 3 |                                                                                                                  | 46                                    | 9,10,11              | 01 02 03             | 60                       |              | ns            |

|                                                                                    | t <sub>SHL</sub> 3 |                                                                                                                  |                                       |                      | 01<br>02<br>03       | 60<br>90<br>60           |              |               |

| INT setup to clock †                                                               | t <sub>SLH4</sub>  | -<br> <br> -                                                                                                     | 48                                    | 9,10,11              | 01,02                | 80                       | _            | ns            |

| Data valid after RD ↑                                                              | t <sub>SHL4</sub>  | _                                                                                                                | 16                                    | 9,10,11              | 01,02<br>03<br>All   | <u>80</u><br>  70<br>  0 | -!<br>-!<br> | <br> <br>     |

| (DO - D7)                                                                          | t <sub>HHZ1</sub>  | -                                                                                                                |                                       |                      |                      | <u> </u>                 |              |               |

| See footnotes at end of                                                            | table.             | -d                                                                                                               | 1                                     |                      | 1.,                  | <u>l , </u>              | <del></del>  |               |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                    | AWING                                                                                                            | SIZE                                  |                      |                      |                          | 59           | 62-3848       |

|                                                                                    |                    | SUPPLY CENTER 45444                                                                                              | · · · · · · · · · · · · · · · · · · · | REVI                 | SION LE              | EVEL                     | SHE          | ET<br>8       |

| Test                                                              | Symbol   Conditions<br>  -55°C ≤ T <sub>C</sub> ≤ +125°C  <br>  unless otherwise specified | No s                                                                                                             | Group A<br>subgroups | Device  <br>  type | Limits   |             | Unit      |          |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|----------|-------------|-----------|----------|

|                                                                   | <br> <br>                                                                                  | unless otherwise specified<br>1/ 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V                                                 | <u>2</u> /<br>       | <br>               |          | Min         | Max       |          |

| AIT valid after clock ↓                                           | t <sub>HLH1</sub>                                                                          | V <sub>CC</sub> = 4.5 V<br> unless otherwise specified;<br> C <sub>L</sub> = 140 pF ±10%<br> see figures 4 and 5 | <br>                 |                    | ALL      | 0           |           | ns       |

|                                                                   | t <sub>HHL</sub> 1                                                                         |                                                                                                                  | 18                   | 9,10,11<br> <br>   | ALL      | 0           | <br> <br> | ns       |

| BURSQ valid after                                                 | t <sub>HLH2</sub>                                                                          | -                                                                                                                | 39                   | 9,10,11            | ALL      | <br>  0<br> |           | ns       |

|                                                                   | t <sub>HHL2</sub>                                                                          |                                                                                                                  | <br> <br>            |                    | ALL      | 0           | <br> <br> |          |

| RESET valid after<br>clock †                                      |                                                                                            | 47                                                                                                               | 9,10,11              | ALL                | 0        |             | ns        |          |

|                                                                   | t <sub>HHL</sub> 3                                                                         |                                                                                                                  |                      |                    | ALL      | 0           | <br> <br> | ns       |

| INT valid after clock ↑                                           | t <sub>HLH4</sub>                                                                          | -<br> <br> -<br>                                                                                                 | 49                   | 9,10,11            | ALL      | 0           |           | ns       |

|                                                                   | t <sub>HHL</sub> 4                                                                         |                                                                                                                  |                      | <br> <br> <br>     | ALL      | 0           |           | ns       |

| Clock † to address valid delay (A <sub>O</sub> -A <sub>15</sub> ) | ilid t <sub>PLH1</sub>                                                                     |                                                                                                                  | 6                    | 9,10,11            | 01       |             | 110       | _  ns    |

|                                                                   | t <sub>PHL1</sub>                                                                          | _                                                                                                                |                      | <u> </u>           | 03       | <u> </u>    | 90        | <u> </u> |

| Address valid to<br>MREQ ↓ delay                                  | t <sub>PLH2</sub>                                                                          | _                                                                                                                | 7                    | 9,10,11            | ALL      | 7/          | -         | ns       |

| Address stable before                                             | t <sub>PHL2</sub>                                                                          | _[                                                                                                               |                      |                    | <u> </u> | 8/          |           |          |

| IORQ \$                                                           | t <sub>PLH3</sub>                                                                          | _                                                                                                                | 26                   | 9,10,11            | ALL      | 8/          | -         | ns       |

| Clock T to address<br>float delay                                 | t <sub>PLZ1</sub>                                                                          | -<br>-                                                                                                           | 44                   | 9,10,11            | 01       | 1           | 90        | <br>ns   |

|                                                                   | t <sub>PHZ1</sub>                                                                          |                                                                                                                  |                      | <u> </u>           | 03       | <u> </u>    | 80        |          |

| See footnotes at end of                                           | table.                                                                                     |                                                                                                                  |                      |                    |          |             |           |          |

| MILI                                                              | ANDARDI<br>TARY DR                                                                         | AWING                                                                                                            | SIZE                 |                    |          | *1          | 59        | 62-3848  |

|                                                                   |                                                                                            | SUPPLY CENTER 45444                                                                                              |                      | REV                | SION L   | EVEL        | SHE       | ET<br>9  |

| Test                                                     | Symbol Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$ |                                                                                          | Refer.     | Group A subgroups  | Device<br>type | L             | imits    | Unit           |

|----------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------|------------|--------------------|----------------|---------------|----------|----------------|

|                                                          | i<br> <br>                                                     | unless otherwise specified<br>  <u>1</u> / 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V               | <u>2</u> / | <br> <br>          | !              | Min           | Max      | <u> </u><br> - |

| Ad <u>dres</u> s sta <u>bl</u> e from<br>MREQ ↑ , RD ↑ , | t <sub>PLH4</sub>                                              | V <sub>CC</sub> = 4.5 V<br> unless otherwise specified;<br> C <sub>L</sub> = 140 pF ±10% | 45         | 9,10,11            | ALL            | <u>9</u> /    |          | ns             |

| WR     Or TORQ                                           | t <sub>PHL4</sub>                                              | see figures 4 and 5                                                                      |            |                    |                | -             | <u>.</u> |                |

| Data stable before WR ↓                                  | t <sub>PZL1</sub>                                              |                                                                                          | 29         | 9,10,11            | ALL            | 10/           |          | l ns           |

| (memory write)                                           | t <sub>PZH1</sub>                                              |                                                                                          |            |                    |                |               | <u> </u> |                |

| Data stable before WR ↓ (I/O write)                      | t <sub>PZL2</sub>                                              |                                                                                          | 33         | <br> <br>  9,10,11 | ALL            | <u>11</u> /   |          | <br> <br>  n:  |

|                                                          | t <sub>PZH2</sub>                                              | 1                                                                                        | <u></u>    |                    |                | . <del></del> | İ        | İ              |

| Data stable from WR T                                    | t <sub>PLZ2</sub>                                              | LZ2                                                                                      | 35         | 9,10,11            | ALL            | 12/           |          | l n            |

|                                                          | t <sub>PHZ2</sub>                                              |                                                                                          | İ          |                    |                | _             | į        | İ              |

| Clock † to data float<br>delay                           | t <sub>PLZ3</sub>                                              |                                                                                          | 42         | 9,10,11            | 01,02          |               | 90       | <br>  n:       |

|                                                          | t <sub>PHZ3</sub>                                              |                                                                                          |            |                    | 03             |               | 80       | Ï              |

| Clock   to data valid delay                              | t <sub>PZL</sub> 3                                             |                                                                                          | 53         | 9,10,11            | 01             |               | 150      | l n            |

|                                                          | <sup>t</sup> PZH3                                              |                                                                                          | İ          |                    | 02             |               | 130      | <u> </u>       |

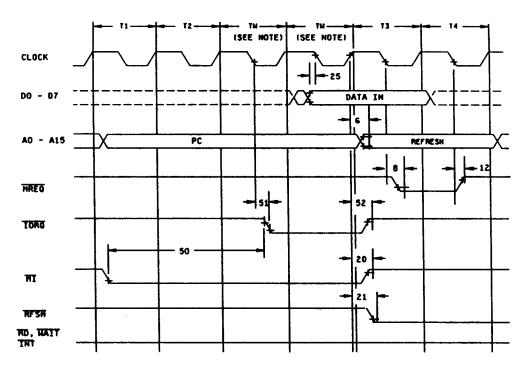

| Clock ↓ to MREQ ↓ delay                                  | t <sub>PHL5</sub>                                              |                                                                                          | 8          | 9,10,11            | 01             |               | 95       | n              |

| ***                                                      | 1                                                              | <u>. j</u>                                                                               | İ          |                    | 03             |               | 100      |                |

| Clock ↓ to MREQ ↑ delay                                  | <br> t <sub>PLH5</sub>                                         |                                                                                          | 12         | 9,10,11            | 01<br>02       |               | 95       | n              |

| See footnotes at end of                                  |                                                                | 1                                                                                        | 1          | 1                  | 03             | 1             | 1 70     | Ī              |

| ····    |                    |        |

|---------|--------------------|--------|

|         | STANDARDIZED       |        |

|         | MILITARY DRAWING   |        |

| DEFENSE | ELECTRONICS SUPPLY | CENTER |

|         | DAYTON, OHIO 45444 |        |

|         | ELECTRONICS SUPPLY | CENTER |

| SIZE |                | 5962-38480  |

|------|----------------|-------------|

|      | REVISION LEVEL | SHEET<br>10 |

| 1 4.5 × ≤ v <sub>CC</sub> ≤ 5.5 ∨                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Test                                  | -55°C ≤ T <sub>C</sub> ≤ +125°C   No subgroup    | Group A                                                        | Device<br>type | <u>.</u>      |             | Unit     |                                                |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|----------------------------------------------------------------|----------------|---------------|-------------|----------|------------------------------------------------|-----------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                                                  | unless otherwise specified  1/ 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V | <u>2</u> /<br> | <br> <br>     |             | Min      | <br>  Max                                      |           |

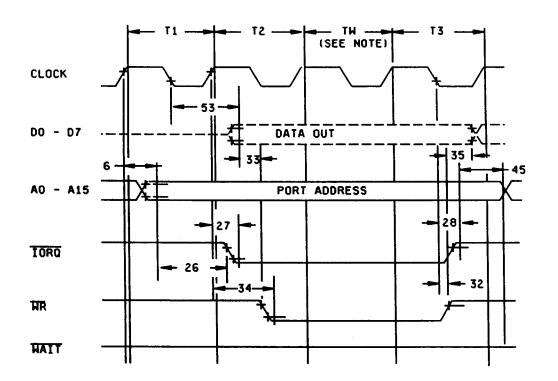

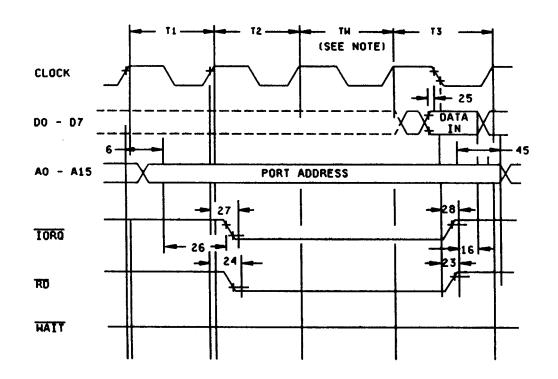

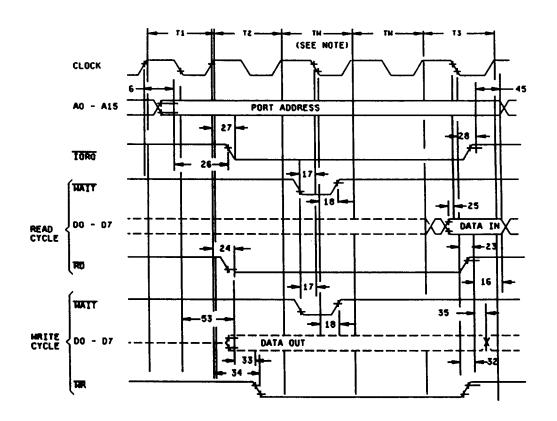

| See Figures 4 and 5   Clock † to IORQ   delay   t_{PH.T}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock † to MREQ † delay               | t <sub>PLH6</sub>                                | unless otherwise specified;                                    | 9              | 9,10,11       |             |          |                                                | ns        |

| Clock   to   IORQ   delay   tplh7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |                                                  |                                                                | ļ              | <u> </u>      |             |          |                                                |           |

| Clock   to   IORQ   delay   tplh7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Clock † to IORQ ↓ delay               | t <sub>nu z</sub>                                |                                                                | 27             | <br>  9,10,11 | 01          |          | 75                                             | ns        |

| Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard  | , ,                                   | j FAL                                            |                                                                | İ              |               |             |          |                                                | İ         |

| Clock   to   TORQ   delay   t_{PLH8}   28   9,10,11   01   85   ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Clock t to TOPO t delay               | 1.                                               | -                                                              | 52             | 9 10 11       | 1           |          | 1                                              | ne .      |

| Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard   Standard  | ctock   to long   detay               | PLH7                                             |                                                                | 52             | 9,10,11       | 02          |          | 100                                            | 115       |

| Clock   to   IORQ   delay   tphL8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | <del>                                     </del> | -                                                              | -              |               | 1 03        |          | <u>  70                                   </u> | 1         |

| Clock   to   IORQ   delay   the to   to   To   to   to   To   to   to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clock ↓ to IORQ ↑ delay               | t <sub>PLH8</sub>                                |                                                                | 28             | 9,10,11       |             |          |                                                | ns        |