REVISIONS **APPROVED** DATE DESCRIPTION LTR Add one yendor CAGE 18324. 25 June Change parameters in table I. 1987 Add program procedure B. Update vendor's part numbers Change screening and group A inspection. REV PAGE Α Α REV A **REV STATUS** 9 **h**o OF PAGES PAGES 1 2 5 **Defense Electronics** Roones This drawing is available for use by **Supply Center** all Departments and Agencies of the Dayton, Ohie Department of Defense TITLE: MICROCIRCUITS, 1K x 8 REGISTERED PROM WITH PROGRAMMABLE INITIALIZE, Original date MONOLITHIC SILICON of drawing: CODE IDENT. NO. DWG NO. SIZE 5962-86706 9 October 1986 14933 OF 23 REV PAGE AMSC N/A Α 5962-E347

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

DESC FORM 193

MAY 86

- 1. SCOPE

- 1.1 Scope. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

- 1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1 Device type. The device type shall identify the circuit function as follows:

| Device type | Generic number            | Circuit function                                                         | Access time   |

|-------------|---------------------------|--------------------------------------------------------------------------|---------------|

| 01          | 27S35<br>82HS187A         | 1024 x 8 bit registered PROM with programmable INITIALIZE (Asynchronous) | 45 ns         |

| 02          | 27S35A<br>82HS187A        | 1024 x 8 bit registered PROM with programmable INITIALIZE (Asynchronous) | <b>4</b> 0 ns |

| 03          | 27537<br>82HS1 <b>89A</b> | 1024 x 8 bit registered PROM with programmable INITIALIZE (Synchronous)  | 45 ns         |

| 04          | 27S37A<br>82HS189A        | 1024 x 8 bit registered PROM with programmable INITIALIZE (Synchronous)  | 40 ns         |

1.2.2 Case outlines. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

| Outline letter   | Case outline                                                                                                                                                                                   | Gpw3                                                           |    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----|

| L<br>K<br>3<br>X | D-9 (24-lead, 1/4" x 1 1/4"), dual-in-line pact<br>F-6 (24-lead, 3/8" x 5/8"), flat package<br>C-4 (28-terminal, .450" x .450"), square chip<br>C-12 (32-terminal, .450" x .550"), rectangular | carrier package chyptical carrier package chip carrier package | 20 |

| MILITARY DRAWING                               | SIZE | 149 |     | 52-86706 |   |

|------------------------------------------------|------|-----|-----|----------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |      | ŔE  | v A | PAGE     | 2 |

1.3 Absolute maximum ratings. -0.5 V dc to +7.0 V dc DC input voltage - - - - - - - - - - - - - - - - --0.5 V dc to +5.5 V dc -0.5 V dc to +5.5 V dc -30 mA to +5.0 mA Storage temperature range - - - - - - - - - - --65°C to +150°C Maximum power dissipation (Pp) 1/- - - - - - Lead temperature (soldering, 10 seconds) - - - - -1.02 W 300 C Thermal resistance, junction-to-case (0JC) 2/:

Cases K and L------See MIL-M-38510, appendix C Case 3 - - - - - - - - - - - - - - - -80°C/W 3/ 75°C/W 3/ Junction temperature (T<sub>J</sub>) ---------21 V dc DC voltage applied to outputs during programming - - -DC current into outputs during programming (max duration of 1.0 s)------250 mA dc 1.4 Recommended operating conditions. 4.5 V dc minimum to 5.5 V dc maximum 2.0 V dc 0.8 V dc -55°C to +125°C 2. APPLICABLE DOCUMENTS 2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein. **SPECIFICATION** MILITARY MIL-M-38510 - Microcircuits, General Specification for. **STANDARD MILITARY** MIL-STD-883 - Test Methods and Procedures for Microelectronics. (Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.) 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence. 3. REQUIREMENTS 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. Must withstand the added  $P_D$  due to short circuit test (e.g.,  $I_{SC}$ ). Heat sinking is recommended to reduce the junction temperature. When a thermal resistance value for this case is included in MIL-M-38510, appendix C, that value 3/ shall supersede the value indicated herein. DWG NO. CODE IDENT. NO. SIZE MILITARY DRAWING 14933 5962-86706 A DEFENSE ELECTRONICS SUPPLY CENTER 3 REV PAGE DAYTON, OHIO

- 3.2 Design, construction, and physical dimensions. The design, construction and physical dimensions shall be as specified in MIL-M-38510 and herein.

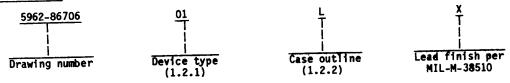

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

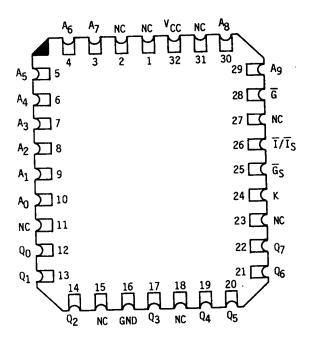

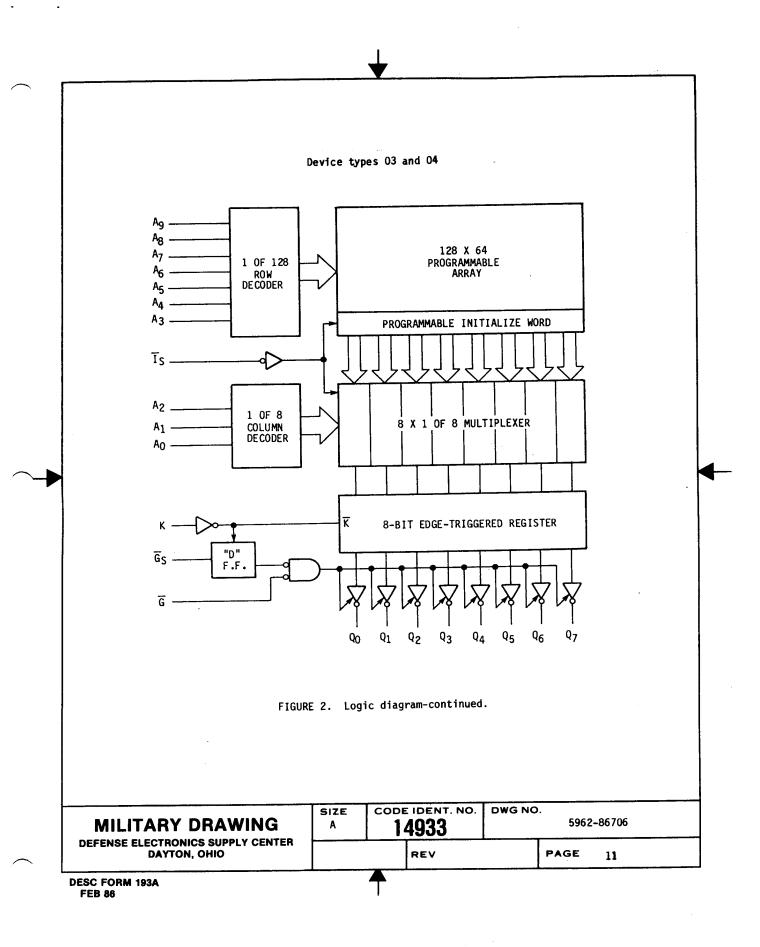

- 3.2.2 Logic diagram. The logic diagram shall be as specified on figure 2.

- 3.2.3 Truth tables.

- 3.2.3.1 Unprogrammed devices. Testing to the applicable truth table, or alternate testing as specified in 4.3.1.d, shall be used for unprogrammed devices for contracts involving no altered item drawing. When testing is required per 4.3 herein, the devices shall be programmed by the manufacturer prior to test in a checkerboard pattern (a minimum of 50 percent of the total number of bits programmed) or to any altered item drawing pattern which includes at least 25 percent of the total number of bits programmed.

- 3.2.3.2 <u>Programmed devices</u>. The truth table for programmed devices shall be as specified by an altered item drawing.

- 3.2.4 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full recommended case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.4 herein

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.9 <u>Processing options</u>. Since the PROM is an unprogrammed memory capable of being programmed by either the manufacturer or the user to result in a wide variety of PROM configurations, two processing options are provided for selection, using an altered item drawing.

- 3.9.1 Unprogrammed PROM delivered to the user. All testing shall be verified through group A testing as defined in 4.3.1(d). It is recommended that users perform subgroups 7 and 9 after programming to verify the specific program configuration.

- 3.9.2 Manufacturer-programmed PROM delivered to the user. All testing requirements and quality assurance provisions herein, including the requirements of the altered item drawing shall be satisfied by the manufacturer prior to delivery.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 | DWG NO.<br>5962-86706 |   |

|-----------------------------------------------------------------|------|-------|-----------------------|---|

|                                                                 |      | REV   | PAGE                  | 4 |

|   | ł |   |  |

|---|---|---|--|

| _ | L | _ |  |

| 7 |   | • |  |

| Test                         | <br> Symbol<br>  | -55°C < T <sub>C</sub> < +125°C<br>4.5 V < V <sub>CC</sub> < 5.5 V                                                                                 |         | Group A<br>subgroups | Lin<br>Min    | nits<br>Max    | Unit                 |

|------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|---------------|----------------|----------------------|

| Output high voltage          | V <sub>OH</sub>  | (unless otherwise specified)<br> V <sub>CC</sub> = 4.5 V,<br> V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> ,<br> I <sub>OH</sub> = -2.0 mA | A11     | 1, 2, 3              | 2.4           |                | ٧                    |

| Output low voltage           | V <sub>OL</sub>  |                                                                                                                                                    | A11     | 1, 2, 3              | <br>          | 0.50           | V                    |

| Input high voltage           | ν <sub>IH</sub>  | 1/ 2/                                                                                                                                              | A11     | 1, 2, 3              | 2.0           | <br> <br>      | ٧                    |

| Input low voltage            | V <sub>IL</sub>  | <u>1</u> / <u>2</u> /                                                                                                                              | A11     | 1, 2, 3              | <br> <br>     | 0.8            | V                    |

| Input clamp voltage          | A <sup>IC</sup>  |                                                                                                                                                    | A11     | 1, 2, 3              | <br> <br>     | -1.2           | ٧                    |

| Input low current            | I IL             | <br> V <sub>CC</sub> = 5.5 V,<br> V <sub>IN</sub> = 0.45 V                                                                                         | All     | 1, 2, 3              | <br>          | <br> -250<br>  | <br>  μ <b>Α</b><br> |

| Input high current           | IIH              |                                                                                                                                                    | A11     | 1, 2, 3              | <br> <br>     | l<br>l 50<br>l | !<br>  μ <b>Α</b>    |

| Output short-circuit current | ISC              | $ V_{CC}  = 5.5 \text{ V}, V_{OUT} = 0 \text{ V}$                                                                                                  | A11<br> | 1 1, 2, 3            | <br>  -15<br> | <br>  -90<br>  | i mA<br>i            |

| Power supply current         | Icc              | V <sub>CC</sub> = 5.5 V,<br> ATT inputs = GND                                                                                                      | All     | 1, 2, 3              |               | 185            | l mA                 |

| Output leakage<br>current    | ICEX             | V <sub>CC</sub> = 5.5 V, V <sub>0</sub> = 5.5 V                                                                                                    | A11     | 1, 2, 3              |               | 60<br>1        | μA                   |

|                              | <br>             | V <sub>G</sub> = 2.4 V   V <sub>0</sub> = 0.4 V                                                                                                    | A11     | 1, 2, 3              |               | <br>  -60<br>  | μA                   |

| Functional tests             |                  | <br> See 4.3.1(e)<br>                                                                                                                              | A11     | 7, 8                 |               | <br> <br>      |                      |

| Input capacitance            | IC <sub>IN</sub> | V <sub>IN</sub> = 2.0 V, f = 1.0 MHz                                                                                                               | A11     | 4                    |               | 10.0           | l pF                 |

| Output capacitance           | COUT             | V <sub>OUT</sub> = 2.0 V, f = 1.0 MHz                                                                                                              | A11     | 4                    |               | 13.0           | l pF                 |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 | DWG NO.<br>5962-86706 |   |

|-----------------------------------------------------------------|------|-------|-----------------------|---|

|                                                                 |      | REV A | PAGE                  | 5 |

| T                                            | ABLE I.              | Electrical performance charact                                                                                                              | eristics   | - continue           | ed.               |               |         |

|----------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|-------------------|---------------|---------|

| Test                                         | <br> Symbol<br> <br> | Conditions $-55^{\circ}C \leq T_C \leq +125^{\circ}C$ $4.5 \text{ V } \leq \text{ V}_{CC} \leq 5.5 \text{ V}$ [(unless otherwise specified) |            | Group A<br>subgroups | Lir<br>Min        | mits<br>  Max | Unit    |

| Address to K high, setup time                | <br> TAVKH<br>       | <u>5</u> /                                                                                                                                  |            | 9, 10, 11            | 40                |               | ns      |

|                                              | <u> </u><br>         |                                                                                                                                             | 01, 03<br> | 9, 10, N             | 45                | <u> </u>      | i ns    |

| Address to K high,<br>hold time              | TKHAX                | 5/                                                                                                                                          | A11        | 9, 10, 11            | 5                 | <br> <br>     | ns      |

| Delay from K high to output valid, for       | TKHQV1               | 5/                                                                                                                                          | 02, 04     | 9, 10, 11            |                   | <br>  25<br>  | ns      |

| initially active<br>outputs (high or<br>low) |                      | <br>                                                                                                                                        | 01, 03     | 9, 10, 11            |                   | 30            | ns      |

| K pulse width (high or low)                  | TKHKL,               | <u>5</u> /                                                                                                                                  | A11        | 9, 10, 11            | 25                | 1             | ns      |

| GS to K high setup<br>time                   | TGSVKH               | 5/                                                                                                                                          | A11        | 9, 10, 11            | <br>  15<br>      | ]<br>         | ns<br>l |

| GS to K high hold time                       | TKHGSX               | <u>5/</u>                                                                                                                                   | A11        | 9, 10, 11            | 5.0               | <br> <br>     | ns      |

| Delay from I low to output valid (high       | TILQV                | <u>5</u> /                                                                                                                                  | 01         | 9, 10, 11            |                   | 40            | ns      |

| or low) <u>6</u> /                           |                      | !<br> <br>                                                                                                                                  | 02         | 9, 10, 11            | <br>              | 35            | ns      |

| Asynchronous T recovery to K high 6/         | TIHKH                | 5/<br>  <u>5</u> /                                                                                                                          | 01, 02     | 9, 10, 11            | <br>  25<br> <br> | ]<br>         | ns      |

| Asynchronous T pulse width (low) 6/          | TTILIH               | <u>5</u> /                                                                                                                                  | 01, 02     | 9, 10, 11            | <br>  30<br>      |               | ns      |

| TS to K high setup time 7/                   | TISVKH               | <u>5</u> /                                                                                                                                  | 03         | 9, 10, 11            | 35                | <br>          | ns      |

| <del>_</del>                                 |                      | T .                                                                                                                                         |            | L                    |                   |               |         |

See footnotes at end of table.

| MILITARY DRAWING                               | SIZE | <br>1933 | <b>10</b> . | DWG NO<br>596 | 2-86706 |   |

|------------------------------------------------|------|----------|-------------|---------------|---------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |      | REV      | A           |               | PAGE    | 6 |

04 9, 10, 11 30

|                                               |                   |                                                                                                                       | Toot   Symbol   Conditions   Device Group A   Limits |                           |             |                   |           |  |  |  |  |  |

|-----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|-------------|-------------------|-----------|--|--|--|--|--|

| Test                                          | Symbol<br> <br>   | Conditions<br>  -55°C < T <sub>C</sub> < +125°C<br>  4.5 V < V <sub>CC</sub> < 5.5 V<br> (unless otherwise specified) |                                                      | Group A<br> subgroups<br> | Min         | mits<br>  Max<br> | Unit      |  |  |  |  |  |

| IS to K high hold<br>time <u>6</u> /          | TKHISX            | <br>  <u>5</u> /<br>                                                                                                  | 03, 04                                               | 9, 10, 11                 | 5           |                   | ns        |  |  |  |  |  |

| Delay from K high to<br>output valid for ini- | <br> <br> TKHQV2  | <br> <br> 5/                                                                                                          | 01, 03                                               | <br> 9, 10, 11<br>        |             | 35                | ns        |  |  |  |  |  |

| tially high-Z outputs                         | <br> <br>         | <b>-</b><br> <br>                                                                                                     | 02, 04                                               | 9, 10, 11                 |             | 30                | ns        |  |  |  |  |  |

| Delay from G low to                           | TGLQV             | <br>                                                                                                                  | 01, 03                                               | 9, 10, 11                 | <br> <br>   | 35                | ns        |  |  |  |  |  |

| output valid (high<br>or low)                 | <br> <br> <br>    |                                                                                                                       | 02, 04                                               | 9, 10, 11                 | !<br>!<br>! | ]<br>  30<br>     | l ns      |  |  |  |  |  |

| Delay from K high to                          | I<br>I TKHOZ      | <br>                                                                                                                  | 01, 03                                               | 9, 10, 11                 |             | 35                | l<br>l ns |  |  |  |  |  |

| output high-Z 8/                              |                   | <u> </u>                                                                                                              |                                                      | 9, 10, 11                 | l<br> <br>  | 30                | l<br>I ns |  |  |  |  |  |

| Delay from E high to                          | I<br>I<br>I TGHOZ | i<br> <br>  15/                                                                                                       | 01, 03                                               | 9, 10, 11                 |             | 35                | l<br>l ns |  |  |  |  |  |

| output high-Z 8/                              |                   | <u>                                     </u>                                                                          | 02, 04                                               | 9, 10, 11                 |             | 30                | ns        |  |  |  |  |  |

- 1/ These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- $^{2/}$  V<sub>IL</sub> and V<sub>IH</sub> threshold levels are guaranteed for 0.8 V and 2.0 V respectively during dc testing. For ac and functional testing V<sub>IL</sub> and V<sub>IH</sub> limits of -0.2 V and 4.0 V are implemented to allow for noise margins needed in a high speed, automated test equipment environment, when fast switching of multiple I/O's is encountered.

- 3/ Only one output should be shorted at a time. Duration of the short circuit should not be more than one second.

- These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

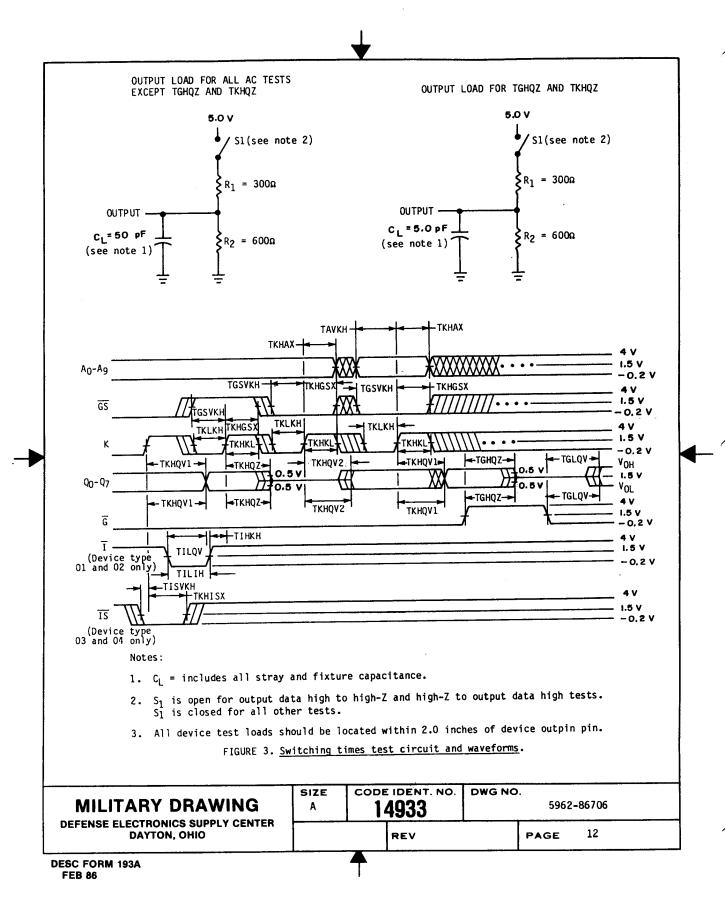

- 5/ AC tests are performed with input 10 to 90% rise and fall times of 5 ns or less.

- $\underline{6}/$  Applies only when programmable initialize is in the asynchronous operation mode.

- 7/ Applies only when programmable initialize is in the synchronous operation mode.

- 8/ TKHQZ and TGHQZ are measured to the V<sub>OH</sub> -0.5 V and V<sub>OL</sub> +0.5 V output levels respectively. All other switching parameters are tested from and to the 1.5 V threshold levels.

- 9/ All voltages given are referenced to the test system ground for ac and functional testing. Voltages given for dc testing are referenced to the microcircuit ground terminal.

| MILITARY DRAWING                               | SIZE<br>A | 14933 | DWG NO.<br>5962-86706 |   |

|------------------------------------------------|-----------|-------|-----------------------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |           | REV A | PAGE                  | 7 |

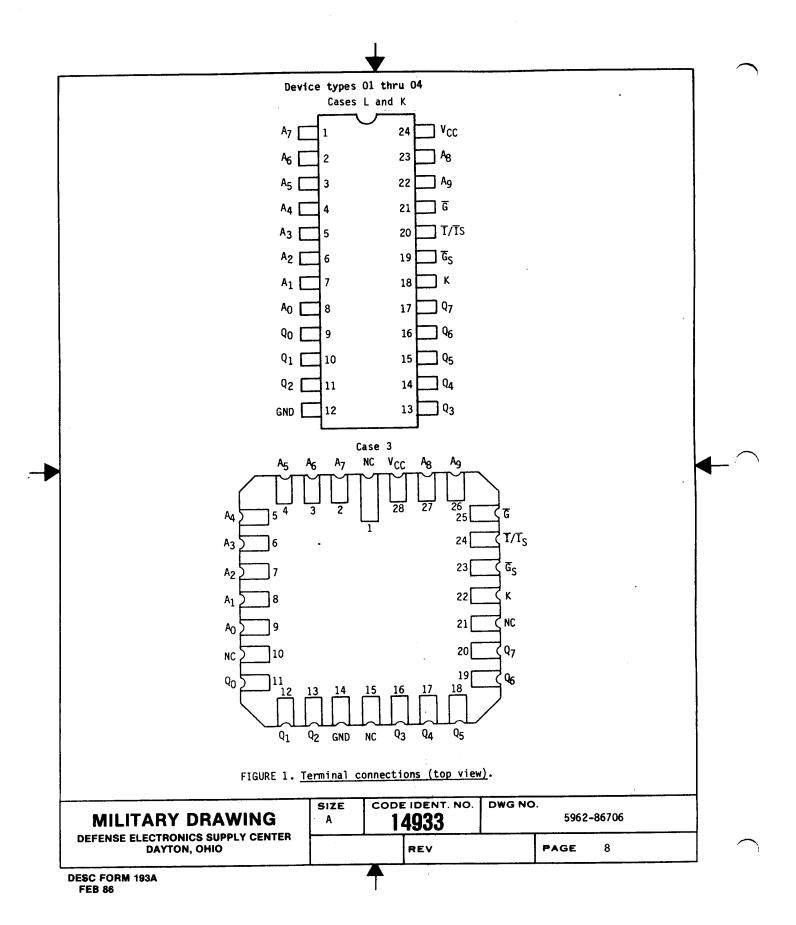

FIGURE 1. Terminal connections (top view) - continued.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE<br>A | A 14933 |  | DWG NO.<br>5962-86706 |   |  |

|-----------------------------------------------------------------|-----------|---------|--|-----------------------|---|--|

|                                                                 |           | REV     |  | PAGE                  | 9 |  |

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test (method 1015 of MIL-STD-883).

- (1) Test condition C or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- c. All devices processed to an altered item drawing may be programmed either before or after burn-in at the manufacturer's discretion. The required electrical testing shall include, as a minimum, the final electrical tests for programmed devices as specified in table II herein.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $C_{\rm IN}$  measurement) shall be measured only for the initial test and after process or design changes which may affect input capacitance.

- d. Unprogrammed devices shall be tested for programmability and ac performance compliance to the requirements of group A, subgroup 9, 10 and 11. Either of two techniques is acceptable:

- (1) Testing the entire lot using additional built-in test circuitry which allows the manufacturer to verify programmability and ac performance without programming the user array. If this is done, the resulting test patterns shall be verified on all devices during subgroups 9, 10, and 11, group A testing per the sampling plan specified in MIL-STD-883, method 5005.

- (2) If such compliance cannot be tested on an unprogrammed device, a sample shall be selected to satisfy programmability requirements prior to performing subgroups 9, 10, and 11. Twelve devices shall be submitted to programming (see 3.2.3.1). If more than two devices fail to program, the lot shall be rejected. At the manufacturer's option, the sample may be increased to 24 total devices with no more than four total device failures allowed. Ten devices from the programmability sample shall be submitted to the requirements of group A, subgroups 9, 10, and 11. If more than two total devices fail, the lot shall be rejected. At the manufacturer's option, the sample may be increased to 20 total devices with no more than four total device failures allowable.

- e. Subgroups 7 and 8 must verify input to output logic combinations.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 |      |

|-----------------------------------------------------------------|------|-------|------|

|                                                                 |      | REV A | PAGE |

## 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test (method 1005 of MIL-STD-883) conditions:

- Test condition  ${\tt C}$  or  ${\tt D}$  using the circuit submitted with the certificate of compliance (see 3.5 herein).

- $T_A = +125^{\circ}C$ , minimum. (2)

- Test duration: 1,000 hours, except as permitted by appendix B of MIL-M-38510 and method 1005 of MIL-STD-883.

- c. The group C, subgroup 1 sample shall include devices tested in accordance with 4.3.1.d.

TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                       | Subgroups<br>(per method<br>5005, table I) |

|---------------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters (method 5004)                         |                                            |

| Final electrical test parameters (method 5004)                      | 1*, 2, 3, 7, 8, 9,<br>10**, 11**           |

| Group A test requirements (method 5005)                             | 1, 2, 3, 7, 8, 9,<br>10**, 11**            |

| Groups C and D end-point<br>electrical parameters<br>(method 5005)  | 1, 2, 3, 7, 8,                             |

| Additional electrical subgroups<br>for group C periodic inspections |                                            |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 DWG NO. 5962-86706 |   |     |    |

|-----------------------------------------------------------------|------|--------------------------|---|-----|----|

|                                                                 |      | REV                      | P | AGE | 14 |

PDA applies to subgroup 1.

\* Subgroups 10 and 11, if not tested, shall be guaranteed to the limits specified in table I.

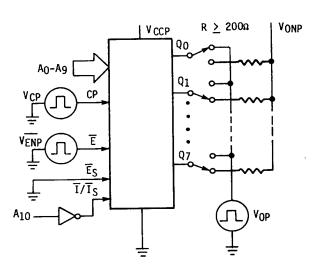

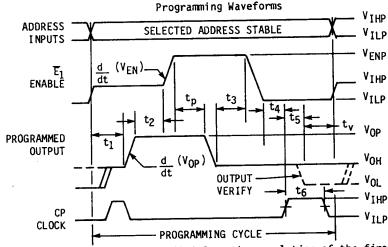

- a. Connect the device in the electrical configuration for programming as shown on figure 4. The waveforms on figure 4 and the programming procedures of table IIIA shall apply to these procedures.

- b. Terminate all outputs, to VONP through a pull up resistor, R.

- c. Apply VCCP to VCC.

- d. Connect G and Gs to VILP.

- e. Raise  $\overline{I}/\overline{I}_S$  input to  $V_{IHP}$ .

- f. Address the PROM with the binary address of the selected word to be programmed.

- g. Apply  $V_{IHP}$  to the  $\overline{G}$  input.

- h. After a delay of  $T_1$ , apply a low to high transition to the clock (K).

- i. After a delay of  $T_2$ , apply  $V_{0p}$  for a duration of  $T_3$  + (rise time of the enable input) +  $T_p$ , to the output selected for programming.

- j. After a delay of  $T_3$  + rise time of the programmed output, apply  $V_{FE}$  for a duration of  $T_P$  + rise time of the programmed output +  $T_4$ , to the G input. G is then reduced to  $V_{ILP}$ .

- k. After a delay of T5, the opening of the fuse is verified. Each data verification must be preceded by a Low to High transition of the clock (K). This will load the array data into the output data register. During verification,  $V_{CC}$  remains unchanged at  $V_{CCP}$ .

- The outputs should be programmed one at a time, since the internal decoding circuitry is capable of sinking only one unit of programming current at a time. Note that the PROM is supplied with fuses generating a low level logic output. Programming a fuse will cause the output to go to a high level logic in the verify mode.

- m. Repeat 4.4a through 4.4k for all other bits to be programmed.

- n. If any unit does not verify data as programmed, it shall be considered a programming reject.

- 4.4.1 Programming the initialized word.

- a. Repeat steps 4.4a through 4.4d.

- b. Connect  $T/I_S$  to  $v_{ILP}$ . This deselects the internal programming circuitry for all other addresses.

- c. The initialized word is then programmed, output by output, similar to any other address location, following 4.4g through 4.4n.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 | DWG NO.<br>5962-86706 |  |  |

|-----------------------------------------------------------------|------|-------|-----------------------|--|--|

|                                                                 |      | REV   | PAGE 15               |  |  |

|                                                       |                                    |              |                                           | i      |                | <u> </u>                 |                    |                       |                                       |  |

|-------------------------------------------------------|------------------------------------|--------------|-------------------------------------------|--------|----------------|--------------------------|--------------------|-----------------------|---------------------------------------|--|

| Description                                           | Parameter <br> <br>                | TA           | Conditions<br>T <sub>A</sub> = +25°C ±5°C |        | 1              | Min Recom-<br>  mended   |                    | Max                   | T Unit                                |  |

| using enable voltage l<br>at 10 to 40 mA              | V <sub>FE</sub>                    |              |                                           | -      |                | 14.5                     | 15                 | 15.5                  | <br>  V<br>                           |  |

| Program voltage                                       | V <sub>OP</sub>                    | at 15        | to 200 m                                  | A      |                | 19.5                     | 20                 | 20.5                  | <br>  Y<br>                           |  |

| Input high level duringl<br>programming and<br>verify | VIHP                               |              |                                           |        |                | 2.4                      | 5                  | 5.5                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

| Input low level during programming and verify         | V <sub>ILP</sub>                   |              |                                           |        |                | 0.0                      | 0.3                | 0.5                   | Y<br> <br>                            |  |

| V <sub>CC</sub> during<br>programming                 | V <sub>CCP</sub>                   | at I         | C = 50 to                                 | 200 mA |                | 5                        | 5.2                | 5.5                   | ٧                                     |  |

| Rate of output<br>voltage change                      | dV <sub>OP</sub> /dt               | <br>         |                                           |        | Ì              | 20                       |                    | 250                   | V/uS                                  |  |

| Rate of fusing enable voltage change                  | dV <sub>FE</sub> /dt               | <br>         |                                           |        |                | 50                       |                    | 1000                  | V/uS                                  |  |

| Fusing time first attempt                             | <br> tp<br>                        | <br> <br>    |                                           |        |                | 40                       | 50                 | 100                   | us                                    |  |

| Fusing time subsequent attempts                       | <br> tp<br>                        |              |                                           |        |                | 4                        | 5                  | 1000                  | ms                                    |  |

| Delays between various level changes                  | t <sub>1</sub> -t <sub>6</sub><br> | <u> </u><br> |                                           |        | i<br> <br>     | 100                      | i<br>i             | 2000                  | i ns                                  |  |

| Period during which output is sensed for VBLOWN level | ity                                |              |                                           |        | <br> <br> <br> |                          | <br>  500<br> <br> | <br>                  | ns                                    |  |

| Pull-up voltage on<br>outputs not being<br>programmed | I V <sub>ONP</sub>                 |              |                                           |        | <br> <br> <br> | V <sub>CCP</sub><br>-0.3 | VCCP               | V <sub>CCP</sub> +0.3 | V                                     |  |

| Pull-up resistor on outputs not being programmed      | R                                  |              |                                           |        |                | 0.2                      | 2                  | 5.1                   | KΩ                                    |  |

| Current into outputs not to be programmed             | I I ONP                            |              |                                           |        | <br> <br>      | ·                        |                    | 20                    | mA                                    |  |

|                                                       |                                    |              | SIZE                                      | CODE   | IDEN           | T. NO.                   | DWG NO.            |                       |                                       |  |

| MILITARY DE                                           |                                    |              | A                                         | 14     | 4933           | 3                        | 5962               | -86706                |                                       |  |

| DEFENSE ELECTRONICS DAYTON, O                         | SUPPLY CEN                         | TER          |                                           |        | REV            | <del></del>              |                    | PAGE 16               |                                       |  |

Powered by ICminer.com Electronic-Library Service CopyRight 2003

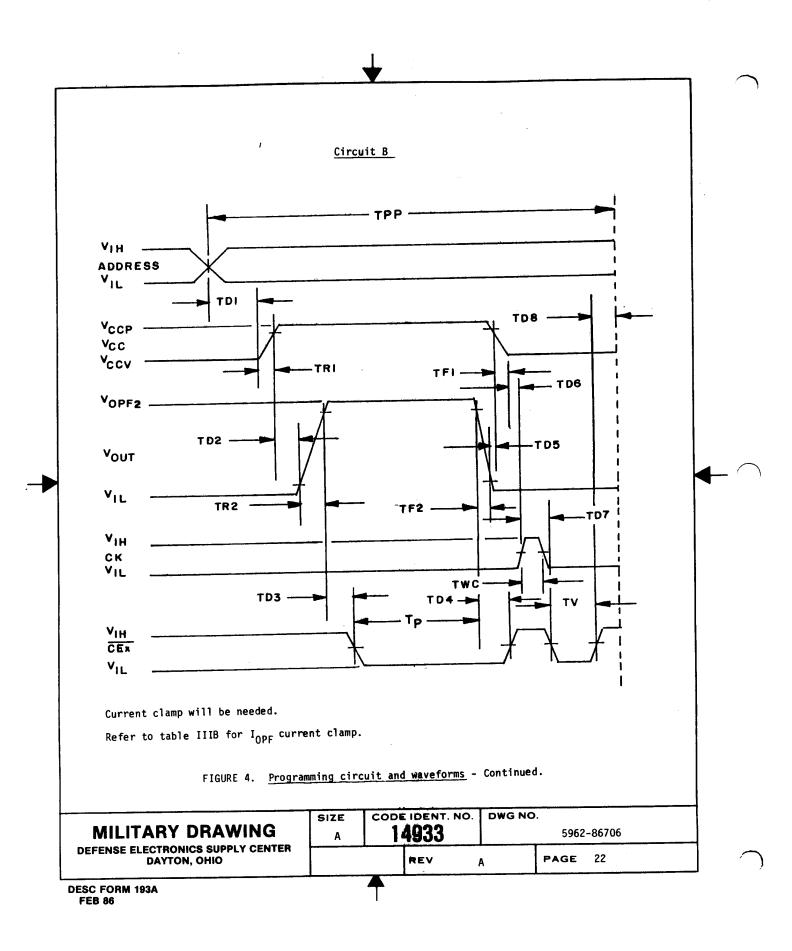

- a. Connect the device, following the electrical configuration for programming. The waveforms shown on figure 4 and the programming characteristics of table IIIB shall apply to these procedures.

- b. Output pins should be terminated with a 10  $k\Omega$  resistor to VCC.

- c. Bypass  $V_{CC}$  to ground with a 0.01  $\mu F$  capacitor.

- d. Apply initial voltage of  $V_{IH}$  to the programming control pin  $(\overline{CE_X})$ , with appropriate voltage to chip enable pins (as applicable) in accordance with table I.

- e. Apply VIL to all other pins.

- f. Select the word to be programmed by applying  $\text{V}_{IL}$  or  $\text{V}_{IH}$  on the appropriate address pins, and reset Tp to 5  $\mu s$  .

- g. Wait for TD1 and raise the VCC pin to VCCP.

- h. Wait for  $T_{D2}$  and raise the corresponding output pin to  $Y_{OPF}$ .

- i. Wait for  $T_{D3}$  and lower the programming control pin ( $\overline{\text{CE}_{X}}$ ) to  $V_{\text{IL}}$  for a duration of  $T_{\text{P}}$ .

- j. Simultaneously lower the output to  $v_{

m IL}$  and begin waiting for  $v_{

m D4}$ .

- k. Return the programming control pin,  $\overline{\text{CE}_{X}}$  to  $V_{\text{IH}}$ .

- 1. Wait for TD5 and lower VCC to VCCV.

- m. Wait for  $T_{D6}$  and lower input programming control pin  $\overline{\text{CE}_{X}}$  to  $extsf{Y}_{IL}$  for the duration of  $extsf{T}_{V}$ .

- n. A properly blown fuse will read  $V_{OL}$ , and an unblown fuse will read  $V_{OH}$ .

- 1. If the fuse is blown, go to 4.5q.

- 2. If fuse is unblown, go to 4.50.

- o. If Tp is less than 20  $\mu s$  , increment Tp by 5  $\mu s$  and go to 4.5g. If Tp is equal or greater than 5  $\mu s$  go to 4.5p.

- p. If  $T_p$  is equal to or greater than 20  $\mu s$ , then the device is a reject. STOP.

- q. Wait for  $T_{D8}$  and select the next output or address to be programmed.

- r. Repeat steps 4.5f through 4.5n until all required addresses are programmed.

- s. Program the initialization word by applying  $V_{IL}$  to the  $T/T_S$  pin. After the  $T/T_S$  word is programmed, return the  $T/T_S$  pin to  $V_{IH}$ .

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 | DWG NO.<br>5962-86706 |  |

|-----------------------------------------------------------------|------|-------|-----------------------|--|

|                                                                 |      | REV A | PAGE 17               |  |

- Wait for T<sub>D6</sub>, keeping V<sub>CC</sub> at V<sub>CCV</sub>.

- 2. Lower CEx input to VIL.

- 3. Sequentially select  $T/T_S$  word, all addresses,  $\overline{G}/\overline{G}_S$  and  $T/T_S$  in the memory.

- 4. A properly blown fuse will read  $V_{OL}$ , and unblown fuse will read  $V_{OH}$ .

- End of programming procedure.

- u. Programming verification, refer to table III:

- 1. Wait for  $T_{D6}$  and apply clock pulse of duration TWC, refer to figure 4.

- 2. Wait for  $T_{D7}$  and lower input programming control pin  $\overline{\text{CE}_X}$  to  $\text{V}_{IL}$  for the duration of  $T_V$  .

- 3. Go to 4.5n.

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO

SIZE

A 14933

CODE IDENT. NO. DWG NO. 5962-86706

REV A PAGE 18

| TABLE IIIB. | Programming charac |

|-------------|--------------------|

|             |                    |

|                             |                                  |                                                               | !<br>}        | !<br>     |               |                      |  |

|-----------------------------|----------------------------------|---------------------------------------------------------------|---------------|-----------|---------------|----------------------|--|

| Parameter                   | Symbol                           | Conditions                                                    | <br>  Min<br> | Recom-    | <br>  Max<br> | Unit                 |  |

| Power supply voltage        | V <sub>CCP</sub> 1               | I <sub>CCP</sub> = 500 mA                                     | 8.5           | 8.75      | 9.0           | V                    |  |

| Verify voltage              | VCCV                             |                                                               | 4.75          | 5.0       | 5.25          | !<br>! V<br>!        |  |

| High input voltage          | V <sub>IH</sub>                  | I <sub>IH</sub> = 50 μA                                       | 2.4           | 3.0       | 5.5           | <br>  V<br>          |  |

| Low input voltage           | VIL                              | I <sub>IL</sub> = -500 μA                                     | 0.0           | 0.0       | 0.5           | V                    |  |

| Forced output current       | I <sub>OPF2</sub>                |                                                               | 150           | 185       | 220           | l mA                 |  |

| Forced output voltage       | V <sub>OPF</sub> 3               |                                                               | 20.5          |           | 21.0          | V                    |  |

| Output high voltage         | V <sub>OH</sub>                  |                                                               | 2.0           |           |               | V                    |  |

| Output low voltage          | V <sub>OL</sub>                  |                                                               |               | <br> <br> | 1.0           | V                    |  |

| Program time                | Трр                              | 50 percent to 50 percent                                      |               | j 58      | <br>          | <br>  μ <b>s</b><br> |  |

| V <sub>CC</sub> delay time  | T <sub>D1</sub>                  | 50 percent add to                                             | 10            | 10        | 25<br>        | μs<br>l              |  |

| V <sub>OUT</sub> delay time | T <sub>D2</sub>                  | 90 percent V <sub>CCP</sub> to<br>10 percent V <sub>OPF</sub> | 1             | 1         | <br>  5<br>   | μS<br>               |  |

| Pulse sequence delays       | T <sub>D3</sub> -T <sub>D8</sub> | See figure 4                                                  | 1             | 1         | 10            | μS                   |  |

| V <sub>CC</sub> rise time   | T <sub>R1</sub>                  | 10 percent to 90 percent                                      | 4             | 7         | 8             | μS                   |  |

| V <sub>OUT</sub> rise time  | T <sub>R2</sub>                  | 10 percent to 90 percent                                      | 3             | 10        | 17            | μS                   |  |

See footnotes at end of table.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 | DWG NO.<br>5962-86706 |    |

|-----------------------------------------------------------------|------|-------|-----------------------|----|

|                                                                 |      | REV A | PAGE                  | 19 |

|                            | ļ               |                          |                      |     | 1   |              |

|----------------------------|-----------------|--------------------------|----------------------|-----|-----|--------------|

| Parameter                  | Symbol          | Conditions               | Min Recom-<br>mended |     | Max | Unit         |

| V <sub>CC</sub> fall time  | T <sub>F1</sub> | 90 percent to 10 percent | 2                    | 4   | 10  | μ\$          |

| V <sub>OUT</sub> fall time | T <sub>F2</sub> | 90 percent to 10 percent | 3                    | 7   | 21  | μS           |

| CEX programming            | Tp4             | 10 percent to 90 percent | 5                    |     | 20  | μS           |

| CEx verify pulse           | Ty width        | 10 percent to 10 percent | 5                    | 5   | 10  | <br>  μs<br> |

| Clock pulse width (CK)     | TWC             | 50 percent to 50 percent | .5                   | .75 | 5   | μS           |

<sup>1.</sup> If the overall program/verify cycle Tpp exceeds the recommended (rec) value, a 25 percent duty cycle must be used for VCCP.

## 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

## 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE<br>A | 1933  | DWG NO.<br>5962-86706 |      |    |

|-----------------------------------------------------------------|-----------|-------|-----------------------|------|----|

|                                                                 |           | REV A |                       | PAGE | 20 |

<sup>2.</sup> For the program current pulse Iopp, a current source must be used with a voltage limit set at Vopp.

3. Maximum output voltage Vopp must be limited to 21.0 V.

4. To is 5  $\mu$ s at first attempt and increments 5  $\mu$ s each additional programming attempt until fuse is blown or 20 us is reached.

- All delays between edges are specified from the completion of the first edge to the beginning of the second edge; i.e, not the midpoints.

- 2. Delays  $t_1$  through  $t_6$  must be greater than 100 ns; maximum delays of 1  $\mu s$  are recommended to minimize heating during programming.

- 3. During  $\mathbf{t}_{\mathbf{V}}$  the output being programmed is switched to the load R and read to determine if additional programming pulses are required.

- 4. Outputs not being programmed are connected to  ${\rm V}_{\rm ONP}$  through register R which provides output current limiting.

FIGURE 4. Programming circuit and waveforms.

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE<br>A | 14933 | DWG NO.<br>5962-86706 |      |    |

|-----------------------------------------------------------------|-----------|-------|-----------------------|------|----|

|                                                                 |           | REV   |                       | PAGE | 21 |

DESC FORM 193A FEB 86

Notes:

6.4 Approved source of supply. Approved sources of supply are listed herein. Additional sources will be added as they become available. The vendors listed herein have agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

| Military drawing  <br>part number | Vendor<br>CAGE<br>number | Vendor<br>  similar part<br>  number <u>1</u> / |  |

|-----------------------------------|--------------------------|-------------------------------------------------|--|

| 5962-8670601LX                    | 34335<br>18324           | AM27S35/BLA<br>82HS187A/BLA                     |  |

| 5962-8670601KX<br>5962-8670601XX  | 34335<br>34335           | AM27S35/BKA<br>AM27S35/BUA                      |  |

| 5962-86706013X                    | 34335<br>18324           | AM27S35/B3A<br>82HS187A/B3X                     |  |

| 5962-8670602LX /                  | 34335<br>18324           | AM27S35A/BLA<br>82HS187A/BLA                    |  |

| 5962-8670602KX<br>5962-8670602XX  | 34335<br>34335           | AM27S35A/BKA<br>  AM27S35A/BUA                  |  |

| 5962-86706023X                    | 34335<br>18324           | AM27S35A/B3A<br>  82HS187A/B3X                  |  |

| 5962-8670603LX                    | 34335<br>18324           | <br>  AM27S37/BLA<br>  82HS189A/BLA             |  |

| 5962-8670603KX                    | 34335<br>34335           | AM27S37/BKA<br>AM27S37/BUA                      |  |

| 5962-86706033X                    | 34335<br>18324           | AM27S37/B3A<br>82HS189A/B3X                     |  |

| 5962-8670604LX                    | <br>  34335<br>  18324   | AM27S37A/BLA<br>  82HS189A/BLA                  |  |

| 5962-8670604KX<br>5962-8670604XX  | 34335<br>34335           | AM27S37A/BKA<br>AM27S37A/BUA                    |  |

| 5962-86706043X<br>                | <br>  34335<br>  18324   | AM27S37A/B3A<br>82HS189/B3X                     |  |

Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

| Vendor CAGE<br>number                                           | Vendor name and address                                              |           |        | rogrammin<br>Procedure |                         |

|-----------------------------------------------------------------|----------------------------------------------------------------------|-----------|--------|------------------------|-------------------------|

| 34335                                                           | Advanced Micro Device<br>901 Thompson Place<br>Sunnyvale, CA 94088   | s, Incorp | orated | A                      | Platinum silicide fuse  |

| 18324                                                           | Signetics, Incorporat<br>4130 S. Market Court<br>Sacramento CA 95834 |           |        | 8                      | Zapped vertical emitter |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |                                                                      | SIZE      | 149    |                        | DWG NO.<br>5962-86706   |

|                                                                 |                                                                      |           | RE     | <b>У</b> А             | PAGE 23                 |