|                                                                                | <del></del>           | _        |    |                                    | - |             |       |      |      | F | REV                   | SIO                                                                 | NS |   |     |     |          |      |          |              |             |              |       |     |    |    |

|--------------------------------------------------------------------------------|-----------------------|----------|----|------------------------------------|---|-------------|-------|------|------|---|-----------------------|---------------------------------------------------------------------|----|---|-----|-----|----------|------|----------|--------------|-------------|--------------|-------|-----|----|----|

| LTR                                                                            |                       |          |    |                                    |   |             | DE    | SCF  | IPTK | × |                       | -                                                                   |    |   |     |     |          | D    | ATE      | (YR-N        | IO-DA       | ,            | APF   | ROV | ED | 4  |

|                                                                                |                       |          | •  |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

|                                                                                |                       |          |    |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

|                                                                                |                       |          |    |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

|                                                                                |                       |          |    |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

| REV                                                                            |                       | _        |    |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

| SHEE                                                                           | т                     | $\dashv$ |    |                                    |   |             |       | _    | H    |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

| REV                                                                            |                       |          |    |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          |              |             |              | Щ     |     |    |    |

| SHEE                                                                           | т                     | 22       | 23 |                                    |   |             |       |      |      |   |                       |                                                                     |    |   |     |     |          |      |          | _            | L           | _            |       |     |    |    |

| REV                                                                            | STATUS                | T        | RE | V                                  |   |             |       |      |      |   |                       |                                                                     |    |   |     |     | <u> </u> | _    | <u> </u> | <u> </u>     | <b> </b>    | <del> </del> |       |     | _  |    |

|                                                                                | HEETS                 |          | Sł | IEET                               |   | 1           | 2     | 3    | 4    | 5 | 6                     | 7                                                                   | 8  | 9 | 10  | 11  | 12       | 13   | 14       | 15           | 16          | 17           | 18    | 19  | 20 | 21 |

| PMIC                                                                           |                       |          |    |                                    |   | Ke          |       | Ø.   | 41   | 2 | <del>)</del>          |                                                                     |    | - |     | DEI | FENS     | E EL | ECTI     | RONI<br>N, O | CS S<br>HIO | UPP<br>1544  | LY CE | NTE | R  |    |

| }                                                                              | NDAI<br>MILIT<br>DRAV | AR       | Y  | ע.<br>_                            | _ | APPROVED BY |       |      |      |   | M U                   | MICROCIRCUITS, DIGITAL, CMOS 8K X 8<br>UV EPROM, MONOLITHIC SILICON |    |   |     |     |          |      |          |              |             |              |       |     |    |    |

| THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL DEPARTMENTS<br>AND AGENCIES OF THE |                       |          | TS | DRAWING APPROVAL DATE 21 JUNE 1988 |   |             |       |      | SIZE |   | <b>67268</b> 5962-875 |                                                                     |    |   | 751 | 5   |          |      |          |              |             |              |       |     |    |    |

| DEPARTMENT OF DEFENSE REVISION LEVEL SHEET 1 OF 23                             |                       |          |    |                                    |   |             | VISIO | N LE | VEL. |   |                       |                                                                     |    |   |     | SHE | ET       |      | 1        |              | OF          |              | 23    |     |    |    |

\* U.S. GOVERNMENT PRINTING OFFICE: 1987 -- 748-129/60911

5962-E225

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

#### 1. SCOPE

1.1~Scope. This drawing describes device requirements for class B microcircuits in accordance with  $1.\overline{2.1}$  of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

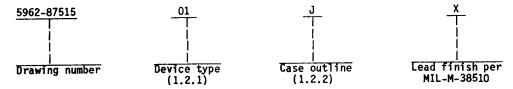

1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1 Device types. The device types shall identify the circuit function as follows:

| Device type | Generic number | Circuit function | Access time |

|-------------|----------------|------------------|-------------|

| 01          | See 6.4        | 8K x 8 UV EPROM  | 45 ns       |

| 02          | See 6.4        | 8K x 8 UV EPROM  | 55 ns       |

| 03          | See 6.4        | 8K x 8 UV EPROM  | 70 ns       |

| Ŏ <b>4</b>  | See 6.4        | 8K x 8 UV EPROM  | 90 ns       |

| 05          | See 6.4        | 8K x 8 UV EPROM  | 45 ns       |

| 06          | See 6.4        | 8K x 8 UV EPROM  | 55 ns       |

1.2.2 <u>Case outlines</u>. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

| Outline letter Case outline                                                         |           |

|-------------------------------------------------------------------------------------|-----------|

| J D-3 (24 lead, 1.290" x .610" x .225"), dual-in-line part of the first package 1/2 | ackage 1/ |

## 1.3 Absolute maximum ratings.

# 1.4 Recommended operating conditions.

Case operating temperature (T<sub>C</sub>) - - - - - - - - - - - - - - - 55°C to +125°C supply voltage ( $V_{CC}$ )- - - - - - - - - - - - - - +4.5 V dc to +5.5 V dc

1/ Lid shall be transparent to permit ultraviolet light erasure.

Z/ Must withstand the added Pp due to short circuit test, e.g., Ios.

3/ Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening conditions in accordance with method 5004 of MIL-STD-883.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A | Δ |                | 5962-87515 |       |   |

|------------------------------------------------------|-----------|---|----------------|------------|-------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           |   | REVISION LEVEL |            | SHEET | 2 |

DESC FORM 193A SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1968--549-904

### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

**MILITARY**

MIL-M-38510

- Microcircuits, General Specification For.

**STANDARD**

**MILITARY**

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

- 3.2.2 Truth tables. The truth tables shall be as specified on figure 2.

- 3.2.2.1 <u>Unprogrammed or erased devices</u>. The truth table for unprogrammed devices shall be as specified on figure 2.

- 3.2.2.2 <u>Programmed devices</u>. The requirements for supplying programmed devices are not part of this drawing.

- 3.2.3 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.4 herein.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87515

REVISION LEVEL

SHEET

3

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988—549-90-

|                                      | TABLE            | I. Electri                                                                                            | cal perf                                             | ormance         | charac1         | teristics.                |                            |                   |                            |                  |

|--------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------|-----------------|---------------------------|----------------------------|-------------------|----------------------------|------------------|

| Test                                 | Symbol           | 1 Vgg = 0 1                                                                                           | Condition  < TC <+1  / 4.5 V otherwise               | < VCC           | : 5.5 V<br>F1ed | Group A<br> subgroups<br> | <br> Device<br> types<br>  | Lim<br> <br>  Min | its<br>  Max<br>           | Unit             |

| Input leakage current                | ILI              | V <sub>IN</sub> = 5.5                                                                                 | Y and G                                              | ID .            |                 | 1,2,3                     | A11                        |                   | ±10                        | <br>  μ <b>A</b> |

| Output leakage current               | ILO              | V <sub>OUT</sub> = 5.5                                                                                | 5 V and (                                            | MD              |                 | 1,2,3                     | A71                        |                   | ±10                        | <br>  μ <b>A</b> |

| Operating supply current (active) 1/ | I <sub>CC1</sub> | CS = V <sub>II</sub> ,<br> DO to D7 =<br> f = max                                                     | V <sub>CC</sub> = 5.<br>= 0 mA                       | 5 Y             |                 | 1,2,3                     | <br> <br>  A11             |                   | 120                        | <br>  mA<br>     |

| Standby current,<br>TTL inputs       | I <sub>CC2</sub> | CS = 2.0                                                                                              | V, Y <sub>CC</sub> -                                 | 5.5 Y           |                 | 1,2,3                     | A11<br> <br>               |                   | 40                         | l mA             |

| Standby current,<br>CMOS inputs      | I <sub>CC3</sub> | V <sub>CC</sub> = 5.5                                                                                 | V <sub>CC</sub> = 5.5 V, CS = V <sub>CC</sub> -0.3 V |                 |                 | 1,2,3                     | A11<br> <br>               |                   | 40                         | mA               |

| Input low voltage                    | VIL              | V <sub>CC</sub> = 4.5                                                                                 | V <sub>CC</sub> = 4.5 V and 5.5 V                    |                 |                 | 1,2,3                     | <br>  A11<br>              | !<br>!            | 8.0                        | V<br>  V         |

| Input high voltage                   | VIH              | V <sub>CC</sub> = 4.5 V and 5.5 V                                                                     |                                                      |                 | 1,2,3           | <br>  A]]                 | 2.0                        |                   | <b>V</b>                   |                  |

| Output voltage low                   | VOL              | I <sub>OL</sub> = 16 mA, V <sub>IH</sub> = 2.0 V<br>  V <sub>CC</sub> = 4.5 V, V <sub>IL</sub> = .8 V |                                                      |                 | 1,2,3           | <br>  A11<br>             |                            | 0.45              | <br>  V<br>                |                  |

| Output voltage high                  | <b>V</b> OH      | IOH = -4 I<br>VCC = 4.5                                                                               | mA, VIH<br>V, VIL                                    | = 2.0<br>= .8 ¥ | i<br>,          | 1,2,3                     | <br>  A11<br>              | 2.4               |                            | <br>  V<br>      |

| Output short circuit current 2/      | 105              | V <sub>O</sub> = GND                                                                                  |                                                      |                 |                 | 1,2,3                     | A11<br>                    |                   | -100                       | l mA             |

| Input capacitance                    | CIN              | f = 1.0 M <br> T <sub>C</sub> = +25°(                                                                 | Hz I                                                 | /IN = 0         | Ý               | 4                         | <br>  A11                  |                   | 6                          | l<br>l pF        |

| Output capacitance                   | COUT             | TSee 4.3.16<br>V <sub>CC</sub> = 5.5                                                                  | e [1                                                 | OUT =           | V<br>L A<br>L[] | T<br> <br>                | <br>                       |                   | 12<br> <br>                | T<br> <br>       |

| Address to output<br>delay           | tACC<br>3/4/     | CS = VIL                                                                                              |                                                      |                 |                 | 9,10,11                   | 01,05<br>02,06<br>03<br>04 |                   | 45<br>  55<br>  70<br>  90 |                  |

| See footnotes at end of              | table.           |                                                                                                       |                                                      |                 |                 |                           |                            |                   |                            | — <del></del>    |

| STANDARD<br>MILITARY DR              |                  | G                                                                                                     | SIZE<br>A                                            |                 |                 |                           | 59                         | 62-875            | 15                         |                  |

| DEFENSE ELECTRONICS DAYTON, OHIO     |                  | MEVISION LEVEL                                                                                        |                                                      |                 |                 | SHEET 4                   |                            |                   |                            |                  |

± U. B. GOVERNMENT PRINTING OFFICE: 1968--549-90

| 1                          | TABLE I.                  | Electrical performance character                                                                                                                                                                              | ristics - (                         | ontinued                       |      |                |      |

|----------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------|------|----------------|------|

| Test                       | <br> Symbol<br> <br> <br> | Conditions $-55^{\circ}\text{C} \leq \text{T}_{\text{C}} < +125^{\circ}\text{C}$ $\text{V}_{\text{SS}} = 0 \text{ V} + 4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}$ unless otherwise specified | <br> Group A<br> subgroups<br> <br> | <br> Device<br> types<br> <br> | Lim: |                | Unit |

| CS to output delay         | t <sub>CS</sub> 4/        |                                                                                                                                                                                                               | 9, 10, 11                           | 01,02<br>05<br>03,04,          |      | 35<br>45<br>55 | , ns |

| CS high to output<br>float |                           | CS = VIL                                                                                                                                                                                                      | 9, 10, 11                           | 01,02<br>05<br>03,04,          |      | 35<br>45<br>55 | ns   |

| Address to output hold     | 1toH<br>3/4/              | CS = VIL                                                                                                                                                                                                      | <br> 9, 10, 11<br>                  | A11                            | 0    | <br>           | ns   |

TTL inputs: V<sub>IL</sub>  $\leq$  0.8 V, V<sub>IH</sub> > 2.0 V. Not more than one output should be shorted at a time, and short circuit test (I<sub>OS</sub>) should not exceed 30 seconds

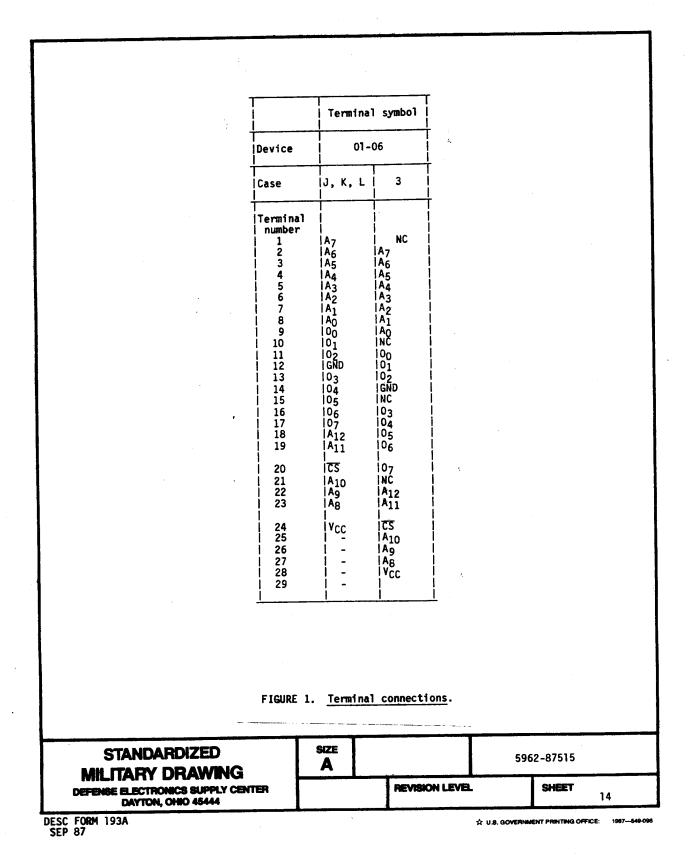

See figure 4.

4/ Output shall be loaded in accordance with figure 3.

- 3.5 Processing EPROMS. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.5.1 Erasure of EPROMS. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.4.

- 3.5.2 Programmability of EPROMS. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.5.

- 3.5.3 <u>Verification of erasure of programmed EPROMS</u>. When specified, devices shall be verified as either programmed to specified program or erased. As a minimum, verification shall consist of performing a funtional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

- 3.6 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

| STANDARDIZED  MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |            |       | 5962-87515 |   |  |

|--------------------------------------------------------------------------------------|-----------|------------|-------|------------|---|--|

|                                                                                      |           | REVISION L | EVEL. | SHEET      | 5 |  |

DESC FORM 193A SEP 87

**☆ U. S. GOVERNMENT PRINTING OFFICE: 1988**

- 3.9 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 Screening. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition C or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- c. A data retention stress shall be included as part of the screening procedure and shall consist of the following steps:

# Margin test method A.

- At +25°C, program greater than 95 percent of the bit locations, including the slowest programming cell. The remaining bits shall provide a worse case speed pattern. Bake, unbiased, for 72 hours at  $^{+140}$ C or for 32 hours at  $^{+150}$ C or for 8 hours at  $^{+200}$ C. At  $^{+25}$ C, perform a margin test using  $V_m = ^{+5.8}$ V to loose timing (i.e.,  $t_{ACC} = 1$   $\mu$ s). Perform dynamic burn-in in accordance with 4.2a. (1)

- (3)

- (4)

- (5) (6)

- At +25°C, perform a margin test using  $V_m=\pm 5.8$  V. Perform electrical test in accordance with 4.2b. Erase in accordance with 3.5.1. Devices may be submitted to quality conformance inspection. Verify erasure in accordance with 3.5.3.

- (7) (8)

#### Margin test method B.

- Program at +25°C greater than 95 percent of the bit locations, including the slowest (1)

- programming cell. The remaining cells shall provide a worst case speed pattern. Bake, unbiased, for 72 hours at +140°C or for 32 hours at +150°C or for 8 hours at +200°C. Perform margin test using  $V_m=+5.55$  V and  $V_m=+4.40$  V at +25°C using loose timing (3)

- (i.e.,  $t_{ACC}=1~\mu s$ ). Erase (see 3.5.1). Program at +25°C with a 50 percent pattern (checkerboard bar). Perform margin test using  $V_m=+5.75~V$  and  $V_m=+4.40~V$  at +25°C with loose timing. Perform dynamic burn-in for 48 hours at +150°C (see 4.2a).

- (7)

- Perform margin test using  $V_m = +5.55 \text{ V}$  and  $V_m = +4.40 \text{ V}$  at  $+25^{\circ}\text{C}$  using loose timing. (8)

- (9)

- (10)

- Erase (see 3.5.1).

Program at +25°C with a 50 percent pattern (checkerboard).

Perform margin test using  $V_m = +5.75$  V and  $V_m = +4.40$  V at +25°C with loose timing.

Perform dynamic burn-in for 48 hours at +150°C (see 4.2a). (11)

- (12) Perform margin test using  $V_m=+5.55\ V$  and  $V_m=^1+4.40\ V$  at +25°C using loose timing. Perform electrical tests (see 4.2b). (13)

- (14)

- Erase (see 3.5.1), except devices submitted for groups A, B, C, and D testing. (15)

- (16)Verify erasure (see 3.5.3).

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |            |      | 5962-87515 |   |

|------------------------------------------------------|-----------|------------|------|------------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION I | EVEL | SHEET      | 6 |

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1968--549-904

4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-SID-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

## 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. All devices selected for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified except devices being submitted to group B, C, and D testing.

- d. As a minimum, subgroups 7 and 8 shall consist of verifying the EPROM pattern specified.

- e. Subgroup 4 ( $C_{\rm IN}$  and  $C_{\rm OUT}$  measurements) shall be measured only for the initial test and after process or design changes which may affect capacitance.

- 4.3.2 Groups B inspection. Group B inspection shall be in accordance with table II of method 5005 of MIL-STD-883 and as follows:

- a. Electrostatic discharge sensitivity (ESDS) testing shall be performed in accordance with MIL-STD-883, method 3015 for initial testing and after any design or process changes which may affect input-output protection circuitry. The option to categorize devices as ESD sensitive without performing the test is not allowed. Device types categorized as ESD sensitive shall be further tested using method 3015 modified as follows:

Only those device types that pass ESDS testing at 1000 volts or greater shall be considered as conforming to the requirements of this drawing.

# 4.3.3 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition C or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- c. All devices submitted for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified.

- 4.4 Erasing procedure. The recommended erasure procedure for the device is exposure to shortwave ultraviolet light which has a wavelength of 2537 angstroms (Å). The intergrated dose (i.e., UV intensity x exposure time) for erasure should be a minimum of 25 Ws/cm². The erasure time with this dosage is approximately 35 minutes using a ultraviolet lamp with a 12,000  $\mu$ W/cm² power rating. The device should be placed within one inch of the lamp tubes during erasure. The maximum intergrated dose the device can be exposed to without damage is 7258 Ws/cm² (1 week at 12,000  $\mu$ W/cm²). Exposure of EPROMS to high intensity UV light for long periods may cause permanent damage.

|                                                      |           |                |                  | - |

|------------------------------------------------------|-----------|----------------|------------------|---|

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-87515       |   |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | . <b>SHEET</b> 7 |   |

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

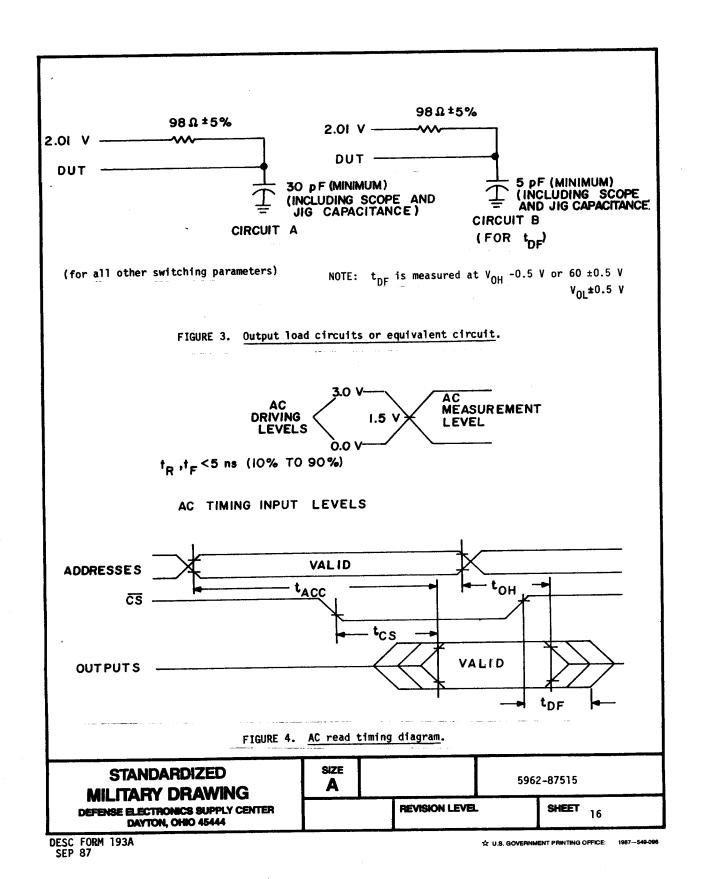

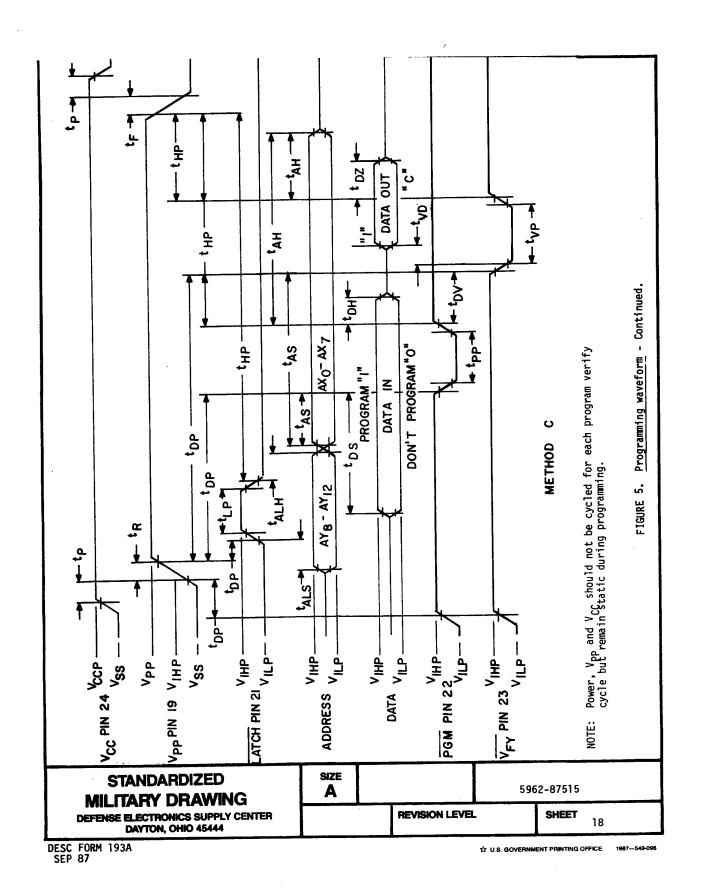

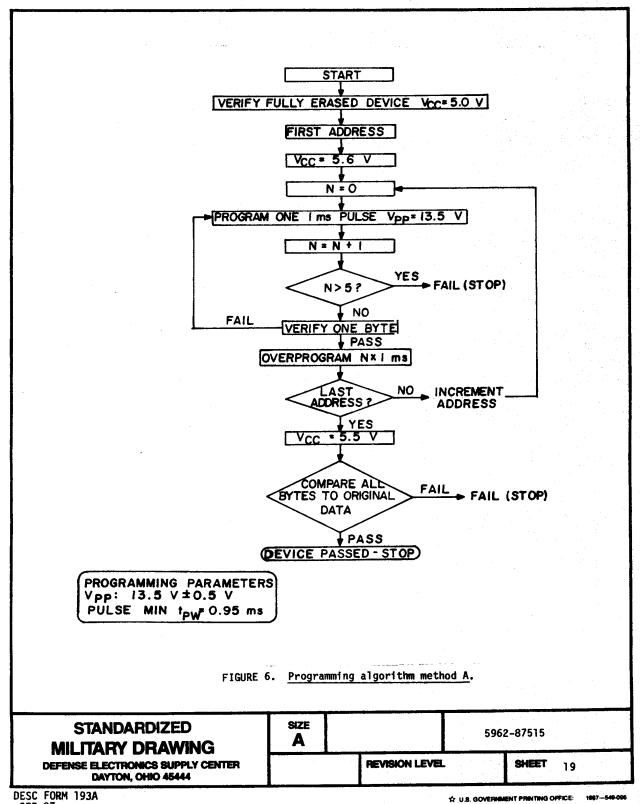

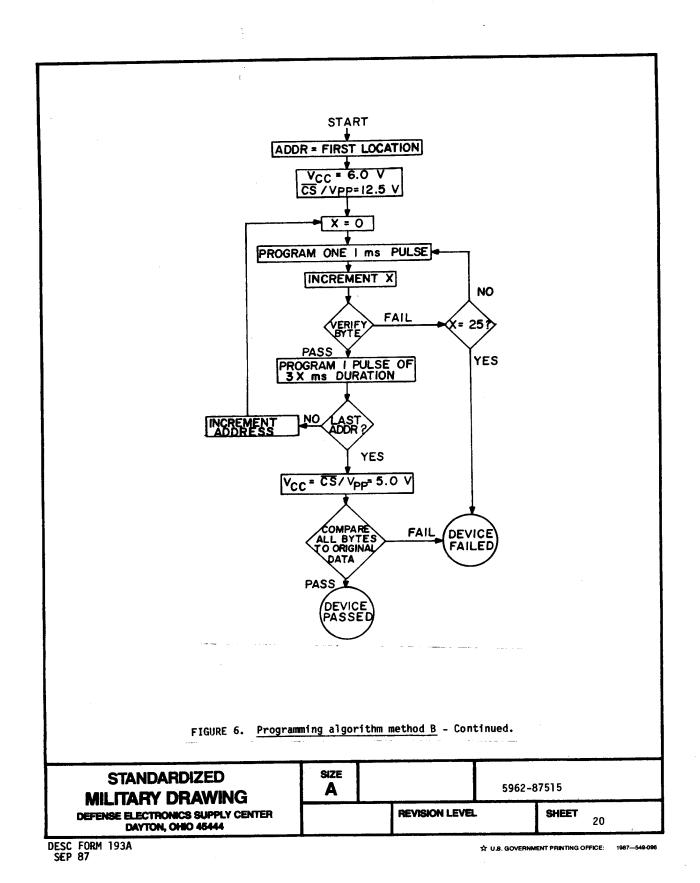

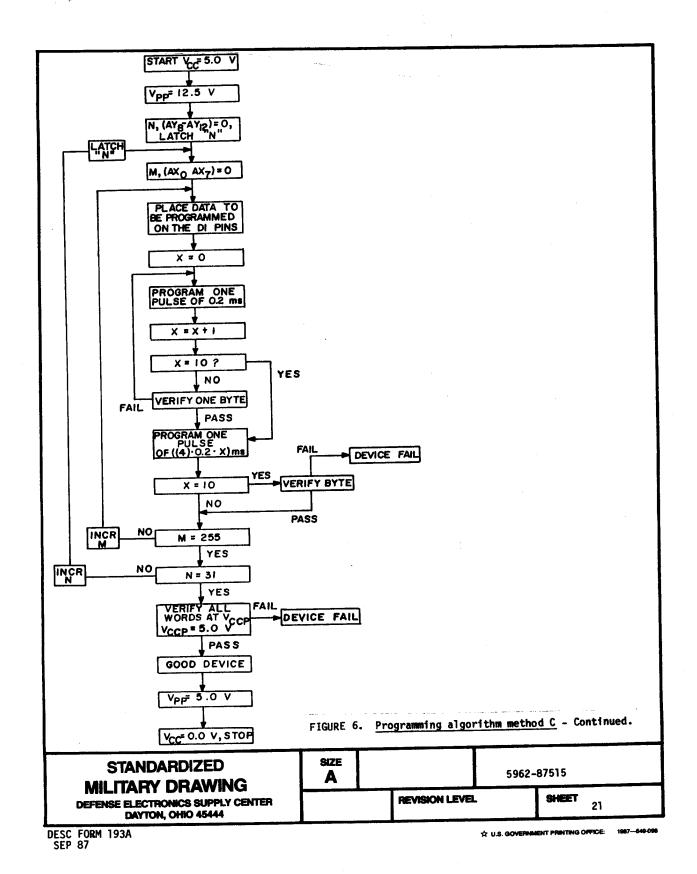

- 4.5 Programming procedure. The programming characteristics in table III and the programming algorithm of figure 5 shall be used to program the device.

- 4.5.1 Programming method A. Initially and after each erasure all bits are in the "1" state. Programming is performed by raising  $V_{CC}$  to 5.6 V, disabling the outputs, addressing the byte to be programmed, presenting the data to be programmed onto the data pins, and applying a 13.5 V pulse to the C5/Vpp pin for 1 ms. The byte is then verified by removing the input data and reading the programmed byte as in the read operation. A 0.1  $\mu$ F capacitor between  $V_{pp}$  and GND is needed to prevent excessive voltage transients which could damage the device.

- 4.5.2 Programming method B. Two 12.5 V  $\overline{\text{CS/Vpp}}$  pulse widths are used to program; initial and overprogram. Input addresses are set to address the desired byte.  $V_{CC}$  is raised to 6.0 V. The first  $\overline{\text{CS/Vpp}}$  pulse is 1 ms. The programmed byte is then verified. If the byte programmed successfully, then an overprogram  $\overline{\text{CS/Vpp}}$  pulse is applied for 3 ms. If the byte fails to program after the first 1 ms pulse, then up to 25 successive 1 ms pulses are applied with a verification after each pulse. When the byte passes verification, the overprogram pulse width is three times the number of 1 ms pulses required earlier (75 ms maximum). If the part fails to verify after 25 1 ms pulses have been applied, it is considered as failed. After the first byte is programmed, the input addresses are set to the next address repeating the alogorithm until all required addresses are programmed. Then  $V_{CC}$  is lowered to 5.0 V. All bytes subsequently are read to compare with the original data to determine if the device passes or fails.

Motes: V<sub>CC</sub> must be applied simultaneously or before  $\overline{\text{CS/V}_{pp}}$  and removed simultaneously or after  $\overline{\text{CS/V}_{pp}}$ . When programming the 27HC641/2 a 0.1  $\mu\text{F}$  capacitor is required across  $\overline{\text{CS/V}_{pp}}$  and ground to supress spurious voltage transients which can damage the device.

# 4.5.3 Programming method C.

- a. The waveforms of figure 5 and programming characteristics of table III shall apply.

- b. Initially and after each erasure all bits are in the low "L" state. Information is introduced selectively programming a high "H" into the desired bit locations. A programmed "H" can be changed to an "L" by ultraviolet light erasure (see 4.4).

- c. The programming mode is entered by raising pin A<sub>11</sub> to V<sub>DD</sub>. In this mode, pin A<sub>10</sub> becomes a latch signal, allowing the upper 5 address bits to be latched and held in an onboard register, while the lower 8 address bits are presented on the same pins for selecting one of 256 memory bytes. The addressed location is programmed and verified with the application of a PGM and VFY pulse applied to pins A<sub>9</sub> and A<sub>8</sub> respectively. Entering and exiting the programming mode should be done with care.

- d. Addressing during programming and blankcheck is accomplished by multiplexing the upper 5 address bits with the lower 8. The address designations for the lower 8 addressing bits is AXO through AX7 and the upper 5 address bits are designated AY8 through AY12.

Addressing while in these modes is accomplished by placing the upper 5 bits of address on pins A4, A3, A2, A1, and A0 with the LSB on pin A0. These address bits are loaded into an onboard register by clocking pin A10, the latch signal, from  $V_{\rm ILP}$  to  $V_{\rm IHP}$  and back to  $V_{\rm ILP}$ . The lower 8 address bits are then placed on pins A0 through A7, with the LSB on pin A0. The upper 5 bits remain in the onboard latch until a new value is loaded or power is removed from the device. All 256 bytes addressed by the lower 8 bits may be accessed by sequencing the lower 8 addresses without changing the upper 5 bits or relatching the value in the onboard register.

e. Blankcheck is accomplished by performing a verify cycle, sequencing through all memory address locations, where all the data read will be "0"s.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-87515 |  |  |

|------------------------------------------------------|-----------|----------------|------------|--|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 8    |  |  |

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

- f. Programming is accomplished with an intelligent algorithm. The sequence of operations is to enter the programming mode by placing Vpp on pin Ag. This should be done after a minimum delay from power up, and be removed prior to power down by the same delay.

- g. Address the location to be programmed and place the data to be programmed on the data pins. Clock the  $\overline{PGM}$  signal from  $V_{IHP}$  to  $V_{ILP}$  and back to  $V_{IHP}$  with a pulse width of 200 us.

- h. Remove the data from the data pins, then verify the location by taking the  $\overline{V_{FY}}$  signal from  $V_{IHP}$  to  $V_{ILP}$ , comparing the output with the desired data and then returning  $\overline{V_{FY}}$  to  $V_{IHP}$ .

- i. If the contents are correct, a second overprogram pulse of four times the original 200  $\mu s$  is delivered with the data to be programmed again on the data pins.

- j. If the data is not correct, a second 200 μs pulse is applied to PGM with the data on the data pins. The compare and overprogram operation is repeated with an overprogram pulse width four times the sum of the initial program pulses. This operation continues until the location is programmed or 10 initial program pulses are attempted.

- k. If on the tenth attempt, the location fails to verify, an overprogram pulse of 8 ms is applied, and the content of the location is once more verified. If the location still fails to verify, the device is rejected.

- 1. Once a location verifies successfully, the address is advanced to the next location, and the process is repeated until all locations are programmed.

- m. After all locations are programmed, they should be verified at  $V_{CCP} = 5.0 \text{ V}$ .

TABLE II. Electrical test requirements.

| <br>  MIL-STD-883 test requirements<br>                          | Subgroups<br>  (per method<br>  5005, table I) |

|------------------------------------------------------------------|------------------------------------------------|

| <br>  Interim electrical parameters<br>  (method 5004)           |                                                |

| <br>  Final electrical test parameters<br>  (method 5004)        | 1*,2,3,7*,8,9,10,                              |

| Group A test requirements<br>  (method 5005)                     | 1,2,3,4**,7***,<br>8***,9,10,11                |

| <br>  Group B end-point electrical<br>  parameters (method 5005) | 1****                                          |

| Groups C and D end-point<br>  Gretrical parameters (method 5005) | 2,3,7,8                                        |

<sup>\*</sup> PDA applies to subgroup 1 and 7.

### 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A | Δ |                |  | 5962-87515 |   |  |

|------------------------------------------------------|-----------|---|----------------|--|------------|---|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           |   | REVISION LEVEL |  | SHEET      | 9 |  |

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987—549-096

<sup>\*\*</sup> See 4.3.1e. \*\*\* See 4.3.1d.

<sup>\*\*\*\*</sup> Applies to electrostatic discharge sensitivity test. See 4.3.2.

| Parameter                                            | Symbol          | Conditions                                                                                             | L          | imits                  | Unit       |  |

|------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------|------------|------------------------|------------|--|

|                                                      |                 | Conditions T <sub>C = +25 C +5 C</sub> V <sub>CC = 5.5 V ±0.5 V,</sub> V <sub>PP = 13.5 V ±0.5 V</sub> | Min        | Max                    | <br> <br>  |  |

| Input load current                                   | ILI             | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                               |            | ±10                    | μ <b>A</b> |  |

| Vpp supply current during programming pulse          | Ірр             | 2/ 3/                                                                                                  |            | 30                     | mA         |  |

| V <sub>CC</sub> supply current                       | Icc             |                                                                                                        |            | 60                     | mA         |  |

| Output low voltage during verify                     | V <sub>OL</sub> | I <sub>OL</sub> = 16 mA                                                                                |            | 0.45                   | V          |  |

| Output high voltage during verify                    | VOH             | I I <sub>OH</sub> = -4 mA                                                                              | 2.4        |                        | ) V        |  |

| Input low voltage                                    | VIL             |                                                                                                        | -0.1       | 0.8                    | Į V        |  |

| Input high voltage                                   | ν <sub>IH</sub> |                                                                                                        | 2.0        | V <sub>CC</sub> +0.3 V | <b>V</b>   |  |

| Address setup time                                   | tas             |                                                                                                        | 2          |                        | μS         |  |

| Chip disable setup time                              | tDF             |                                                                                                        | !<br>      | 30                     | ns         |  |

| Data setup time                                      | t <sub>DS</sub> |                                                                                                        | 2          |                        | μS         |  |

| Program pulse width                                  | tpy             |                                                                                                        | 1          | 10                     | ms         |  |

| Data hold time                                       | ¢DH             | <br>                                                                                                   | 2          |                        | μS         |  |

| Chip select delay                                    | tcs             | :                                                                                                      | <br> <br>  | 30                     | l ns       |  |

| Vpp rise and fall time                               | t <sub>RF</sub> |                                                                                                        | 1          |                        | l ns       |  |

| STANDARDIZED  MILITARY DRAWIN                        |                 | SIZE A REVISION LEVI                                                                                   | <u></u>    | 5962-87515<br>SHEET    |            |  |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                 | MEAISION LEA                                                                                           | <b>51.</b> |                        | 10         |  |

Powered by ICminer.com Electronic-Library Service CopyRight 2003

| Parameter                                   | Symbol                                             | Conditions                                                                            |      | Limits     | Unit                |

|---------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------|------|------------|---------------------|

|                                             |                                                    | T <sub>C</sub> = 25°C ±5°C<br>V <sub>CC</sub> = 6.0 V ±0.25 V,<br>Vpp = 12.5 V ±0.5 V | Min  | Max        | <br> <br> <br> <br> |

| Input load current                          | ILI                                                | V <sub>IN</sub> = V <sub>CC</sub> or GND                                              |      | <b>±10</b> | μ <b>Α</b>          |

| Vpp supply current during programming pulse | Ірр                                                | 2/ 3/                                                                                 |      | 30         | l mA                |

| V <sub>CC</sub> supply current              | ICC                                                | 2/                                                                                    |      | 80         | i mA                |

| Output low voltage during verify            | VOL                                                | I <sub>OL</sub> = 16 mA                                                               |      | 0.45       | V                   |

| Output high voltage during verify           | VOH                                                | I I <sub>OH</sub> = -4 mA                                                             | 2.4  | <br> <br>  | ٧                   |

| Input low voltage                           | ۸IΓ                                                |                                                                                       | -0.1 | 0.8        | <br>  V             |

| Input high voltage                          | \v_IH                                              |                                                                                       | 2.0  | VCC+0.3 V  | <br>  Y<br>         |

| Address setup time                          | tas                                                | 4/                                                                                    | 2    |            | μS                  |

| Address hold time                           | tah                                                | 4/                                                                                    | 2    |            | μS                  |

| Chip disable setup time                     | t <sub>DFP</sub>                                   | 4/ 5/                                                                                 | 0    | 130        | l ns                |

| Data setup time                             | t <sub>DS</sub>                                    | <u>4</u> /                                                                            | 2    |            | μS                  |

| V <sub>CC</sub> setup time                  | tycs                                               | 4/                                                                                    | 2    |            | l<br>lμs            |

| Program pulse width                         | tpW                                                | 4/ 6/                                                                                 | 0.95 | 1.05       | ms                  |

| Overprogram pulse width                     | topw                                               | 4/ 7/                                                                                 | 2.85 | 78.75      | <br>  ms<br>        |

| Data hold time                              | t <sub>DH</sub>                                    | 4/                                                                                    | 2    | :          | μS                  |

| CS/V <sub>pp</sub> setup time               | tcss                                               | 4/                                                                                    | 2    |            | l us                |

| Chip select delay                           | tcs                                                | 4/                                                                                    |      | 70         | ns                  |

| See footnotes at end of tabl                | e.                                                 |                                                                                       |      |            |                     |

| STANDARDIZE                                 |                                                    | SIZE<br>A                                                                             | ł    | 5962-87515 |                     |

|                                             | MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER |                                                                                       | VEL. | SHEET      |                     |

| TABLE III.                                | Programming      | characteristics for me      |          |            |                                       |

|-------------------------------------------|------------------|-----------------------------|----------|------------|---------------------------------------|

| Parameter                                 | Symbol           | Conditions                  | Lf       | mits       | Unit                                  |

| rarame ter                                |                  | T <sub>C</sub> = +25°C ±5°C | Min      | Max        |                                       |

| rogramming voltage                        | Vpp              | <u>8</u> /                  | 12.0     | 13.0       | ٧                                     |

| Supply voltage                            | YCCP             |                             | 4.75     | 5.25       | V                                     |

| Input high voltage                        | VIHP             |                             | 3.0      |            | V                                     |

| Input low voltage                         | VILP             |                             |          | 0.4        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Output high voltage                       | V <sub>OH</sub>  | <u>9</u> /                  | 2.4      |            | V                                     |

| Output low voltage                        | VOL              | <u>9</u> /                  |          | 0.40       | V                                     |

| Programming supply current                | Ірр              |                             |          | 50.0       | mA                                    |

| Programming pulse width                   | tpp              |                             | 0.2      | 10         | ms                                    |

| Address setup time                        | tAS              |                             | 1.0      |            | μS                                    |

| Data setup time                           | tos              |                             | 1.0      |            | μS                                    |

| Address hold time                         | t <sub>AH</sub>  |                             | 1.0      |            | μS                                    |

| Data hold time                            | t <sub>DH</sub>  |                             | 1.0      |            | μS                                    |

| Ypp rise and fall time                    | t <sub>R</sub> , | <u>10</u> /                 | 1.0      |            | μS                                    |

| Delay to verify                           | tyD              |                             | 1.0      |            | μς                                    |

| Verify pulse width                        | tγp              | , <u>i</u>                  | 2.0      |            | μS                                    |

| Verify data valid                         | t <sub>D</sub> γ | :                           | 1.0      |            | μS                                    |

| Verify HIGH to high-Z                     | t <sub>DZ</sub>  |                             |          | 1.0        | <br>  μS                              |

| See footnotes at end of tabl              | e.               |                             |          |            |                                       |

| STANDARDIZED                              |                  | SIZE<br>A                   |          | 5962-87515 |                                       |

| MILITARY DRAW<br>DEFENSE ELECTRONICS SUPP |                  |                             | ON LEVEL | SHEET      | 12                                    |

★ U. S. GOVERNMENT PRINTING OFFICE: 1968—549-90

| TABLE III. Programming characteristics for method C - Continued. $1/$ |                  |                                           |      |      |              |  |  |

|-----------------------------------------------------------------------|------------------|-------------------------------------------|------|------|--------------|--|--|

|                                                                       | C                | Conditions                                | Limi | Unit |              |  |  |

| Parameter                                                             | Symbol  <br>     | Conditions<br>T <sub>C</sub> = +25°C ±5°C | Min  | Max  | -  """       |  |  |

| Address setup time to latch                                           | tals             |                                           | 1.0  |      | <br>  μs<br> |  |  |

| Adress hold time from latch                                           | t <sub>ALH</sub> |                                           | 1.0  |      | μS           |  |  |

| Latch pulse width                                                     | t <sub>L</sub> p |                                           | 1.0  |      | μS           |  |  |

| Delay to function                                                     | t <sub>DP</sub>  |                                           | 1.0  |      | μS           |  |  |

| Hold from function                                                    | t <sub>HP</sub>  |                                           | 1.0  |      | μS           |  |  |

| Power up/down                                                         | tp               |                                           | 20.0 |      | ms           |  |  |

See figure 5 for the programming waveform: TTL inputs V<sub>IL</sub>  $\leq$  0.8 V, V<sub>IH</sub> > 2.0 V. AC power component adds 3 mA/MHz.

Input rise and fall times (10 percent to 90 percent): 5 ns

Input pulse levels: 0.0 V to 3.0 V Input timing reference level: 1.5 V Output timing reference level: 1.5 V

Tested initially and after any design or process change which may affect this parameter. Initial program pulse width tolerance is 1 ms  $\pm 5$  percent.

The length of the overprogram pulse may vary from 2.85 ms to 78.75 ms as a function of the iteration counter value X.

VCCP must be applied prior to Vpp.

9/ During verify operation.

$1\overline{0}$ / Measured 10 percent and 90 percent points.

### NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-87515 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 13   |

DESC FORM 193A **SEP 87**

| VCC             | CS/Vpp           | 00-07                                                                                       |

|-----------------|------------------|---------------------------------------------------------------------------------------------|

| 5 V ±10%        | VIL              | FF H                                                                                        |

| 5 V ±10%        | IV <sub>IH</sub> | High Z                                                                                      |

| v <sub>cc</sub> | V <sub>PP</sub>  | <br> Data in<br>                                                                            |

| VCC             | V <sub>IL</sub>  | Programmed<br>byte                                                                          |

|                 | 5 V ±10%         | 5 V ±10%   V <sub>IL</sub>   5 V ±10%   V <sub>IH</sub>   V <sub>CC</sub>   V <sub>PP</sub> |

/1 See table III.

Truth table for unprogrammed devices.

Programming method A and B,

devices 01-04

| 17            | Mode                     | <br> Outputs     | A <sub>12</sub>            | A <sub>11</sub> | l cs | A <sub>10</sub> | I A <sub>9</sub> | A <sub>8</sub>     | I v <sub>cc</sub>   | Power           |

|---------------|--------------------------|------------------|----------------------------|-----------------|------|-----------------|------------------|--------------------|---------------------|-----------------|

| Type<br> <br> | Mode                     |                  | 12                         | i ''<br>!       | 1    | 1               | 1<br>1           | <u> </u>           | <u> </u>            | 1               |

| A11           | Read                     | D <sub>OUT</sub> | A <sub>12</sub>            | A <sub>11</sub> | AIF  | A <sub>10</sub> | Ag               | A8                 | VCC                 | Icc             |

| All           | Not selected             | High-Z           | A <sub>12</sub>            | A <sub>11</sub> | VIH  | A <sub>10</sub> | A9               | A8                 | Vcc                 | ISB             |

| A11           | Program                  | D <sub>IN</sub>  | V <sub>ILP</sub> **        | Vpp**           | VILP | Latch           | VILP             | V <sub>IHP**</sub> | V <sub>CCP</sub> ** | Icc             |

| All           | <br> Program<br> inhibit | <br> <br> High=Z | <br> <br> V <sub>ILP</sub> | V <sub>PP</sub> | VILP | Latch           | VIHP             | VIHP               | vcc                 | ICC             |

| A11           | <br> Program verify      | D <sub>OUT</sub> | VILP                       | Vpp             | VILP | Latch           | VIHP             | VILP               | V <sub>CC</sub>     | Icc             |

| A11           | Blank check              | D <sub>OUT</sub> | VILP                       | V <sub>PP</sub> | AILb | Latch           | AIHb             | VILP               | Vcc                 | 1 <sub>CC</sub> |

\*\*  $V_{CCP} = 5.0 \text{ V } \pm 0.25 \text{ V}; V_{PP} = 13.5 \text{ V } \pm 0.5 \text{ V}; V_{ILP} = 0.4 \text{ V max.}; V_{IHP} = 3.0 \text{ V min.}$

Truth table for unprogrammed devices.

Programming method C,

devices 05 and 06

Figure 2. Truth tables.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87515

REVISION LEVEL

SHEET 15

DESC FORM 193A SEP 87 ☆ U.S. GOVERNMENT PRINTING OFFICE: 1967—549-098

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987-549-096

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Powered by ICminer.com Electronic-Library Service CopyRight 2003

6.4 Approved sources of supply. Approved sources of supply are listed herein. Additional sources will be added as they become available. The vendors listed herein have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to DESC-ECS.

| Military drawing     | Vendor           |                                       | Replacement            |

|----------------------|------------------|---------------------------------------|------------------------|

| part number          | CAGE             | similar part                          | military specification |

| •                    | number           | number 1/                             | part number            |

|                      | 1                |                                       |                        |

| 5962-8751501JX       | 66579            | WS57C49B-45DMB                        | [                      |

|                      | 1FN41            | AT27HC641-45DM/883                    |                        |

| 5962-8751501LX       | 66579            | WS57C49B-45TMB                        |                        |

|                      | 1FN41            | AT27HC642-45DM/883                    |                        |

| 5962-87515013X       | 66579            | I<br>IWS57C49B-45CMB                  | ·<br>[                 |

|                      | 1FN41            | AT27HC641-45LM/883                    |                        |

| 5962-8751501KX       | <br>  66579      | <br> WS57C49B-45FMB                   |                        |

| 5962-8751502JX       | 66579            | WS57C49B-55DMB                        |                        |

| 2902-8/3130207       | 005/9<br>  1FN41 | AT27HC641-55DM/883                    | 1                      |

|                      | 1 11 11 12       | 1                                     |                        |

| 5962-8751502LX       | 66579            | WS57C49B-55TMB                        |                        |

|                      | 1FN41            | AT27HC642-55DM/883                    | f<br>r                 |

| <br> 5962-87515023X  | 66579            | WS57C49B-55CMB                        |                        |

| 10302-0702000        | 1FN41            | IAT27HC641-55LM/883                   | į                      |

| 5962-8751502KX       | 66579            | WS57C49B-55FMB                        | <u> </u>               |

| 5962-8751503JX       | <br>  1FN41      | <br> AT27HC641-70DM/883               | <b>!</b><br>!          |

|                      | 66579            | WS57C49B-70DMB                        |                        |

| 5050 07515031 V      | 15141            | [<br> AT27HC642-70DM/883              |                        |

| 5962-8751503LX       | 1FN41<br>  66579 | WS57C49B-70TMB                        |                        |

|                      | 1                |                                       |                        |

| 5962-87515033X       | 1FN41<br>  66579 | AT27HC641-70LM/883<br> WS57C49B-70CMB | Į                      |

|                      | 1 00373          | W337C43B-70CHB                        |                        |

| 5962-8751503KX       | 66579            | WS57C49B-70FMB                        |                        |

| <br>  5962-8751504JX | 1FN41            | IAT27HC641-90DM/883                   |                        |

|                      | 66579            | WS57C49B-90DMB                        |                        |

| E062 07515041 V      | 1FN41            | AT27HC642-90DM/883                    |                        |

| 5962-8751504LX       | 1 66579          | WS57C49B-90TMB                        |                        |

|                      | 1 003/3          | [H3070430-30100                       | <del></del>            |

| 5962-87515043X       | j 1FN41          | AT27HC641-90LM/883                    | İ                      |

|                      | 66579            | WS57C49B-90CMB                        | <u> </u>               |

| 5962-8751504KX       | <br>  66579      | <br> WS57C49B-90FMB                   | 1                      |

| 330E-0/31304KX       | 1 00073          | 11122.0120-201110                     | <u> </u>               |

See footnote at end of table.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87515

REVISION LEVEL

SHEET

22

DESC FORM 193A SEP 87

**★ U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904**

| Military drawing part number | Vendor<br>  CAGE<br>  number | Vendor<br>  similar part<br>  number <u>1</u> / | Replacement  military specification   part number |

|------------------------------|------------------------------|-------------------------------------------------|---------------------------------------------------|

| 5962-8751505LX               | 65786                        | CY7C261-45WMB                                   |                                                   |

| 5962-87515053X               | 65786                        | CY7C261-45QMB                                   |                                                   |

| 5962-8751505KX               | 65786                        | CY7C261-45TMB                                   |                                                   |

| 5962-8751506LX               | 65786                        | CY7C261-55WMB                                   |                                                   |

| 5962-87515063X               | 65786                        | CY7C261-55QMB                                   |                                                   |

| <br> 5962-8751506KX          | 65786                        | CY7C261-55TMB                                   |                                                   |

$\frac{1}{2}$  Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

| Vendor CAGE<br>number | Vendor name<br>and address                                                         | Margin test<br>method | Programming<br>method |

|-----------------------|------------------------------------------------------------------------------------|-----------------------|-----------------------|

| 66579                 | WaferScale Intergration Inc.<br>47280 Kato Road<br>Fremont, CA 94538               | A                     | A                     |

| 1FN41                 | ATMEL Corporation<br>2095 Ringwood Ave<br>San Jose, CA 95131                       | A                     | 8                     |

| 65786                 | Cypress Semiconductor Corporation<br>3901 North First Street<br>San Jose, CA 95134 | n B                   | С                     |

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87515

REVISION LEVEL

23

DESC FORM 193A SEP 87

**☆ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-804**