|                           |                                 |                                       |                                       |      |         |          |      | RI     | EVISI   | LONS |             |             |              |      |        |             |      |      |      |           |

|---------------------------|---------------------------------|---------------------------------------|---------------------------------------|------|---------|----------|------|--------|---------|------|-------------|-------------|--------------|------|--------|-------------|------|------|------|-----------|

| LTR                       |                                 |                                       |                                       |      | D       | ESCR     | IPTI | ON     |         |      |             |             | D            | ATE  | (YR-MC | D-DA)       |      | APPR | OVED |           |

|                           |                                 |                                       |                                       |      |         |          |      |        |         |      |             |             |              |      |        |             |      |      |      |           |

| REV<br>SHEET              |                                 |                                       |                                       |      |         |          |      |        |         |      |             |             |              |      |        |             |      |      |      |           |

| REV                       | 15                              | 16                                    | 17                                    | 18   | 19      | 20       | 21   | 22     |         | 24   | 25          | -           |              |      | ļ      |             |      |      |      |           |

| SHEET  REV STAT  OF SHEET | US                              | L '`_                                 | <u>  ''</u>                           | RE   | 1       | <u> </u> | 1    | 2      | 23<br>3 | 4    | 25<br>5     | 6           | 7            | 8    | 9      | 10          | 11   | 12   | 13   | 14        |

| PMIC N/A                  |                                 | ZED                                   | · · · · · · · · · · · · · · · · · · · | PREP | ared e  | an!      | m. / | Her    |         | Di   | EFENS       |             |              | ONIC |        | PPLY<br>454 | CENT | i    | 1    | <u> </u>  |

| MII                       | AWIN  IG IS A  ALL DEI  ICIES C | RY<br>G<br>WAILAE<br>PARTME<br>OF THE | BLE •                                 | APPR | OVED BY | BY Y     | DATE | M<br>M | sh      | UN:  | VER<br>NOLI | SAL<br>THIO | PER          | LIC  | ERAI   | AL, IN      |      | FACE | ,    | re<br>——— |

| AMSC N/A                  |                                 |                                       |                                       | REVI | SION L  | EVEL.    |      |        |         | A    | ET          | ŀ           | 5 <b>726</b> | 8    | OF     |             |      | 27   |      | 1         |

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes B, Q, and M) and space application (device classes S and V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of radiation hardness assurance (RHA) levels are reflected in the PIN.

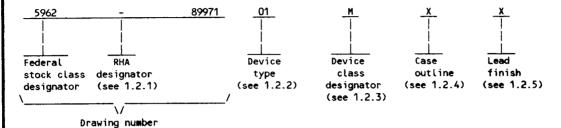

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes M, B, and S RHA marked devices shall meet the MIL-M-38510 specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>               | Frequency |

|-------------|----------------|---------------------------------------|-----------|

| 01          | 8744H-10       | Remote universal peripheral interface | 10 MHz    |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

| Device class | Device requirements documentation                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------|

| н            | Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883 |

| B or S       | Certification and qualification to MIL-M-38510                                                                          |

| Q or V       | Certification and qualification to MIL-I-38535                                                                          |

1.2.4 <u>Case outline(s)</u>. For device classes M, B, and S, case outline(s) shall meet the requirements in appendix C of MIL-M-38510 and as listed below. For device classes Q and V, case outline(s) shall meet the requirements of MIL-I-38535, appendix C of MIL-M-38510, and as listed below.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>2 |

| 1.2.5 <u>Lead finish</u> . The lead finish shall be as specific for classes Q and V. Finish letter "X" shall not be marked designation is for use in specifications when lead finished interchangeable without preference.                                                                                                                                                               | s on the microcia                      | rcult or its packaging. II                                                                               | ic ^         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|--------------|

| 1.3 Absolute maximum ratings. 1/                                                                                                                                                                                                                                                                                                                                                         |                                        |                                                                                                          |              |

| Storage temperature — — — — — — — — $V_{CC}$ supply voltage with respect to ground $(V_{SS})$ (excepted temperature(soldering 10 seconds) — — — — — — — Thermal resistance, junction—to—case $(\Theta_{JC})$ — — — — — — Junction temperature( $T_J$ ) — — — — — — — — — — Maximum power dissipation( $P_D$ ) — — — — — — — — — Maximum voltage $V_{PP}$ to $V_{SS}$ — — — — — — — — — — |                                        | -65°C to +150°C<br>-0.5 V to +7.0 V<br>+300°C<br>See MIL-M-38510, appendix<br>+150°C<br>2.0 W<br>+21.5 V | c            |

| 1.4 Recommended operating conditions.                                                                                                                                                                                                                                                                                                                                                    |                                        |                                                                                                          |              |

| Case operating temperature (T <sub>C</sub> ) Supply voltage, V <sub>C</sub> (                                                                                                                                                                                                                                                                                                            |                                        | -55°C to +125°C<br>5.0 V ±10%<br>2.2 V<br>2.5 V<br>0.7 V<br>10 MHz                                       |              |

| 1.5 <u>Digital logic testing for device classes Q and V</u> .                                                                                                                                                                                                                                                                                                                            |                                        |                                                                                                          |              |

| Fault coverage measurement of manufacturing<br>logic tests (MIL-STD-883, test method 5012)                                                                                                                                                                                                                                                                                               | <del>-</del> -                         | XX percent <u>2</u> /                                                                                    |              |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                  |                                        |                                                                                                          |              |

| 2.1 Government specifications, standards, bulletin, and<br>specifications, standards, bulletin, and handbook of the i<br>Index of Specifications and Standards specified in the sol<br>specified herein.                                                                                                                                                                                 | ssue listed in t                       | nat issue of the Departmen                                                                               | L OI Delense |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                           |                                        |                                                                                                          |              |

| MILITARY                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                                                                                                          |              |

| MIL-M-38510 - Microcircuits, General Spe<br>MIL-I-38535 - Integrated Circuits, Manuf                                                                                                                                                                                                                                                                                                     | ecification for.<br>facturing, Genera  | al Specification for.                                                                                    |              |

| STANDARDS                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                                                                          |              |

| MILITARY                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                                                                                                          |              |

| MIL-STD-480 - Configuration Control-Eng<br>MIL-STD-883 - Test Methods and Procedure                                                                                                                                                                                                                                                                                                      | ineering Changes,<br>es for Microelect | , Deviations and Waivers.<br>tronics.                                                                    |              |

| 1/ Stresses above the absolute maximum rating may cause operation at the maximum levels may degrade performa                                                                                                                                                                                                                                                                             | e permanent damag<br>ance and affect i | ge to the device. Extended reliability.                                                                  | i            |

| 2/ Values will be added when they become available.                                                                                                                                                                                                                                                                                                                                      |                                        |                                                                                                          |              |

|                                                                                                                                                                                                                                                                                                                                                                                          |                                        |                                                                                                          |              |

| STANDARDIZED<br>MILITARY DRAWING                                                                                                                                                                                                                                                                                                                                                         | SIZE<br>A                              |                                                                                                          | 5962-89971   |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                                                                                                                                                                                                                     |                                        | REVISION LEVEL                                                                                           | SHEET 3      |

BULLETIN

MILITARY

MTL-BUL-103

- List of Standardized Military Drawings (SMD's).

HANDBOOK

MILITARY

MIL-HDBK-780

- Standardized Military Drawings.

(Copies of the specifications, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. For device classes B and S, a full electrical characterization table for each device type shall be included in this SMD. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.4 herein.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 1.

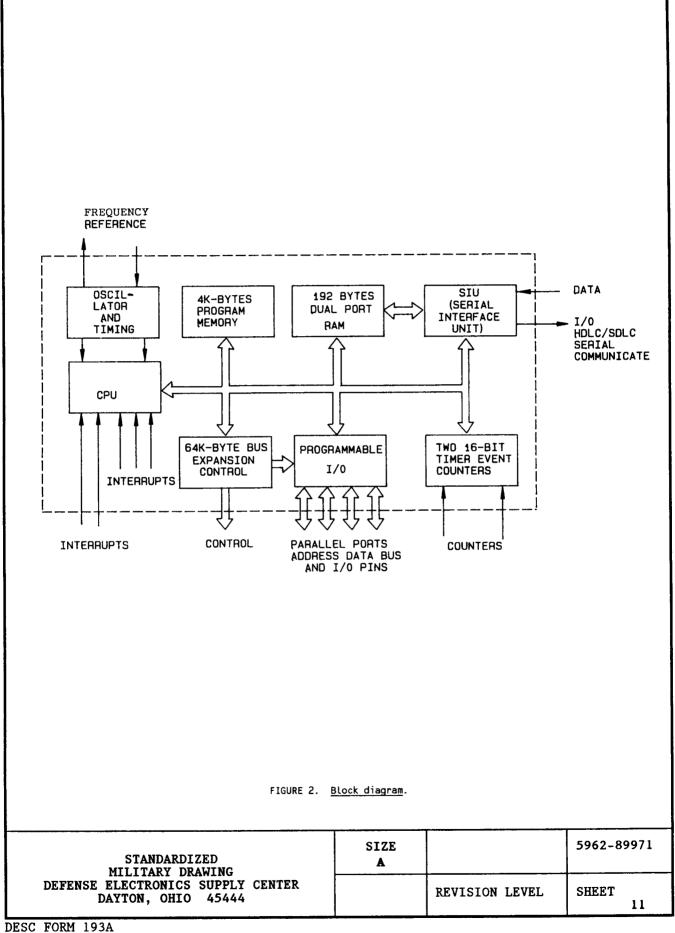

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 2.

- 3.2.4 Radiation exposure circuit. The radiation exposure circuit shall be specified when available.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes B and S shall be in accordance with MIL-M-38510. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 4    |

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes B and S shall be a "J" or "JAN" as required in MIL-M-38510. The certification mark for device classes Q and V shall be a "QML" as required in MIL-I-38535.

- 3.6 Certificate of compliance. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.3 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.2 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-1-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or device classes B and S in MIL-M-38510 or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change for device class M. For device class M, notification to DESC-ECC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-480.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device classes M, B, and S</u>. Device classes M, B, and S devices covered by this drawing shall be in microcircuit group number 105 (see MIL-M-38510, appendix E).

- 3.11 <u>Serialization for device class S</u>. All device class S devices shall be serialized in accordance with MIL-M-38510.

- 3.12 <u>Processing EPROM's</u>. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.12.1 <u>Erasure of EPROM's</u>. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.5.

- 3.12.2 <u>Programmability of EPROM's</u>. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.6 and table III.

- 3.12.3 <u>Verification of erasure of programmability of EPROM's</u>. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>5 |

| Test                                                        | Symbol                                                                                          | Conditions 1/                                                                                                                    | 1/  Group A 1    |     | Limits                     |                                       |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|-----|----------------------------|---------------------------------------|--|

|                                                             | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>  V <sub>CC</sub> = 5.0 V ±10%<br>  unless otherwise specifi | $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$ $V_{CC} = 5.0 \text{ V } \pm 10\%$ unless otherwise specified                       | subgroups        | Min | Max                        | •                                     |  |

| Output low voltage ports 1, 2, 3                            | v <sub>oL</sub>                                                                                 | V <sub>CC</sub> = 4.5 V,<br> V <sub>IN</sub> = V <sub>IH</sub> min, V <sub>IL</sub> max,<br> I <sub>OL</sub> = 1.6 mA <u>Z</u> / | 1, 2, 3          |     | 0.45                       | <b>V</b>                              |  |

| Output low voltage<br>ports 0, ALE,<br>PSEN                 | v <sub>0L1</sub>                                                                                | V <sub>CC</sub> = 4.5 V,<br>  V <sub>IN</sub> = V <sub>IH</sub> min, V <sub>IL</sub> max,<br>  I <sub>OL</sub> = 2.4 mA          | 1, 2, 3          |     | 0.45                       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

| Output high voltage ports 1, 2, 3                           | V <sub>CH</sub>                                                                                 | V <sub>CC</sub> = 4.5 V,<br>  V <sub>IN</sub> = V <sub>IH</sub> min, V <sub>IL</sub> max,<br>  I <sub>OH</sub> = -80 μA          | 1, 2, 3          | 2.4 |                            | V                                     |  |

| Output high voltage<br>port O, ALE,<br>PSEN                 | V <sub>ОН</sub> 1                                                                               | V <sub>CC</sub> = 4.5 V,<br>  V <sub>IN</sub> = V <sub>IH</sub> min, V <sub>IL</sub> max,<br>  I <sub>OH</sub> = -400 μA         | 1, 2, 3          | 2.4 |                            | V                                     |  |

| Logical O input<br>current ports<br>1, 2, 3                 | IIL                                                                                             | v <sub>IN</sub> = 0.45 v <u>3</u> /                                                                                              | 1, 2, 3          |     | <br>  <b>-500</b><br> <br> | μA                                    |  |

| Input high current<br>to RST/VPD<br>for reset               | I <sub>IH1</sub>                                                                                | v <sub>IN</sub> = v <sub>CC</sub> -1.5 v                                                                                         | 1, 2, 3          |     | 500                        | μΑ                                    |  |

| Input leakage<br>current to<br>port O                       | I IL1                                                                                           | 0.45 V < V <sub>IN</sub> < V <sub>CC</sub>                                                                                       | 1, 2, 3          |     | ±125                       | μΑ                                    |  |

| Logical O input<br><u>cu</u> rrent to<br>EA/V <sub>PP</sub> | I <sub>I</sub> IL1                                                                              | v <sub>IN</sub> = 0.45 v                                                                                                         | 1, 2, 3          |     | <br>  -15<br> <br>         | mA                                    |  |

| Power supply current                                        | Icc                                                                                             | V <sub>CC</sub> = 5.5 V,   V <sub>IN</sub> = 5.5 V                                                                               | 1, 2, 3          |     | <br>  300<br>              | mA                                    |  |

| Logical O input<br>current XTAL2                            | I <sub>IL2</sub>                                                                                | XTAL1 = V <sub>SS</sub> ,<br>  V <sub>IL</sub> = 0.45 V                                                                          | <br> 1, 2, 3<br> |     | -3.5                       | m.A                                   |  |

| Logical input current to EA/V <sub>PP</sub>                 | IIH                                                                                             |                                                                                                                                  | 1, 2, 3          |     | <br>  500<br>              | μ <b>Α</b>                            |  |

See footnotes at end of table.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-8 <del>99</del> 71 |

|------------------------------------------------------|-----------|----------------|-------------------------|

| DEFENSE ELECTROMICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>6              |

| Test                                    | Symbol            | Conditions 1/                                                                                                   | Group A   | Limi                    | ∐<br>∐Unit              |    |

|-----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|-----------|-------------------------|-------------------------|----|

|                                         |                   | $-55^{\circ}C \le T_{C} \le +1\overline{2}5^{\circ}C$ $V_{CC} = 5.0 \text{ V } \pm 10\%$ unless otherwise speci | subgroups | Min                     | Max                     |    |

| Capacitance of<br>I/O buffer            | c <sup>10</sup>   | Test frequency = 1 MHz 4                                                                                        | / 4       |                         | 10                      | pF |

| Functional test                         |                   | See 4.4.1b                                                                                                      | 7, 8      |                         |                         |    |

| ALE pulse width                         | t <sub>LHLL</sub> |                                                                                                                 | 9, 10, 11 | 2t <sub>CLCL</sub> -40  |                         | ns |

| Address setup to ALE                    | †AVLL             | See figure 3 5/                                                                                                 | 9, 10, 11 | t <sub>CLCL</sub> -40   |                         | ns |

| Address hold after<br>ALE               | t <sub>LLAX</sub> | See figure 3 <u>5</u> /                                                                                         | 9, 10, 11 | t <sub>CLCL</sub> -35   |                         | ns |

| ALE to valid Instr<br>In                | t <sub>LLIV</sub> | See figure 3 5/                                                                                                 | 9, 10, 11 | <br>                    | 4t <sub>CLCL</sub> -150 | ns |

| ALE to PSEN                             | t <sub>LLPL</sub> | See figure 3 5/                                                                                                 | 9, 10, 11 | t <sub>CLCL</sub> -25   |                         | ns |

| PSEN pulse width                        | t <sub>PLPH</sub> | See figure 3 5/                                                                                                 | 9, 10, 11 | 3t <sub>CLCL</sub> -60  |                         | ns |

| PSEN to valid Instr<br>In               | t <sub>PLIV</sub> | See figure 3 5/                                                                                                 | 9, 10, 11 |                         | 3t <sub>CLCL</sub> -150 | ns |

| Input In <u>str</u> hold<br>after PSEN  | t <sub>PXIX</sub> | See figure 3 5/                                                                                                 | 9, 10, 11 | 0                       |                         | ns |

| Input In <u>str</u> float<br>after PSEN | t <sub>PXIZ</sub> | See figure 3 <u>3/5</u> /                                                                                       | 9, 10, 11 |                         | t <sub>CLCL</sub> -20   | ns |

| Address <u>vali</u> d<br>after PSEN     | <sup>t</sup> PXAV | See figure 3 <u>3</u> / <u>5</u> /                                                                              | 9, 10, 11 | t <sub>CLCL</sub> -8    | <u> </u>                | ns |

| Address to valid<br>Instr In            | t <sub>AVIV</sub> | See figure 3 5/                                                                                                 | 9, 10, 11 |                         | 5t <sub>CLCL</sub> -150 | ns |

| Ad <u>dres</u> s float to<br>PSEN       | tAZPL             | See figure 3 5/                                                                                                 | 9, 10, 11 | -25                     |                         | ns |

| RD pulse width                          | t <sub>RLRH</sub> |                                                                                                                 | 9, 10, 11 | 6t <sub>CLCL</sub> -100 |                         | ns |

See footnote at end of table.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 7    |

| Test                               | Symbol                     | Conditions 1/       |                                           | Group A   | Limit                   | Unit                    |    |

|------------------------------------|----------------------------|---------------------|-------------------------------------------|-----------|-------------------------|-------------------------|----|

|                                    |                            | V <sub>CC</sub> = 5 | c ≤ +125°C<br>.O V ±10%<br>wise specified | subgroups | Min                     | Nax                     | ļ  |

| R pulse width                      | t <sub>WLWH</sub>          | See figure 3        | <u>5</u> /                                | 9, 10, 11 | 6t <sub>CLCL</sub> -100 |                         | ns |

| ddress hold after<br>ALE           | tLLAX                      | See figure 3        | <u>2</u> / <u>5</u> /                     | 9, 10, 11 | t <sub>CLCL</sub> -35   |                         | ns |

| D to valid<br>Data In              | t <sub>RLDV</sub>          | See figure 3        | 5/                                        | 9, 10, 11 |                         | 5t <sub>CLCL</sub> -165 | ns |

| a <u>ta</u> hold after<br>RD       | <sup>t</sup> RHDX          | See figure 3        | <u>5</u> /                                | 9, 10, 11 | 0                       |                         | ns |

| a <u>ta</u> float after<br>RD      | t <sub>kHDZ</sub>          | See figure 3        | 2/ 5/                                     | 9, 10, 11 |                         | 2t <sub>CLCL</sub> -70  | ns |

| LE to valid<br>Data In             | t <sub>LLDV</sub>          | See figure 3        | <u>5</u> /                                | 9, 10, 11 |                         | āt <sub>CLCL</sub> -150 | ns |

| ddress to<br>valid Data In         | <sup>t</sup> AVPV          | See figure 3        | <u>5</u> /                                | 9, 10, 11 |                         | 9t <sub>CLCL</sub> -165 | ns |

| LE to UR or RB                     | tLLWL                      | See figure 3        | <u>5</u> /                                | 9, 10, 11 | 3t <sub>ELEL</sub> -50  | 3t <sub>CLCL</sub> +50  | ns |

| ddress to WR                       | tavwL                      | See figure 3        | 5/                                        | 9, 10, 11 | 4t <sub>CLCL</sub> -130 |                         | ns |

| R or RD high to<br>ALE high        | t <sub>WHLH</sub>          | See figure 3        | 5/                                        | 9, 10, 11 | t <sub>CLCL</sub> -50   | t <sub>CLCL</sub> +50   | ns |

| Data valid to WR<br>transition     | t <sub>DVWX</sub>          | See figure 3        | <u>5</u> /                                | 9, 10, 11 | t <sub>CLCL</sub> -70   |                         | ns |

| Da <u>ta</u> setup before<br>WR    | <sup>t</sup> qv <b>w</b> H | See figure 3        | <u>5</u> /                                | 9, 10, 11 | 7t <sub>CLCL</sub> -150 |                         | ns |

| Da <u>ta</u> hold after<br>WR      | t <sub>WHQX</sub>          | See figure 3        | <u>5</u> /                                | 9, 10, 11 | t <sub>CLCL</sub> -50   |                         | ns |

| Ad <u>dr</u> ess float after<br>RD | <sup>t</sup> RLAZ          | See figure 3        | <u>2</u> / <u>5</u> /                     | 9, 10, 11 |                         | 25                      | ns |

| Data clock                         | t <sub>DCY</sub>           | See figure 3        | <u>5</u> /                                | 9, 10, 11 | 500                     | -                       | ns |

See footnotes at end of table.

| STANDARDĮZED<br>MILITARY D <b>RAW</b> ING            | SIZE<br>A                             | The second secon | 5962-89971 |

|------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYFON, OHIO 45444 | om televiti i tu timme i tu time time | REVISION LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SHEET<br>8 |

|                        | TABI              | E I. <u>Electrical p</u>                                          | erformance cha          | racteristics | - Continue  | ed. |                |

|------------------------|-------------------|-------------------------------------------------------------------|-------------------------|--------------|-------------|-----|----------------|

| Test                   | Symbol            | Conditio                                                          | ons 1/                  | Group A _    | <u>Limi</u> | ts  | <br>  Unit<br> |

|                        |                   | -55°C ≤ T <sub>C</sub><br>V <sub>CC</sub> = 5.C<br>unless otherwi | y ±10%<br>ise specified | Subgi oups   | Min         | Max |                |

| Data clock low         | tucL              | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 180         |     | ns             |

| Data clock high        | t <sub>DCH</sub>  | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 100         |     | ns             |

| Transmit data<br>delay | t <sub>1D</sub>   | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    |             | 180 | ns             |

| Data setup time        | tpss              | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 40          |     | ns             |

| Data hold time         | t <sub>DHS</sub>  | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 40          |     | ns             |

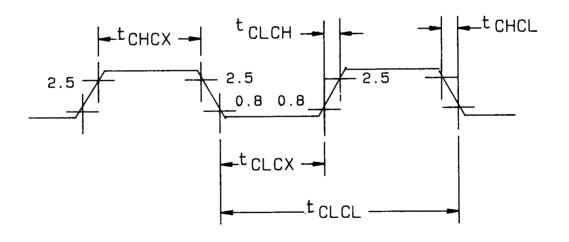

| Oscillator period      | tcLCL             | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 100         | 167 | ns             |

| High time              | <sup>t</sup> cHCX | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 20          |     | ns             |

| Low time               | tcLcx             | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    | 20          |     | ns             |

| Rise time              | <sup>t</sup> cLCH | See figure 3                                                      | <u>5</u> /              | 9, 10, 11    |             | 20  | ns             |

| Fall time              | t <sub>CHCL</sub> | See figure 3                                                      | <u>2</u> / <u>5</u> /   | 9, 10, 11    |             | 20  | ns             |

$<sup>\</sup>underline{1}/$  All testing to be performed using worst case conditions, unless otherwise specified.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>9 |

V<sub>OL</sub> is degraded when the device rapidly discharges external capacitance. This ac noise is most pronounced during emission of address data. When using external memory, locate the latch or buffer as close to the device as possible.

<sup>3/</sup> Except P1.6 (pin 7), P3.0 (pin 10) and P3.1 (pin 11) which are equal to -700  $\mu$ A max.

<sup>&</sup>lt;u>4/</u> See 4.4.1c.

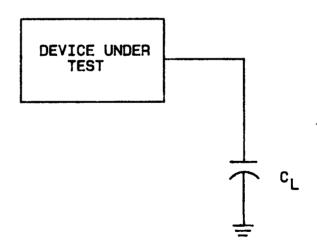

$<sup>\</sup>frac{5/}{\text{is 80 pF.}}$  Output Load capacitance, C<sub>L</sub>, for port O, ALE,  $\overline{\text{PSEN}}$  outputs is 100 pF. Load capacitance for all other outputs is 80 pF.  $1/\text{t}_{\text{CLCL}} = 6$  MHz to 10 MHz.

| Device type        |                    | 01               | Device type        | 0               |                  |

|--------------------|--------------------|------------------|--------------------|-----------------|------------------|

| Case outline       | ļ                  | 2                | Case outline       | Q               | 1                |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>port | Terminal<br>number | Terminal symbol | Terminal<br>port |

| 01                 |                    | P 1.0            | 21                 | A8              | P 2.0            |

| 02                 |                    | P 1.1            | 22                 | A9              | P 2.1            |

| 03                 |                    | P 1.2            | 23                 | A10             | ₱ 2.2            |

| 04                 |                    | P 1.3            | 24                 | 911             | P 2.3            |

| 05                 |                    | P 1.4            | 25                 | A12             | P 2.4            |

| 06                 |                    | P 1.5            | 26                 | A13             | P 2.5            |

| 07                 | RTS                | P 1.6            | 27                 | A14             | P 2.6            |

| 08                 | CTS                | P 1.7            | 28                 | A15             | ₱ 2.7            |

| . 09               | RST                |                  | 29                 |                 | PSEN             |

| 10                 | I/O/RXD            | P 3.0            | 30                 | PROG            | ALE              |

| 11                 | DATA/TDX           | P 3.1            | 31                 | VPP             | EA               |

| 12                 | INTO               | P 3.2            | 32                 | AD7             | P 0.7            |

| 13                 | INT1               | P 3.3            | 33                 | AD6             | ₽ 0.6            |

| 14                 | то                 | P 3.4            | 34                 | AD5             | P 0.5            |

| . 15               | SCLK/T1            | P 3.5            | 35                 | AD4             | P 0.4            |

| 16                 | WR                 | P 3.6            | 36                 | AD3             | P 0.3            |

| 17                 | RD                 | P 3.7            | 37                 | AD2             | P 0.2            |

| 18                 |                    | XTAL2            | 38                 | AD1             | P 0.1            |

| 19                 |                    | XTAL1            | 39                 | ADO             | P 0.0            |

| 20                 |                    | v <sub>ss</sub>  | 40                 |                 | v <sub>cc</sub>  |

FIGURE 1. Terminal connections.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A | ;              | <del>59</del> 62- <del>899</del> 71 |

|------------------------------------------------------|-----------|----------------|-------------------------------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHRET                               |

# MEMORY ACCESS Program Memory Read Cycle - t CY (SEE NOTE) H-ILLIV -LHLL ALE \_t թլթн t<sub>PXAV</sub> PSEN tLLAX-XIX9 tAVLL-INSTR IN PORT 0 INSTR IN A7-A0 TINSTR IN A7-A0 ADDRESS A15-A8 ADDRESS A15-A8 ADDR OR SFR-P2 Data Memory Read Cycle —<sup>է</sup>լ Lov t WHLH-ALE **PSEN** ±'ALRH RD —<sup>t</sup> AHDZ talov -<sup>t</sup>RHDX – <sup>t</sup>LLAX DATA IN A7-A0 PORT 0 t<sub>RLAZ</sub> ADDRESS A15-A8 OR SFR-P2 PORT 2 OR SER-PZ -tavwl -\_tavov -Data Memory Write Cycle ALE PSEN 80 \_t ovwx - <sup>t</sup>avwh-±whox• DATA OUT PORT 0 ADDRESS A15-AB OR SFR-P2 PORT 2 ADDRESS NOTE: $t_{CY} = 4$ Clock cycles. FIGURE 3. Switching test circuit and waveforms - Continued. 5962-89971 SIZE STANDARDIZED Α MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER SHEET REVISION LEVEL DAYTON, OHIO 45444 13

# SERIAL I/O WAVEFORMS Synchronous Data Transmission --t<sub>DCY</sub> --<sup>t</sup>DCL -SCLK -<sup>t</sup>DCH -DATA Synchronous Data Reception \_tocy -<sub>-tocl</sub> ---SCLK DATA —<sup>t</sup>DHS – toss -FIGURE 3. Switching test circuit and waveforms - Continued. SIZE 5962-89971 STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 **A** REVISION LEVEL SHEET 14 DESC FORM 193A

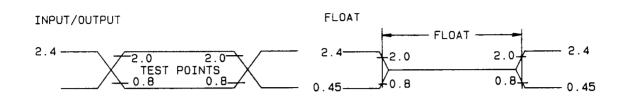

# AC Testing Input, Output, Float Waveforms

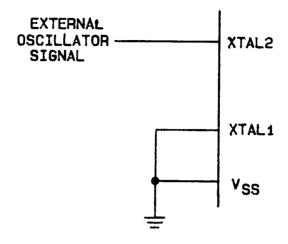

# External Clock Drive XTAL2

FIGURE 3. Switching test circuit and waveforms - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>15 |

# External Drive Configuration

# Output Load Circuit

FIGURE 3. <u>Switching test circuit and waveforms</u> - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE BLECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>16 |

#### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein). For device classes B and S, sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 and the device manufacturer's QM plan.

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes B and S, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to qualification and quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-I-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device classes M, B, and S.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. For device class M, the test circuit shall be submitted to DESC-ECC for review with the certificate of compliance. For device classes B and S, the test circuit shall be submitted to the qualifying activity.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. A data retention stress test shall be included as part of the screening procedure and shall consist of following steps:

#### Margin test method A.

- (1) Program greater than 95 percent of the bit locations, including the slowest programming cell (see 3.12.2). The remaining cells shall provide a worst case speed pattern.

- (2) Bake, unbiased, for 72 hours at +140°C to screen for data retention lifetime.

- (3) Perform a margin test using  $V_M$  = +5.9 V at +25°C using loose timing (i.e.,  $t_{ACC}$  > 1  $\mu$ s).

- (4) Perform dynamic burn-in (see 4.2.1a).

- (5) Margin at  $V_M = 5.9 \text{ V}$ .

- (6) Perform electrical tests (see 4.2).

- (7) Erase (see 3.12.1), except devices submitted for groups A, B, C, and D testing.

- (8) Verify erasure (see 3.12.3).

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>17 |

#### Margin test method B.

- (1) Program at 25°C, 100 percent of the bits.

- (2) Bake, unbiased, for 24 hours at 250°C.

- (3) Perform margin test at  $V_M = 5.9 \text{ V}$ .

- (4) Erase (see 3.12.1).

- (5) Perform interim electrical tests in accordance with table IIA.

- (6) Program 100 percent of the bits and verify (see 3.12.2).

- (7) Perform burn-in (see 4.2.1a).

- (8) One-hundred percent test at 25°C (group A, subgroups 1 and 7).  $V_{M}$  = 5.9 V with loose timing, apply PDA.

- (9) Perform remaining final electrical subgroups and group A testing.

- (10) Erase. Devices may be submitted for groups B, C, and D at this time.

- (11) Verify erasure (see 3.12.3). Steps 1 through 4 are performed at wafer level.

# 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be submitted to DESC-ECC with the certificate of compliance and shall be under the control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MIL-I-38535 and as detailed in table IIB herein.

#### 4.3 Qualification inspection.

- 4.3.1 <u>Qualification inspection for device classes B and S</u>. Qualification inspection for device classes B and S shall be in accordance with MIL-M-38510. Inspections to be performed shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.3.2 Qualification inspection for device classes Q and V. Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.4 <u>Conformance inspection</u>. Quality conformance inspection for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein) and as specified herein. Quality conformance inspection for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. Inspections to be performed for device classes M, B, and S shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5). Technology conformance inspection for classes Q and V shall be in accordance with MIL-I-38535 including groups A, B, C, D, and E inspections and as specified herein except where option 2 of MIL-I-38535 permits alternate in-line control testing.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                 | 5962-89971  |

|------------------------------------------------------|-----------|-----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYFON, OHIO 45444 |           | REVISION: LEVEL | SHEET<br>18 |

# TABLE IIA. Electrical test requirements.

| Test<br>requirements                                       | Subgroups<br>(per method 5005, table I) |                                                   |                                                   | Subgroups<br>(per MIL-I-38535,<br>table III)     |                                    |

|------------------------------------------------------------|-----------------------------------------|---------------------------------------------------|---------------------------------------------------|--------------------------------------------------|------------------------------------|

|                                                            | Device<br> class<br>  M                 | Device<br> class<br>  B                           | <br> Device<br> class<br>  S                      | Device<br> class<br>  Q                          | Device<br> class<br>  V            |

| Interim electrical<br>  parameters<br>  (see 4.2)          |                                         |                                                   | 1, 7, 9                                           | <br> <br>                                        | 1, 7, 9                            |

| <br> Final electrical<br>  parameters<br>  (see 4.4)       | 1, 2, 3, 7,<br>8, 9, 10, 11<br>1/       | <br> 1, 2, 3, 7,<br> 8, 9, 10, 11<br>  <u>2</u> / | <br> 1, 2, 3, 7,<br> 8, 9, 10, 11<br>  <u>2</u> / | <br> 1, 2, 3, 7,<br> 8, 9, 10,<br> 11 <u>1</u> / | 1, 2, 3, 7,   8, 9, 10,   11       |

| <br> Group A test<br>  requirements<br>  (see 4.4)         | 1, 2, 3, 4,<br>17, 8, 9, 10,            | <br> 1, 2, 3, 4,<br> 7, 8, 9, 10,<br> 11          | <br> 1, 2, 3, 4,<br> 7, 8, 9, 10,<br> 11          | <br> 1, 2, 3, 4,<br> 7, 8, 9,<br> 10, 11         | 1, 2, 3, 4,<br>17, 8, 9,<br>10, 11 |

| Group B end-point electrical parameters (see 4.4)          |                                         | <br> <br>                                         | <br> 2, 8a, 10<br> <br>                           |                                                  |                                    |

| Group C end-point<br>electrical<br>parameters<br>(see 4.4) | 2, 8a, 10                               | <br> 2, 8a, 10<br> <br>                           |                                                   | <br> 2, 8a, 10<br>                               | <br>  2, 8a, 10<br> <br>           |

| Group D end-point<br>electrical<br>parameters<br>(see 4.4) | <br> 2, 8a, 10<br>                      | <br> 2, 8a, 10<br> <br>                           | <br> 2, 8a, 10<br> <br>                           | <br> 2, 8a, 10<br> <br>                          | <br> 2, 8a, 10<br> <br>            |

| Group E end-point electrical parameters (see 4.4)          | 2, 8a, 10                               | <br> 2, 8a, 10<br> <br>                           | 2, 8a, 10                                         | <br> 2,8a,10<br>                                 | <br> 2, 8a, 10<br>                 |

$<sup>\</sup>underline{1}$ / PDA applies to subgroup 1.

# 4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. For device class M, subgroups 7 and 8 tests shall consist of verifying the EPROM pattern specified and instruction set. The instruction set forms a part of the vendor's test tape and shall be maintained and available from the approved source of supply. For device classes B and S, subgroups 7 and 8 tests shall include verification of the device functionality (including verification of EPROM pattern specified and instruction set). For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device; these tests shall have been graded in accordance with MIL-STD-883, test method 5012 (see 1.5 herein).

- c. Subgroup 4(C<sub>10</sub> measurements) shall be measured only for the initial test and after process or design changes which may affect input capacitance. A minimum sample size of five devices with zero rejects shall be required.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-89971  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>19 |

<sup>2</sup>/ PDA applies to subgroups 1 and 7.

#### TABLE IIB. Additional screening for device class V.

| Test                               | MIL-STD-883, test method                | Lot requirement |

|------------------------------------|-----------------------------------------|-----------------|

| Particle impact<br>noise detection | 2020                                    | 100%            |

| Internal visual                    | 2010, condition A or approved alternate | 100x            |

| Nondestructive                     | 2023 or<br>approved alternate           | 100x            |

| Reverse bias burn-in               | 1015                                    | 100%            |

| Burn-in                            | 1015, total of 240 hours<br>at +125°C   | 100x            |

| Radiographic                       | 2012                                    | 100%            |

- 4.4.2 <u>Group B inspection</u>. The group B inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.3 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.3.1 Additional criteria for device classes M, B, and S. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition C or D. For device class M, the test circuit shall be submitted to DESC-ECC for review with the certificate of compliance. For device classes B and S, the test circuit shall be submitted to the qualifying activity.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- d. All devices selected for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified.

- 4.4.3.2 <u>Additional criteria for device classes Q and V</u>. The steady-state life test duration, test condition and test temperature or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The steady-state life test circuit shall be submitted to DESC-ECC with the certificate of compliance and shall be under the control of the device manufacturer's TRB in accordance with MIL-I-38535.

- 4.4.4 Group D inspection. The group D inspection end-point electrical parameters shall be as specified in table IIA herein.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE |                | 5962-89971 |

|------------------------------------------------------|------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |      | REVISION LEVEL | SHEET 20   |

- 4.4.5 Group E inspection. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes B, S, Q, and V shall be M, D, R, and H and for device class M shall be M and D. RHA quality conformance inspection sample tests shall be performed at the RHA level specified in the acquisition document.

- a. RHA tests for device classes B and S for levels M, D, R, and H or for device class M for levels M and D shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- b. End-point electrical parameters shall be as specified in table IIA herein.

- c. Prior to total dose irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table IIA herein.

- d. For device classes M, B, and S, the devices shall be subjected to radiation hardness assured tests as specified in M1L-M-38510 for RHA level being tested, and meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A$  = +25°C  $\pm$ 5 percent, after exposure.

- e. Prior to and during total dose irradiation testing, the devices shall be biased to establish a worst case condition as specified in the radiation exposure circuit.

- f. For device classes M, B, and S, subgroups 1 and 2 in table V, method 5005 of MIL-STD-883 shall be tested as appropriate for device construction.

- g. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

- 4.5 <u>Erasing procedure</u>. The recommended erasure procedure is exposure to ultraviolet light (at 2537 Angstroms) to an integrated dose of at least 15 W-s/cm<sup>2</sup> rating for 20 to 30 minutes, at a distance of about 1 inch, should be sufficient.

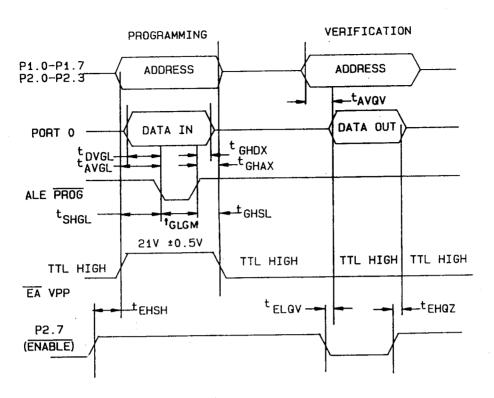

- 4.6 <u>Programming procedures</u>. The programming characteristics in table III and the following procedures shall be used for programming the device:

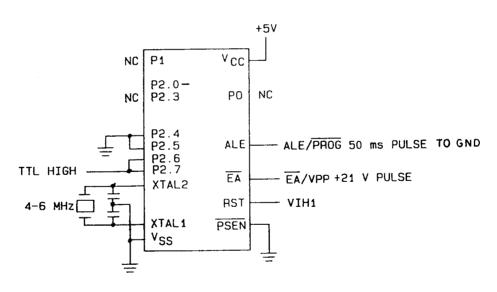

- a. Connect the device in the electrical configuration (see figure 4) for programming. The waveforms of figure 4 and programming characteristics of table III shall apply.

- b. Initially and after each erasure, all bits are in the high "H" state. To be programmed, the device must be running with a 4 to 6 MHz oscillator. The address of an EPROM location to be programmed is applied to port 1 and pins P2.0-P2.3 of port 2, while the data byte is applied to port 0. Pins P2.4-P2.6 and PSEN should be held low, and P2.7 and RST high. (These are all TTL levels except RST, which requires 2.5 V for high). EA/V<sub>PP</sub> is held normally high, and is pulsed to +21 V. While EA/V<sub>PP</sub> is at 21 V, The ALE/PROG pin, which is normally being held high, is pulsed low for 50 ms. The EA/V<sub>PP</sub> is returned to high.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89971  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>21 |

TABLE III. Programming and verification characteristics.

| Symbol              | Parameter <u>1</u> /            | Min                 | Max                 | Units |

|---------------------|---------------------------------|---------------------|---------------------|-------|

| V <sub>PP</sub>     | Programming supply voltage      | 20.5                | 21.5                | V     |

| I <sub>PP</sub>     | Programming current             |                     | 30                  | mA .  |

| 1/t <sub>CLCL</sub> | Oscillator frequency            | 4                   | 6                   | MHz   |

| <sup>t</sup> AVGL   | Address setup to PROG           | 48t <sub>CLCL</sub> |                     | ns    |

| <sup>†</sup> GHAX   | Address hold after PROG         | 48t <sub>CLCL</sub> |                     | ns    |

| <sup>t</sup> DVGL   | Data setup to PROG              | 48t <sub>CLCL</sub> |                     | ns    |

| t <sub>GHDX</sub>   | Data hold after PROG            | 48t <sub>CLCL</sub> |                     | ns    |

| t <sub>EHSH</sub>   | ENABLE high to V <sub>PP</sub>  | 48t <sub>CLCL</sub> |                     | ns    |

| <sup>t</sup> SHGL   | V <sub>PP</sub> setup to PROG   | 10                  |                     | μS    |

| <sup>t</sup> GHSL   | V <sub>PP</sub> hold after PROG | 10                  |                     | μS    |

| <sup>t</sup> GLGH   | PROG width                      | 45                  | 55                  | ms    |

| tAVQV               | Address to data valid           |                     | 48t <sub>CLCL</sub> | ns    |

| tELQV               | ENABLE to data valid            |                     | 48t <sub>CLCL</sub> | ns    |

| t <sub>EHQZ</sub>   | Data float after ENABLE         | 0                   | 48t <sub>CLCL</sub> | ns    |

$\underline{1}/$  The following conditions apply during programming and verification:

- a. V<sub>SS</sub> = 0 V

- b.  $+4.5 \text{ V} \leq \text{V}_{CC} \leq +5.5 \text{ V}$

- c.  $21^{\circ}C \leq T_{C} \leq 27^{\circ}C$

- d. See figure 4

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5 <del>96</del> 2-89971 |

|------------------------------------------------------------------------------------|-----------|----------------|-------------------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>22             |

# EPROM Programming Security Bit Programming and Verification Waveforms

Security Bit Programming Configuration

FIGURE 4. EPROM programming configuration and waveforms.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89971 |

|---------------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                             |           | REVISION LEVEL | SHEET 23   |

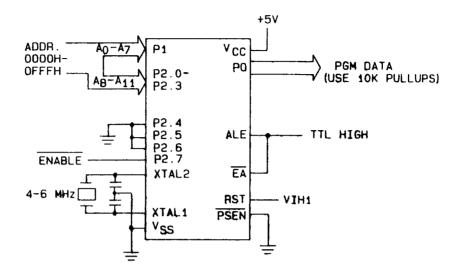

# Programming Verification Configuration

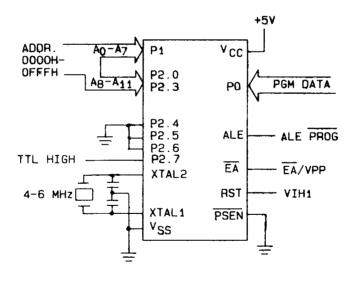

#### Programming Configuration

FIGURE 4. EPROM programming configuration and waveforms - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5 <del>962-899</del> 71 |

|------------------------------------------------------|-----------|----------------|-------------------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYFOR, ONIO 45444 |           | REVISION LEVEL | SHEET<br>24             |

#### PACKAGING

5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V.

#### 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.1.2 Substitutability. Device classes B and Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.3 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and which SMD's are applicable to that system. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-ECC, telephone (513) 296-6022.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECC, Dayton, Ohio 45444, or telephone (513) 296-8526.

- 6.5 Symbols, definitions, and functional descriptions.

| Symbol     | Туре | Name and Description                                                                                                                                                                                                                                           |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADO-AD7    | 1/0  | Port 0 (PO.O-PO.7): Port 0 is an 8-bit open drain bidirectional I/O port. It is also the multiplex low-order address and data bus when using external memory. It is used for data output during program verification. Port 0 can sink/source six LS TTL loads. |

|            | 1/0  | Port 1 (P1.0-P1.7): Port 1 is an 8-bit quasi-bidirectional I/O. It is used for the low-order address byte during program verification. Port 1 can sink/source four LS TTL loads.                                                                               |

| RTS (P1.6) | 0    | Request-to-Send output: A low indicates that the device is ready to transmit.                                                                                                                                                                                  |

| CTS (P1.7) | I    | Clear-to-Send input: A low indicates that a receiving station is ready to receive.                                                                                                                                                                             |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89971  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>25 |

| Symbol        | Туре | Name and Description                                                                                                                                                                                                                                                                                                                        |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A8-A15        | 1/0  | Port 2 (P2.0-P2.7): Port 2 is an 8-bit quasi-bidirectional I/O port. It also emits the high-order address byte when accessing external memory. It is used for the high-order address and the control signals during program verification. Port 2 sink/source four LS TTL loads.                                                             |

|               | 1/0  | Port 3 (P3.0-P3.7): Port 3 is an 8-bit quasibidirectional I/O port. It also_contains the interrupt, timer, serial port, and RD and WR pins that are used by various options. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate. Port 3 can sink/source four LS TTL loads. |

| I/O R×D (P3.0 | ) I  | In point-to-point or multipoint configurations, this pin controls the direction of pin P3.1. Serves as Receive Data input in loop and diagnostic modes.                                                                                                                                                                                     |

| DATA TXD (P3. | 1) 0 | In point-to-point or multipoint configurations, this pin functions as data input/output. In loop mode, it serves as transmit pin. A "O" written to this pin enables diagnostic mode.                                                                                                                                                        |

| INTO (P3.2)   | I    | Interrupt 0 input or gate control input for counter 0.                                                                                                                                                                                                                                                                                      |