# SYSTEM CONTROLLER AND DATA MODEM

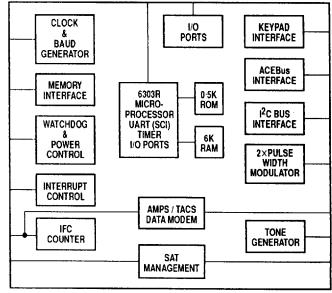

The ACE9050 provides the control and interface functions needed for AMPS or TACS analog cellular handsets. The device has been designed using GEC Plessey Semiconductors sub-micron CMOS technology for low power and high performance.

The ACE9050 contains an embedded microcontroller and peripheral functions. The controller is of the 6303 type with a Serial Communication Interface, Timer, ROM and RAM. The peripheral functions are: Data Modem, SAT Management, Serial Chip Interfaces, I<sup>2</sup>C Interface, two Pulse Width Modulators, IFC Counter, Tone generator, I/O ports, Watchdog and Crystal Oscillator.

Several power down modes are incorporated in the device as is a processor emulation mode for software and system development.

An index to this data sheet is given on pages 49 and 50.

#### **FEATURES**

- Low Power, Low Voltage (3.6 to 5.0 V) Operation

- 3.0V Memory Interface

- Power Down and Emulation Modes

- 6303R-type Microcontroller

- MAMPS or TACS Modem

- Watchdog and Power Control Logic

- SAT Detection, Generation and Loopback

- 6K bytes RAM

- Interface to FLASH and EEPROM Memories

- 512 byte ROM Boot Block

- I/O Ports for Keyboard Scanning

- I<sup>2</sup>C Controller

- Small Outline 100-pin package

#### **APPLICATIONS**

- AMPS and ETACS Cellular Telephones

- Two-way Radio Systems

## RELATED PRODUCTS

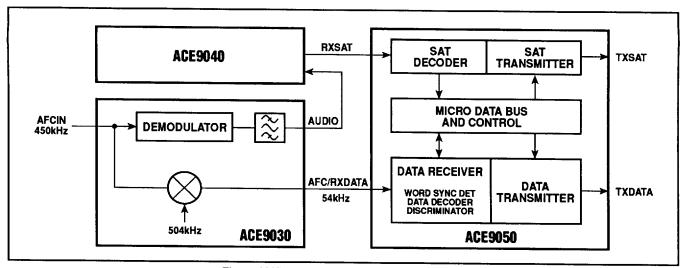

The ACE9050 is part of GEC Plessey Semiconductors' ACE chipset, together with the following:

ACE9010 RF Front End with VCO

ACE9020 Receiver and Transmitter interface

ACE9030 Radio Interface and Twin Synthesiser

ACE9040 Audio Processor

#### **ORDERING INFORMATION**

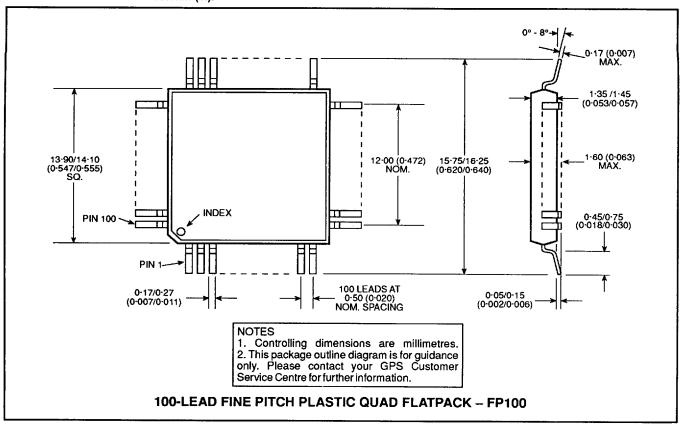

Industrial temperature range.

TQFP 100-lead 14×14mm, 0.5mm pitch package (FP100)

ACE9050 / IG / FP1N: trays and dry packed

ACE9050 / IG / FP1Q: tape mounted and dry packed

## **ABSOLUTE MAXIMUM RATINGS**

Supply voltages  $V_{\text{DD}}$ ,  $V_{\text{DDM}}$ Storage temperature Operating temperature Voltage on any pin

-0.5V to +6V -55°C to +150°C -40°C to +85°C V<sub>SS</sub>-0.5V to V<sub>DD</sub>+0.5V

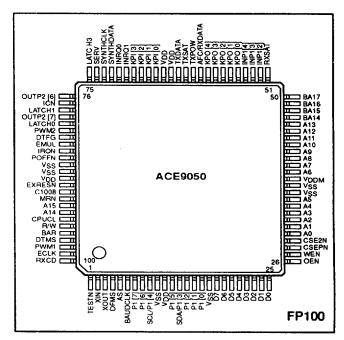

Fig.1 Pin connections - top view. Pin 1 is identified by moulded spot and by coding orientation. See Table 1 for detailed pin descriptions.

Fig.2 ACE9050 simplified block diagram

■ 3768522 0028909 538 ■

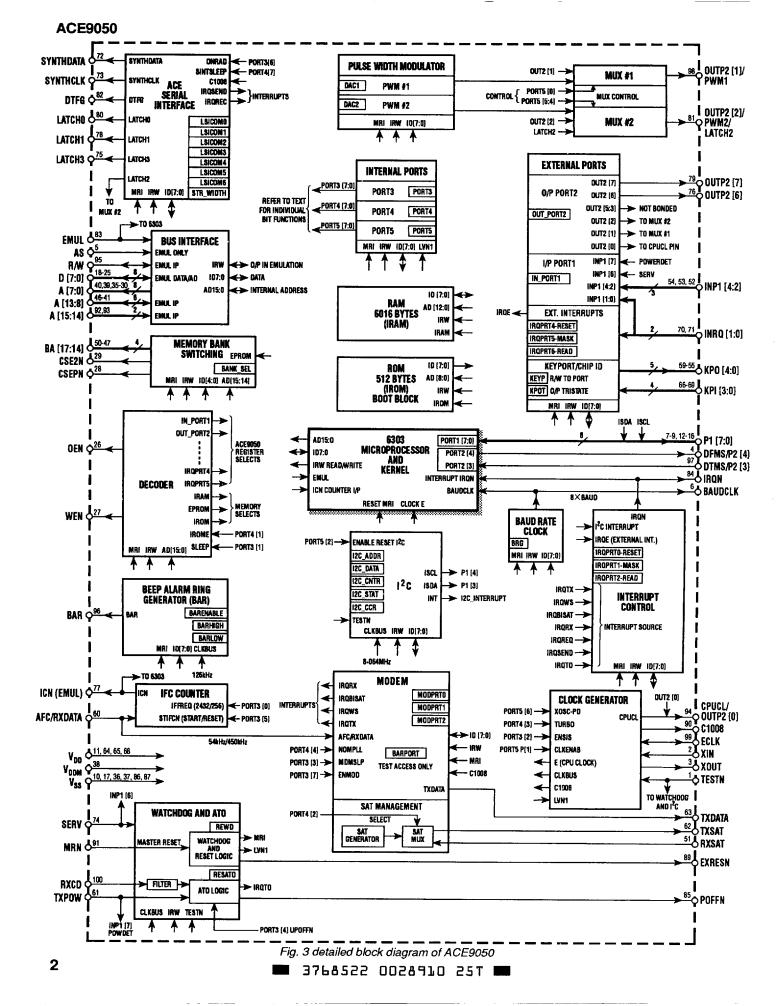

# **FUNCTIONAL OVERVIEW**

## MICROPROCESSOR UNIT

The processor unit is program compatible with the standard 6303R. It contains the following hardware:

8-bit CPU

Serial Communication Interface: SCI (UART)

16-bit timer/counter

8-bit I/O port (P1)

2-bit I/O port (P2)

The processor bus speed can be either 1.008 MHz or 2.016 MHz. An Emulation mode is provided whereby the internal 6303 is bypassed to allow software development on a standard 6303 In-Circuit Emulator (ICE).

#### **MEMORY**

The ACE9050 contains 512 bytes of ROM and 6144 bytes of RAM internally.

The ROM code facilitates system initiation after a reset and the programming of FLASH memory via the 6303 SCI (UART). The Internal RAM area represents the total RAM requirement anticipated for a cellular phone.

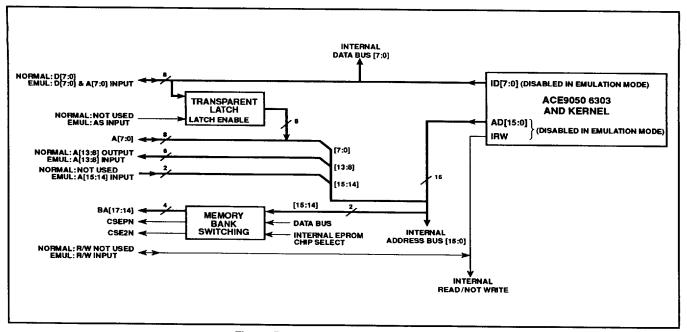

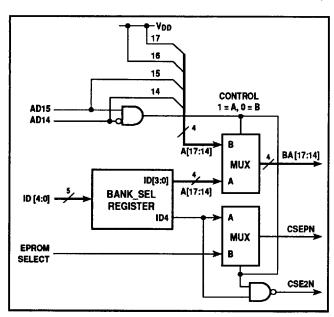

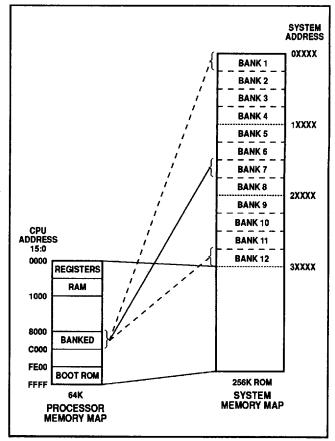

# **BUS INTERFACE and MEMORY BANK SWITCHING**

These blocks create the Data, Address and Control lines for the external memory. The external address bus is expanded from the standard 16 bits up to 18 bits by a banked addressing scheme. This increases the memory address space from 64K to 256K. Two programmable Chip Selects (CSEPN and CSE2N) are generated.

The Memory Interface will operate down to +3V, allowing the use of low voltage memory parts.

In Emulation mode the external processor controls the ACE9050 via the Bus Interface block.

#### **EXTERNAL PORTS**

The ACE9050 contains two Keypad Interface ports, two maskable external interrupts, and both Input and Output ports. These are in addition to the 6303 bidirectional Port1 and Port2. The Output port provides two high current outputs for driving LEDs.

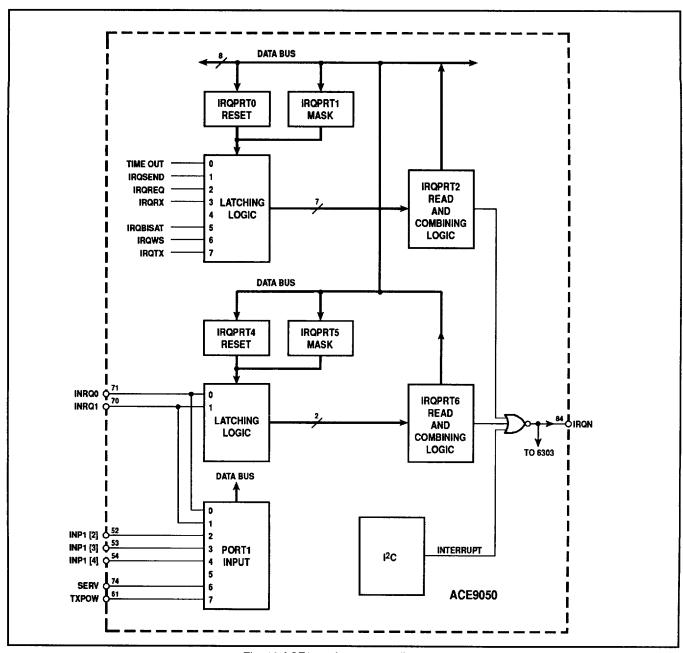

## **DECODER and INTERRUPT CONTROL**

The Decoder block memory maps ACE9050 register locations onto the processor's address space.

The Interrupt Control block handles both internal and external interrupt sources. These are fed into control logic allowing individual masking and reset by software. The Interrupt control logic output is internally connected to the 6303 IRQ and also drives an external pin.

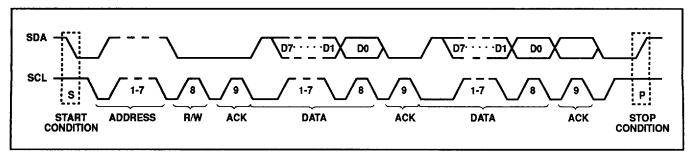

# ACE SERIAL INTERFACE (SINT) and I2C

Three serial interface protocols are supported: UART, I<sup>2</sup>C and ACEBus. The 6303 provides a UART interface via the SCI block.

The ACE9050 I<sup>2</sup>C block provides an I<sup>2</sup>C interface with both Master and Slave capability.

The ACEBus is designed for use with the ACE Chipset and has a data rate of just over 1MBits/sec. Three Latch pulse are available to target data at the relevant IC and control the ACE9030 Synthesiser.

#### BEEP, ALARM and RING TONE GENERATOR (BAR)

The BAR Generator is intended to drive an acoustic tone transducer. It has a programmable single digital pulse train output.

#### **MODEM and SAT MANAGEMENT**

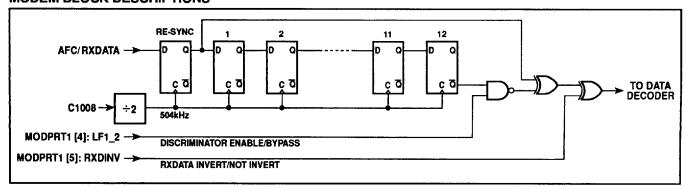

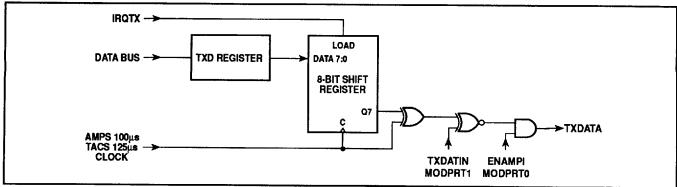

The Modem provides two way data transfer and SAT management over the radio link between a base station and phone handset. AMPS and TACS data rates are supported.

The Modem block contains: Digital Discriminator, Data Decoder and Word Synchronising hardware. Various modes can be selected by software. A squeich level is also set by software so that the quality of each data byte can be assessed.

SAT detection and generation at the standard three frequencies 5970Hz, 6000Hz and 6030Hz is included.

#### **WATCHDOG and POWER CONTROL (ATO)**

The Watchdog function will provide an internal and external Reset if the processor does not make a write access to a defined address every 4 seconds.

An Autonomous Time Out circuit (ATO) will drive the POFFN output low if Transmitter power is detected without Receiver power, independent of any processor operation. POFFN must be used in conjunction with external regulators to control power to the mobile handset.

# IF CONTROL COUNTER (IFC)

The Intermediate Frequency Control (IFC) Counter is used as part of an AFC Loop. The IFC Counter provides a pulse after a set number of IF input pulses. The IFC Counter output is connected to the 6303 timer input and an external pin (ICN).

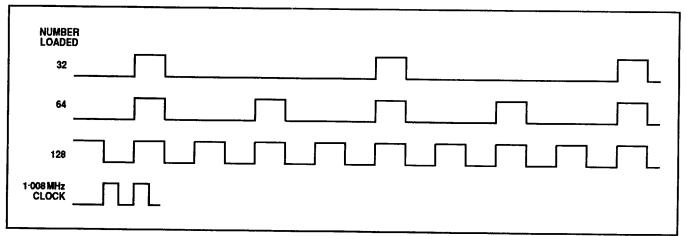

#### TWIN PULSE WIDTH MODULATORS

Two independently programmable Pulse Width Modulators (PWMs) are available. These provide digital output pulse trains, controllable by software. The output can be filtered externally to provide a DAC function. Typical applications are battery charging control and LCD contrast control.

#### **CLOCK GENERATOR**

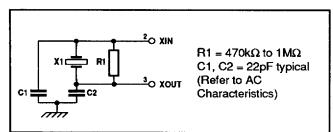

The Clock Generator provides all the various internal and external clocks from a single 8.064 MHz source. The source can either be an external crystal or the ACE9030.

# **PIN DESCRIPTIONS**

| Pin      | Name                     | Туре  | Block                  | Description                                                                                                         | Internal     |

|----------|--------------------------|-------|------------------------|---------------------------------------------------------------------------------------------------------------------|--------------|

| 1        | TESTN                    | ı     | CLKWDATO               | Connect to V <sub>DD</sub>                                                                                          | PU           |

| 2        | XIN                      |       | CLK                    | Crystal connection CMOS input: 8-064 MHz                                                                            | None         |

| 3 4      | XOUT<br>DFMS/P2 [4]      | 0/0   | CLK<br>CPU             | Crystal connection                                                                                                  |              |

| 5        | I AS                     | ] "   | BINT                   | CPU Port2 bit 4 or Serial interface (SCI) output Address strobe (Latch Address during Emulation)                    | None<br>PU   |

| 6        | BAUDCLK                  | 0 (1) | BAUD                   | Baud Rate Gen. output for Emulation (Input in test mode)                                                            | PU           |

| 7        | P1[7]                    | 1/0   | CPU                    | PORT 1 of CPU                                                                                                       | None         |

| 8        | P1[6]                    | 1/0   | CPU                    | PORT 1 of CPU                                                                                                       | None         |

| 9        | P1[4]/SCL                | 1/0   | CPU / I <sup>2</sup> C | PORT 1 of CPU/I <sup>2</sup> C SCL                                                                                  | None         |

| 10       | V <sub>SS</sub>          |       |                        | Ground                                                                                                              | -            |

| 12       | V <sub>DD</sub><br>P1[5] | 110   | CPU                    | Digital Supply PORT 1 of CPU                                                                                        | Na.          |

| 13       | P1[3]/ SDA               | 1/0   | CPU / I <sup>2</sup> C | PORT 1 of CPU/I <sup>2</sup> C SDA                                                                                  | None<br>None |

| 14       | P1[2]                    | 1/0   | CPU                    | PORT 1 of CPU                                                                                                       | None         |

| 15       | P1[1]                    | 1/0   | CPU                    | PORT 1 of CPU                                                                                                       | None         |

| 16       | P1[0]                    | 1/0   | CPU                    | PORT 1 of CPU                                                                                                       | None         |

| 17       | V <sub>SS</sub>          | ١     |                        | Ground                                                                                                              | -            |

| 18<br>19 | D7<br>D6                 | 1/0   | BINT                   | Data bus (and Emulation Address A7 Input)                                                                           | None         |

| 20       | D5                       | 1/0   | BINT<br>BINT           | Data bus (and Emulation Address A6 Input) Data bus (and Emulation Address A5 Input)                                 | None         |

| 21       | D4                       | 1/0   | BINT                   | Data bus (and Emulation Address A4 Input)                                                                           | None<br>None |

| 22       | D3                       | 1/0   | BINT                   | Data bus (and Emulation Address A3 Input)                                                                           | None         |

| 23       | D2                       | 1/0   | BINT                   | Data bus (and Emulation Address A2 Input)                                                                           | None         |

| 24       | D1                       | 1/0   | BINT                   | Data bus (and Emulation Address A1 Input)                                                                           | None         |

| 25       | D0                       | 1/0   | BINT                   | Data bus (and Emulation Address A0 Input)                                                                           | None         |

| 26<br>27 | OEN<br>WEN               | 0     | DEC<br>DEC             | Output Enable Write Enable                                                                                          | •            |

| 28       | CSEPN                    | l ŏ   | MEMB                   | C/S External EPROM                                                                                                  | -            |

| 29       | CSE2N                    | Ιŏ    | MEMB                   | C/S External EEPROM                                                                                                 |              |

| 30       | A0                       | Ō     | BINT                   | Address bus                                                                                                         | _            |

| 31       | A1                       | 0     | BINT                   | Address bus                                                                                                         | -            |

| 32       | A2                       | 0     | BINT                   | Address bus                                                                                                         | - 1          |

| 33<br>34 | A3<br>A4                 | 0     | BINT<br>BINT           | Address bus Address bus                                                                                             | l - i        |

| 35       | A5                       | l ŏ   | BINT                   | Address bus                                                                                                         | ·            |

| 36       | V <sub>ss</sub>          | `     | 5                      | Ground                                                                                                              |              |

| 37       | V <sub>SS</sub>          | İ     |                        | Ground                                                                                                              | _            |

| 38       | V <sub>DDM</sub>         |       |                        | Digital Supply for Memory Interface (pins18-35, 38-50)                                                              | -            |

| 39       | A6                       |       | BINT                   | Address bus                                                                                                         | -            |

| 40<br>41 | A7<br>A8                 | 0 (1) | BINT<br>BINT           | Address bus<br>Address bus (Input during Emulation)                                                                 |              |

| 42       | A9                       | 000   | BINT                   | Address bus (Input during Emulation) Address bus (Input during Emulation)                                           | None<br>None |

| 43       | A10                      | O (i) | BINT                   | Address bus (Input during Emulation)                                                                                | None         |

| 44       | A11                      | 0 (1) | BINT                   | Address bus (Input during Emulation)                                                                                | None         |

| 45       | A12                      | 0 (1) | BINT                   | Address bus (Input during Emulation)                                                                                | None         |

| 46       | A13                      | 0 (1) |                        | Address bus (Input during Emulation)                                                                                | None         |

| 47<br>48 | BA14<br>BA15             |       | MEMB                   | Address bus (Extended Address: From Bank Select Register)                                                           | -            |

| 49       | BA16                     | 0     | MEMB<br>MEMB           | Address bus (Extended Address: From Bank Select Register) Address bus (Extended Address: From Bank Select Register) | -            |

| 50       | BA17                     | ŏ     | MEMB                   | Address bus (Extended Address: From Bank Select Register) Address bus (Extended Address: From Bank Select Register) |              |

| 51       | RXSAT                    | Ī     | MODEM                  | Received SAT input                                                                                                  | None         |

| 52       | INP1 [2]                 | 1     | EPORT                  | Bit 2 Input Port1                                                                                                   | None         |

| 53       | INP1 [3]                 | !     | EPORT                  | Bit 3 Input Port1                                                                                                   | None         |

| 54<br>55 | INP1 [4]<br>KPO [0]      |       | EPORT                  | Bit 4 Input Port1                                                                                                   | None         |

| 56       | KPO [0]<br>  KPO [1]     | 00    | EPORT<br>EPORT         | Keypad scan output/output port<br>Keypad scan output/output port                                                    | -            |

| 57       | KPO [2]                  | 0     | EPORT                  | Keypad scan output/output port Keypad scan output/output pon                                                        |              |

| 58       | KPO [3]                  | ŏ     | EPORT                  | Keypad scan output/output port                                                                                      | _            |

| 59       | KPO [4]                  | 0     | EPORT                  | Keypad scan output/output port                                                                                      | _            |

| 60       | AFC/RXDATA               | !     | IFC/MODEM              | 54/450kHz IF input fromACE9030                                                                                      | None         |

| 61<br>62 | TXPOW                    |       | WDATO                  | Power detect from transmitter                                                                                       | None         |

| 62<br>63 | TXSAT<br>TXDATA          | 0 0   | MODEM<br>MODEM         | SAT Output TACS / AMPS Modern Output                                                                                | - 1          |

| 64       | V <sub>DD</sub>          |       | MODEIM                 | TACS / AMPS Modem Output Digital Supply                                                                             |              |

| 65       | V <sub>DD</sub>          |       |                        | Digital Supply                                                                                                      |              |

|          |                          |       |                        | ÷ 117                                                                                                               |              |

Table 1

Cont...

4

**■** 3768522 0028912 022 **■**

| Pin | Name            | Туре  | Block     | Description                                               | Internal |

|-----|-----------------|-------|-----------|-----------------------------------------------------------|----------|

| 66  | KPI [3]         | 1     | EPORT     | Keypad scan input/input port                              | PD       |

| 67  | KPI [2]         | - 1   | EPORT     | Keypad scan input/input port                              | PD       |

| 68  | KPI [1]         | 1     | EPORT     | Keypad scan input/input port                              | PD       |

| 69  | KPI [o]         | 1     | EPORT     | Keypad scan input/input port                              | PD       |

| 70  | INRQ1           | t     | EPORT     | External Interrupt (also Bit1 Input Port1)                | PD       |

| 71  | INRQ0           | 1     | EPORT     | External Interrupt (also Bit0 Input Port1)                | PD       |

| 72  | SYNTHDATA       | 0     | SINT      | SynthBus Data Line                                        |          |

| 73  | SYNTHCLK        | 0     | SINT      | SynthBus 126kHz Clock                                     |          |

| 74  | SERV            |       | WDATO     | 1 = Service Mode                                          | None     |

| 75  | LATCH3          | 0     | SINT      | Latch, programmable length. (To ACE9030, LATCHC pin)      | 110176   |

| 76  | OUTP2 [6]       | 0     | EPORT     | Output Port2 Bit 6: High Current Driver                   | 1 1      |

| 77  | ICN             | 0 (1) | IFC       | IF Counter Output for Emulation (input in Test mode)      | PU       |

| 78  | LATCH1          | O     | SINT      | Latch O/P (To ACE9030 receiver Interface, LATCHB pin)     | '        |

| 79  | OUTP2[7]        | 0     | EPORT     | Output Port2 Bit 7: High Current Driver                   |          |

| 80  | LATCH0          | 0     | SINT      | Latch O/P (To ACE9040, LEN)                               | 1        |

| 81  | OUTP2[2]/PWM2/  | 0     | PWM       | Output Port2 Bit 2/Pulse Width Modulator #2 Output/       |          |

|     | LATCH2          |       |           | SynthBus Latch O/P.                                       | 1        |

| 82  | DTFG            | 1/0   | SINT      | Bidirectional serial inter-chip data, to/from the ACE9030 | None     |

| 83  | EMUL            | 1     | BINT/CPU  | 1 = CPU Emulation Mode                                    | PD       |

| 84  | IRQN            | 0 (1) | CPU       | CPU Interrupt for Emulation (input in Test mode)          | '.       |

| 85  | POFFN           | 0     | WDATO     | Power On/Off                                              |          |

| 86  | V <sub>SS</sub> | 1     |           | Ground                                                    | 1 .      |

| 87  | V <sub>ss</sub> |       |           | Ground                                                    | 1 - 1    |

| 88  | V <sub>DD</sub> |       |           | Digital Supply                                            |          |

| 89  | EXRESN          | 0     | WDATO     | External reset output                                     | 1 .      |

| 90  | C1008           | 0     | CLK       | 1.008MHz Clock for ACEBus, ACE9030 and ACE9040            |          |

| 91  | MRN             | 1     | WDATO     | 0 = Chip reset                                            | None     |

| 92  | A15             |       | BINT      | Address input for Emulation only                          | PU       |

| 93  | A14             | 1     | BINT      | Address input for Emulation only                          | PÜ       |

| 94  | CPUCL/OUTP2[0]  | 0     | CLK/EPORT | 8.064MHz clock/Out Port 2 bit 0                           | '-       |

| 95  | R/W             | 0 (1) | BINT      | Read/Write (Input during Emulation)                       | None     |

| 96  | BAR             | 0     | BAR       | Beep, Alarm, Ring Tone Output                             | 1.57.5   |

| 97  | DTMS            | 1/0   | CPU       | CPU Port 2 bit 3 or Serial interface (SCI) input          | None     |

| 98  | OUTP2 [1]/PWM 1 | 0     | PWM       | Output Port 2 Bit 1/Pulse Width Modulator #1 Output       |          |

| 99  | ECLK            | 0 (1) | CLK       | Processor Clock (Input during Emulation)                  | None     |

| 100 | RXCD            | [ 1   | WDATO     | Carrier detect from RX                                    | None     |

## Table 1 (continued)

# **ABBREVIATIONS**

| BAR<br>BAUD<br>BINT<br>MEMB<br>CLK<br>CPU<br>DEC<br>EPORT | Beep, Alarm and Ring tone generator Baud Rate generator Bus Interface Memory Bank switching Clock generator 6303 microprocessor unit Decoder External Port | IPC<br>IFC<br>MODEM<br>PWM<br>SINT<br>WDATO<br>PU<br>PD | I <sup>2</sup> C interface IF Control counter AMPS/TACS Modem Pulse Width Modulator and MUX Serial Inter-chip interface Watchdog/Autonomous Time Out Internal Pullup resistor present |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIONI                                                     | External Fort                                                                                                                                              | PD                                                      | Internal Pulldown resistor present                                                                                                                                                    |

# **UNUSED INPUTS**

Input or bidirectional pins must have a suitable pullup or pulldown reststor if they are configured as inputs, with no external drive. Some inputs have an internal pullup or pulldown resistor of the order of  $100k\Omega$ ; this value is suitable if the pin is not subject to excessive noise or residual current greater than  $15\mu$ A. If the pins shown in Table 2 are not used in the system, an external resistor will be required.

| Pin | Name   | Pin | Name          | Pin | Name                  |

|-----|--------|-----|---------------|-----|-----------------------|

| 4   | DFMS   | 15  | P1 [1]        | 61  | TXPOW                 |

| 7   | P1 [7] | 16  | P1 [0]        | 74  | SERV                  |

| 8   | P1 [6] | 51  | RXSAT         | 82  | DTFG (Requires        |

| ø   | P1 [5] | 52  | INP1 [2]      | 1   | programming resistor) |

| 12  | P1 [4] | 53  | INP1 [3]      | 91  | MRN                   |

| 13  | P1 [3] | 54  | INP1 [4]      | 97  | DTMS                  |

| 14  | P1 [2] | 60  | AFC_IN/RXDATA | 100 | RXCD                  |

NOTE: P1 [7:0], DFMS and DTMS are configured as inputs upon reset.

Table 2

# **ELECTRICAL CHARACTERISTICS**

The Electrical Characteristics are guaranteed over the following range of operating conditions (unless otherwise stated):  $T_{AMB} = -40$ °C to +85°C,  $V_{DD} = 3.6$ V to 5.5V,  $V_{DDM} = 3.0$ V to 5.5V (note 2)

# **DC CHARACTERISTICS**

|                                              |                   |                    | Value               |                    |       |                                                    |

|----------------------------------------------|-------------------|--------------------|---------------------|--------------------|-------|----------------------------------------------------|

| Characteristic                               | Symbol            | Min.               | Тур.                | Max.               | Units | Conditions                                         |

| Supply current (Normal clock)                | IDDNOR            |                    | 3⋅5                 |                    | mA    | 1.008MHz ECLK, V <sub>DD</sub> = 5V                |

| Supply current (Turbo clock)                 | IDDTUR            |                    | 6.0                 |                    | mA    | 2·016MHz ECLK, V <sub>DD</sub> = 5V                |

| Supply current (Static)                      | I <sub>DDSB</sub> |                    | 150                 |                    | μА    | No clock & osc. powered down                       |

| Input high voltage                           | V <sub>IH</sub>   | 0.7V <sub>DD</sub> |                     |                    | V     |                                                    |

| Input low voltage                            | V <sub>IL</sub>   | -0∙5               |                     | 0.2V <sub>DD</sub> | ٧     |                                                    |

| Output high voltage                          | V <sub>OH</sub>   | 0.8V <sub>DD</sub> | 0.92V <sub>DD</sub> |                    | ٧     | $I_{OH} = 2mA, V_{DD} > 3.6V$                      |

|                                              |                   |                    |                     |                    |       | $I_{OL} = 1 \text{mA}, V_{DD} \leq 3.6 \text{V}$   |

| Output low voltage                           | V <sub>OL</sub>   |                    | 0.2                 | 0.4                | ٧     | $I_{OH} = 2mA, V_{DD} > 3.6V$                      |

|                                              | <u> </u>          |                    |                     |                    |       | $I_{OL} = 1.5 \text{mA}, V_{DD} \leq 3.6 \text{V}$ |

| High current drive O/P source (pins 76 & 79) | Іонні             |                    |                     | 10                 | mA    | V <sub>DD</sub> > 3·6V                             |

|                                              | 1                 |                    |                     | 6                  |       | V <sub>DD</sub> = 3.6V                             |

| High current drive O/P sink (pins 76 & 79)   | I <sub>OLHI</sub> |                    |                     | 10                 | mA    | V <sub>DD</sub> > 3·6V                             |

|                                              |                   |                    |                     | 9                  |       | V <sub>DD</sub> = 3.6V                             |

| Tristate leakage current                     | loz               |                    |                     | 1                  | μА    | No Pullup/down cell                                |

| input leakage current                        | I <sub>IN</sub>   |                    |                     | 1                  | μА    | No Pullup/down cell                                |

| Pullup/down resistance                       | R <sub>IN</sub>   | 35                 |                     | 150                | kΩ    | $V_{DD} = 5.5V, T_{AMB} = 25^{\circ}C$             |

## **NOTES**

# **AC CHARACTERISTICS (CLOCKS and CRYSTAL)**

|                          |                     |      | Value     |     |       |                                       |  |

|--------------------------|---------------------|------|-----------|-----|-------|---------------------------------------|--|

| Characteristic           | Symbol              | Min. | Min. Typ. |     | Units | Conditions                            |  |

| Oscillator frequency     | fosc                |      | 8.064     |     | MHz   | External crystal                      |  |

| Oscillator external I/P  | f <sub>IP</sub>     |      | 8.064     |     | MHz   | CMOS/800mV sine I/P AC coupled        |  |

| AC coupling capacitor    | C <sub>COUPLE</sub> |      | 10        |     | nF    | Sine input                            |  |

| External resistor        | R1                  | 470  | 1000      |     | kΩ    | Crystal oscillator                    |  |

| External capacitors      | C1, C2              |      | 22        |     | ρF    | Crystal oscillator (note 1)           |  |

| Crystal ESR              | XTAL <sub>ESR</sub> |      |           | 120 | Ω     | Crystal oscillator                    |  |

| Startup time             | t <sub>SU</sub>     |      |           | 5   | ms    | Crystal oscillator                    |  |

| Radio serial control bus | C1008               |      | 1.008     |     | MHz   | · · · · · · · · · · · · · · · · · · · |  |

| Microprocessor clock     | ECLK1               |      | 1.008     |     | MHz   | Normal clock                          |  |

| Microprocessor clock     | ECLK2               |      | 2.016     | Î   | MHz   | Turbo clock                           |  |

| Clock output             | CPUCL               |      | 8.064     |     | MHz   | Output enabled                        |  |

| Watchdog time out        | WD <sub>TO</sub>    |      | 4         |     | s     | Normal Mode                           |  |

| Autonomous time out      | ATO <sub>TO</sub>   |      | 30        |     | S     | Normal Mode                           |  |

## NOTES

■ 3768522 0028914 9T5 ■

<sup>1.</sup> The DC Characteristics Min. and Max figures are guaranteed by test.

<sup>2.</sup> The voltage on  $V_{DDM}$  must be less than or equal to  $V_{DD}$ .

<sup>1.</sup> Refer to crystal manufacturer for exact deatils.

# **TIMING DIAGRAMS**

# NORMAL MODE PROCESSOR INTERFACE

# **Read Cycle**

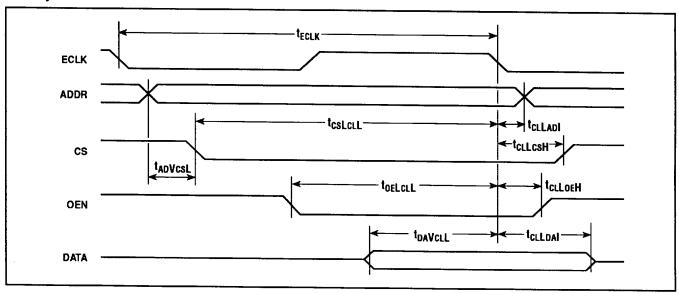

Fig.4 ACE9050 6303 Read cycle timing diagram

# **Timing Cycle Conditions**

Input clock frequency, XIN = 8.064MHz. Worst case Timings:  $T_{AMB} = -40$ °C to +85°C,  $V_{DD} = +3.6$ V to +5.5V Typical timings:  $T_{AMB} = +25$ °C,  $V_{DD} = +3.75$ V

| Description             | Sumb at | Normal clock |      |      | Turbo clock |            |      |       |

|-------------------------|---------|--------------|------|------|-------------|------------|------|-------|

| bescription             | Symbol  | Min.         | Тур. | Max. | Min.        | Тур.       | Max. | Units |

| Cycle time              | teck    |              | 992  |      |             | 496        |      | ns    |

| Address valid to CS low | tADVCSL | 2            | 4    | 9    | 2           | 4          | 9    | ns    |

| Chip Select set-up time | tcsLcLL | 940          | 972  | 985  | 445         | 480        | 490  | ns    |

| OEN set-up time         | toelcll | 485          | 492  | 495  | 240         | 245        | 248  | ns    |

| Data set-up time        | tDAVCLL | 35           | 1    |      | 35          | - '        |      | ns    |

| Data hold time          | tCLLDAI | 1 0          | l    |      | 0           |            |      | ns    |

| OEN hold time           | tclLoeH | 1 0          | 1    | 4    | o           | <b>l</b> ₁ | 4    | ns    |

| CS hold time            | tclLcsH | 9            | 24   | 45   | 9           | 24         | 45   | ns    |

| Address hold time       | tCLLADI | 7            | 18   | 42   | 7           | 18         | 42   | ns    |

Table 3 ACE9050 6303 Read cycle timing

# Write Cycle (Normal Mode)

Fig. 5 ACE9050 6303 Write cycle timing diagram

# **Timing Cycle Conditions**

Input clock frequency, XIN = 8.064MHz. Worst case timings:  $T_{AMB} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{DD} = +3.6V$  to +5.5V Typical timings:  $T_{AMB} = +25^{\circ}C$ ,  $V_{DD} = +3.75V$

|                               |                      | N    | ormal cloc | k    | ٦    | Turbo cloc | k    | Unite |

|-------------------------------|----------------------|------|------------|------|------|------------|------|-------|

| Description                   | Symbol               | Min. | Тур.       | Max. | Min. | Тур.       | Max. | Units |

| Cycle time                    | t <sub>ECLK</sub>    |      | 992        |      |      | 496        |      | ns    |

| Address valid to end of Write | t <sub>ADVWEH</sub>  | 835  | 853        | 862  | 395  | 420        | 427  | ns    |

| Address hold time             | tweHADI              | 125  | 140        | 151  | 63   | 72         | 93   | ns    |

| Chip enable set-up time       | t <sub>CSLWEH</sub>  | 825  | 840        | 860  | 390  | 415        | 425  | ns    |

| WE pulse width                | tweLweH              | 363  | 364        | 371  | 173  | 181        | 184  | ns    |

| Data valid set-up time        | tDAVWEH              | 365  | 368        | 371  | 177  | 183        | 192  | ns    |

| Data hold time                | tweHDAI              | 120  |            |      | 60   |            |      | ns    |

| Address valid to data low Z   | t <sub>ADVDALZ</sub> | 451  | 473        | 487  | 203  | 225        | 239  | ns    |

| Address valid to chip select  | tADVCSL              | 0    | 5          | 10   | 0    | 4          | 9    | ns    |

| WE high to CS high            | tweHcsH              | 127  | 140        | 163  | 66   | 72         | 105  | ns    |

Table 4 ACE9050 6303 Write cycle timing

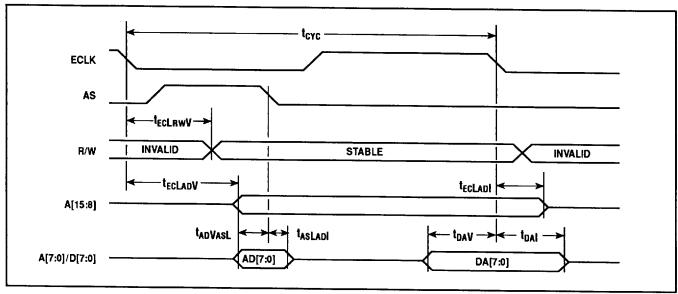

# **EMULATION MODE PROCESSOR INTERFACE**Read and Write Cycles

Fig.6 ACE9050 6303 Emulation mode Read/Write cycles timing diagram

# **Emulation Mode Timing Cycle Conditions**

Input clock ECLK frequency = 1.008MHz (Normal clock), 2.016MHz (Turbo clock),  $T_{AMB}$  = +25°C,  $V_{DD}$  = +5V ±10%

| Description                  | Symbol              | Normal clock |      |      | 7    | urbo cloc | k        |       |

|------------------------------|---------------------|--------------|------|------|------|-----------|----------|-------|

| Description                  | Symbol              | Min.         | Тур. | Max. | Min. | Тур.      | Max.     | Units |

| Cycle time                   | tcyc                |              | 992  |      |      | 496       |          | ns    |

| Read/Write settling time     | t <sub>ECLRWV</sub> |              |      | 250  |      |           | 160      | ns    |

| Address delay time           | teclady             | 1            |      | 250  |      |           | 160      | ns    |

| Address hold time            | tecladi             | 1 0          |      |      | 0    |           | 100      | ns    |

| Address to latch set-up time | tadvast             | 60           |      |      | 20   |           |          | ns    |

| Address to latch hold time   | tasLadi             | 30           |      |      | 20   |           |          |       |

| Data set-up time - WRITE     | t <sub>DAV-W</sub>  | 50           |      |      | 50   |           |          | ns    |

| Data hold time - WRITE       | t <sub>DAI-W</sub>  | 1 1          |      | 1    | 30   |           |          | ns    |

| Data set-up time - READ      |                     | 80           |      |      | 00   |           | <u> </u> | ns    |

| Data hold time - READ        | t <sub>DAV-R</sub>  | 80           |      |      | 80   |           | 1        | ns    |

| Data Hold time - READ        | l tDAl-R            | 1 1          | 1    |      | 1    |           | 1        | ns    |

Table 5 6303 Emulation Mode Read/Write cycles timing

# SERIAL INTERFACE BLOCK

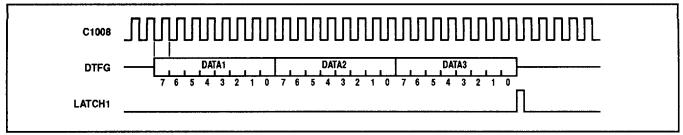

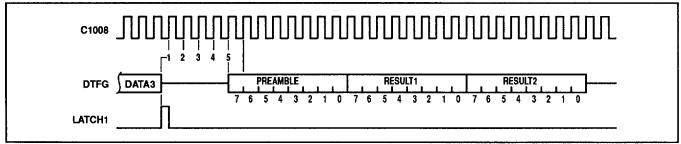

# **ACEBus Read and Write Timings**

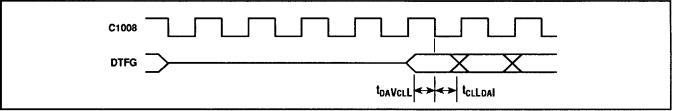

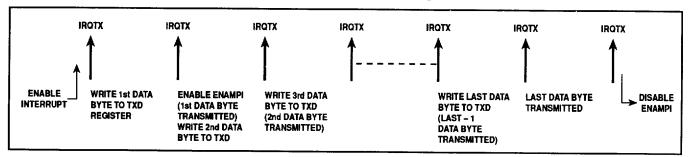

Fig.7 ACEBus Transmit Data flow

Fig.8 ACEBus Receive Data flow

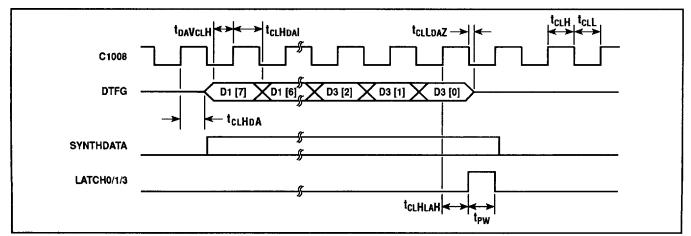

Fig.9 ACEBus Transmit timing diagram

Fig.10 ACEBus Receive timing diagram

# **ACEBus Timing Cycle Conditions**

Input clock frequency, XIN = 8.064MHz. Worst case Timings:  $T_{AMB} = -40^{\circ}\text{C}$  to + 85°C,  $V_{DD} = +3.6\text{V}$  to +5.5V Typical timings:  $T_{AMB} = +25^{\circ}\text{C}$ ,  $V_{DD} = +3.75\text{V}$

|                                        |                     |       | Value |       |       |                    |  |

|----------------------------------------|---------------------|-------|-------|-------|-------|--------------------|--|

| Characteristic                         | Symbol              | Min.  | Тур.  | Max.  | Units | Conditions         |  |

| TRANSMIT Clock high to Data bus driven | t <sub>CLHDA</sub>  | 491   |       |       | ns    |                    |  |

| Data set-up time                       | t <sub>DAVCLH</sub> | 488   |       |       | ns    |                    |  |

| Data hold time                         | tCLHDAI             | 491   |       |       | ns    |                    |  |

| Clock high to Latch high               | tCLHLAH             | 491   |       |       | ns    |                    |  |

| Latch width 0 and 1                    | t <sub>PW01</sub>   | 491   | 496   |       | ns    |                    |  |

| Latch width 3                          | t <sub>PW3</sub>    | 0.099 |       | 12.59 | ms    | Programmable width |  |

| Clock low                              | t <sub>CLL</sub>    |       | 496   |       | ns    | -                  |  |

| Clock high                             | tclH                |       | 496   |       | ns    |                    |  |

| Clock high to data line tristate       | tCLHDAZ             | 0     |       | 5     | ns    |                    |  |

| RECEIVE                                |                     |       |       |       |       |                    |  |

| Data set-up time                       | tDAVCLL             | 14    |       | 1     | ns    |                    |  |

| Data hold time                         | t <sub>CLLDAI</sub> | 14    |       |       | ns    |                    |  |

Table 6 ACEBus Read and Write timings

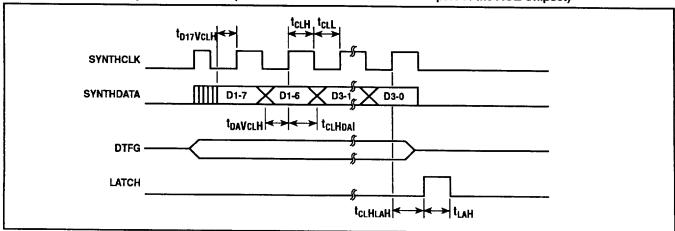

# SynthBus (Note: The SynthBus is not required when the ACE9050 is used as part of the ACE Chipset)

Fig.11 SynthBus timing diagram

# **SynthBus Timing Cycle Conditions**

Input clock frequency, XIN = 8.064MHz. Worst case Timings:  $T_{AMB} = -40$ °C to +85°C,  $V_{DD} = +3.6$ V to +5.5V Typical timings:  $T_{AMB} = +25$ °C,  $V_{DD} = +3.75$ V

|                                     |                       |      | Value |      |       |                                       |

|-------------------------------------|-----------------------|------|-------|------|-------|---------------------------------------|

| Characteristic                      | Symbol                | Min. | Тур.  | Max. | Units | Conditions                            |

| First data bit set-up time          | t <sub>D17</sub> VCLH | >0   |       | 7.84 | μs    | · · · · · · · · · · · · · · · · · · · |

| Data bit set-up time (except first) | t <sub>DAVCLH</sub>   | 1    | 3.9   |      | μs    |                                       |

| Data hold time                      | tCLHDAI               |      | 4.0   |      | μs    |                                       |

| Clock high to latch high            | tCLHLAH               |      | 4.97  |      | μs    |                                       |

| Latch width                         | tLAH                  |      | 952   |      | ns    |                                       |

| Clock low                           | t <sub>CLL</sub>      |      | 3.99  |      | μs    |                                       |

| Clock high                          | tolH                  |      | 3.93  | ]    | μs    |                                       |

Table 7 SynthBus timing

# INTERNAL REGISTERS AND RESET STATUS

# **ACE9050 REGISTERS**

| Name      | R/W   | Address | Description            | D7-0 reset condition | Notes |

|-----------|-------|---------|------------------------|----------------------|-------|

| IN PORT1  | R     | 22-23   | External IP Port       | EE0EEE00             | 1, 6  |

| OUT_PORT2 | R/W   | 24-25   | External OP Port       | 00000000             |       |

| PORT3     | R/W   | 26-27   | Internal Port          | 00000000             | 2     |

| BARPORT   |       | 28-29   | Test-Do Not Access     |                      |       |

| IRQPRT2   | R     | 2C-2D   | Read Int Interrupts    | 111X111              | 3, 7  |

| IRQPRT6   | R     | 2E-2F   | Read Ext Interrupts    | XXXX1111             |       |

| MODPRT0   | RW    | 30-31   | Modem                  | 00000000             |       |

| MODPRT1   | RW    | 32-33   | Modem                  | 00000000             |       |

| MODPRT2   | RW    | 34-35   | Modem                  | 00000000             |       |

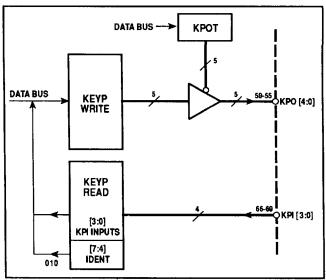

| KEYP      | RW    | 36-37   | Key Pad IP and Chip ID | 0010EEEE             | 6     |

| LSICOM4   | R     | 3A-3B   | ACE Interface RX1      | EEEEEEE              | 4, 6  |

| LSICOM5   | R     | 3C-3D   | ACE Interface RX2      | EEEEEEE              | 4, 6  |

| LSICOM6   | R     | 3E-3F   | ACE Interface RX3      | EEEEEEEE             | 4, 6  |

| PORT4     | RW    | 40-41   | Internal Port          | 0000010              |       |

| PORT5     | RW    | 42-43   | Internal Port          | 00000011             |       |

| BANK SEL  | l w l | 44      | Bank Select            | xxx00000             | 7     |

| RESERVED  |       | 45      | Do Not Access          |                      |       |

| BARHIGH   | w     | 50      | BAR On                 | 00000000             | ŀ     |

| BARLOW    | w     | 51      | BAR Off                | 00000000             |       |

| BARENABLE | w     | 52      | BAR OE                 | XXXXXX0              | 7     |

| BRG       | w     | 53      | UART Baud select       | xxxxxooo             | 5, 7  |

| 12C_ADDR  | R/W   | 54      | I <sup>2</sup> C       | 00000000             |       |

| I2C DATA  | R/W   | 55      | I <sup>2</sup> C       | 00000000             |       |

| I2C_CNTR  | R/W   | 56      | I <sup>2</sup> C       | 00000000             |       |

| 12C STAT  | R     | 57      | I <sup>2</sup> C       | 11111000             |       |

| I2C CCR   | w     | 57      | I <sup>2</sup> C       | 0000000              |       |

| DAC1      | w     | 5B      | PWM 1 data             | 00000000             |       |

| DAC2      | w     | 5C      | PWM 2 Data             | 00000000             |       |

| LSICOM0   | w     | 60-61   | ACE Interface TX1      | 00000000             | ŀ     |

| LSICOM1   | w     | 62-63   | ACE Interface TX2      | 00000000             |       |

| LSICOM2   | w     | 64-65   | ACE Interface TX3      | 0000000              |       |

| LSICOM3   | w     | 66      | ACE Interface Control  | 00000000             |       |

| STR WIDTH | w     | 67      | Latch 3 Width          | 00000000             |       |

| KPOT      | w     | 68-69   | O/P type for KPO       | XXX11111             | 7     |

| REWD      | w     | 6A-6B   | Reset Watchdog         | XXXXXXXX             | 7     |

| RESAT0    | w     | 6C-6D   | Reset Time Out         | XXXXXXXX             | 7     |

| IRQPRT0   | w     | 70-71   | Reset Int Interrupts   | 00000000 (Reset)     |       |

| IRQPRT1   | w     | 72-73   | Mask Int Interrupts    | 00000000 (Masked)    |       |

| IRQPRT4   | w     | 74-75   | Reset Ext Interrupts   | XXXX0000             | 7     |

| IRQPRT5   | W     | 76-77   | Mask Ext Interrupts    | XXXX0000             | 7     |

Table 8 ACE9050 ports

# NOTES:

- 1. Bit 6 is set (1) in SERV mode. Bits 1 and 0 are set (1) if the corresponding interrupt is enabled (inverse of IRQPRT6).

- 2. Bit 4 (UPOFFN) is set (1) in SERV mode, but reset (0) in Normal mode.

- 3. Bit 4 is not used and should be treated as undetermined.

- 4. The LSICOM4, 5 and 6 ports values will depend on the DTFG input.

- 5. In SERV mode the Boot block will set up BRG to 00000100 (9600 Baud).

- 6. E = Depends on external input.

- 7. X = Not used or undetermined.

#### ACE9050 6303 REGISTERS

| Name     | R/W | Address | Description              | D7-0 reset condition | Notes |

|----------|-----|---------|--------------------------|----------------------|-------|

| DDR1     | w   | 00      | Data Dir Register P1     | 00000000             | 1     |

| DDR2     | W   | 01      | Data Dir Register P2     | 00000000             | 1     |

| PORT1    | R/W | 02      | Data Port 1              | EEEEEEE              | 2     |

| PORT2    | R/W | 03      | Data Port 2              | 010XXXXX             | 3, 4  |

| TCSR     | R/W | 08      | Timer Control/Status     | 00000000             |       |

| FRC_HIGH | R/W | 09      | Free Run Counter MSB     | 00000000             |       |

| FRC_LOW  | R/W | 0A      | Free Run Counter LSB     | 00000000             |       |

| OCR_HIGH | R/W | OΒ      | O/P Compare Reg MSB      | 11111111             |       |

| OCR_LOW  | R/W | 0C      | O/P Compare Reg LSB      | 11111111             |       |

| ICR_HIGH | R   | 0D      | I/P Capture Reg MSB      | 00000000             |       |

| ICR_LOW  | R   | 0E      | I/P Capture Reg LSB      | 00000000             |       |

| RMCR     | w   | 10      | Rate & Mode Control      | XXXX0000             | 4,5   |

| TRCSR    | R/W | 11      | Tx/Rx Control and Status | 00100000             | 6     |

| RDR      | R   | 12      | Rx Data                  | 0000000              |       |

| TDR      | W   | 13      | Tx Data                  | 00000000             |       |

| RAMCR    | R   | 14      | Not Used                 | 00000000             | 7     |

Table 9 6303 ports

#### NOTES:

- 1. Both ports set to input (0 = I/P, 1 = O/P)

- 2. E = external input

- 3. 6303 internally set to Multiplexed mode

- 4. X = Unused or undetermined

- 5. Set to 00001100 in SERV mode

- 6. Set to 00111010 in SERV mode

- 7. This register Read only in the ACE9050

# **MODES OF OPERATION**

The ACE9050 has three independent modes of operation: Normal, Emulation, Service.

| Mode                 | Pin          | Enabled<br>High<br>High |  |

|----------------------|--------------|-------------------------|--|

| Emulation<br>Service | EMUL<br>SERV |                         |  |

| Normal               | -            | Default mode            |  |

Table 10 Modes of operation

# 1, NORMAL MODE

This is intended to be the mode of operation when the ACE9050 is fully commissioned in the application. The internal 6303 Microprocessor is used and the Boot block ensures the program counter goes to the beginning of the ROM code area after initialisation. In Normal mode various blocks can be powered down to save current, and the processor can be programmed to run at 1.008MHz or 2.016MHz.

# 2. EMULATION MODE

This mode is intended for system and software development work. In Emulation mode the Internal 6303 processor is made redundant and its function is replaced in the system by an external 6303 processor. This is to facilitate using a generic 6303 In-Circuit Emulator (ICE) for software development. Table 11 shows the functionality of external pins that change in this mode. This is to enable all of the internal functions of the ACE9050 to operate as they would in Normal mode. In Emulation mode the external processor or ICE must be set up to operate in Multiplexed mode. This mode is only intended for use at room temperature.

| Normal mode |               |     | Emulation mode       |      |

|-------------|---------------|-----|----------------------|------|

| Pin         | Function Type |     | Function             | Туре |

| D[7:0]      | Data          | 1/0 | Data and A[7:0] I/P  | 1/0  |

| A[13:8]     | Address       | 0   | Address I/P A[13:8]  | 1    |

| A[15:14]    | Not used      | 1   | Address I/P A[15:14] | 1    |

| ECLK        | 6303 Clk      | 0   | ACE9050 Clock I/P    | 1    |

| R/W         | Not used      | 0   | Read/Write strobe    | 1    |

| AS          | Not used      | 1   | Address Latch strobe | 1    |

| IRQN        | Not used      | 0   | 6303 Interrupt       | 0    |

| ICN         | Not used      | 0   | 6303 Timer P2 [0]    | 0    |

Table 11 Normal and Emulation mode functions

# 3. SERVICE MODE

This mode is intended for system development and phone service, where reprogramming of a FLASH ROM device is required. The two areas that are affected by Service mode are:

- The Watchdog and Autonomous Time Out (ATO) resets are inhibited. This is intended for software development work. The POFFN pin (85) is initially programmed to be a 1 by the ROM code in this mode.

- The internal ROM code facilitates loading of a program into the RAM area from the SCI. This program would normally be a FLASH loading program. The SCI may then be used to load new object code into the FLASH memory of a system.

The ROM code has a time out function so that if a valid start code is not detected on the SCI normal code operation will begin. The ROM code is fully described in the Internal ROM Boot Block section.

#### 4. TEST MODE

Test mode increases the efficiency of volume testing of the part. Pin 1, TESTN, should be hardwired to  $V_{\rm DD}$ .

## **5. POWER DOWN MODES**

To reduce overall power consumption, selective power down of various blocks is available under software control. In the power down state each block will go to a predetermined logic state. The following power reduction features are included:

Bus Interface (CSEPN = 1 and Address = 3FFF) 8-064 MHz external Clock Off 1-008 MHz external Clock Off AMPS/TACS Modern power down ACE Serial Chip Interface Power down CPU Sleep Mode Crystal Oscillator Off 1MHz/2MHz Bus speed

# **FUNCTIONAL DESCRIPTIONS**

#### 1. ACE9050 6303R DESCRIPTION

**General Description**

The embedded processor in the ACE9050 is functionally equivalent to a generic 6303R micro. This data sheet outlines the functionality of the embedded processor, detailing its operation with the internal peripheral circuitry. It is not intended as a programmers guide for a 6303. If further information is required the following publications are recommended:

HITACHI 8-bit single-Chip Microcomputer Data Book Sept. 1989 Motorola Microprocessors Data Manual Macro Assemblers Reference Manual, Motorola Semiconductors MC68MASR(D).

The 6303 is an 8-bit processing unit which has a completely compatible instruction set with the 6301. It has object code upwardly compatible with the HD6300, HD6801 and HD6802.

The ACE9050 has 6016 bytes of internal RAM (the 6303R has 128 bytes). Other features are: a Serial communications interface (SCI or UART), a 16-bit timer, 8-bit I/O port and a 5-bit I/O port (only 2 are bonded out from the ACE9050). The bus speed can be configured to 1.008 in Normal mode or 2.016MHz in Turbo mode.

The ACE9050 has an Emulation mode whereby its internal 6303 is bypassed and the peripheral functions may be driven externally by a standard 6303 ICE.

#### ACE9050 6303R Pin Description

The ACE9050 6303 is embedded in a kernel which interfaces to the rest of the circuitry. Table 12 describes the internal connections to the ACE9050 6303. In Emulation mode, none of the output pins drive the internal buses.

#### Clock

The CPU Clock is provided from the Clock Generator Circuit in the ACE9050. This clock is either 1.008MHz or 2.016MHz. It is not further divided down in the 6303, so this clock frequency is the same as the processor bus speed. Refer to the Clock Generator section for details of how to configure the internal

| Name            | I/O  | Description                             |  |

|-----------------|------|-----------------------------------------|--|

| $V_{DD}$        | ı    | Internal power supply                   |  |

| V <sub>SS</sub> | 1    | Internal Ground                         |  |

| XTAL            | -    | Not connected                           |  |

| External        | -    | Not Used (System Clock Driven           |  |

|                 |      | into E directly)                        |  |

| E               | ı    | System Clock IP                         |  |

| NMI             | -    | Not used: Tied to VDD                   |  |

| IRQ             | ı    | Connected to Interrupt Control block    |  |

|                 |      | and IRQN pin                            |  |

| RES             | ı    | Connected to Internal Reset MRI         |  |

| Port2 [0]       | 1/0* | Internally connected to IFC Counter     |  |

| Port2 [1]       | -    | Not connected                           |  |

| Port2 [2]       | 1/0* | Internally connect to Baud Clk          |  |

| Port2 [3]       | 1/0  | External Pin (SCI I/P or Port2)         |  |

| Port2 [4]       | 1/0  | External Pin (SCI O/P or Port2)         |  |

| Port1 [7:0]     | 1/0  | External Pin (Port1 I/0 Access)         |  |

| Addr [15:8]     | 0    | Connected to internal address Bus       |  |

| D/A [7:0]       | I/O  | Internally connected to Buses           |  |

| R/W             | 0    | Connected to internal logic and R/W pin |  |

| AS              | 0    | Connected to internal logic             |  |

| STBY            | •    | Standby mode disabled = V <sub>DD</sub> |  |

<sup>\*</sup>Port2 bits 0 and 1 must be configured as inputs in the 6303 to use the IFC and Baud rate generator functions.

clocks.

Table 12 Generic 6303 I/O mapping

#### Port 1

This is an eight bit I/O port with the direction of each bit being defined by the data direction register DDR1 as given in Table 13. The Port can be accessed for read and write via the Port1 register. The output buffers have tristate capability, being high impedance when used as inputs. When the processor is reset these are high impedance. Two pins (Bits 3 and 4) associated with this port are also used as I/O from the I<sup>2</sup>C interface on the ACE9050. This is configured by Port 5 bit 2. The 6303 is internally configured to mimic Multiplexed mode of operation, so this port cannot be configured to output the lower address bits. The ACE9050 has dedicated pins for this purpose.

# **Associated Registers**

| Name                 | Description                                                                      |

|----------------------|----------------------------------------------------------------------------------|

| DDR1<br>Bits [7: 0]  | Sets corresponding Port line to output     Sets corresponding Port line to input |

| Port 1<br>Bits [7:0] | Read and Write access to Port 1                                                  |

Port 2 Table 13 Port 1 associated registers

This is a five-bit I/O port with the direction of each bit being defined by the data direction register DDR2. Only bit 3 and bit 4 are connected to external pins. This allows access to the I/O port and Serial Interface functions. Bit 0 and bit 2 are internally connected to the IFC and Baud clock. They must be configured as inputs to use these functions. Bit 0 and bit 2 are not externally accessible

The ACE9050 has an additional Output Port 2, which is separate from the 6303 Port 2.

#### **Associated Registers**

| Name                  | Description  1: Sets corresponding Port line to output 0: Sets corresponding Port line to input |  |

|-----------------------|-------------------------------------------------------------------------------------------------|--|

| DDR2*<br>Bits [4:0]   |                                                                                                 |  |

| Port 2*<br>Bits [4:3] | Read and Write access to Port 2                                                                 |  |

The TRCSR register overrules these registers.

\*Table 14 Port 2 associated registers\*

#### **Programmable Timer**

The ACE9050 6303R contains a 16 bit programmable timer which may measure the period of an input waveform, as with a standard 6303R. This counter runs from the ECLK. The counter cannot generate an output waveform. The input to the timer is internally connected to the IFC counter for the AFC loop function. The timer hardware consists of an 8-bit status and control register, a 16-bit free running counter and a 16-bit input capture register.

# TCSR (Timer Control and Status Register)

The Control and Status register has three flags: Input capture, Output Compare Match and Timer Overflow. Each flag has an associated interrupt enable. The other two bits in the register are for control of the output level and input edge select. The bits are described in Table 15.

| Bit | R/W | Name | Description                                                                                       |  |

|-----|-----|------|---------------------------------------------------------------------------------------------------|--|

| 7   | R   | ICF  | Transition of appropriate type occurred on input (ICN). Cleared by read of Input Capture register |  |

| 6   | R   | OCF  | Match between Free Running Counter and Output Compare Register*                                   |  |

| 5   | R   | TOF  | Timer overflow. Cleared by read of counter.                                                       |  |

| 4   | R/W | EICI | Enable an ICF interrupt                                                                           |  |

| 3   | R/W | EOCI | Enable an OCF interrupt*                                                                          |  |

| 2   | R/W | ETOI | Enable Timer overflow interrupt                                                                   |  |

| 1   | R/W | IEDG | 0 = Negative edge on ICN trigger ICR<br>1 = Positive edge on ICN trigger ICR                      |  |

| 0   | R/W | OLVL | Output level*                                                                                     |  |

<sup>\*</sup>As the timer cannot generate an output these bits are considered nonfunctional in the ACE9050.

Table 15 TCSR bit descriptions

#### **FRC: Free Running Counter**

The FRC is a 16-bit ReadWrite counter; Data can be read from or written to it. The register has extra hardware to load and save both bytes of the counter simultaneously when a double byte store instruction is used. The counter is incremented by the processor clock. Reading from the counter does not affect it.

## **ICR: Input Capture Register**

The ICR is a 16-bit Read register which holds the value of the Free Running Counter when a transition is detected on ICN, i.e. the IFC Counter Output.

# Serial Communication Interface (SCI or UART)

The processor contains a full-duplex asynchronous Serial Communications interface. It consists of a transmitter and receiver which operate independently but with the same data format and rate. Both parts communicate with the CPU via the data bus and to the outside world via Port 2. Interrupts generated can be individually masked. The receiver can be sent to 'sleep' by software. No receive interrupts are generated during a message in this state. The Baud rate can be generated within the ACE9050 6303 or the ACE9050 can provide a baud rate generator and selection register external to the processor block. This allows the following standard baud rates to be programmed: 600,1200. 2400, 4800 or 9600.

The hardware consists of four registers: an 8-bit control/status register, 4-bit mode select, an 8-bit receive data and an 8-bit transmit data register.

| Bit | R/W | Name | Description                                                        |  |

|-----|-----|------|--------------------------------------------------------------------|--|

| 7   | R   | RDRF | RX Data Register Full*                                             |  |

| 6   | R   | ORFE | Overrun/Framing Error*                                             |  |

| 5   | R   | TDRE | TX Data Register Empty                                             |  |

| 4   | R/W | RIE  | RX Interrupt Enable: Enables an interrupt for both Bit 7 and Bit 6 |  |

| 3   | R/W | RE   | RX Enable. This sets Port2 bit 3 to Input regardless of the DDR2   |  |

| 2   | RW  | TIE  | TX Interrupt enable: Bit 5 will generate an Interrupt              |  |

| 1   | R/W | TE   | TX Enable: This sets Port2 bit 4 to Outp regardless of DDR2        |  |

| 0   | R/W | WU   | Wake Up: Set by software and cleared by hardware.**                |  |

<sup>\*</sup> Overrun is where new data is placed in the Receive register before the old data has been read. Framing Error is where the bit counter is not synchronised with the boundary of the byte in the Received bit stream defined in Table 17.

\*\* The Wake Up mode is intended for systems where more than one Processor is on the UART link, and is addressed by the first byte of data. If the address is incorrect the processor can disable the interrupts and effectively ignore the word.

Table 16 TRCSR: Transmit/Receive Control Status Register bit descriptions

| Condition     | Bit 7 | Bit 6 |

|---------------|-------|-------|

| No Data       | 0     | 0     |

| Good Data RX  | 1     | 0     |

| Framing error | 0     | 1     |

| Overrun error | 1     | 1     |

#### NOTE:

Bits 7 and 6 are cleared by reading the Status register, followed by reading the Received Data register

Table 17

# RMCR Transfer Rate/Mode Control Register

The mode select register controls the clock source and setup. This is a write-only register. The processor can use an internally divided down processor clock to give the Baud clock. The Baud rate division ratio can be set to a value from 16 to 4096. However, this could lead to non-standard Baud rates so the ACE9050 provides a separate Baud rate generator. The bit functions of this register are described in Table 18.

| Bits   | Value | Description                      |

|--------|-------|----------------------------------|

| [7: 4] | XXXX  | Not used                         |

|        |       | Clock Control mode               |

| [3: 2] | 00    | SCI disabled                     |

|        | 01    | Use processor Clk for Baud rate  |

|        | 10    | Not used                         |

|        | 11    | Use ACE 9050 Baud rate generator |

|        |       | Speed Select (Bits 3: 2 = 01)    |

| [1:0]  | 00    | E÷16                             |

|        | 01    | E÷128                            |

|        | 10    | E÷1024                           |

|        | 11    | E÷4096                           |

Table 18 RMCR Transfer Rate/Mode Control register

| Bits         | Description                                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------|

| [7:0] (Data) | RDR: Received Data Register Read received bits. First bit received is placed in bit 0, last in bit 7                      |

| [7:0] (Data) | TDR: Transmit Data Register Write register to store bits before serial transfer from Transmit shift register, bit 0 first |

Table 19 Receive and Transmit Data registers

In Normal Mode the SCI should be initialised before operation. This means writing to the mode select and the control/status register. In Service Mode the SCI is configured for 9600 baud, and the receive interrupt enabled. When the transmitter is first initialised it will send a ten-bit preamble of '1's before being ready to transmit data.

Once initialisation is complete data transmission enabled by writing to the transmit data register. TDRE is set to 0. A start bit is transmitted (0). Next the eight bit data starting at bit0 are transmitted followed by a single stop bit (1). The hardware sets the TDRE bit in the TRCSR register. If the CPU does not transfer another word the output goes high.

The receiver is configured during initialisation. If enabled and a start bit is detected (0), the next nine bits will be sampled approximately at the centre of each bit. If the ninth bit is a 1 the data is transferred to the Receive data register. The RDFR bit is set in the TRCSR register. If the ninth bit is not a 1 or the receive data register is full then the ORFE bit is set to indicate an error. A read of the TRCSR register followed by a read of the Received data register (RDR) will clear these flags.

#### RAM Control Register (RAMCR)

This register is read only in the ACE9050. Bit 6 (RAME) is set to zero: this is because the RAM on the ACE9050 is external to the 6303 block. Bit 7 (STBY) is also set to zero by the ACE9050 because Standby mode is not supported.

# **Operating Modes**

The Generic 6303R has two modes: Multiplexed and non-Multiplexed, where the mode is selected externally using P2[0], P2[1] and P2[2]. This is not required on the ACE9050, where the mode is set to mimic multiplexed internally when the reset (MRN) is released. The ACE9050 processor has two fundamental modes of operation: Emulation and Normal, which are described in the MODES OF OPERATION section.

#### **Low Power Consumption Modes**

The generic 6303 Standby mode is not supported by the ACE9050 6303. The STBY pin is not accessible. The Sleep

mode is fully supported by the ACE9050 6303. This mode is entered by execution of the SLP instruction. Escape is via an interrupt or reset.

#### Address, Data and Memory Control

The Address, Data and control lines from the ACE9050 6303 connect to a kernel which interfaces to the on chip bus structures. The Bus Interface block provides suitable buffering to drive required buses externally, and configure the I/O for Emulation mode.

# **Interrupt Processing**

The interrupt processing in the ACE9050 6303 is essentially the same as a generic 6303, the exception being NMI, which is not available. The IRQN is internally connected to the I<sup>2</sup>C interrupt, the External Interrupt and the Internal interrupt blocks.

These blocks combine all the possible sources for interrupts into one line which is connected to IRQN. This is also connected to a pin for use in Emulation mode. The IRQN is maskable. The interrupt mask bit in the Condition Code Register must be zero for the CPU to respond to the Interrupt request, as with a generic 6303.

The Interrupt Vector Memory map is shown in Table 20.

| Priority | Vector |      | Interrent                 |

|----------|--------|------|---------------------------|

| Friority | MSB    | LSB  | Interrupt                 |

| 1        | FFFE   | FFFF | RES                       |

| 2        | FFEE   | FFEF | TRAP                      |

| 3        | FFFA   | FFFB | Software Interrupt (SWI)  |

| 4        | FFF8   | FFF9 | IRQN                      |

| 5        | FFF6   | FFF7 | ICF (Timer Input Capture) |

| 6        | FFF4   | FFF5 | OCF (Timer OP Compare)    |

| 7        | FFF2   | FFF3 | TOF (Timer Overflow)      |

| 8        | FFF0   | FFF1 | SCI (UART)                |

Table 20 Interrupt vector memory map

# **Error Processing**

An interrupt is generated when an undefined op-code is fetched, or when an instruction is fetched from an impossible address. This is in the range 0000-007F for the ACE9050 (0000-001F for a standard 6303).

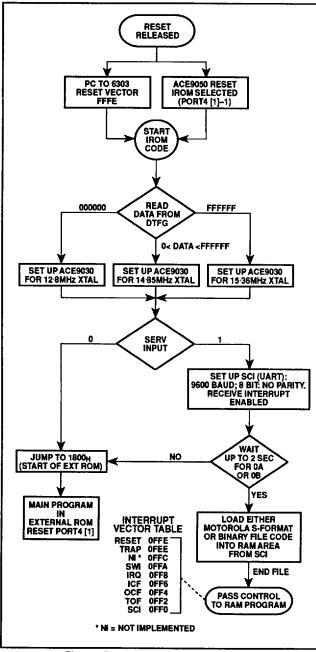

# 2. INTERNAL ROM BOOT BLOCK

The ROM code provides a boot block for the ACE9050. Following a reset condition code execution will always start in the internal ROM. The internal ROM data flow depends on the condition of the SERV Input and thus the mode of operation of the ACE9050. The operation flow of the IROM is shown in Fig. 12 and described in the following sections:

# **Normal Mode**

- 1. Read serial data on ACEBus DTFG line

- 2. Configure ACE9030 Reference dividers via ACEBus.

- Set the program counter to the beginning of external ROM (1800<sub>H</sub>).

#### Service Mode

- 1. Read serial data on ACEBus DTFG line

- Configure ACE9030 Reference Dividers via ACEBus

- 3. Configure the UART to RX

- Wait 2 seconds for special code on UART if not found go to step 3 of Normal Mode

- 5. Load Data from UART into RAM

- Pass control to Program loaded in RAM

- Map Interrupt Vectors to RAM space.

- 8. The RAM program can then Program a FLASH memory via the UART.

## Steps 1and 2 - Both Modes

The ACE Chipset offers the flexibility of using one of three different crystal frequencies: 12.8, 14.85 or 15.36 MHz. The chosen crystal can be used to generate all the system clocks and local oscillator frequencies required in a cellular phone application. The ACE9050 must detect what crystal is being used and set up the correct value for the OSC8 dividers in the ACE9030. This is handled in the Internal ROM. Upon Reset the ACE9030 sets the OSC8 for a 15:36 MHz Crystal, so the ACE9050 is not clocked faster than 8-064 MHz.

The system designer must set up the DTFG input (the Radio Serial Interface, pin 82), using an external resistor of approximately  $10k\Omega$ . The crystal frequency determines where the resistor is terminated, as shown in Table 21. Upon reset the ACE9050 Internal ROM reads the DTFG input and programs the ACE9030 OSC8 accordingly.

| Crystal  | Serial Data RXed  | Resistor from pin 82 to: |

|----------|-------------------|--------------------------|

| 12·8MHz  | 000000            | V <sub>SS</sub> (Gnd)    |

| 14·85MHz | 0 < Data < FFFFFF | A1 (pin 31)              |

| 15∙36MHz | FFFFFF            | V <sub>DD</sub>          |

Table 21

#### Step 3 - Normal Mode

Program code in the external EPROM at address 1800H is started. The Internal ROM resides at the top of the processor address space FE00H - FFFFH. Obviously the main program requires access to this space for Interrupt vectors. The Internal ROM is deselected by setting PORT4 [1] to zero. It is recommended that any external program does this quickly and always before enabling any Interrupt sources.

#### Step 3 - Service Mode

The Internal ROM will initialise the 6303 SCI (UART) and set up the Baud rate generator to 9600 Baud. The SCI is initialised to the following:

Receiver On

Transmitter ON

Receive Interrupt enabled

9600 Baud rate from ACE9050 Baud Rate Generator

The Receive interrupt will remain enabled after the IROM code execution. The UART is always configured for 8-bit data transfer, no parity and one stop bit.

#### Steps 4, 5 and 6 - Service Mode

When in service mode the ACE9050 can download a program from the SCI to RAM. To achieve this the first code (start code) must be sent down to the SCI within 2 seconds of releasing Reset. The boot block code will write the subsequent code into RAM. Two code formats are supported:

- (a) Motorola S- Record format

- (b) Binary dump

# (a) Motorola S-Record Format

The start code for this format is 'OA' in ASCII (i.e. 30H, 41H).

s0nnppppxxxxxxxxxxcc

First Record in file

s1nnppppdddddddddddddcc Data record with 16-bit address

s9nneeeecc

End of file record (nn = 3)

#### where:

nn = Number of bytes (xx+pp+dd+cc) in record.

pppp = Load address

dd = data bytes, 1 to 16

xxxx = Name of program (ASCII coded)

eeee = Program entry address

cc=checksum calculated from [255-sum(pp)+sum (dd)+ sum (xx)+sum (ee)+nn)] MOD 256

When the 's9' is read in from the End of File Record, the code will jump to the reset vector. This is mapped to 0FFE by the IROM. The RAM program will then begin execution as for a reset. The last 6 characters of the record file (nneeeecc) will be received while the program is running.

## (b) Binary dump file

This format is for the binary representation of the code, not a proprietary binary format code. The start code for this format is OB' ASCII (ie 30<sub>H</sub>, 42<sub>H</sub>) . First two bytes are the start address pointer.

The next two bytes are the end address pointer +1. The next bytes are the data bytes. These are loaded consecutively from the start to the end address. When the last data byte is received the program counter will go to the loaded code start address pointer.

#### Step7-Interrupt Vector table

The Internal ROM will map the 6303 Interrupt vector table to an address space in RAM so the loaded program can deal with interrupts as shown in Table 22. In general only the SCI interrupt is required for a Flash Loading program.

| Vector address | Interrupt                |

|----------------|--------------------------|

| 0FFE           | Reset                    |

| 0FEE           | Trap                     |

| 0FFC           | Not Implemented          |

| 0FFA           | SWI Software interrupt   |

| 0FF8           | IRQN                     |

| 0FF6           | ICF Timer Input compare  |

| 0FF4           | OCF Timer Output compare |

| 0FF2           | TOF Timer overflow       |

| 0FF0           | SCI                      |

|                | 1                        |

Table 22

# RAM Area Reserved for IROM Operation

The IROM code itself requires a small amount of RAM during its operation. This area must not be used for storage of the RAM program.

#### RAM Reserved area: 080<sub>H</sub> to 100<sub>H</sub>

Fig. 12 shows the data flow for the internal ROM.

#### 3. DECODER

The Decoder logic creates the memory map for system containing the ACE9050. Internally, it maps the ACE9050 registers, RAM and ROM onto the System Memory map. External ROM is also mapped onto the available address space by the Decoder, but the situation can be complicated by the Bank Address switching circuitry. Refer to Table 23 on the following page for details of memory mapping.

Note that the ACE9050 contains Memory Banked Switching circuitry. Refer to the section 4 'BUS INTERFACE AND MEMORY

BANKING' below for details.

The Decoder also creates suitably timed Output Enable and Write Enable signals (refer to Figs. 4 and 5) for parallel read and write cycles to external devices.

**3768522 0028925 780**

| Address (hex) | Description                |

|---------------|----------------------------|

| 0000-001F     | 6303 Registers             |

| 0020-007F     | Internal ACE9050 Registers |

| 0080-17FF     | RAM                        |

| 1800-7FFF     | Non Banked external ROM    |

| 8000-BFFF     | Banked external ROM        |

| C000-FDFF     | Non-Banked external ROM    |

| FE00-FFFF     | Internal / External ROM    |

Table 23

Fig. 12 Data flow for the internal ROM