# COMPLETE µP COMPATIBLE 12-BIT DAC

#### **FEATURES**

- Output ranges: 0 to  $\pm 10V$ ,  $\pm 10V$ ,

- Coding: binary; offset binary

- Linearity: ±0.01%

- Settling time: 2.5µS

- µP compatible

- 28-pin package

- CMOS, TL compatible

- Double buffered inputs

#### DESCRIPTION

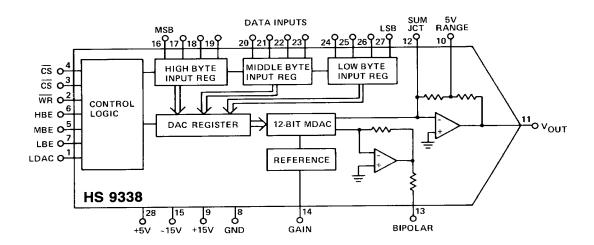

HS9338 is a µP compatible, complete 12-bit double buffered digital-to-analog converter. To enhance application flexibility, the data input registers have been configured as 3 independent, 4-bit bytes. This enables the user to directly interface to 4, 8, and 12-bit data buses. HS9338 comes complete with interface control logic. The three separate byte enable inputs latch data from the bus into the

appropriate primary data latches. The LDAC input transfers data from the primary latches to the DAC register. In addition to these input functions are two chip select inputs and a read/write input allowing direct memory-map configurations. All input controls are static to allow hardwired configurations.

### **FUNCTIONAL DIAGRAM**

# **SPECIFICTIONS**

(Typical @25 °C unless otherwise noted. Power supply voltages: +15V, -15V, +5V, ( $\pm 5\%$ ))

| MODEL                                                             | HS 9338-2            | HS 9338-0        |

|-------------------------------------------------------------------|----------------------|------------------|

| DIGITAL INPUT                                                     |                      |                  |

| Resolution                                                        | 12 Bit               | •                |

| Unipolar Code                                                     | Binary               | *                |

| Bipolar Code                                                      | Offset Binary        |                  |

| Logic Compatibility <sup>1</sup>                                  | CMOS, TTL            |                  |

| Control Logic Inputs                                              | 20 µ A               | •                |

| IIH @VIH = 2.4V                                                   | -0.36mA              | *                |

| IIL @VIL = 0.4V<br>Data Input Current <sup>5</sup>                | ± 1µ A               | •                |

|                                                                   | <del>-</del> ·       |                  |

| ANALOG OUTPUT                                                     | ± 0.1% FSR           | *                |

| Scale Factor Accuracy <sup>2</sup><br>Initial Offset <sup>2</sup> | 10.1701.011          |                  |

| Bipolar                                                           | ± 0.1% FSR max       | •                |

| Unipolar                                                          | ±0.05% FSR max       | •                |

| Voltage Range <sup>2</sup>                                        |                      | *                |

| Bipolar                                                           | ± 10V,               | *                |

| Unipolar                                                          | 0 to +10V            |                  |

| STATIC PERFORMANCE                                                |                      | + 0.050% FSR max |

| Integral Linearity <sup>3</sup>                                   | ± 0.015% FSR max     | ± 0.050% FSR max |

| Differential Linearity                                            | ± 0.024 FSR max      | 10 Bits          |

| Monotonicity                                                      | 12 Bits              | 10 100           |

| DYNAMIC PERFORMANCE                                               |                      |                  |

| Full Scale Transition                                             | 5 0                  | *                |

| Settling Time                                                     | 5µS max<br>2.5µS max | •                |

| Full Carle Transition                                             | 2.5 µ 5 max          |                  |

| Full Scale Transition Slew Rate                                   | 10V/µS min           | •                |

| Delay to Analog Output                                            | • •                  |                  |

| From Bits Input <sup>4</sup>                                      | 220nS                | •                |

| From LDAC                                                         | 220nS                | •                |

| From CS4 or WE4                                                   | 225nS                |                  |

| STABILITY                                                         |                      |                  |

| Scale Factor                                                      | 20ppm FSR            | :                |

| Integral Linearity                                                | 1ppm FSR max         | •                |

| Differential Linearity                                            | 1ppm FSR max         |                  |

| Offset Drift                                                      | 10ppm/°C             | •                |

| Bipolar                                                           | 5ppm/°C              | •                |

| Unipolar  Monotonicity Temperature Range                          | 0°C to +70°C         | •                |

| * '                                                               | 0 0 10 7 10 0        |                  |

| ± 15V POWER SUPPLY                                                | 12mA                 | *                |

| + 15V Supply Current                                              | 10mA                 | •                |

| - 15V Supply Current<br>PSRR                                      | 0.005%/%             | •                |

| · =:                                                              |                      |                  |

| + 5V POWER SUPPLY<br>+ 5V Supply Current                          | 24mA                 | *                |

|                                                                   | 2 11177              |                  |

| TEMPERATURE RANGE                                                 | - 55°C to +125°C     | *                |

| Operating                                                         | - 65°C to +155°C     | *                |

| Storage                                                           | - 00 0 10 1 100 0    |                  |

| MECHANICAL                                                        | Di d                 | *                |

| Case Style                                                        | Plastic              |                  |

NOTES: 1. Control inputs are TTL and 5V CMOS only. data inputs are fully CMOS and TTL compatible. 2. See APPLICATION NOTES for adjustment procedures. 3. Specified as "Best Straight Line". 4. Operating the unit with the DAC Register transparent may result in output "glitches" due to logic skewing with the unit. 5. Digital Input Voltage must not exceed supply voltage or go below -0.5V. "O" 0.8V.2.4V "1" VDD.

\*Same as HS 9338-2.

**CAUTION:** ESD (Electro-Static Discharge) sensitive device. Permanent damage may occur when unconnected devices are subjected to high energy electrostatic fields. Unless otherwise noted, the voltage at any digital input should never exceed the supply voltage by more than 0.5 volts or go below - 0.5 volts.

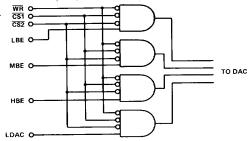

### CONTROL LOGIC FUNCTIONAL DIAGRAM

#### TRUTH TABLE

| HS 9338 CONTROL INPUTS |             |             |     |     |     | HS 9338 OPERATION |                                                                                           |  |

|------------------------|-------------|-------------|-----|-----|-----|-------------------|-------------------------------------------------------------------------------------------|--|

| WR                     | CS1         | CS2         | LBE | MBE | HBE | LDAC              | H3 3038 OF ENATION                                                                        |  |

| 1<br>X<br>X            | X<br>1<br>X | X<br>X<br>1 | ×   | х   | ×   | ×                 | Device not selected<br>Output reflects previously<br>loaded data                          |  |

| 0                      | 0           | 0           | 1   | 0   | 0   | 0                 | Write data into low byte<br>data register                                                 |  |

| 0                      | 0           | 0           | 0   | 1   | 0   | 0                 | Write data into middle<br>byte data register                                              |  |

| 0                      | 0           | 0           | 0   | 0   | 1   | 0                 | Write data into high byte data register                                                   |  |

| 0                      | o           | 0           | 0   | 0   | 0   | 1                 | Load DAC register with<br>data in low byte middle<br>byte and high byte data<br>registers |  |

| 0                      | 0           | 0           | 1   | 1   | 1   | 0                 | Write data simultaneous<br>into all data registers                                        |  |

| 0                      | 0           | 0           | 1   | 1   | 1   | 1                 | Write data directly into<br>DAC register                                                  |  |

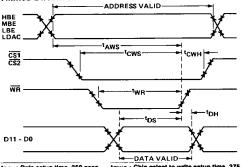

t<sub>DS</sub>: Data setup time, 250 neec t<sub>DH</sub>: Data hold time, 20 neec

ICWS : Chip select to write setup time, 375 nsec tCWH: Chip select to write hold time, 0 nsec twR : Write pulse width, 350 need taws : Address to write setup time, 250 need

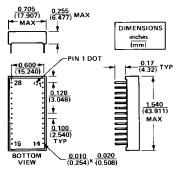

#### PACKAGE OUTLINE

#### PIN DIAGRAM

| PIN | FUNCTION                                                    |  |  |  |

|-----|-------------------------------------------------------------|--|--|--|

| 1   | LDAC, LOADS DAC REGISTER AND CHANGES OUTPUT                 |  |  |  |

| 2   | WR, WRITE INPUT, ACTIVATES ALL CONTROLS                     |  |  |  |

| 3   | CS2, CHIP SELECT INPUT 2                                    |  |  |  |

| 4   | CSI, CHIP SELECT INPUT 1                                    |  |  |  |

| 5   | MBE, MIDDLE BYTE ENABLE, D4 TO D7                           |  |  |  |

| 6   | HBE, HIGH BYTE ENABLE, D8 TO D11                            |  |  |  |

| 7   | LBE, LOW BYTE ENABLE, DO TO D3                              |  |  |  |

| 8   | GND, GROUND, ANALOG AND DIGITAL GROUND CONNECTED INTERNALLY |  |  |  |

| 9   | V <sub>CC</sub> , +15V SUPPLY                               |  |  |  |

| 10  | RANGE, 5V OUTPUT HANGE INPUT                                |  |  |  |

| 11  | VOUT, DAC VOLTAGE OUTPUT                                    |  |  |  |

| 12  | SUMJCT, SUMMING JUNCTION OF OUTPUT OPAMP                    |  |  |  |

| 13  | BIPOLAR, CONNECTED TO SUMJCT FOR BIPOLAR OUTPUT RANGE       |  |  |  |

| 14  | GAIN, INPUT TO ADJUST FULL SCALE OUTPUT VOLTAGE             |  |  |  |

| 15  | V <sub>EE</sub> , -15V SUPPLY                               |  |  |  |

| 16  | D11, DATA INPUT, WEIGHT 2-1, MSB                            |  |  |  |

| 17  | D10, DATA INPUT, WEIGHT 2-2                                 |  |  |  |

| 18  | D9, DATA INPUT, WEIGHT 2-3                                  |  |  |  |

| 19  | D8, DATA INPUT, WEIGHT 2-4                                  |  |  |  |

| 20  | D7, DATA INPUT, WEIGHT 2-5                                  |  |  |  |

| 21  | D6, DATA INPUT, WEIGHT 2 <sup>-6</sup>                      |  |  |  |

| 22  | D5, DATA INPUT, WEIGHT 2-7                                  |  |  |  |

| 23  | D4, DATA INPUT, WEIGHT 2-8                                  |  |  |  |

| 24  | D3, DATA INPUT, WEIGHT 2 <sup>-9</sup>                      |  |  |  |

| 25  | D2, DATA INPUT, WEIGHT 2-10                                 |  |  |  |

| 26  | D1, DATA INPUT, WEIGHT 2-13                                 |  |  |  |

| 27  | DO, DATA INPUT, WEIGHT 2-12, LSB                            |  |  |  |

| 28  | V <sub>DD</sub> , +5V SUPPLY, CONTROL LOGIC                 |  |  |  |

|     |                                                             |  |  |  |

#### **OUTPUT CONNECTIONS**

|   | RANGE          | OUTPUT | CONNECT<br>PIN 12 | CONNECT<br>PIN 10 | CONNECT<br>PIN 13 |

|---|----------------|--------|-------------------|-------------------|-------------------|

| ı | 0 to + 10V     | PIN 11 | OPEN              | OPEN              | OPEN              |

| ١ | – 10V to + 10V | PIN 11 | PIN 13            | OPEN              | PIN 12            |

| ı | -5V to +5V     | PIN 11 | PIN 13            | PIN 12            | PIN 12            |

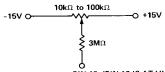

#### **OUTPUT OFFSET ADJUST**

to PIN 12 (PIN 12 IS AT VIRTUAL GROUND) RANGE: ±0.25% F.S.

Adjust for  $V_{0,iit}$  = 0.000 Volt at input code 00 . . . 0 for unipolar operation or at input code 10 . . . 0 for bipolar operation.

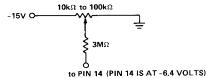

#### **OUTPUT GAIN ADJUST**

RANGE: ±0.5%

Adjust for  $V_{out}$  = +9.9976 Volt at input code 11 . . . 1 (4.9988 Volt on 0.5V range) or for  $V_{Out}$  = -10.000 Volt at input code 00 . . . 0 (-5.0000 Volt on ±5V range) if set up for bipolar operation.

# APPLICATIONS INFORMATION

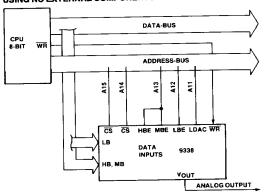

# INTERFACING THE HS9338 TO AN 8-BIT PROCESSOR USING NO EXTERNAL COMPONENTS

This mode of operation requires 13k bytes of unused addresses. No additional address decoder is necessary. The two chip-select input together with the byte-enable and load-DAC inputs are used to control all functions of the DAC. Through selecting the address-lines the user can vary the addresses used to control the DAC. In the above figure the control signals have the following address-configurations (hex):

HBE, MBE 2000 LBE 1000 LDAC 0800

The LDAC input should not be tied together to the LBE input to ensure correct data transfer between the DAC registers.

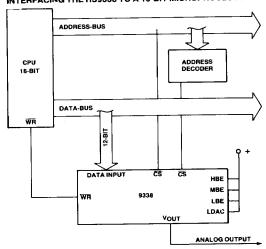

## INTERFACING THE HS9338 TO A 16-BIT MICROPROCESSOR

Interfacing the HS9338 to a 16-Bit microprocessor is quite easy, because no multiplexing of the data inputs is necessary. An address decoder and the second chip-select input is used to select the DAC.

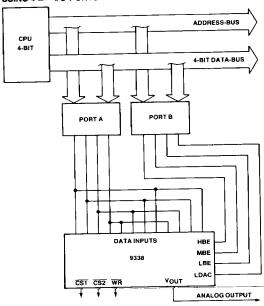

# INTERFACING THE HS9338 to a 4-BIT MICROPROCESSOR USING 4-BIT I/O-PORTS

This figure shows how to operate the HS 9338 with two 4-Bit ports. The chip-selects are tied to ground allowing continuous operation; they can be used for operating more DAC's at the same port. In the first step data should appear at the port A outputs; in the second step the control flags should appear on port B.

# PRODUCT SCREENING AND QUALIFICATION

Products cataloged as Class B are fully screened in accordance with Method 5004 of MIL-STD-883, Class B.

Hybrid Systems is equipped to perform qualification and quality conformance testing of its products to the Class B requirements of MIL-STD-883, Method 5005. Processing to applicable Class S requirements is available where the higher confidence level is required.

## ORDERING INFORMATION

| MODEL     | DESCRIPTION             |  |

|-----------|-------------------------|--|

| HS 9338-2 | μΡ DAC, 0.01% Linearity |  |

| HS 9338-0 | μΡ DAC, 0.05% Linearity |  |

Specifications subject to change without notice.