# 80C24 AutoDUPLEX™ CMOS Ethernet Interface Adapter

96345

This document is an LSI Logic document. Any reference to SEEQ Technology should be considered LSI Logic.

## Functional Features

- Low Power CMOS Technology Ethernet Serial Interface Adapter with Integrated Manchester Code Converter (MCC<sup>TM</sup>), AUI and 10Base-T Transceiver with Output Wave Shaping and on chip filters.

- Meets IEEE 802.3 10Base-5, 10Base-2, 10Base-T Standards

- Direct Interface to SEEQ, INTEL, AMD & NATIONAL LAN Controllers

- Automatic or Manual Selection of AUI/10Base-T Interface

- Provides AutoDUPLEX<sup>™</sup> Detect Function for SEEQ LAN Controllers and Doubles Bandwidth to 20 MBits/sec for Switched Networks

- Status Indicators: Link, Transmit & Receive, Port Selection-AUI/TP, TP Cable Polarity

- Diagnostic Loopback Support

- Power On Reset with Power Down Mode to Conserve System Power

- Separate Analog/Digital Power and Ground Pins to Minimize Noise

## Interface Features

- Meets IEEE 10Base-T Standards and IEEE 802.3 standards for AUI.

- On Chip Transmit Wave Shaping and Low Pass Filter Circuits No External Filters Required

- Selectable Termination Impedance to Support UTP and STP Cables, (100 ohms, 150 ohms)

- Long Cable Mode Support > 100 Meters

- Automatic Polarity Correction

- Link Integrity Test Disable, Selectable Coded Link Pulse for AutoDUPLEX Mode

- Low differential and common mode noise on TP transmit outputs.

- Differential Transmit Drivers to support 50 Meters of AUI Cable Lengths.

- Direct AUI interface to the Manchester Code Converter.

MCC and AutoDUPLEX are trademarks of SEEQ Technology, Inc.

Note: Check for latest Data Sheet revision before starting any designs.

SEEQ Data Sheets are now on the Web, access SEEQ Home Page www.seeq.com

- or -

LSI Logic at www.lsilogic.com

## General Description

The SEEQ 80C24 is a CMOS single chip Ethernet serial interface adapter with a completely integrated Manchester Code Converter (MCC), AUI & 10Base-T transceiver with wave shaping & filters eliminating the need for external filters. The 80C24 is designed to interface directly with SEEQ's family of Ethernet data link controllers- 8003, 80C03, 8005, 80C04, Intel, AMD & National's controllers. The chip provides automatic polarity correction, automatic port selection, support for cables longer than 100m, UTP/ STP cable selection, power down mode, separate analog & digital ground pins & a link disable feature. It also provides a selectable coded link pulse to implement AutoDUPLEX function together with SEEQ's 80C03, 80C04 & NCORE controllers allowing seamless full duplex operation in switched network implementations doubling network bandwidth to 20 Mbps in 10Base-T. The 80C24 is typically suitable for adapter boards, motherboards and stand-alone TP transceiver designs & switching hubs.

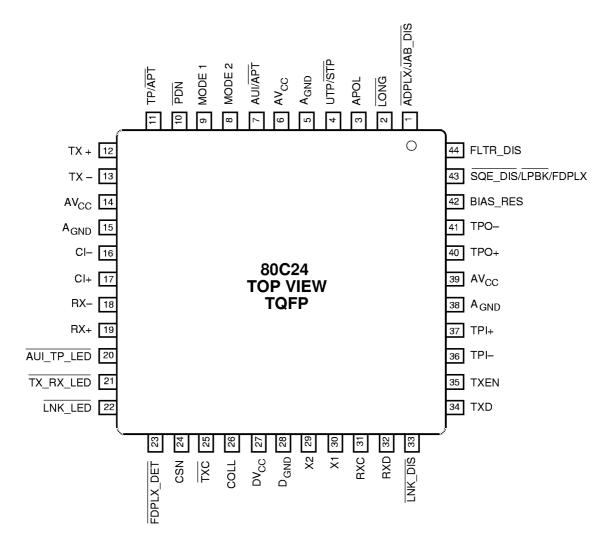

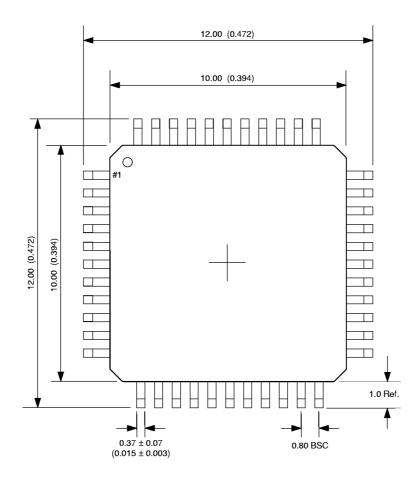

Note: Refer to Appendix B for the Thin Quad Flat Package (TQFP).

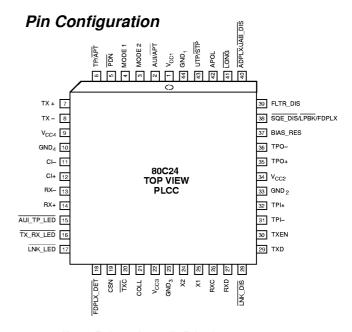

## 80C24 Pin Description

| Pin | Name             | I/O                              | Description                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----|------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | V <sub>CC1</sub> | _                                | Power supply pin. $+5V \pm 5\%$ .                                                                                                                                                                                                                                                                            |  |  |  |  |

| 2   | AUI/APT          | Input<br>Pulldown <sup>[1]</sup> | AUI Port/autoport select input.  AUI/APT TP/APT  0 0 Automatic port selection enabled when LNK_DIS=1  0 1 TP port selected  1 0 AUI port selected                                                                                                                                                            |  |  |  |  |

|     |                  |                                  | 1 1 Invalid                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 3,4 | MODE2,<br>MODE1  | Inputs<br>Pulldown               | Controller interface mode select input. These pins select one of four possible controller interfaces.  Controller MODE2 MODE1 SEEQ 0 0 NSC 0 1 INTEL 1 0 AMD 1 1                                                                                                                                             |  |  |  |  |

| 5   | PDN              | Input<br>Pulldown                | Powerdown input. When $\overline{PDN} = 0$ , all functions are disabled and power consumption is reduced to a minimum.                                                                                                                                                                                       |  |  |  |  |

| 6   | TP/APT           | Input<br>Pullup <sup>[2]</sup>   | TP Port/autoport select input. See AUI/APT.                                                                                                                                                                                                                                                                  |  |  |  |  |

| 7   | TX+              | Output                           | AUI transmit output, positive.                                                                                                                                                                                                                                                                               |  |  |  |  |

| 8   | TX-              | Output                           | AUI transmit output, negative.                                                                                                                                                                                                                                                                               |  |  |  |  |

| 9   | V <sub>CC4</sub> | _                                | Power supply pin. +5V ±5%.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 10  | GND₄             |                                  | Ground pin.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 11  | CI–              | Input                            | AUI collision input, negative.                                                                                                                                                                                                                                                                               |  |  |  |  |

| 12  | CI+              | Input                            | AUI collision input, positive.                                                                                                                                                                                                                                                                               |  |  |  |  |

| 13  | RX-              | Input                            | AUI receive input, negative.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 14  | RX+              | Input                            | AUI receive input, positive.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 15  | AUI_TP_LED       | Output                           | Port select indication output. This pin is an open drain output and is capable of driving an LED from V <sub>CC</sub> . This pin also indicates reverse polarity on the twisted pair inputs by blinking on and off when the polarity is reversed.  AUI_TP_LED = High Z AUI port selected.  TP port selected. |  |  |  |  |

| 16  | TX_RX_LED        | Output                           | Transmit and receive activity output. This output goes low and stays low for a minimum of 0.2 sec, when there is packet transmission or reception on the TP or AUI port. This pin is an open drain output and is capable of driving an LED from V <sub>cc</sub> .                                            |  |  |  |  |

$<sup>\</sup>label{eq:continuous} \textbf{[1] Pulldown indicates that the pin is pulled down internally so that the default state is low.}$

<sup>[2]</sup> Pullup indicates that the pin is internally pulled up so that the default state is high.

# Pin Description cont'd

| Pin | Name             | I/O             | Description                                                                                                                                                                                        |  |  |  |  |

|-----|------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 17  | LNK_LED          | Output          | Link pulse detect output. When $\overline{LNK\_LED} = 0$ , link pulse is detected on twisted pair receive input. This pin is an open drain output and is capable of driving an LED from $V_{cc}$ . |  |  |  |  |

| 18  | FDPLX_DET        | Output          | Full duplex detect output. When FDPLX_DET = 0, the device has been placed in the full duplex mode by either selection or the AutoDUPLEX feature.                                                   |  |  |  |  |

| 19  | CSN              | Output          | Carrier sense output. This controller interface output indicates valid data and collisions on the receive TP or AUI inputs.                                                                        |  |  |  |  |

| 20  | TXC              | Output          | Transmit clock output. This controller interface output provides a 10MHZ clock to the controller. Transmit data from the controller on TXD is clocked in on edges of $\overline{TXC}$ .            |  |  |  |  |

| 21  | COLL             | Output          | Collision output. This controller interface output is asserted when collision between transmit and receive data is occuring, and during SQE test.                                                  |  |  |  |  |

| 22  | V <sub>CC3</sub> | _               | Power supply pin. $+5V \pm 5\%$ .                                                                                                                                                                  |  |  |  |  |

| 23  | GND₃             | _               | Ground pin.                                                                                                                                                                                        |  |  |  |  |

| 24  | X2               | Output          | Crystal oscillator output. The master clock for the device is generated by either placing a crystal between X1 and X2, or by applying an external clock to X1.                                     |  |  |  |  |

| 25  | X1               | Input           | Crystal oscillator input. The master clock for the device is generated by either placing a crystal between X1 and X2, or by applying an external clock to X1.                                      |  |  |  |  |

| 26  | RXC              | Output          | Receive clock output. This controller interface output provides a 10MHZ clock to the controller. Receive data on RXD is clocked out on edges of RXC.                                               |  |  |  |  |

| 27  | RXD              | Output          | Receive data output. This controller interface output contains receive data decoded from the receive TP/AUI inputs and is clocked out on edges of RXC.                                             |  |  |  |  |

| 28  | LNK_DIS          | Input<br>Pullup | Link disable input. When LNK_DIS = 0, link pulse functions are disabled; that is, no link pulses are transmitted on TP outputs, link pulse detection on receive TP inputs ignored.                 |  |  |  |  |

| 29  | TXD              | Input           | Transmit data input. This controller interface input contains data to be transmitted on either TP or AUI transmit outputs and is clocked in on edges of TXC.                                       |  |  |  |  |

| 30  | TXEN             | Input           | Transmit enable input. This controller interface input has to be asserted when data on TXD is valid.                                                                                               |  |  |  |  |

| 31  | TPI –            | Input           | Twisted pair receive input, negative.                                                                                                                                                              |  |  |  |  |

| 32  | TPI+             | Input           | Twisted pair receive input, positive.                                                                                                                                                              |  |  |  |  |

| 33  | GND <sub>2</sub> | _               | Ground pin.                                                                                                                                                                                        |  |  |  |  |

| 34  | V <sub>CC2</sub> | _               | Power supply pin. $+5V \pm 5\%$ .                                                                                                                                                                  |  |  |  |  |

# Pin Description cont'd

| Pin | Name                       | I/O               | Description                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-----|----------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 35  | TPO+                       | Output            | Twisted pair transmit output, positive.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 36  | TPO-                       | Output            | Twisted pair transmit output, negative.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 37  | BIAS_RES                   | Output            | Bias resistor set. A resistor tied between this pin and $A_{\mbox{\tiny GND}}$ sets the twisted pair transmit peak output current level on TPO $\pm$ .                                                                                                                                                                                  |  |  |  |  |

| 38  | SQE_DIS/<br>LPBK/<br>FDPLX | Input<br>Pullup   | SQE disable/loopback/full duplex enable input. This pin has three distinct functions. The pin is configured as one of the first two functions, SQE_DIS and LPBK, depending on whether TP or AUI port is selected.                                                                                                                       |  |  |  |  |

|     |                            |                   | IF TP PORT IS SELECTED AND LNK_DIS = 1                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|     |                            |                   | SQE_DIS = 1 SQE test enabled<br>= 0 SQE test disabled                                                                                                                                                                                                                                                                                   |  |  |  |  |

|     |                            |                   | IF AUI PORT IS SELECTED AND LNK_DIS = 0  LPBK = 1 Loopback disabled = 0 Loopback enabled                                                                                                                                                                                                                                                |  |  |  |  |

|     |                            |                   | This pin can be configured as the third function, FDPLX, by setting AUI/APT = 0, TP/APT = 0. LNK_DIS = 0, FDPLX = 1. This pin combination forces the device into the full duplex mode. It is important to note that the link pulses will be present even though the LNK_DIS pin is held low. This happens only in this particular mode. |  |  |  |  |

| 39  | FLTR_DIS                   | Input<br>Pulldown | Filter disable input. When FLTR_DIS=1, the internal transmit and receive filters are disabled.                                                                                                                                                                                                                                          |  |  |  |  |

| 40  | ADPLX/<br>JAB_DIS          | Input<br>Pullup   | Autoduplex enable/jabber disable input. This pin changes function depending on whether TP or AUI port is selected.                                                                                                                                                                                                                      |  |  |  |  |

|     |                            |                   | IF TP PORT IS SELECTED AND LNK_DIS = 1 ADPLX = 1 Half duplex selected = 0 Autoduplex on                                                                                                                                                                                                                                                 |  |  |  |  |

|     |                            |                   | IF AUI PORT IS SELECTED AND LNK_DIS = 0  JAB_DIS = 1 Jabber enabled = 0 Jabber disabled                                                                                                                                                                                                                                                 |  |  |  |  |

| 41  | LONG                       | Input<br>Pullup   | Long cable mode input. When LONG = 0, the receive input thresholds are reduced to accomodate cable lengths in excess of 100 meters.                                                                                                                                                                                                     |  |  |  |  |

| 42  | APOL                       | Input<br>Pulldown | Autopolarity input. When APOL = 1, this pin enables the autopolarity function and automatically corrects for reversed polarity on the twisted pair receive inputs, TPI±.                                                                                                                                                                |  |  |  |  |

| 43  | UTP/STP                    | Input<br>Pullup   | Cable type select input. This pin adjusts the twisted pair transmit output current level to accomodate either 100 ohm (UTP) or 150 ohm (STP) cable.  UTP/STP = 1 100 ohm cable (UTP) = 0 150 ohm cable (STP)                                                                                                                            |  |  |  |  |

| 44  | GND₁                       | _                 | Ground pin.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

## **BLOCK DESCRIPTION**

## Functional Description

The 80C24 is an Ethernet adapter with a completely integrated Manchester Code Converter, 10Base-T transceiver with on chip filters. The device contains both 10Base-T and AUI interfaces compliant with IEEE 802.3 specifications. The chip is divided into four major blocks, namely (i) The controller interface (ii) The Encoder / Decoder (iii) The twisted pair interface and (iv) The AUI. The input signals are received on the TP or AUI receivers depending on which is selected. Both the twisted pair and AUI receivers contain a threshold comparator to validate the signal and a zero crossing comparator for checking the transitions. Then the data is sent to the PLL in the decoder to separate the data from the clock. On the other side, digital transmit data is clocked into the device via the controller interface. The data is then sent to the Manchester encoder to be encoded. Encoded data is then transmitted on the twisted pair or AUI based on the selected port.

#### The Controller Interface

The 80C24 is designed to interface directly to SEEQ's 80C03, 80C04 & NCORE controllers, INTEL's 82586/596/ 592/593 LAN controllers, NSC and AMD's controllers with the use of MODE1 & MODE2 pins. The controller interface consists of the Transmit/Receive data (TXD/RXD), transmit/receive Clocks (TXC/RXC), the Transmit Enable (TXEN) input, the collision output (COLL), the Full Duplex acknowledgment (FDPLX\_DET) and the Carrier Sense Output (CSN) pins. On the transmit side, data on TXD is clocked into the device on the edges of TXC clock output only when the data valid signal (TXEN) is asserted. On the receive side, data on RXD is clocked out on edges of RXC. In the SEEQ, NSC and AMD modes, RXC follows TXC for 2.2 μs in the TP mode or 1.8 μs in the AUI mode and then switches to the recovered clock. In the Intel mode, RXC is held low for 2.2 μs in the TP mode or 1.8 μs in the AUI mode while the PLL is acquiring lock and then switches to the recovered lock. The FDPLX DET pin signifies to the controller that full duplex channels have been established.

The following mode table illustrates the selection of the appropriate inputs to match the controller.

| MODE 2 | MODE 1 | Controller |

|--------|--------|------------|

| 0      | 0      | SEEQ       |

| 0      | 1      | NSC        |

| 1      | 0      | INTEL      |

| 1      | 1      | AMD        |

## The Encoder/Decoder

Manchester encoding is a process of combining the clock & the data stream together so that they can be transmitted on the twisted pair interface or AUI at the transceiver side. Once encoded, the first half contains the complement of the data and the second half contains the true data, so that a transition is always guaranteed at the middle of a bit cell. Data encoding and transmission begins with TXEN going active, and the subsequent data is clocked on the edges of TXC and then gets encoded. The end of a transmit packet occurs at a bit cell center if the last bit is a "ONE" or at a bit boundary if the last bit is a "ZERO".

The decoding is a process of recovering the encoded data stream coming from the receiver side and decoding it back into the clock and data outputs using the phase locked loop technique. The PLL is designed to lock into the preamble of the incoming signal at less than 20 bit times with a maximum jitter of  $\pm 13.5$  ns at the TPI or AUI inputs and can also sample the incoming data with this amount of jitter. The ENDEC asserts the CSN signal to indicate to the controller that the data and clock received are valid and available. There is an inhibit period after the end of a frame after a node has finished transmitting for 4.4  $\mu$ s during which CSN is deasserted irregardless of the state of the receiver and collision status.

## Twisted Pair Interface

#### (a) The transmitter function

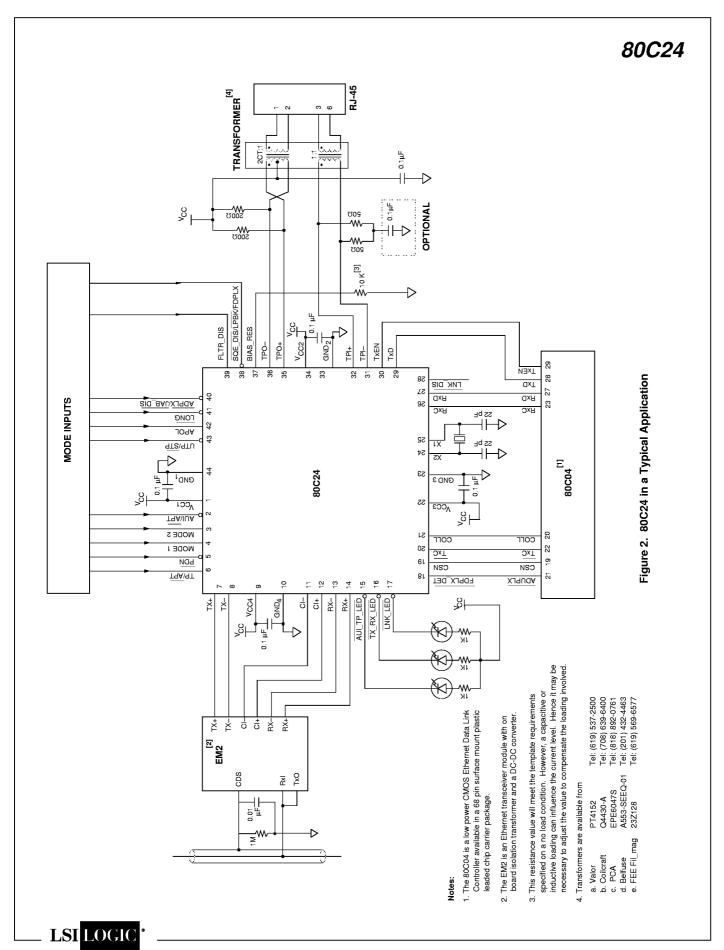

The transmitter transfers Manchester encoded data from the ENDEC to the twisted pair cable. The circuit consists of a set of functional blocks to provide pre-coded waveshaped, pre-equalized and smoothed waveforms so that the outputs are made to appear as though it had passed through a 5-7th order external elliptic passive filter, thereby eliminating the need for an external filter. The waveform generator consists of a ROM, DAC, PLL, filter and a output driver to preshape the output waveform transmitted onto the twisted pair cable to meet the pulse template requirements outlined in IEEE STD 802.3 and illustrated in figure 12. The DAC first converts the data pulse into a stair stepped representation of the desired output waveform, which goes through a second order low-pass filter. The DAC values are determined from the ROM addresses. which are chosen to have different values for long and short data bits so as to shape the pulse to meet the 10Base-T waveform template. The line driver takes the smoothed current waveform and converts it into an high current output that can drive the TP directly without any external filters. The current output is also guaranteed to have a very low common mode and differential noise. The interface to the twisted pair cable requires a transformer

## 80C24 TPO 전 - TP∔ -TP-LP FILTER Ϋ́ <del>Х</del> Х ¥ 다 I 다 다 LP FILTER AUI INTERFACE POLARITY DETECT SQUELCH LINK PULSE DETECT PORT DETECT DAC AUI SQUELCH PORT DETECT CLOCK ROM SOI EN SEN Figure 1. 80C24 Block Diagram TP INTERFACE JABBER DETECT COLLISION DATA RCV DATA **▼** MCLK COLLISION DETECT MANCH ENCODER MANCH DECODER (PLL) MODE OUTPUTS ENDEC LED DRIVERS MODE INPUTS osc CONTROLLER INTERFACE MODE 1 — ADPLX/JAB\_DIS — LONG — UTP/STP — FLTR\_DIS — SQE\_DIS/LPBK/FDPLX — APOL – LNK\_DIS – PDN – LNK\_LED — TX\_RX\_LED — AUI\_TP\_LED — AUI/<u>APT</u> — TP/<u>APT</u> — MODE 2 — ₹ Q RXC SN A TXEN FDPLX\_DET ▼ HOO ĮŽ. LSI LOGIC

with a ratio of 2:1 on transmit and a 1:1 on receive, with two 200 ohm resistors connected as shown in figure 2. The output driver is a current source. The output current level is set by the values of the resistor tied between the BIAS\_RES (Pin 37) & GND. The current level is determined by the following equation.

$$I_{OUT} = (R_{BIAS} RES^{/10K})^* 50 mA$$

Though a 10K resistor will meet the template requirements specified with a no load condition, a capacitive or inductive loading can influence the level, because the transmitter has a current source output. So, in a actual application, it might be necessary to adjust the value to compensate the loading involved. For example, the bias resistance value for a loading of 10 pf will be 8K approximately.

#### (b) The receiver function

The receiver receives the Manchester-encoded data from the twisted pair lines( TPI±) and passes it on to the ENDEC side, where it gets decoded back into the receive clock RXC and the receive data RXD. The inputs first goes through a receive filter, which is a continuous time 3rd order low pass filter with a typical 3 dB cutoff frequency of 20-25 Mhz. The filter's output then passes through two different types of comparators, namely threshold and zero crossing. The threshold comparator compares the TPI± inputs with fixed positive and negative thresholds called the squelch levels. The zero crossing comparator senses the transition point on the TPI± inputs without introducing excess jitter and the outputs goes to the PLL in the decoder. The receiver is transformer coupled and needs to be terminated with a  $100\Omega$  resistor or two  $50\Omega$  resistor and a capacitor as described in figure 2.

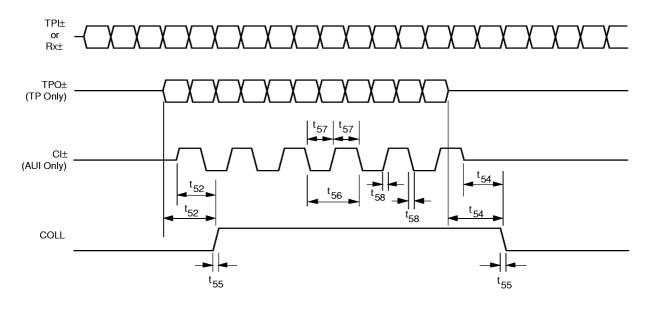

#### (c) Full Duplex Functions

The Full Duplex scheme allows the simultaneous transmission on the  $TPO\pm$  and simultaneous reception on the  $TPI\pm$  without interruption, effectively doubling the bandwidth to 20 MBPS in switched network implementations on 10Base-T. The 80C24 can be made to operate either in the AutoDUPLEX or in the Forced FullDuplex scheme.

The 80C24 is switched on to the AutoDUPLEX mode when an active LOW signal is detected on the  $\overline{ADPLX/JAB\_DIS}$  (pin 40) in the  $\overline{TP}$  mode. In this configuration, Full duplex mode is automatically established by the successful detection of double pulses embedded within the regular link pulses. The 80C24 sends the double pulses in 16 pulse intervals constantly on the  $\overline{TPO\pm}$  pins and continually monitors the  $\overline{TPI\pm}$  pins for similar type of double pulses within a time window of  $210\pm6$ ms. Once the double pulses are detected, the  $\overline{FDPLX\_DET}$  (Pin 18) will go low to acknowledge to the controller that the network will allow

simultaneous transmission and reception on the TP port. The maximum distance between two consecutive pulses in a double pulse is  $5.4 \mu s$ .

The Forced Full-Duplex mode can be established by the following pin combinations.

1.

$$AUI/\overline{APT}$$

(pin 2) = 0,  $TP/\overline{APT}$  (pin 6) = 0; Sets 80C24 in Autoport.

3.

$$\overline{SQE\_DIS}/\overline{LPBK}/FDPLX = 1$$

Forces the 80C24 into FullDuplex.

In this combination, forced full duplex is effectively established and Collision, SQE & the LoopBack functions are disabled.

#### (d) Squelch functions

The squelch function is used to discriminate noise from link test pulses and valid data to prevent the noise from activating the receiver. It is accomplished by a squelch comparator which compares the TPI± signals with a fixed positive and negative squelch value. The output from the comparator goes to a receive squelch circuit which determines whether the input data is valid or not. If the data is invalid, the transceiver enters into an squelched state. The input voltage should exceed ±300mV p-p for five bit times max. (with alternating polarity) for unsquelching to occur. In the Unsquelch state, the value of the threshold in the comparator is reduced to take care of hysteresis effects. While in the unsquelch state, the receive squelch circuit looks for the SOI (Start of Idle) signal at the end of the packet. When the SOI signal is detected, the receive squelch is turned on again.

#### (e) The Link integrity functions

The 80C24 monitors the TPI± pins continuously for valid data and link pulse activity. If neither data or link test pulse is detected for a minimum time, the transceiver enters into a Link Test Fail State and disables the transmitter, receiver, collision presence and the SQE functions. For the transceiver to exit this state, it should receive three consecutive link pulses or valid data at the TPI± inputs to resume normal packet transmission and reception. On the other hand, the transmitter generates link pulses periodically when it's not transmitting data to indicate to the network that the link is intact. Please refer to figure 14 for the diagram illustrating the Transmit Link Pulse Voltage Template as specified in the IEEE 802.3. The Link function could be disabled by providing an active low input to pin 28 (LNK DIS). In this mode, link pulses are neither transmitted nor received. A link pulse detect output capable of driving a LED is also provided for link indication.

#### (f) The Start of Idle (SOI) pulse

The transmit SOI pulse is a positive pulse inserted at the end of every transmission to signal the end and the start of idle period to corresponding receivers. The output pulse is also shaped by the transmit waveshaper to meet the pulse requirements specified in IEEE 802.3. Please refer to figure 13 for the Transmit Start Of Idle Pulse voltage template diagram. The receiver detects the SOI pulse by sensing the missing data transitions with the zero crossing comparator. Once the SOI pulse is detected, another SOI pulse is generated and sent to the Controller interface outputs.

## (g) Automatic Polarity Correction

The 80C24 provides autopolarity detection and correction functions for the twisted pair receiver peak detectors to determine whether normal or inverted data is received over the TPI± pins. Automatic polarity is enabled by making APOL (Pin 42) HIGH. The polarity reversal can be indicated by connecting a LED to the AUI\_TP\_LED pin, which would blink when a reversal is observed. A polarity reversed condition is sensed when four opposite link pulses are detected without the expected polarity or if 3-4 frames are received with a reversed start-of-idle.

#### (h) Jabber functions

The jabber function detects abnormally long streams of Manchester-encoded data on the TXD input with the help of a Jabber detect circuit. The jabber circuit uses a Jabber timer, which monitors the TXEN pin. It starts counting at the beginning of each transmission. If the timer expires before TXEN goes inactive, the 80C24 enters a jabber state disabling the transmit/loopback functions and enabling the collision functions. If TXEN goes inactive before the timer expires, the timer is reset and becomes ready for the next transmission. The jabber function can be disabled in the AUI mode by applying an active low signal to the ADPLX/JAB\_DIS (pin 40). The jabber function can also be disabled in TP mode for certain pin combinations described in Appendix A.

#### (i) Loopback functions

Loopback in the TP mode is internally enabled when Manchester encoded data is transmitted on TPO± and no data is received on the TPI± in order to simulate Coax Ethernet behavior. When internal loopback is enabled, the transmitted data is loopbacked into the RXD and sent to the controller. The loopback function is disabled during Link Fail State, Jabber State and during Full-Duplex Operation.

In the AUI mode, internal loopback function can be forcefully enabled by applying an active low to  $\overline{SQE\_DIS/LPBK/FDPLX}$  (pin 38) and the transmit data can be loopbacked for diagnostic purposes.

#### (j) Long mode

The 80C24 can be made to support longer cable lengths (> 100 meters) by applying an active LOW signal to the LONG (pin 41) pin. When this pin is LOW, the threshold levels of the internal threshold comparators are lowered to accommodate the longer cable length. In normal mode, it supports a cable with 11.5dB of attenuation and in the LONG mode an additional 4dB of attenuation is supported.

#### (k) Cable mode

The UTP/STP pin can be used to configure the 80C24 to be used with a selectable termination impedance of 100 ohms or 150 ohms for use with either UTP or STP cable types respectively. The STP mode is selected by tying this pin LOW. When tied LOW, the output current is reduced so as to keep the amplitude of the transmit signal unchanged from the template when the STP cable is attached.

#### (I) Signal Quality Error Test

The Signal Quality Error test is used to indicate a successful transmission (i,e A transmission without interruptions such as Collision, jabber or Link failure) to the DTE. When the SQE is enabled, a COLL signal is presented to the controller when the transmitter goes idle after a successful transmission of a frame on the twisted pair network. The Signal Quality Error test can be disabled by applying an active low to SQE\_DIS/LPBK/FDPLX (pin 38) since it becomes necessary to disable SQE tests for applications such as repeaters. When this pin is tied low, only the SQE functions are disabled and the normal collision detection functionality is left unchanged during regular transceiver operations. The maximum duration of the SQE test is 850 ns and the maximum SQE test wait delay is 700ns.

#### AUI Interface

The differential transmit output pair TX+/TX- sends the encoded data on to an external transceiver and is capable of driving 50 meters of 780hm shielded AUI cable directly with a jitter of 0.5 ns max. The receive input differential pair RX+/RX- goes through the AUI squelch comparator and the zero crossing comparator. The AUI squelch comparator compares the input signals with fixed minimum and maximum values of -175mv and -325mv respectively, and passes it on to the squelch circuit to determine data validity. The zero crossing comparator senses the transition point of the input pair without introducing excess jitter and passes the data to the phase locked loop of the decoder. The CI+/CI- are the collision input pair signals which would expect a 5 Mhz or a 10 Mhz square wave from an external transceiver.

## **Collisions**

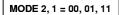

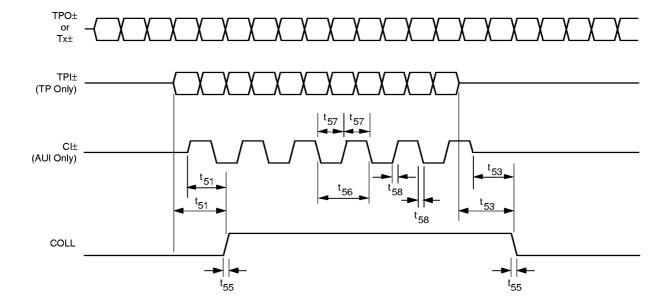

Collisions are generated when two stations try to contend for the network at the same time, which would result in simultaneous activity detected on the TPO± and TPI±. When this happens, COLL will be asserted to indicate to the controller the simultaneous transmission of two or more stations on the network. CSN is also asserted during collision. For further details, about timing, refer to figures 7 and 8.

#### Oscillator

The internal clock generator is controlled either by an external parallel resonant crystal connected across the X1 & X2 or by connecting an clock to the input pin X1. This external 20 Mhz clock is used by the clock circuitry and the PLL to generate a 10 Mhz  $\pm$  0.01% transmit clock. The manchester encoding process uses both the 10Mhz and 20Mhz clocks.

Crystal Specification:

- 1. Parallel resonant mode

- 2. Frequency ........... 20 MHz ±0.01% @ 0 70°C

- 3. Equivalent Series Resistance ........... 25  $\Omega$  max.

- 4. Load Capacitance ...... 20 pf max.

- 5. Case Capacitance ...... 7 pf max.

#### Automatic Port Selection

The automatic port selection feature of the 80C24 can be enabled by applying active low inputs to the  $AUI/\overline{APT}$  (pin 2) &  $TP/\overline{APT}$  (pin 6) respectively. In this mode, 80C24 automatically selects either the TP or AUI port by detecting the presence or absence of activity on the  $TPI\pm$  and  $RX\pm$  respectively. In the Autoport mode, the device powers up with the TP port active. If no activity is detected for a period of 800 ms on the TP port, the device automatically switches to AUI mode. The device will stay in AUI mode as long as no activity is detected on the TP port. Note that activity is defined as the presence of either link pulses or packets.

### Powerdown

The 80C24 can be made to go into a low power mode by applying an active low signal to PDN (pin 5). In this mode, all the functions in the device are disabled and the power consumption is reduced to a bare minimum of 0.5 mA or less.

## **Power Supply Decoupling**

There are four sets of  $V_{cc}$ /GND on the 80C24:  $(V_{cc1}$ /GND<sub>1</sub>,  $VCC_2$ /GND<sub>2</sub>,  $VCC_3$ /GND<sub>3</sub>, and  $VCC_4$ /GND<sub>4</sub>.

All  $V_{cc}$ 's should be connected together as close as possible to the device with a large  $V_{cc}$  plane. If the  $V_{cc}$ 's vary in potential by even a small amount, noise and latchup can result

All GND's should also be connected together as close as possible to the device with a large ground plane. If the GND's vary in potential by even a small amount, noise and latchup can result.

A 0.01-0.1  $\mu$ F decoupling capacitor should be connected between each  $V_{cc}$ /GND set as close as possible to the device pins, preferably within 0.5". The value of the decoupling capacitor should be selected based on whether the noise on  $V_{cc}$ -GND is high or low frequency. A conservative approach would be to use two decoupling capacitors on each  $V_{cc}$ /GND set, one 0.1 $\mu$ F for low frequency and one 0.001  $\mu$ F for high frequency noise on the power supply.

The  $V_{cc}$  connection to the transmit transformer center tap shown in Figure 2 has to be well decoupled in order to minimize common mode noise injection from  $V_{cc}$  onto the TP wires. It is recommended that a 0.01  $\mu$ F decoupling capacitor be placed between the center tap  $V_{cc}$  to the 80C24 GND plane. This decoupling capacitor should be physically placed within 0.5" of the transformer center tap.

The PCB layout and power supply decoupling discussed above should provide sufficient decoupling to acheive the following when measured at the device: (1) the resultant AC noise voltage measured across each  $V_{cc}$ /GND set should be less than 100 mV $_{pp}$ , (2) all  $V_{cc}$ 's should be within 50 m  $V_{pp}$  of each other, and (3) all GND's should be within 50m  $V_{pp}$  of each other.

## Absolute Maximum Ratings

| V <sub>cc</sub> Supply Voltage | –0.3V to 7V   |

|--------------------------------|---------------|

| All Inputs and Outputs         |               |

| Latchup Current                |               |

| Package Power Dissipation      | 1 Watt @ 25°C |

| Storage Temperature            | –65 to +150°C |

| Operating Temperature          | 65 to +125°C  |

| Lead Temperature (Soldering, 1 | 0 sec)250°C   |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Power Supply Characteristics**

Test conditions are as follows:

- 1.  $T = 0 70^{\circ}C$

- 2.  $V_{cc} = 5V \pm 5\%$

- 3. 20 MHZ ±.01%

- 4. BIAS\_RES = 10K, with no load.

|                 |                              |     | Limit |     |      |                            |

|-----------------|------------------------------|-----|-------|-----|------|----------------------------|

| Sym.            | Parameter                    | Min | Тур   | Max | Unit | Conditions                 |

| I <sub>cc</sub> | V <sub>cc</sub> Power Supply |     | 110   | 150 | mA   | Transmitting, TP selected  |

|                 | Current                      |     | 85    | 110 | mA   | Transmitting, AUI selected |

|                 |                              |     |       | 0.5 | mA   | Powerdown                  |

## DC Digital I/O Characteristics

Test conditions are as follows:

- 1.  $T = 0 70^{\circ}C$

- 2.  $V_{CC} = 5V \pm 5\%$ 3. 20 MHZ  $\pm .01\%$

- 4. BIAS\_RES = 10K, with no load.

|                 |                    |     | Limit |      |      |                                   |

|-----------------|--------------------|-----|-------|------|------|-----------------------------------|

| Sym.            | Parameter          | Min | Тур   | Max  | Unit | Conditions                        |

| V <sub>IL</sub> | Input Low Voltage  |     |       | 0.8  | Volt | All except X1                     |

|                 |                    |     |       | 1.5  | Volt | X1                                |

| V <sub>IH</sub> | Input High Voltage | 2   |       |      | Volt | All except X1                     |

|                 |                    | 3.5 |       |      | Volt | X1                                |

| I <sub>IH</sub> | Input High Current |     |       | 1    | μА   | V <sub>IN</sub> = V <sub>CC</sub> |

|                 |                    |     |       |      |      | X1                                |

|                 |                    | 20  | 60    | 120  | μА   | V <sub>IN</sub> = V <sub>CC</sub> |

|                 |                    |     |       |      |      | AUI/APT, MODE1-2, PDN,            |

|                 |                    |     |       |      |      | FLTR_DIS, APOL                    |

| I <sub>IL</sub> | Input Low Current  |     |       | -1   | μА   | V <sub>IN</sub> = GND             |

|                 |                    |     |       |      |      | X1                                |

|                 |                    | -20 | -60   | -120 | μА   | V <sub>IN</sub> = GND             |

|                 |                    |     |       |      |      | LNK_DIS, SQE_DIS/LPBK/FDPLX       |

|                 |                    |     |       |      |      | ADPLX/JAB DIS, LONG,              |

|                 |                    |     |       |      |      | UTP/STP, TP/APT                   |

# DC Digital I/O Characteristics cont'd

|                        |                        | Parameter Min Typ Max |   |     |      |                                                                                                                               |

|------------------------|------------------------|-----------------------|---|-----|------|-------------------------------------------------------------------------------------------------------------------------------|

| Sym.                   | Parameter              |                       |   | Max | Unit | Conditions                                                                                                                    |

| <b>V</b> <sub>OL</sub> | Output Low Voltage     |                       |   | 0.4 | Volt | I <sub>oL</sub> = 2.1 mA All except AUI_TP_LED, TX_RX_LED, LNK_LED                                                            |

|                        |                        |                       |   | 1.2 | Volt | I <sub>oL</sub> = -20mA<br>AUI_TP_LED, TX_RX_LED,<br>LNK_LED                                                                  |

| V <sub>OH</sub>        | Output High Voltage    |                       |   | 4   | Volt | I <sub>OH</sub> = -400μA<br>All except AUI_TP_LED,<br>TX_RX_LED, LNK_LED                                                      |

| l <sub>oz</sub>        | Output Leakage Current |                       |   | -1  | μА   | $V_{\text{OH}} = V_{\text{CC}}$ $\overline{\text{AUI\_TP\_LED}}, \overline{\text{TX\_RX\_LED}},$ $\overline{\text{LNK\_LED}}$ |

| C <sub>IN</sub>        | Input Capacitance      |                       | 5 |     | pF   |                                                                                                                               |

| C <sub>OUT</sub>       | Output Capacitance     |                       | 5 |     | pF   |                                                                                                                               |

## Twisted Pair Interface Characteristics

Unless otherwise specified, all test conditions are as follows:

- 1. T = 0-70°C 2.  $V_{CC}$  = 5V ±5% 3. 20MHZ ±.01%

- 4. BIAS\_RES = 10K, with no load.

- 5. TPO± loading as shown in Figure 2 or equivalent.

- 6. 10Mhz sine wave on TPI±

|      |                                              |                           | Limit              |                           |       |                                                  |

|------|----------------------------------------------|---------------------------|--------------------|---------------------------|-------|--------------------------------------------------|

| Sym. | Parameter                                    | Min                       | Тур                | Max                       | Unit  | Conditions                                       |

| TOV  | TPO± Differential Output<br>Voltage          | 2.2                       | 2.5                | 2.8                       | Vpk   |                                                  |

| TOVT | TPO± Differential Output<br>Voltage Template | S                         | ee Figure          | 12                        |       |                                                  |

| TSOI | TPO± SOI Output<br>Voltage Template          | S                         | ee Figure          | 13                        |       |                                                  |

| TLPT | TPO± Link Pulse Output<br>Voltage Template   | S                         | ee Figure          | 14                        |       |                                                  |

| TOIV | TPO± Differential Output Idle Voltage        |                           |                    | ±50                       | mV    | Measured on Secondary<br>Side of XFMR in Fig. 2  |

| TOIA | TPO± Output Current                          | 44                        | 50                 | 56                        | mA pk | UTP cable mode                                   |

|      |                                              | 29                        | 33                 | 37                        | mA pk | STP cable mode                                   |

| TOIR | TPO± Output Current<br>Adjustment Range      | 0.70                      |                    | 1.40                      |       | V <sub>cc</sub> = 5V Adjustable<br>with BIAS_RES |

| TCMA | TPO± Common Mode<br>AC Output Voltage        |                           | 10                 | 50                        | mV pk | Relative to Value<br>at BIAS_RES = 10K           |

| THD  | TPO± Harmonic<br>Distortion                  |                           |                    | <b>–2</b> 7               | dB    |                                                  |

| TOR  | TPO± Output Resistance                       |                           | 10K                |                           | ohms  |                                                  |

| TOC  | TPO± Output<br>Capacitance                   |                           | 15                 |                           | pF    |                                                  |

| RST  | TPI± Squelch<br>Threshold                    | 310                       |                    | 540                       | mVpk  | LONG = 1                                         |

|      |                                              | 190                       |                    | 330                       | mVpk  | $\overline{LONG} = 0$                            |

| RUT  | TPI± Unsquelch<br>Threshold                  | 190                       |                    | 330                       | mVpk  | LONG = 1                                         |

|      | THESHOLD                                     | 115                       |                    | 200                       | mVpk  | LONG = 0                                         |

| RZT  | TPI± Zero Cross<br>Switching Threshold       |                           |                    | 20                        | mVpk  |                                                  |

| ROCV | TPI± Input Open Circuit<br>Voltage           | (V <sub>cc</sub> /3)-0.25 | V <sub>cc</sub> /3 | (V <sub>cc</sub> /3)+0.25 | Volt  |                                                  |

## Twisted Pair Interface Characteristics cont'd

|      |                                             |                        | Limit |                        |      |            |

|------|---------------------------------------------|------------------------|-------|------------------------|------|------------|

| Sym. | Parameter                                   | Min                    | Тур   | Max                    | Unit | Conditions |

| RCMR | TP⊞ Input Common<br>Mode Voltage Range      | V <sub>cc</sub> /3-1.0 |       | V <sub>cc</sub> /3+1.0 | Volt |            |

| RDR  | TPI+/- Input Differential Voltage Range     |                        |       | V <sub>cc</sub>        | Volt |            |

| RCRR | TPI+/- Input Common<br>Mode Rejection Ratio |                        |       | -20                    | dB   | 0-10Mhz    |

| RIR  | TPI+/- Input Resistance                     | 5K                     |       |                        | ohm  |            |

| RIC  | TPI+/- Input Capacitance                    |                        | 10    |                        | pF   |            |

## **AUI Characteristics**

Unless otherwise specified, all test conditions are as follows:

- 1.  $T = 0-70^{\circ}C$ 2.  $V_{CC} = 5V \pm 5\%$ 3. 20MHZ ±.01%

- 4. BIAS\_RES = 10K with no load.

- 5. 78 ohm, 27 $\mu$ H load on TX $\pm$

- 6. 10Mhz sine wave on RX $\pm$ , CI $\pm$

|      |                                                               |                          | Limit                |                          |       |                                  |

|------|---------------------------------------------------------------|--------------------------|----------------------|--------------------------|-------|----------------------------------|

| Sym. | Parameter                                                     | Min                      | Тур                  | Max                      | Unit  | Conditions                       |

| AOV  | TX±, Differential<br>Output Voltage                           | 550                      |                      | 1200                     | mVpk  |                                  |

| AORF | TX±, Output Rise<br>And Fall Time                             |                          |                      | 5                        | nS    | tR, tF measured at 10-90% points |

| AOIV | TX±, Differential<br>Output Idle Voltage                      |                          |                      | ±40                      | mV    |                                  |

| AOVU | TX±, Differential<br>Output Voltage<br>Undershoot During Idle |                          |                      | -100                     | mV    |                                  |

| AOCD | TX±, Common<br>Mode DC Output Voltage                         | V <sub>cc</sub> /3.5     | V <sub>cc</sub> /3.0 | V <sub>cc</sub> /2.1     | Volt  |                                  |

| AOCA | TX±, Common<br>Mode AC Output Voltage                         |                          |                      | 40                       | mV pk |                                  |

| AOR  | TX±, Output<br>Resistance                                     |                          |                      | 75                       | ohms  |                                  |

| AOC  | TX±, Output<br>Capacitance                                    |                          | 15                   |                          | pF    |                                  |

| AIST | RX±, CI± Squelch<br>Threshold                                 | -175                     |                      | -325                     | mV    |                                  |

| AIUT | RX±, CI± Unsquelch<br>Threshold                               | -100                     |                      | -225                     | mV    |                                  |

| AIZT | RX±, CI± Zero Cross<br>Switching Threshold                    |                          |                      | 20                       | mVpk  |                                  |

| AIOC | RX±, CI± Input Open Circuit<br>Voltage                        | (V <sub>cc</sub> /3)25   | V <sub>cc</sub> /3   | (V <sub>cc</sub> /3)+.25 | Volt  |                                  |

| AICR | RX±, CI± Input Common<br>Mode Voltage Range                   | (V <sub>cc</sub> /3)-1.0 |                      | (V <sub>cc</sub> /3)+1.0 | Volt  |                                  |

| AIVR | RX±, Cl± Input Differential<br>Voltage Range                  | 0                        |                      | V <sub>cc</sub>          | Volt  |                                  |

| AIR  | RX±, CI± Input Resistance                                     | 5K                       | 10K                  |                          | ohm   |                                  |

| AIC  | RX±, Cl± Input Capacitance                                    |                          | 10                   |                          | pF    |                                  |

## **AC Test Timing Conditions**

Unless otherwise specified, all test conditions for timing characteristics are as follows:

- 1.  $T = 0 70^{\circ}C$

- 2.  $V_{cc} = 5v \pm 5\%$

- 3. 20MHZ ±.01%

- 4. BIAS\_RES = 10K, with no load.

- 5. Input Conditions

All Inputs:  $t_{\rm R}$ ,  $t_{\rm F}$ < = 10ns from 20-80% points

6. Output Loading

TPO±: 50 ohms to V<sub>cc</sub> on each output, 10pF

TX±: 78 ohms differentially, 10pF

Open Drain Digital Outputs: 1K pullup, 50pF

All Other Digital Outputs: 50pF

7. Measurement Points

TPO±, TPI±, TX±, RX±, CI±: Zero crossing during data and ±.3V point at start/end of signal

X1:  $V_{cc}/2$  All other inputs and outputs: 1.5 Volts

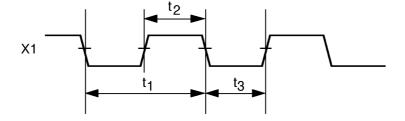

## 20 MHZ Input Clock Timing Characteristics

|                |               | Limit  |        |        |      |            |

|----------------|---------------|--------|--------|--------|------|------------|

| Sym.           | Parameter     | Min    | Тур    | Max    | Unit | Conditions |

| t,             | X1 Cycle Time | 49.995 | 50.005 | 50.005 | nS   |            |

| t <sub>2</sub> | X1 High Time  | 15     |        |        | nS   |            |

| t <sub>3</sub> | X1 Low Time   | 15     |        |        | nS   |            |

Refer to Figure 3 for timing diagram.

Figure 3. 20 MHZ Input Clock Timing

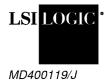

# Transmit Timing Characteristics

|                  |                                            | Limit |          |        |      |                                                       |

|------------------|--------------------------------------------|-------|----------|--------|------|-------------------------------------------------------|

| Sym.             | Parameter                                  | Min   | Тур      | Max    | Unit | Conditions                                            |

| t,,              | TXC Cycle Time                             | 99.99 | 100      | 100.01 | nS   |                                                       |

| t <sub>12</sub>  | TXC High Time                              | 40    |          | 60     | nS   |                                                       |

| t <sub>13</sub>  | TXC Low Time                               | 40    |          | 60     | nS   |                                                       |

| t <sub>14</sub>  | TXC Rise Time                              |       |          | 5      | nS   |                                                       |

| t <sub>15</sub>  | TXC Fall Time                              |       |          | 5      | nS   |                                                       |

| t <sub>16</sub>  | TXEN Setup Time                            | 30    |          |        | nS   |                                                       |

| t <sub>17</sub>  | TXEN Hold Time                             | 0     |          |        | nS   |                                                       |

| t <sub>18</sub>  | TXD Setup Time                             | 30    |          |        | nS   |                                                       |

| t <sub>19</sub>  | TXD Hold Time                              | 0     |          |        | nS   |                                                       |

| t <sub>20</sub>  | Transmit Bit Loss                          |       |          | 2      | Bits | TP and AUI                                            |

| t <sub>21</sub>  | Transmit Propagation<br>Delay              |       |          | 2      | Bits | TP and AUI                                            |

| t <sub>22</sub>  | Transmit Output Jitter                     |       |          | 8      | nS   | TP                                                    |

|                  |                                            |       |          | 0.5    |      |                                                       |

| t <sub>24</sub>  | Transmit Output Rise                       | Se    | e Figure | 12     | nS   | TP                                                    |

|                  | and Fall Time                              |       |          | 5      | nS   | AUI                                                   |

| t <sub>25A</sub> | Transmit SOI Pulse<br>Width to 0.3V Point  | 250   |          |        | nS   | TP<br>Measure TPO± from last                          |

|                  |                                            |       |          |        |      | zero cross to 0.3V point.                             |

|                  |                                            | 200   |          |        | nS   | AUI  Measure TX± from last zero  cross to 0.3V point. |

| t <sub>25B</sub> | Transmit SOI Pulse<br>Width to 40 mV Point |       |          | 4500   | nS   | TP Measure TPO± from last zero cross to 40mV point.   |

|                  |                                            |       |          | 7000   | nS   | AUI Measure TX± from last zero cross to 40 mV point.  |

| t <sub>26</sub>  | TXEN assert to TX_RX_LED assert            |       |          | 150    | nS   |                                                       |

| t <sub>27</sub>  | TX_RX_LED assert time                      | 195   |          | 225    | mS   | Due To TX Activity                                    |

Refer to Figure 4 for timing diagram.

# 80C24

Figure 4. Transmit Timing

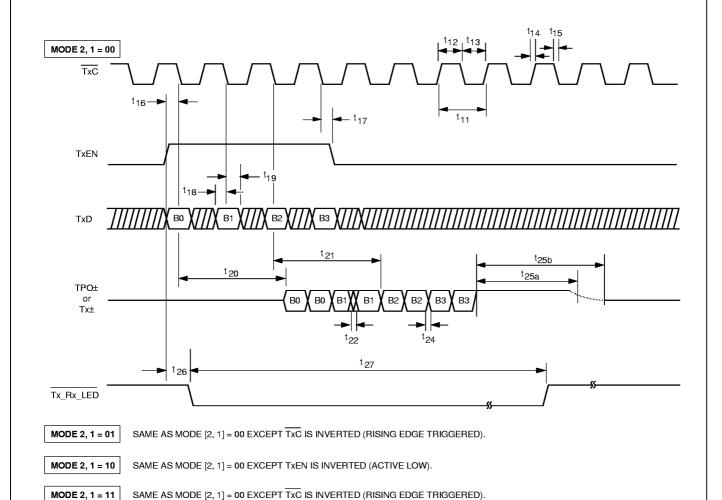

## Receive Timing Characteristics

|                 |                                                                |     | Limit |       |      |                                                           |

|-----------------|----------------------------------------------------------------|-----|-------|-------|------|-----------------------------------------------------------|

| Sym.            | Parameter                                                      | Min | Тур   | Max   | Unit | Conditions                                                |

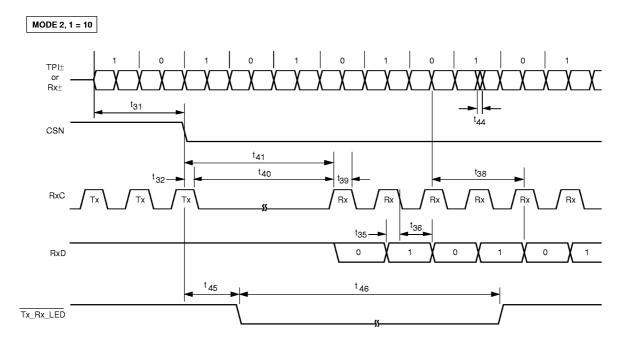

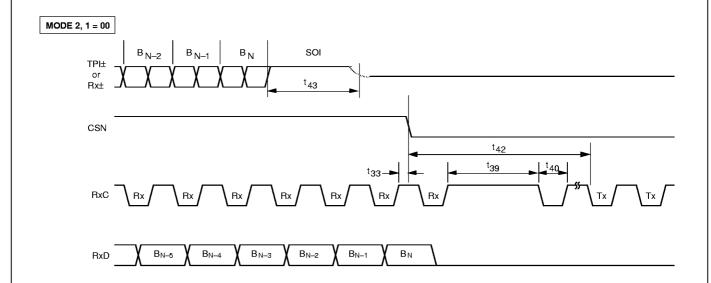

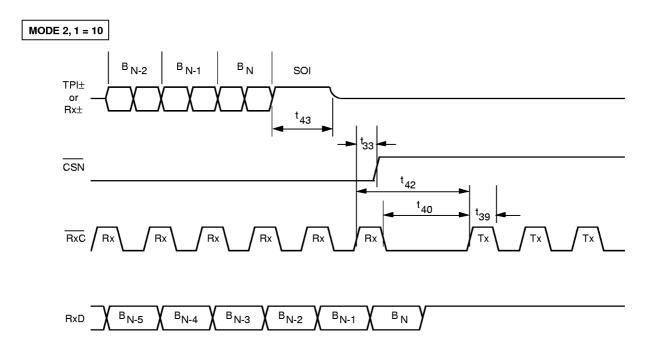

| t <sub>31</sub> | CSN Assert Delay Time                                          |     |       | 600   | nS   | TP                                                        |

| - "             |                                                                |     |       | 240   | nS   | AUI                                                       |

| t <sub>32</sub> | CSN Assert Setup Time                                          | 30  |       |       | nS   |                                                           |

| t <sub>33</sub> | CSN Deassert Hold Time                                         | 20  |       |       | nS   | Mode [2,1] = 00, 01, 11                                   |

|                 |                                                                | 10  |       | 35    | nS   | Mode [2,1] = 10                                           |

| t <sub>35</sub> | RXC to RXD Setup Time                                          | 40  |       |       | nS   |                                                           |

| t <sub>36</sub> | RXC to RXD Hold Time                                           | 30  |       |       | nS   |                                                           |

| t <sub>38</sub> | RXD Propagation Delay                                          |     |       | 200   | nS   |                                                           |

| t <sub>39</sub> | RXC High Time                                                  | 40  |       | 200   | nS   | Mode [2,1] = 00, 01, 11                                   |

|                 |                                                                | 40  |       | 60    | nS   | Mode [2,1] = 10                                           |

| t <sub>40</sub> | RXC Low Time                                                   | 40  |       | 60    | nS   | Mode [2,1] = 00, 01, 11                                   |

|                 |                                                                | 40  |       | 2200  | nS   | Mode [2,1] = 10 Start of Packet                           |

|                 |                                                                | 40  |       | 250   | nS   | Mode [2,1] = 10 End of Packet                             |

| t <sub>41</sub> |                                                                |     |       | 2200  | nS   | TP                                                        |

|                 | Switchover From TX Clock<br>To RX Clock                        |     |       | 1800  | nS   | AUI                                                       |

| t <sub>42</sub> | CSN Deassert To RXC<br>Switchover From Rx Clock<br>To Tx Clock |     |       | 200   | nS   |                                                           |

| t <sub>43</sub> | SOI Pulse Width Required<br>For Idle Detection                 | 125 |       | 200   | nS   | TP Measure TPI± from last zero cross to .3v point.        |

|                 |                                                                | 125 |       | 160   | nS   | AUI<br>Measure RX± from last zero<br>cross to .45v point. |

| t <sub>44</sub> | Receive Input Jitter                                           |     |       | ±13.5 | nS   | Data                                                      |

|                 |                                                                |     |       | ±8.5  | nS   | Preamble                                                  |

| t <sub>45</sub> | CSN Assert To TX_RX_LED Assert                                 |     |       | 100   | nS   |                                                           |

| t <sub>46</sub> | TX_RX_LED Assert time                                          | 195 |       | 225   | mS   | Due To RX Activity                                        |

| t <sub>49</sub> | RXC, RXD, CSN Output<br>Rise And Fall Times                    |     |       | 10    | nS   |                                                           |

Refer to Figures 5 and 6 for timing diagram.

## NOTES:

- 1. CI+ and CI- asserts and deasserts COLL, asynchronously, and asserts and deasserts CSN synchronously with RxC.

- 2. If CI+ and CI- arrives within 4.5 µs from the time CSN was deasserted; CSN will not be reasserted (on transmission node only).

- 3. When CI+ and CI- terminates, CSN will not be deasserted if Rx+ and Rx- are still active.

- 4. When the node finishes transmitting and CSN is deasserted, it cannot be asserted again for 4.5  $\mu s$ .

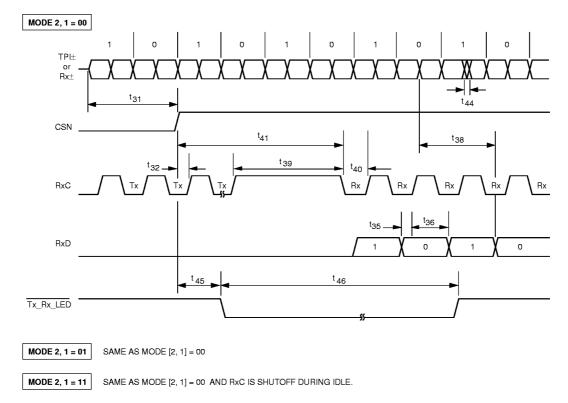

Figure 5a. Receive Timing — Start of Packet for SEEQ, NSC and AMD's Controllers

NOTE:

SAME AS MODE [2, 1] = 00 EXCEPT CSN IS INVERTED (ACTIVE LOW), RxC IS INVERTED (FALLING EDGE TRIGGERED), RxC IS SHUTOFF DURING  $t_{41}$  ACQUISITION TIME, RxD IS HIGH DURING  $t_{41}$  ACQUISITION TIME AND DURING IDLE TIME.

Figure 5b. Receive Timing — Start of Packet for Intel's Controllers

**MODE 2, 1 = 01** SAME AS MODE [2, 1] = 00

MODE 2, 1 = 11 SAME AS MODE [2, 1] = 00 EXCEPT RxC IS SHUTOFF DURING IDLE

Figure 6a. Receive Timing — End of Packet for SEEQ, NSC and AMD's Controllers.

## NOTE:

SAME AS MODE [2, 1] = 00 EXCEPT TXEN IS INVERTED (ACTIVE LOW), RXC IS INVERTED RXC IS SHUTOFF DURING  $t_{41}$  ACQUISITION TIME, RXD IS HIGH DURING  $t_{41}$  ACQUISITION TIME, REFER TO FIGURE 6a.

Figure 6b. Receive Timing — End of Packet for Intel's Controllers.

# **Collision Timing Characteristics**

|                 |                                             |     | Limit |     |      |                    |

|-----------------|---------------------------------------------|-----|-------|-----|------|--------------------|

| Sym.            | Parameter                                   | Min | Тур   | Max | Unit | Conditions         |

| t <sub>51</sub> | COLL Assert Delay Time -<br>Rcv After Xmt   |     |       | 600 | nS   | TP<br>TP⊞ to COLL  |

|                 |                                             |     |       | 300 | nS   | AUI<br>Cl± to COLL |

| t <sub>52</sub> | COLL Assert Delay Time -<br>Xmt After Rcv   |     |       | 600 | nS   | TP<br>TPO± to COLL |

|                 |                                             |     |       | 300 | nS   | AUI<br>CI± to COLL |

| t <sub>53</sub> | COLL Deassert Delay<br>Time - Rcv After Xmt |     |       | 500 | nS   | TP<br>TPl± to COLL |

|                 |                                             |     |       | 500 | nS   | AUI<br>C⊞ to COLL  |

| t <sub>54</sub> | COLL Deassert Delay<br>Time - Xmt After Rcv |     |       | 500 | nS   | TP<br>TPO± to COLL |

|                 |                                             |     |       | 500 | nS   | AUI<br>Cl± to COLL |

| t <sub>55</sub> | COLL Rise And Fall Time                     |     |       | 10  | nS   |                    |

| t <sub>56</sub> | CI± Cycle Time                              | 80  |       | 117 | nS   |                    |

| t <sub>57</sub> | CI± Low Or High Time                        | 35  |       | 70  | nS   |                    |

| t <sub>58</sub> | CI± Rise And Fall Time                      |     |       | 10  | nS   |                    |

Refer to Figures 7 and 8 for timing diagram.

MODE 2, 1 = 10 SAME AS MODE [2, 1] = 00 EXCEPT COLL IS INVERTED (ACTIVE LOW)

Figure 7. Collision Timing — Receive After Transmit

## MODE 2, 1 = 00, 01, 11

MODE 2, 1 = 10

SAME AS MODE 2, 1 = 00 EXCEPT COLL IS INVERTED (ACTIVE LOW)

Figure 8. Collision Timing — Transmit After Receive

# Link Pulse Timing Characteristics

|                 |                                                                                                  |     | Limit |     |                |                                |

|-----------------|--------------------------------------------------------------------------------------------------|-----|-------|-----|----------------|--------------------------------|

| Sym.            | Parameter                                                                                        | Min | Тур   | Max | Unit           | Conditions                     |

| t <sub>61</sub> | Transmit Link Pulse Width                                                                        | 75  |       | 125 | nS             |                                |

| t <sub>62</sub> | Transmit Link Pulse Period                                                                       | 11  |       | 15  | mS             |                                |

| t <sub>63</sub> | Transmit Link Pulse To<br>Double Link Pulse Spacing                                              | 5.0 | 5.2   | 5.4 | μS             | Full Duplex Mode Signalling    |

| t <sub>64</sub> | Transmit Double Link<br>Pulse Interval Spacing                                                   | 16  |       | 16  | Link<br>Pulses | Full Duplex Mode Signalling    |

| t <sub>65</sub> | Receive Link Pulse Width<br>Required For Detection                                               | 35  |       | 200 | nS             |                                |

| t <sub>66</sub> | Receive Link Pulse<br>Minimum Period Required<br>For Detection                                   | 2   | 4     | 7   | mS             | Link_Test_Min                  |

| t <sub>67</sub> | Receive Link Pulse<br>Maximum Period Required<br>For Detection                                   | 50  |       | 150 | mS             | Link_Loss and<br>Link_Test_Max |

| t <sub>68</sub> | Receive Link Pulse To<br>Double Link Pulse Spacing<br>Required For Full Duplex<br>Mode Detection | 4.8 |       | 5.6 | μS             | Full Duplex Mode Detection     |

| t <sub>69</sub> | Receive Double Link Pulse Minimum Period Required For Full Duplex Mode Detection                 | 204 | 210   | 216 | mS             | Full Duplex Mode Detection     |

| t <sub>70</sub> | Receive Double Link Pulse<br>Maximum Period Required<br>for Full Duplex Detection                | 750 |       | 850 | mS             | Full Duplex Detection Mode     |

| t <sub>71</sub> | Receive Link Pulse Assert                                                                        | 2   | 3     | 10  | Link<br>Pulses |                                |

| t <sub>72</sub> | Receive Full Duplex Assert                                                                       |     |       | 7   | μS             | Full Duplex Mode Detection     |

Refer to Figure 9 for timing diagram.

# 80C24

Figure 9. Link Pulse Timing

FDPLX\_DET

## Jabber Timing Characteristics

|                 | Limit                    |         | Limit |     | Limit |            | Limit |  | Limit |  | Limit |  |  |  |

|-----------------|--------------------------|---------|-------|-----|-------|------------|-------|--|-------|--|-------|--|--|--|

| Sym.            | Parameter                | Min Typ |       | Max | Unit  | Conditions |       |  |       |  |       |  |  |  |

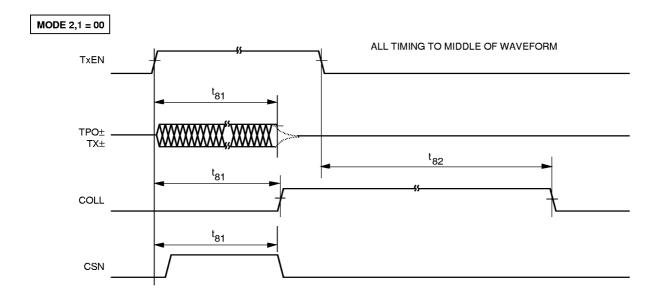

| t <sub>81</sub> | Jabber Activation Time   | 40      |       | 60  | mS    | TP and AUI |       |  |       |  |       |  |  |  |

| t <sub>82</sub> | Jabber Deactivation Time | 400     |       | 430 | mS    | TP and AUI |       |  |       |  |       |  |  |  |

Refer to Figure 10 for timing diagram

MODE 2,1 = 01 SAME AS MODE 2, 1 = 00

MODE 2,1 = 10 SAME AS MODE 2, 1 = 00 EXCEPT COLL IS INVERTED (ACTIVE LOW), CSN IS INVERTED, AND TXEN IS INVERTED.

**MODE 2,1 = 11** SAME AS MODE 2, 1 = 00

Figure 10. Jabber Timing

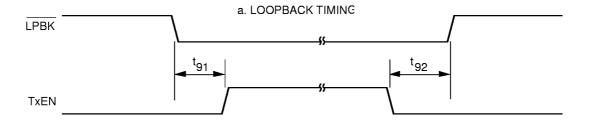

## Loopback/SQE Timing Characteristics

|                 |                 | Limit |     |     |      |            |

|-----------------|-----------------|-------|-----|-----|------|------------|

| Sym.            | Parameter       | Min   | Тур | Max | Unit | Conditions |

| t <sub>91</sub> | LPBK Setup Time | 5     |     |     | μS   | AUI Only   |

| t <sub>92</sub> | LPBK Hold Time  | 5     |     |     | μS   | AUI Only   |

| t <sub>93</sub> | SQE Pulse Delay | 600   |     | 700 | nS   |            |

| t <sub>94</sub> | SQE Pulse Width | 750   |     | 850 | nS   |            |

Refer to Figure 11 for timing diagram.

MODE 2,1 = 01 SAME AS MODE [2, 1] = 00 EXCEPT LPBK INVERTED (ACTIVE HIGH)

MODE 2,1 = 10 SAME AS MODE [2, 1] = 00 EXCEPT TXEN INVERTED, CSN INVERTED

MODE 2,1 = 11 SAME AS MODE [2, 1] = 00 EXCEPT LPBK INVERTED (ACTIVE HIGH)

Figure 11. Loopback/SQE Test Timing

27

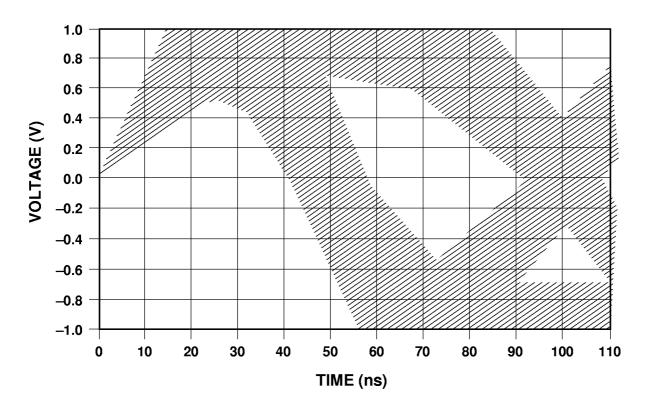

Figure 12. Twisted Pair Output Voltage Template with Line Model.

With and Without Line Model

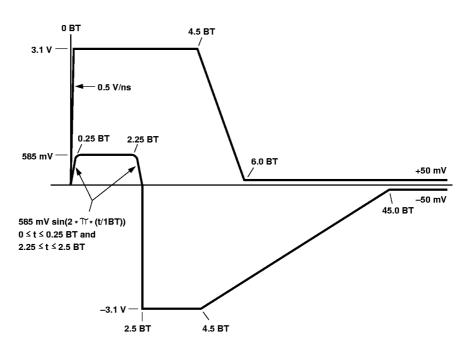

Figure 13. Transmit Start of Idle Pulse Voltage Template

With and Without Line Model

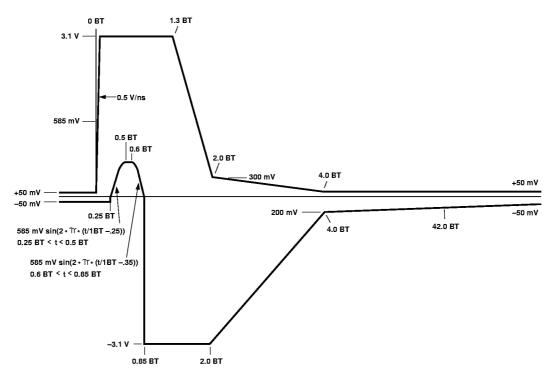

Figure 14. Transmit Link Pulse Voltage Template

## Ordering Information

#### **PART NUMBER**

## Revision History

#### 4/15/96

- All references to separate 'digital' and 'analog' power and grounds deleted.

- There are four sets of  $V_{cc}$ /GND on the 80C24:  $V_{cc1}$ /GND<sub>1</sub>,  $V_{cc2}$ /GND<sub>2</sub>,  $V_{cc3}$ /GND<sub>3</sub>, and  $V_{cc4}$ /GND<sub>4</sub>.

- Page 9, Power Supply Decoupling suggestions added to page.

- -Page 12, DC Digital I/O Characteristics:  $\rm V_{\rm OL}$  (max) changed from 0.8 to 1.2 V.

- Page 15, AUI Characteristics: AOCD (max) changed from Vcc/2.5 to Vcc/2.1.

- Page 31, Table replaced with addendum dated April 1995.

#### 9/9/96

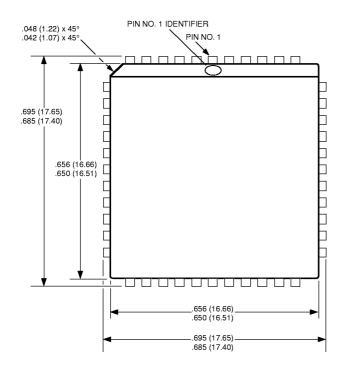

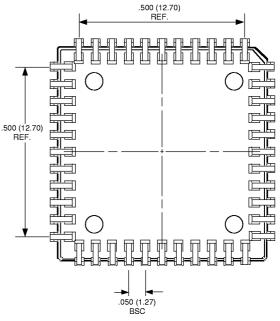

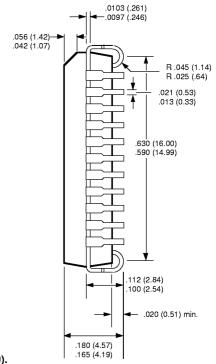

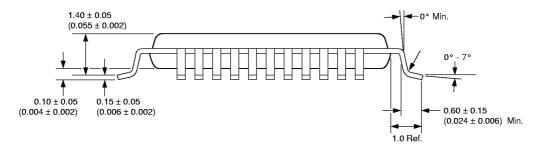

- Pages 33, 34, PLCC and TQFP dimension diagrams have been added to this data sheet.

## 12/10/96

- Pages 17, Transmit Timing Characteristics, TXEN Hold Time (min.) has been changed from 40 to 0.

# Appendix A

## **Mode Port Select Table**

This Mode/Port Select Table lists out all the possible pin combinations and describes the corresponding features that are enabled in those combinations.

|                              |                       |        | INPUTS      |                    |              |                    | FEATURES           |           |          |           |      |          |          |                         |

|------------------------------|-----------------------|--------|-------------|--------------------|--------------|--------------------|--------------------|-----------|----------|-----------|------|----------|----------|-------------------------|