|                         | REVISIONS                                                                   |                                                                                           |            |          |   |     |             |       |    |     |            |      |       |                                                                      |     |    |     |          |          |   |          |   |          |        |         |

|-------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------|----------|---|-----|-------------|-------|----|-----|------------|------|-------|----------------------------------------------------------------------|-----|----|-----|----------|----------|---|----------|---|----------|--------|---------|

| LTR                     | DESCRIPTION                                                                 |                                                                                           |            |          |   |     |             |       |    |     |            | DATE | (YR-  | MO-D                                                                 | Á)  | AF | PRO | WED      |          |   |          |   |          |        |         |

|                         | i                                                                           |                                                                                           |            |          |   |     |             |       |    |     |            |      |       |                                                                      |     |    |     |          |          |   |          |   |          |        |         |

|                         |                                                                             |                                                                                           |            |          |   |     |             |       | ,  |     |            |      |       |                                                                      |     |    |     |          |          |   |          |   |          |        |         |

| REV                     | T                                                                           | Т                                                                                         | Т          | ٦        |   |     |             |       |    |     |            |      |       | Τ                                                                    |     |    |     |          |          |   |          |   |          |        |         |

| SHEET                   | -                                                                           | 十                                                                                         | +          | 1        |   |     |             |       |    |     |            |      |       | T                                                                    |     |    |     |          |          |   |          |   |          |        |         |

| REV                     |                                                                             | 1                                                                                         | 1          |          |   |     |             |       |    |     |            |      |       |                                                                      |     |    |     |          |          |   |          |   |          |        |         |

| SHEET                   |                                                                             |                                                                                           |            |          |   |     |             |       |    |     |            |      |       |                                                                      |     |    |     | L        |          | _ |          |   | _        |        |         |

| REV ST                  |                                                                             | L                                                                                         | RE         | ,        |   |     |             |       |    |     |            |      | L     |                                                                      | L   |    | _   | <u> </u> | <u> </u> | L | <u> </u> | _ | <u> </u> |        | Щ       |

| PMIC N                  | MIC N/A  PREPARED BY  DEFENSE ELECTRONICS SUPPLY CENTER  DAYTON. OHIO 45444 |                                                                                           |            |          |   |     |             |       |    |     |            |      |       |                                                                      |     |    |     |          |          |   |          |   |          |        |         |

| N<br>D                  | NDAR<br>MILITA<br>RAW                                                       | RY<br>ING                                                                                 | ı          |          |   |     | Ra          | D BY  | W  | 00  | سند<br>مرو | n    |       | MICROCIRCUITS, DIGITAL, CMOS, TIMING CONTROLUNIT, MONOLITHIC SILICON |     |    |     |          | ROL      |   |          |   |          |        |         |

| FOR USE<br>AND<br>DEPAR | AGENCII<br>RTMENT (                                                         | DEPAI                                                                                     | RTM<br>THE | ENT<br>E | s | . 7 | <b>NPRI</b> | G API | 88 | Æ b | ATE        |      | <br>- | SIZE                                                                 |     |    | 672 | 268      | }        |   | 59       |   |          | 859    | 99      |

| L                       |                                                                             | AMSC N/A SHEET 1 OF 18  ESC FORM 193 *U.S. GOVERNMENT PRINTING OFFICE: 1987 748-129/60911 |            |          |   |     |             |       |    | -   |            |      | <br>  |                                                                      | one |    |     |          |          |   | ING OF   |   |          | 748-12 | 9/60911 |

5962-E836

DESC FORM 193

SEP 87

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

1. SCOPE  $1.1\,$  Scope. This drawing describes device requirements for class B microcircuits in accordance with  $1.2.1\,$  of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". 1.2 Part number. The complete part number shall be as shown in the following example: 5962-88599 Case outline Lead finish per Drawing number Device type (1.2.1)(1.2.2)MIL-M-38510 1.2.1 Device type. The device type shall identify the circuit function as follows: Device type Generic number Circuit function Frequency 01 32C201 Timing control unit 10 MHz 1.2.2 Case outline. The case outline shall be as designated in appendix C of MIL-M-38510, and as follows: Outline letter Case outline D-3 (24-lead, 1.290" x .610" x .225"), dual-in-line package .1 1.3 Absolute maximum ratings. Supply voltage range - - - - - - - - - - - - - - --0.5 V dc to 7.0 V dc -0.5 V dc to 5.5 V dc -0.5 V dc to 5.5 V dc -65°C to +150°C 1.0 W Lead temperature (soldering, 10 seconds) - - - - - -+300°C Junction temperature (T\_J) - - - - - - - - - - - - Thermal resistance, junction-to-case ( $\theta_{JC}$ ) - - - - -+150°C (See MIL-M-38510, appendix C) 1.4 Recommended operating conditions. Case operating temperature range - - - - - - - --55°C to +125°C Operating supply voltage range -------4.75 V dc to 5.25 V dc 2.0 V dc 0.8 V dc 3.8 V dc 1.0 V dc

## STANDARDIZED MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

DESC FORM 193A SEP 87

## 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510 - Microcircuits, General Specification for.

**STANDARD**

**MILITARY**

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

## 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

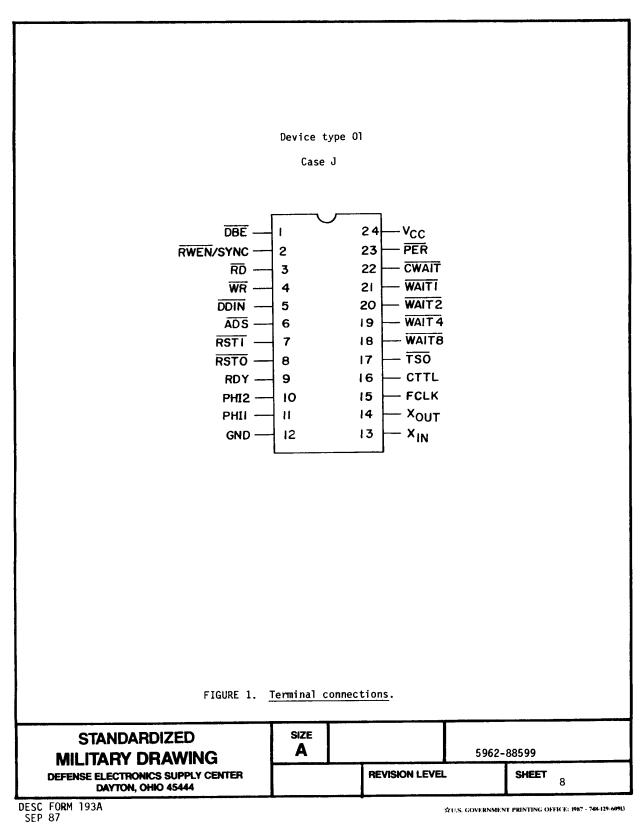

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

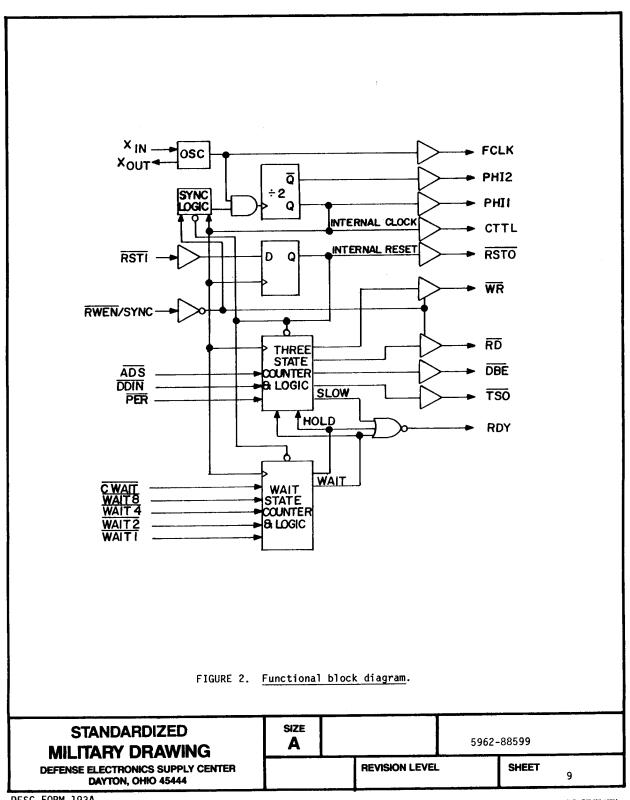

- 3.2.2 Functional block diagram. The functional block diagram shall be as specified on figure 2.

- 3.2.3 Case outline. The case outline shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.4 herein.

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |                | 5962 | -88599 |   |

|------------------------------------------------------|------------------|----------------|------|--------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | •    | SHEET  | 3 |

DESC FORM 193A SEP 87

| Test                                          | Symbol                    | Conditions 2/<br>-55°C < T <sub>C</sub> < +125°C<br>V <sub>CC</sub> = 5.0 V ±5% | Group A<br> subgroups | Limi          | Unit          |           |

|-----------------------------------------------|---------------------------|---------------------------------------------------------------------------------|-----------------------|---------------|---------------|-----------|

|                                               | 1/                        | $V_{CC} = 5.0 \text{ V } \pm 5\%$<br>unless otherwise specifie                  |                       | Min           | Max           |           |

| Input high voltage                            | v <sub>IH</sub><br>       | All inputs except RSTI and   X <sub>IN</sub>                                    | 1,2,3                 | 2.4           |               | <b>V</b>  |

| Input low voltage                             | <br>  v <sub>IL</sub><br> | All inputs except RSTI and   XIN                                                | 1,2,3                 | <br>          | .8            | ٧         |

| RSTI rising threshold voltage                 | <br> Y <sub>T</sub> +     |                                                                                 | 1,2,3                 | 2.0           | 3.5           | ٧         |

| RSTI hysteresis voltage                       | VHYS                      |                                                                                 | 1,2,3                 | .8            | 1.9           | ٧         |

| X <sub>IN</sub> input high voltage            | V <sub>XH</sub>           |                                                                                 | 1,2,3                 | 4.275         |               | ٧         |

| X <sub>IN</sub> input low voltage             | Ι<br>V <sub>XL</sub>      |                                                                                 | 1,2,3                 | i<br>!<br>!   | .525          | ٧         |

| Input low current                             | IIIL                      | V <sub>IN</sub> = 0.0 V                                                         | 1,2,3                 | <br> -20<br>  |               | μA        |

| Input high current                            | IIH                       | AIM = ACC                                                                       | 1,2,3                 |               | <br> +20<br>  | μА        |

| Output low voltage                            | VOL                       | I = 2 mA except PHI1, PHI2,                                                     | 1,2,3                 |               | .525<br> <br> | ٧         |

| Output low voltage<br>PHI1, PHI2              | VOL                       | I = 1 mA                                                                        | 1,2,3                 | <br>          | .525<br> <br> | V         |

| Output high voltage<br>All outputs except OUT | V <sub>OH</sub>           | <br> I = -1 mA<br>                                                              | 1,2,3                 | <br>  3.8<br> | ]<br> <br>    | V         |

| See footnote at end of table.                 | ,                         |                                                                                 |                       |               |               |           |

|                                               |                           |                                                                                 |                       |               |               |           |

|                                               |                           |                                                                                 |                       |               |               |           |

| STANDARDIZED                                  | 10                        | SIZE A                                                                          | 5                     | 962-8859      | 9             | <u></u> . |

| MILITARY DRAWIN                               |                           |                                                                                 |                       |               |               |           |

Electrical performance characteristics - Continued. TABLE I. Conditions  $\frac{2}{-55}$ °C  $\leq T_C \leq +125$ °C  $V_{CC} = 5.0$  V  $\pm 5\%$ Limits Unit Symbol Group A Test subgroups 1/ Min Max unless otherwise specified +20  $\mu \boldsymbol{A}$ 1,2,3 Force 5.25 V on outputs, Three-state leakage current IZH 1 MHz high 1,2,3 -20 μА Force 0.4 V on outputs, Three-state leakage current  $I_{ZL}$ 1 ow 200 mΑ 1,2,3 |All outputs high Supply current Icc |Fin = 10 MHz рF 4 50 Output capacitance  $c_0$ 3/ рF 4 40 Input capacitance  $C_{\rm I}$ 3/ 4 40 рF Clock capacitance 3/ CCLK 9,10,11 100 ns t<sub>CP</sub>7 PHI1 rising edge, to next Clock period |PHI1 rising edge 90 percent PHI1 rising edge, to 90 percent PHI1 rising t<sub>CLb</sub> 9,10,11 35 47 ns Clock high time ledge 43 60 9,10,11 ns Clock low time |10 percent PHI1 falling edge,| tclj to 10 percent PHI1 rising 40 52 At 2.0 V on PHI1 (both edges) 9,10,11 ns Clock pulse width tCLW1 52 40 9,10,11 ns Clock pulse width |At 2.0 V on PHI2 (both edges)| tcLW2 İt<sub>Xh</sub> |2.5 V  $X_{IN}$  rising edge to |2.5 V  $X_{IN}$  falling edge 9,10,11 16 ns  $X_{IN}$  high time (external input) , t<sub>X1</sub>  $X_{\mbox{\scriptsize IN}}$  low time (external  $|2.5\ V\ X_{IN}$  falling edge to 9,10,11 16 ns 12.5 V XIN rising edge input) X<sub>IN</sub> to FCLK rising edge delay 3 29 9,10,11 ns |2.5 V X<sub>IN</sub> rising edge to FCLK rising edge See footnotes at end of table. SIZE STANDARDIZED A 5962-88599 MILITARY DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 5

DESC FORM 193A SEP 87

| TABLE I.                                       | Electrica                      | l performanc                                   | e characteristics                                                            | _ Continue                                 | i.         |                       |                     |

|------------------------------------------------|--------------------------------|------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------|------------|-----------------------|---------------------|

| Test                                           | Symbol                         | -55°C<br>I V <sub>CC</sub>                     | nditions 2/<br>< T <sub>C</sub> < +125°C<br>= 5.0°V ±5%<br>nerwise specified | Group A  <br>  Group A  <br> subgroups<br> | Lim<br>Min | its<br> <br>  Max<br> | <br>  Unit<br> <br> |

| X <sub>IN</sub> to FCLK falling edge<br>delay  | t <sub>XF</sub> r              | <br> 2.5 V X <sub>IN</sub> fa<br> to FCLK fall | alling edge                                                                  | 9,10,11                                    | 6          | 29<br>                | i ns                |

| X <sub>IN</sub> to CTTL rising edge<br>delay   | t <sub>XCR</sub>               | <br> 2.5 V X <sub>IN</sub> ri<br> CTTL rising  | ising edge to<br>edge                                                        | 9,10,11                                    | 3          | 34                    | ns                  |

| X <sub>IN</sub> to PHI1 rising edge<br>delay   | txpr                           | <br> 2.5 V X <sub>IN</sub> ri<br> PHI1 rising  | ising edge to<br>edge                                                        | 9,10,11                                    | 3          | 32                    | ns                  |

| CTTL pulse width                               | t <sub>CTW</sub>               | <br> At 50 percer<br> (both edges)             | nt V <sub>CC</sub> on CTTL                                                   | 9,10,11                                    | 43         | 51                    | ns                  |

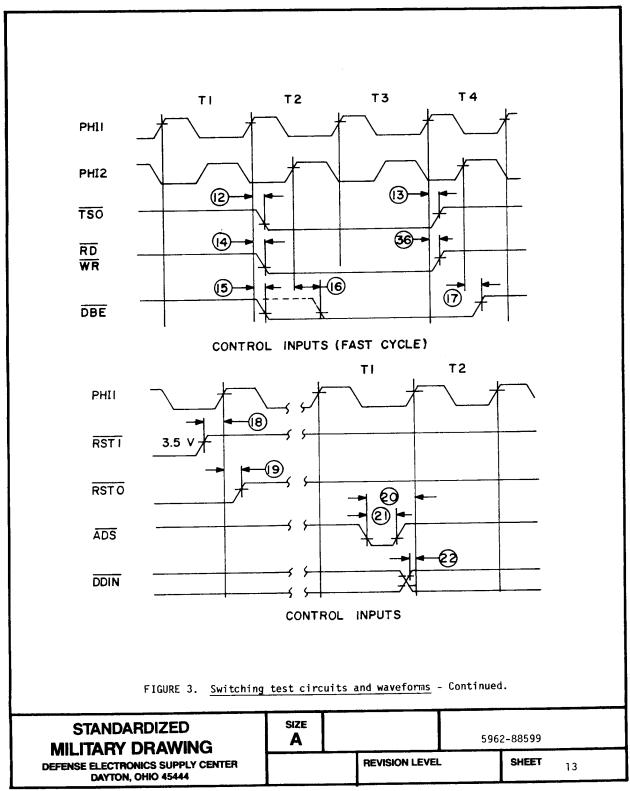

| Setup time                                     | <br> t <sub>RŞTs</sub><br>  18 | <br> Before PHI1<br>                           | rising edge                                                                  | 9,10,11                                    | 20         |                       | ns                  |

| RSTO rising edge delay                         | t <sub>RST</sub> r             | <br> After PHI1  <br>                          | rising edge                                                                  | 9,10,11                                    |            | 21                    | ns                  |

| ADS setup time                                 | t <sub>ADs</sub>               | <br> Before PHI1<br>                           | rising edge                                                                  | 9,10,11                                    | 30         |                       | ns                  |

| ADS pulse width                                | t <sub>ADW</sub>               | <br> ADS leading<br> trailing edg              |                                                                              | 9,10,11                                    | 25         |                       | ns                  |

| DDIN setup time                                | t <sub>DDs</sub>               | <br> Before PHI1<br>                           | rising edge                                                                  | 9,10,11                                    | 15         |                       | ns                  |

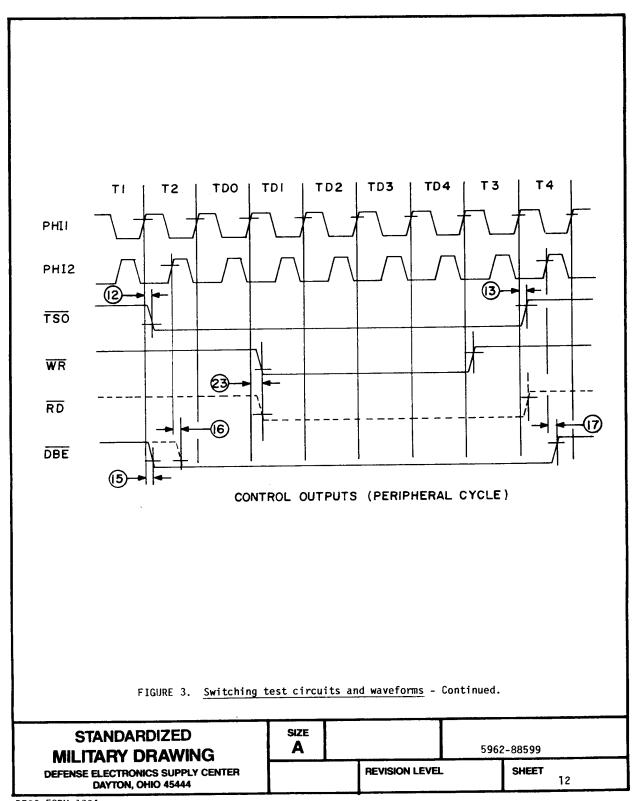

| TSO leading edge delay                         | t <sub>Tf</sub>                | After PHI1                                     | rising edge                                                                  | 9,10,11                                    |            | 12                    | ns                  |

| TSO trailing edge delay                        | t <sub>T</sub> r <sub>13</sub> | <br> After PHI1  <br>                          | rising edge                                                                  | 9,10,11                                    |            | 18                    | ns                  |

| RD/WR leading edge delay<br>(fast cycle)       | tRWF(f)                        | <br> After PHI1                                | rising edge                                                                  | 9,10,11                                    |            | 35                    | ns                  |

| RD/WR leading edge delay<br>(peripheral cycle) | t <sub>RWF</sub> (s)           | After PHI1                                     | rising edge                                                                  | 9,10,11                                    |            | 25                    | ns                  |

| DBE leading edge delay<br>(write cycle)        | t <sub>DBf</sub> (w)           | After PHI1                                     | rising edge                                                                  | 9,10,11                                    |            | 28                    | ns                  |

| DBE leading edge delay<br>(read cycle)         | t <sub>DB</sub> f(r)           | <br> After PHI2  <br>                          | rising edge                                                                  | 9,10,11                                    |            | 21                    | ns                  |

| See footnote at end of table                   | ·•                             |                                                |                                                                              |                                            |            |                       |                     |

| STANDARDIZED<br>MILITARY DRAW                  | _                              | SIZE<br>A                                      |                                                                              | 59                                         | 62-8859    | 9                     |                     |

| DEFENSE ELECTRONICS SUPP<br>DAYTON, OHIO 4544  | LY CENTER                      |                                                | REVISION LI                                                                  | EVEL                                       | SHEE       | ET 6                  |                     |

| TABLE I. <u>Electrical performance characteristics</u> - Continued. |                                                                 |                                                           |                     |      |              |      |  |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------|---------------------|------|--------------|------|--|--|

| Test                                                                | Symbol                                                          | Conditions 2/<br>-55°C < T <sub>C</sub> < +1 <b>25°</b> C | Group A             | Limi | !<br>  Unit  |      |  |  |

|                                                                     | 1/                                                              | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$    | subgroups <br> <br> | Min  | Max          |      |  |  |

| DBE trailing edge delay                                             | trailing edge delay   t <sub>DBr</sub>   After PHI2 rising edge |                                                           | 9,10,11             |      | 23           | ns   |  |  |

| RD/WR trailing edge delay                                           | l<br> trwr<br>  36                                              | <br> After PHI1 rising edge<br>                           | 9,10,11             | :    | 25           | l ns |  |  |

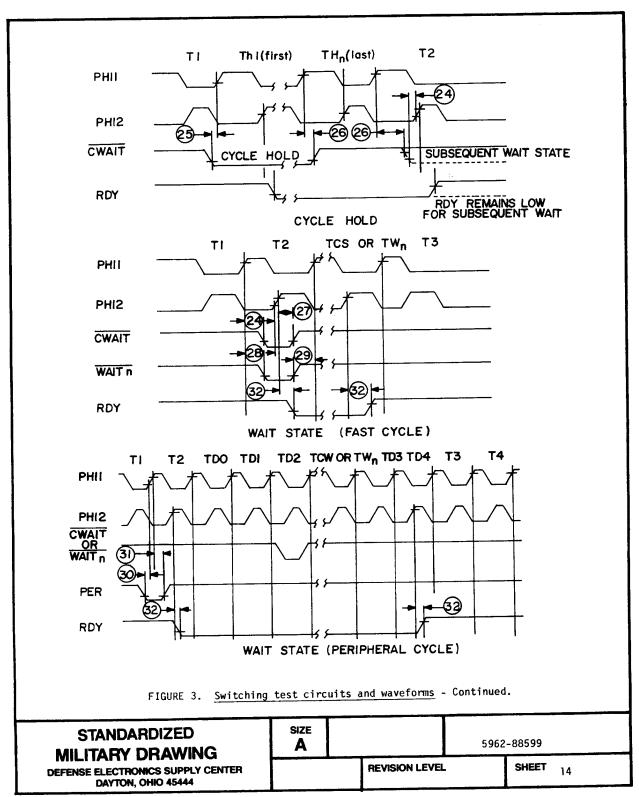

| CWAIT setup time (cycle hold)                                       | tcws(H)                                                         | <br> Before PHI1 rising edge<br>                          | 9,10,11             | 30   |              | ns   |  |  |

| CWAIT hold time (cycle hold)                                        | <br> tcwp(н)<br>  26                                            | <br> After PHI1 rising edge<br>                           | 9,10,11             | 0    |              | l ns |  |  |

| CWAIT setup time (wait states)                                      | t <sub>CWs</sub> (W)                                            | <br> Before PHI2 rising edge                              | 9,10,11             | 10   |              | ns   |  |  |

| CWAIT hold time (wait states)                                       | tcwh(w)                                                         | <br> After PHI2 rising edge<br>                           | 9,10,11             | 20   | <br> <br>    | ns   |  |  |

| WAITn setup time                                                    | <br> t <sub>WS</sub><br>  28                                    | <br> Before PHI2 rising edge<br>                          | 9,10,11             | 7    | <br>         | l ns |  |  |

| WAITn hold time                                                     | <br> t <sub>Wh</sub><br>  29                                    | <br> After PHI2 rising edge<br>                           | 9,10,11             | 20   | <br>         | l ns |  |  |

| PER setup time                                                      | tp <sub>§</sub>                                                 | <br> Before PHI1 rising edge<br>                          | 9,10,11             | 5    |              | l ns |  |  |

| PER hold time                                                       | tp <sub>h</sub>                                                 | <br> After PHI1 rising edge                               | 9,10,11             | 30   | <br> <br>    | ns   |  |  |

| RDY delay                                                           | t <sub>Rd</sub>                                                 | After PHI2 rising edge                                    | 9,10,11             |      | 25           | ns   |  |  |

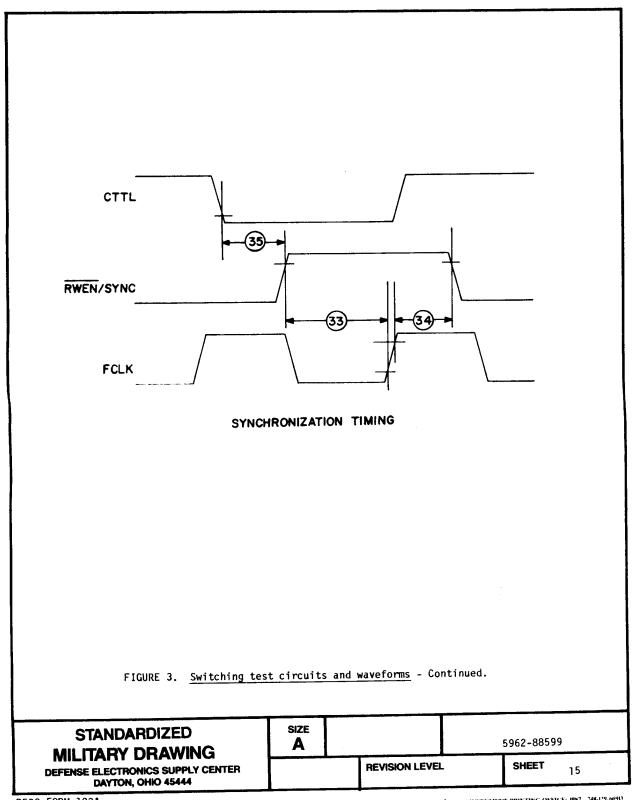

| SYNC setup time                                                     | T                                                               | <br> Before FCLK rising edge                              | 9,10,11             | 6    |              | ns   |  |  |

| SYNC hold time                                                      | t <sub>Syh</sub>                                                | After FCLK rising edge                                    | 9,10,11             | 0    | <br> <br>    | ns   |  |  |

| CTTL/SYNC inversion delay                                           | <br>  t <sub>C</sub> §<br>  35                                  | <br> CTTL (master) to RWEN/SYNC<br>  (slave)              | 9,10,11             |      | <br>  10<br> | ns   |  |  |

Numbers included in this column are timing diagram reference numbers (see figure 3).

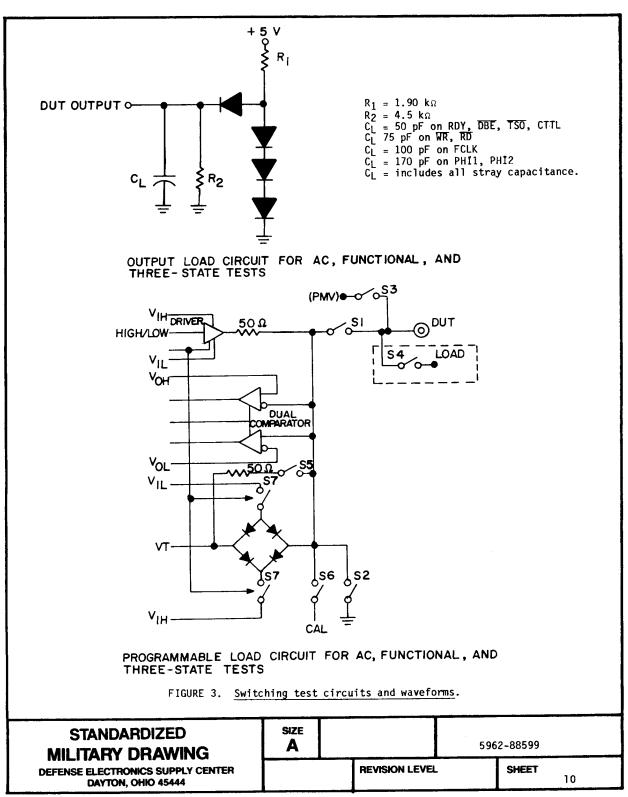

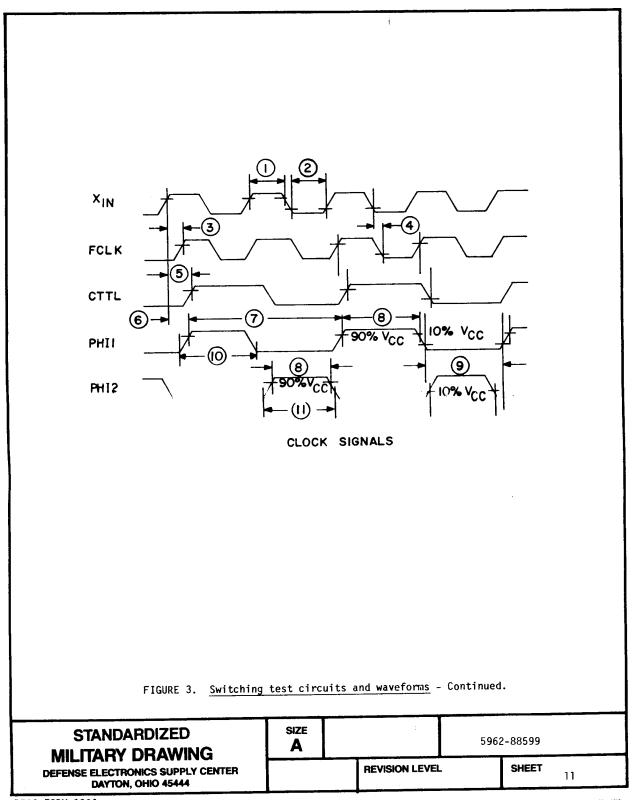

AC loading and test circuits shall be as specified on figure 3. All the timing specifications refer to 15 percent or 85 percent of  $V_{CC}$  on the rising or falling edges of the clock phases PHI1 and PHI2, and all output signals; to 30 percent or 70 percent of  $V_{CC}$  on all the CMOS input signals, and to 0.8 V or 2.0 V on all the TTL input signals, unless specifically stated otherwise.

The capacitance measurements shall be made between the indicated terminal and ground at a frequency of 1 MHz at  $T_{\rm C}$  of +25°C. The dc bias of the measuring instrument shall be less than  $\pm 0.1$  V. The ac signal amplitude shall be less than 50 mV rms.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-88599

REVISION LEVEL

SHEET

7

DESC FORM 193A SEP 87

**☆U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-609**D

- ☆U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

\$\text{\$\pi\$U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

· ☆ U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

☆U.S. GOVERNMENT PRINTING OFFICE: 1967 - 748-129-60913

ratus, government printing office: 1987 - 748-129-60913

☆U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 Screening. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 (C $_{\rm I}$ , C $_{\rm Q}$ , C $_{\rm CLK}$  measurements) shall be measured only for the initial test and after process or design changes which may affect input capacitance.

- d. Subgroups 7 and 8 shall consist of verifying the functionality of the device. It forms a part of the vendor's test tape and shall be maintained and available from the approved sources of supply.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br><b>A</b> |                | 5962 | -88599 |    |

|---------------------------------------------------------|------------------|----------------|------|--------|----|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                  | REVISION LEVEL | L    | SHEET  | 16 |

TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                      | Subgroups<br>  (per method<br>  5005, table I) |

|--------------------------------------------------------------------|------------------------------------------------|

| Interim electrical parameters<br>(method 5004)                     | 1                                              |

| Final electrical test parameters<br>(method 5004)                  | 1*, 2, 3, 7,<br>8, 9, 10, 11                   |

| Group A test requirements<br>(method 5005)                         | 1, 2, 3, 4, 7,<br>8, 9, 10, 11                 |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 2, 8A, 10                                      |

<sup>\*</sup> PDA applies to subgroup 1.

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

- 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Replaceability is determined as follows:

- a. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- b. When a QPL source is established, the part numbered device specified in this drawing will be replaced by the microcircuit identified as part number M38510/55201.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962 | -88599 |    |

|------------------------------------------------------|-----------|----------------|------|--------|----|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | -    | SHEET  | 17 |

6.4 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

| Military drawing<br>  part number | Vendor<br>  CAGE<br>  number | Vendor<br>  similar part<br>  number <u>1</u> / | Replacement   Replacement  military specification    part number |

|-----------------------------------|------------------------------|-------------------------------------------------|------------------------------------------------------------------|

| 5962-8859901JX                    | 27014                        | NS32C201D10/883                                 | MIL-M-38510/55201BJX                                             |

$\frac{1}{2}$  Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

Vendor CAGE number

Vendor name and address

27014

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, CA 95051

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE A 5962-88599

REVISION LEVEL SHEET 18

DESC FORM 193A SEP 87