**User's Manual**

# V850ES/PM1

# **32-Bit Single-Chip Microcontroller**

Hardware

μ**PD703228**

Document No. U16237EJ2V0UD00 (2nd edition) Date Published September 2003 N CP(K)

© NEC Electronics Corporation 2003 Printed in Japan [MEMO]

# **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of July, 2003. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- · Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

# [GLOBAL SUPPORT] http://www.necel.com/en/support/support.html

| NEC Electronics America, Inc. (U.S.)<br>Santa Clara, California | <b>NEC Electronics (Europe) GmbH</b><br>Duesseldorf, Germany | NEC Electronics Hong Kong Ltd.<br>Hong Kong |

|-----------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|

| Tel: 408-588-6000<br>800-366-9782                               | Tel: 0211-65 03 01                                           | Tel: 2886-9318                              |

|                                                                 | <ul> <li>Sucursal en España</li> </ul>                       | NEC Electronics Hong Kong Ltd.              |

|                                                                 | Madrid, Spain                                                | Seoul Branch                                |

|                                                                 | Tel: 091-504 27 87                                           | Seoul, Korea                                |

|                                                                 |                                                              | Tel: 02-558-3737                            |

|                                                                 | <ul> <li>Succursale Française</li> </ul>                     |                                             |

|                                                                 | Vélizy-Villacoublay, France                                  | NEC Electronics Shanghai, Ltd.              |

|                                                                 | Tel: 01-30-67 58 00                                          | Shanghai, P.R. China                        |

|                                                                 |                                                              | Tel: 021-6841-1138                          |

|                                                                 | <ul> <li>Filiale Italiana</li> </ul>                         |                                             |

|                                                                 | Milano, Italy                                                | NEC Electronics Taiwan Ltd.                 |

|                                                                 | Tel: 02-66 75 41                                             | Taipei, Taiwan                              |

|                                                                 |                                                              |                                             |

- Branch The Netherlands Eindhoven. The Netherlands Tel: 040-2445845

- Tyskland Filial Taeby, Sweden Tel: 08-63 80 820

- United Kingdom Branch Milton Keynes, UK Tel: 01908-691-133

Tel: 02-2719-2377

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 6253-8311

.103.4

# PREFACE

| Readers                 | This manual is intended for users who wish to understand the functions of the V850ES/PM1 ( $\mu$ PD703228) and design application systems using this product.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Purpose                 | This manual is intended to give users an understanding of the hardware functions of the V850ES/PM1 shown in the Organization below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Organization            | This manual is divided into two parts: Hardware (this manual) and Architecture (V850ES Architecture User's Manual).HardwareArchitecture• Pin functions• Data types• CPU function• Register set• On-chip peripheral functions• Instruction format and instruction set• Electrical specifications• Dipeline operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| How to Read This Manual | It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.<br>To find the details of a register where the name is known<br>→ Refer to APPENDIX A REGISTER INDEX.<br>To understand the details of an instruction function<br>→ Refer to the V850ES Architecture User's Manual available separately.<br>Register format<br>→ The name of the bit whose number is in angle brackets (<>) in the figure of the register format of each register is defined as a reserved word in the device file.<br>To understand the overall functions of the V850ES/PM1<br>→ Read this manual according to the CONTENTS.<br>To know the electrical specifications of the V850ES/PM1<br>→ Refer to CHAPTER 20 ELECTRICAL SPECIFICATIONS.<br>The mark ★ shows major revised points. |  |  |

| Conventions | Data significance:<br>Active low representation:<br>Memory map address: | Higher digits on the left and lower digits on the right $\overline{xxx}$ (overscore over pin or signal name)<br>Higher addresses on the top and lower addresses on the bottom |

|-------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Note:                                                                   | Footnote for item marked with Note in the text                                                                                                                                |

|             | Caution:                                                                | Information requiring particular attention                                                                                                                                    |

|             | Remark:                                                                 | Supplementary information                                                                                                                                                     |

|             | Numeric representation:                                                 | Binary xxxx or xxxxB                                                                                                                                                          |

|             |                                                                         | Decimal xxxx                                                                                                                                                                  |

|             |                                                                         | Hexadecimal xxxxH                                                                                                                                                             |

|             | Prefix indicating power of 2                                            |                                                                                                                                                                               |

|             | (address space, memory                                                  |                                                                                                                                                                               |

|             | capacity):                                                              | K (kilo): 2 <sup>10</sup> = 1,024                                                                                                                                             |

|             |                                                                         | M (mega): 2 <sup>20</sup> = 1,024 <sup>2</sup>                                                                                                                                |

|             |                                                                         | G (giga): 2 <sup>30</sup> = 1,024 <sup>3</sup>                                                                                                                                |

|             |                                                                         |                                                                                                                                                                               |

# Related Documents

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# Documents related to V850ES/PM1

| Document Name                     | Document No. |

|-----------------------------------|--------------|

| V850ES Architecture User's Manual | U15943E      |

| V850ES/PM1 Hardware User's Manual | This manual  |

#### Documents related to development tools

| Document Name                               |                                                     | Document No.   |

|---------------------------------------------|-----------------------------------------------------|----------------|

| IE-V850ES-G1 (In-Circuit Emulator)          | IE-V850ES-G1 (In-Circuit Emulator)                  |                |

| IE-703228-G1-EM1 (In-Circuit Emulator Optio | n Board)                                            | To be prepared |

| CA850 C Compiler Package Ver. 2.50 or       | Operation                                           | U16053E        |

| Later ID850                                 | C Language                                          | U16054E        |

|                                             | Assembly Language                                   | U16042E        |

| PM plus Ver. 5.10                           |                                                     | U16569E        |

| ID850 Ver. 2.50 Integrated Debugger         | Operation                                           | U16217E        |

| SM850 Ver. 2.50 System Simulator            | Operation                                           | U15182E        |

| SM850 Ver. 2.00 System Simulator            | External Part User Open<br>Interface Specifications | U14873E        |

| RX850 Real-Time OS Ver. 3.13 or Later       | Basics                                              | U13430E        |

|                                             | Installation                                        | U13410E        |

|                                             | Technical                                           | U13431E        |

| RX850 Pro Real-Time OS Ver. 3.13            | Basics                                              | U13773E        |

|                                             | Installation                                        | U13774E        |

|                                             | Technical                                           | U13772E        |

| RD850 Task Debugger Ver. 3.01               |                                                     | U13737E        |

| RD850 Pro Task Debugger Ver. 3.01           |                                                     | U13916E        |

| AZ850 System Performance Analyzer Ver. 3.0  |                                                     | U14410E        |

# CONTENTS

| СНА | <b>APTE</b> F   | R 1 IN         | IRODUCTION                                                           | 14 |

|-----|-----------------|----------------|----------------------------------------------------------------------|----|

|     | 1.1             | Overvi         | ew                                                                   | 14 |

|     | 1.2             | Featur         | es                                                                   | 15 |

|     | 1.3             | Applic         | ation Fields                                                         | 16 |

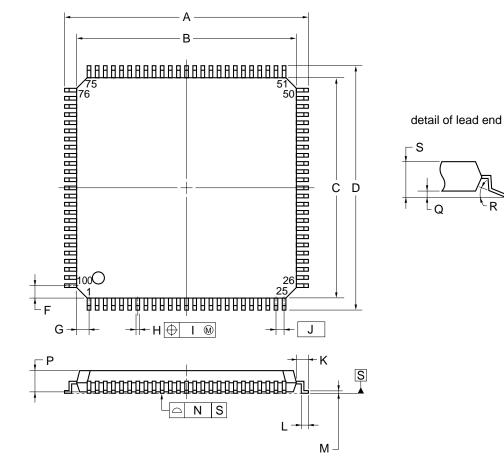

|     | 1.4             | ••             | ng Information                                                       |    |

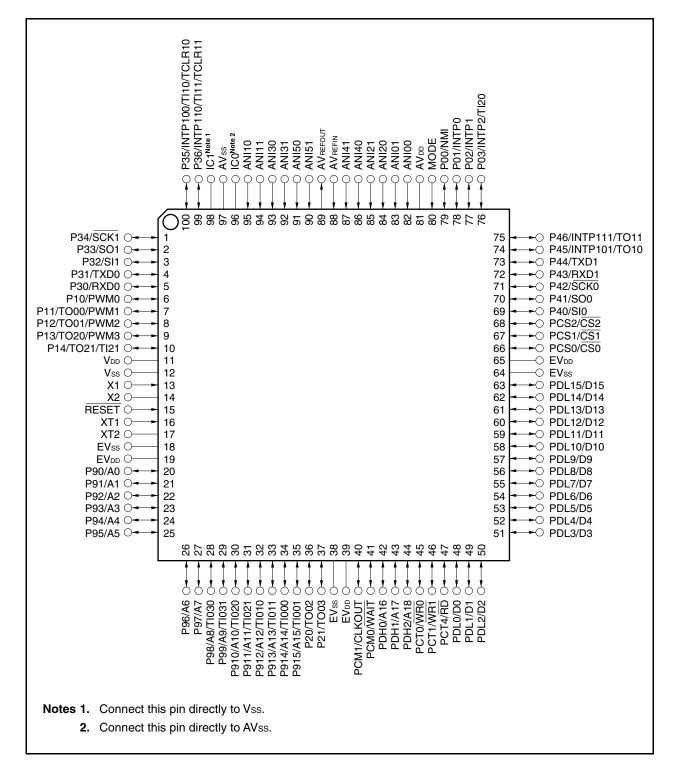

|     | 1.5             |                | onfiguration (Top View)                                              |    |

|     | 1.6             |                | on Block Configuration                                               |    |

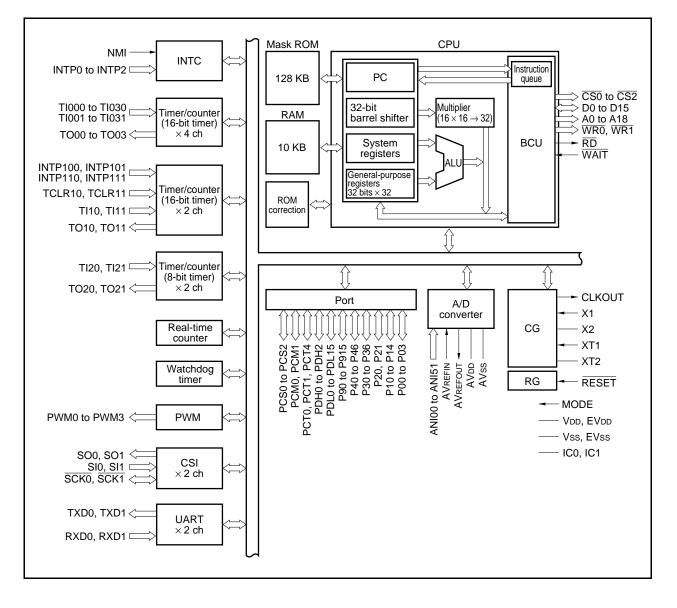

|     |                 | 1.6.1          | Internal block diagram                                               |    |

|     |                 | 1.6.2          | Internal units                                                       |    |

| СНА | <b>APTE</b> F   | 2 PI           | N FUNCTIONS                                                          | 22 |

|     | 2.1             | Din Eu         | nction List                                                          | 22 |

|     | 2.1             |                | atus                                                                 |    |

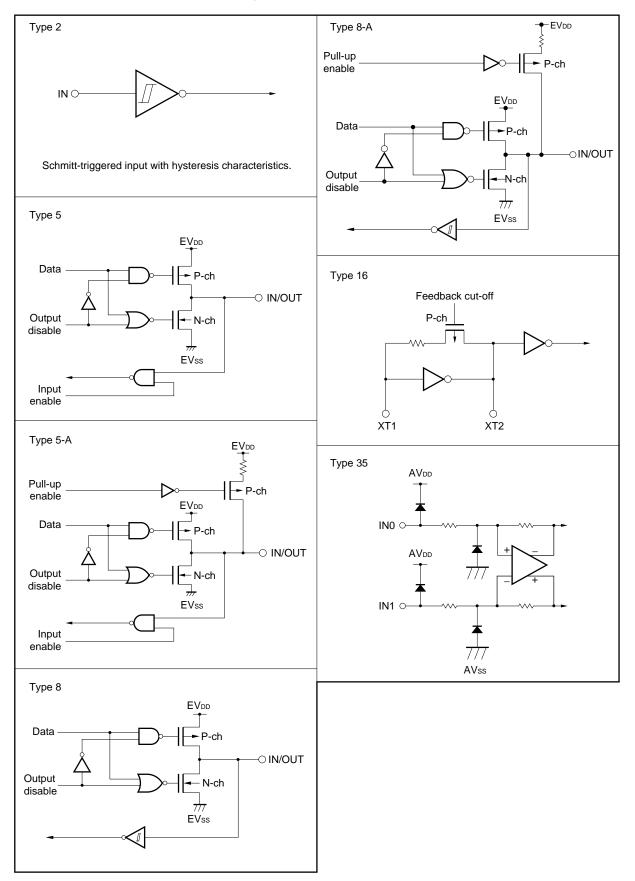

|     | 2.2             |                | of Pin I/O Circuits, I/O Buffer Power Supplies, and Connection of Un |    |

|     |                 |                |                                                                      |    |

| CHA | <b>APTEF</b>    | R 3 CP         | PU FUNCTION                                                          | 32 |

|     | 3.1             | Featur         | es                                                                   | 32 |

|     | 3.2             | CPU R          | egister Set                                                          | 33 |

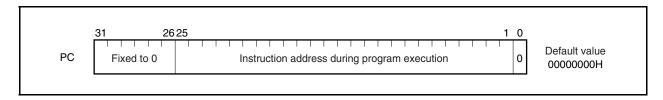

|     |                 | 3.2.1          | Program register set                                                 |    |

|     |                 | 3.2.2          | System register set                                                  | 35 |

|     | 3.3             | Operat         | tion Modes                                                           | 41 |

|     |                 | 3.3.1          | Operation modes                                                      | 41 |

|     |                 | 3.3.2          | Specifying operation mode                                            | 41 |

|     | 3.4             | Addres         | ss Space                                                             | 42 |

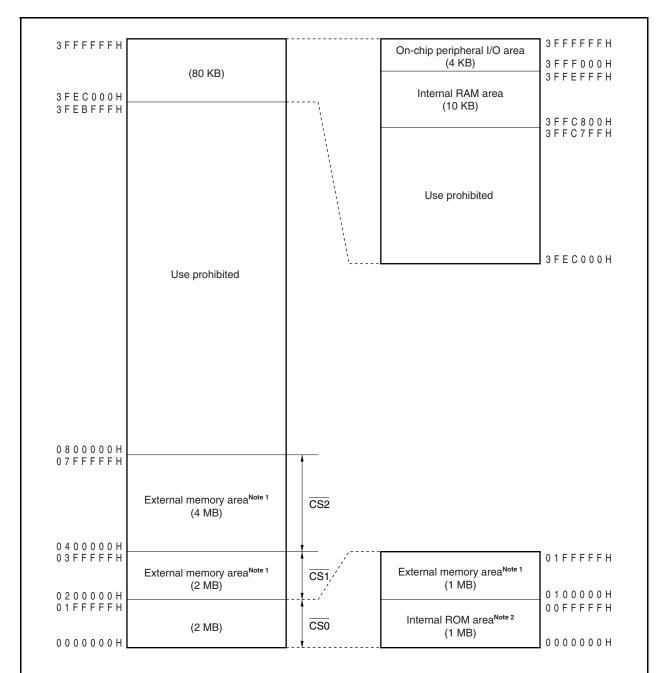

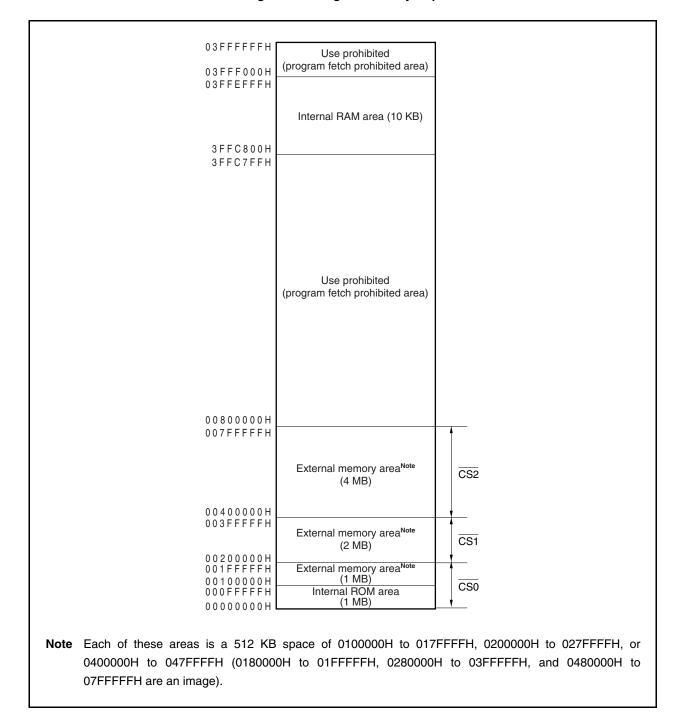

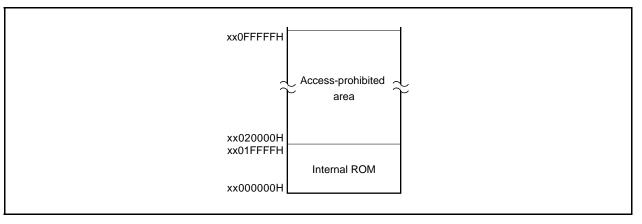

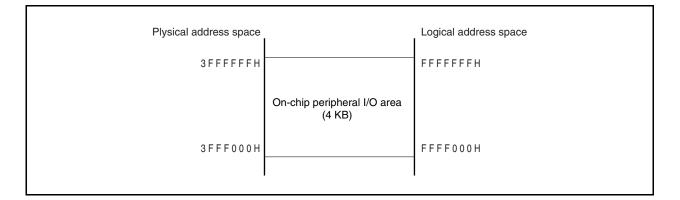

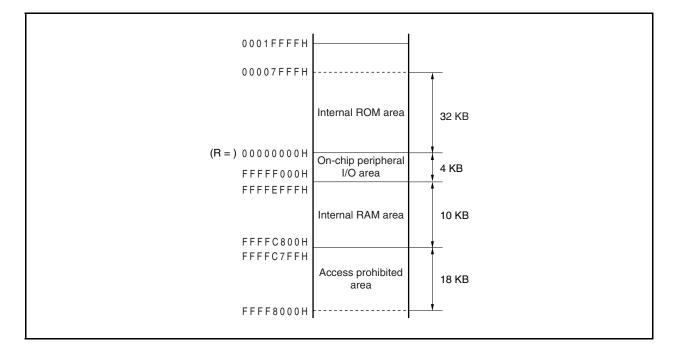

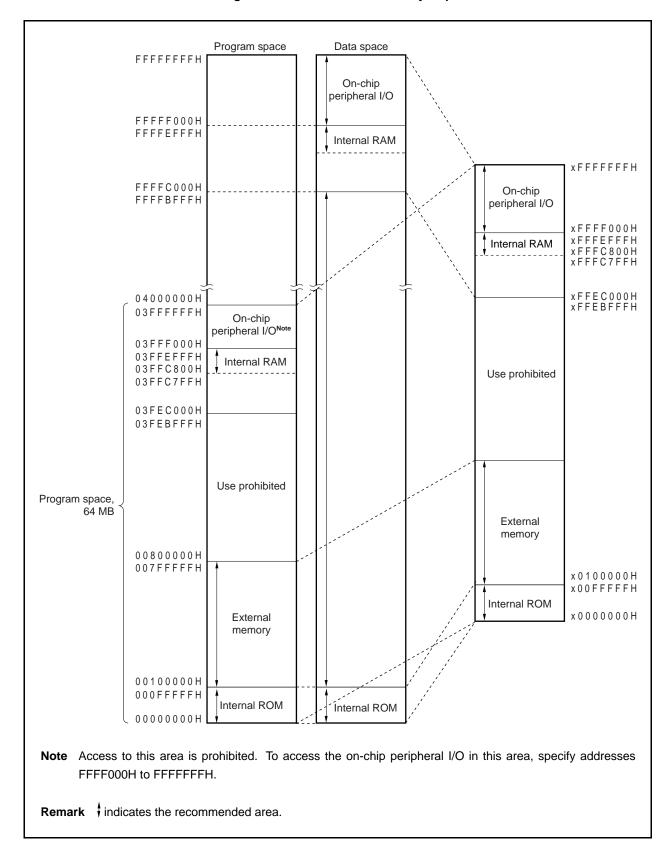

|     |                 | 3.4.1          | CPU address space                                                    | 42 |

|     |                 | 3.4.2          | Wrap-around of CPU address space                                     | 43 |

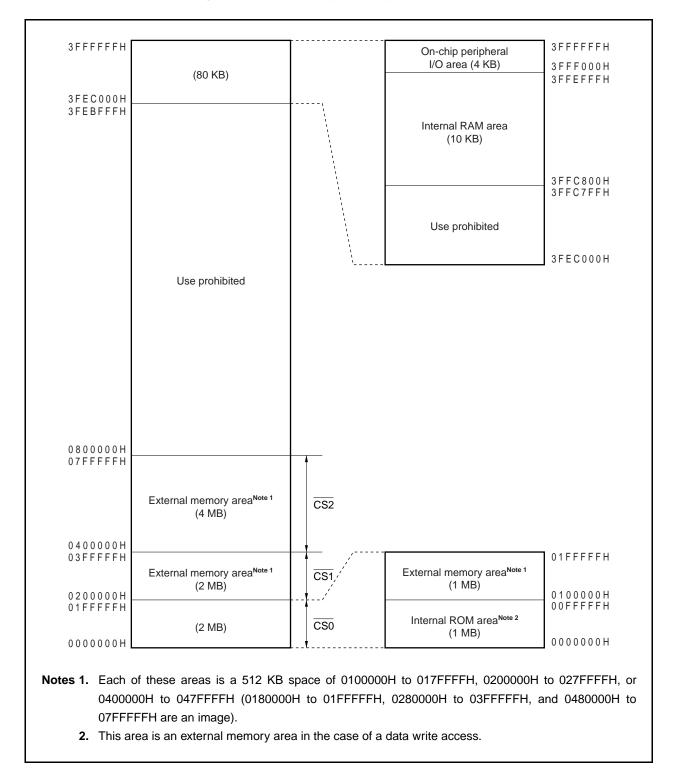

|     |                 | 3.4.3          | Memory map                                                           |    |

|     |                 | 3.4.4          | Areas                                                                | 46 |

|     |                 | 3.4.5          | Recommended use of address space                                     |    |

|     |                 | 3.4.6          | Peripheral I/O registers                                             | 50 |

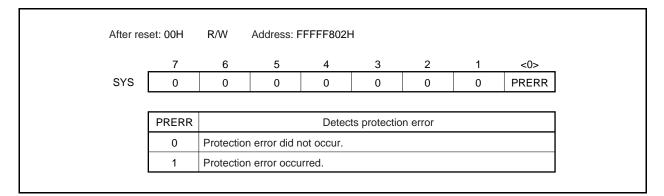

|     |                 | 3.4.7          | Special registers                                                    | 56 |

|     |                 | 3.4.8          | Cautions                                                             | 60 |

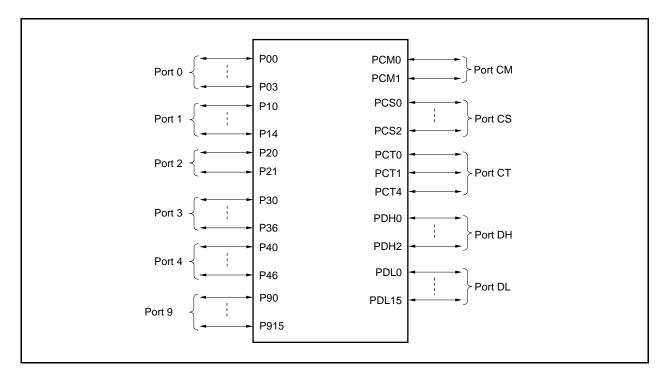

| СНА | APTER           | R 4 PC         | ORT FUNCTIONS                                                        | 63 |

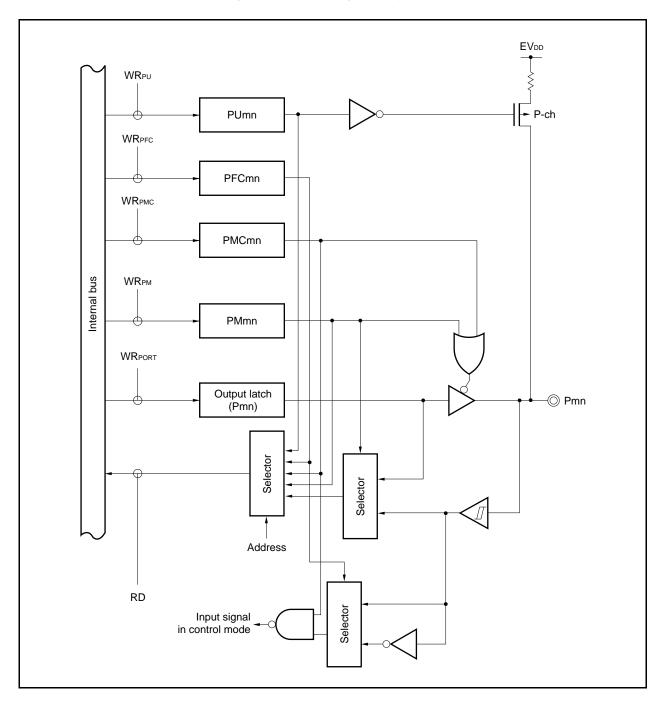

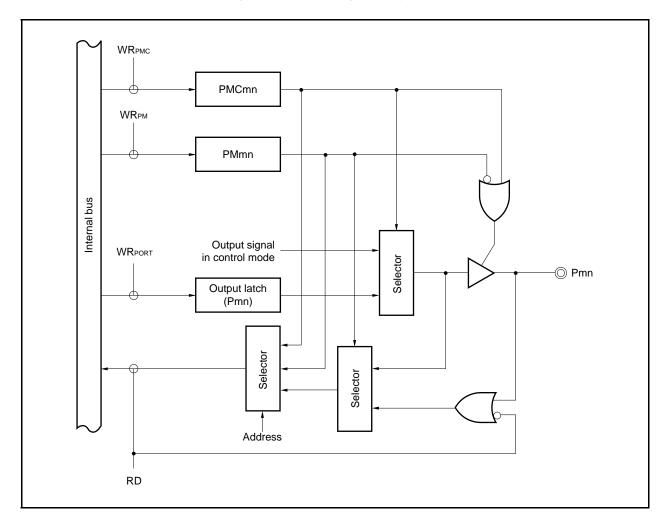

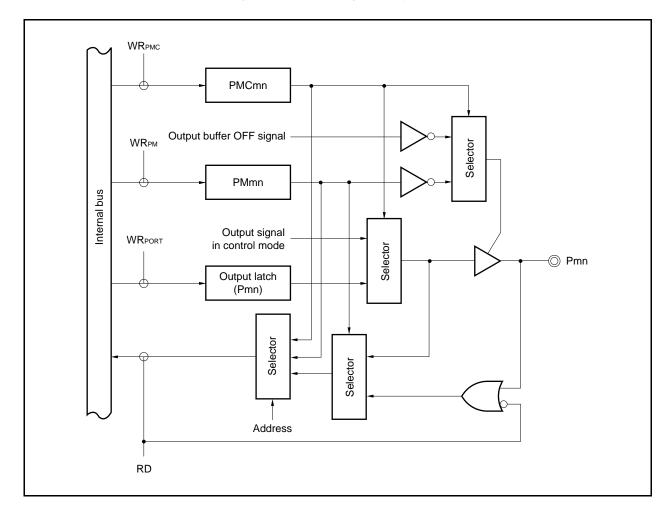

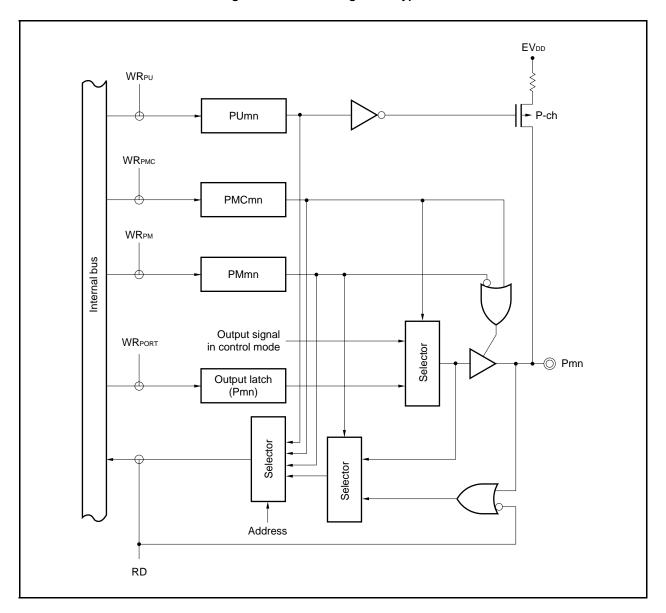

|     | 4.1             | Featur         | es                                                                   | 63 |

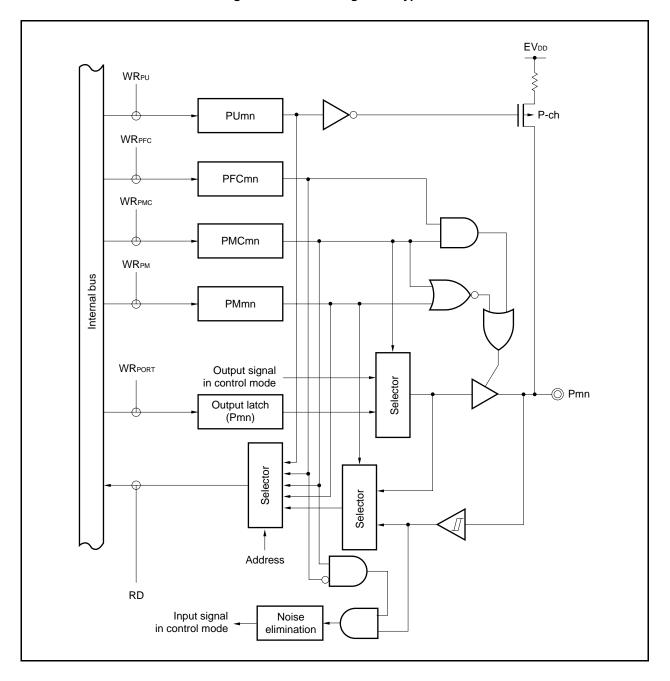

|     | 4.2             |                | Configuration of Port                                                |    |

|     | 4.2<br>4.3      |                | onfiguration                                                         |    |

|     | <del>т</del> .Ј | 4.3.1          | Port 0                                                               |    |

|     |                 | 4.3.1          | Port 1                                                               |    |

|     |                 | 4.3.2<br>4.3.3 | Port 2                                                               |    |

|     |                 | 4.3.3<br>4.3.4 | Port 3                                                               |    |

|     |                 | 4.3.4<br>4.3.5 | Port 4                                                               |    |

|     |                 | ч. <b>0</b> .0 |                                                                      |    |

|        | 4.3.6 Port 9                                                                            | 83  |

|--------|-----------------------------------------------------------------------------------------|-----|

|        | 4.3.7 Port CM                                                                           |     |

|        | 4.3.8 Port CS                                                                           |     |

|        | 4.3.9 Port CT                                                                           |     |

|        | 4.3.10 Port DH                                                                          | 94  |

|        | 4.3.11 Port DL                                                                          |     |

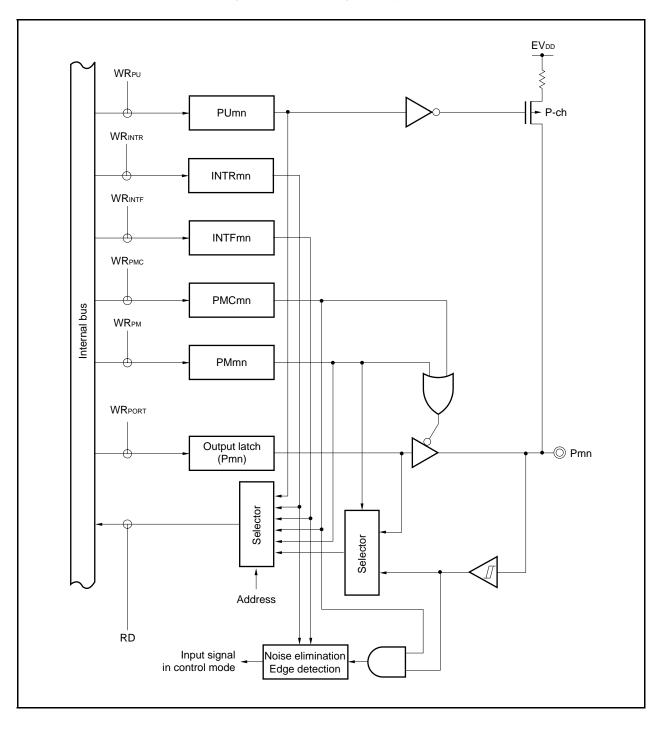

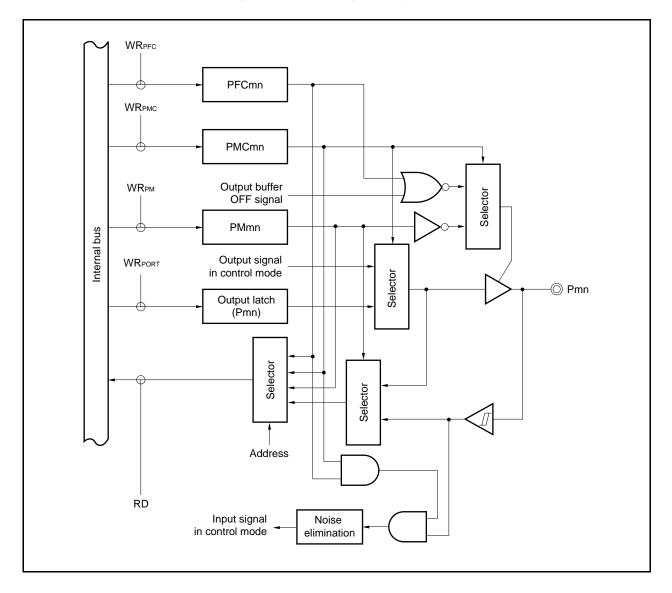

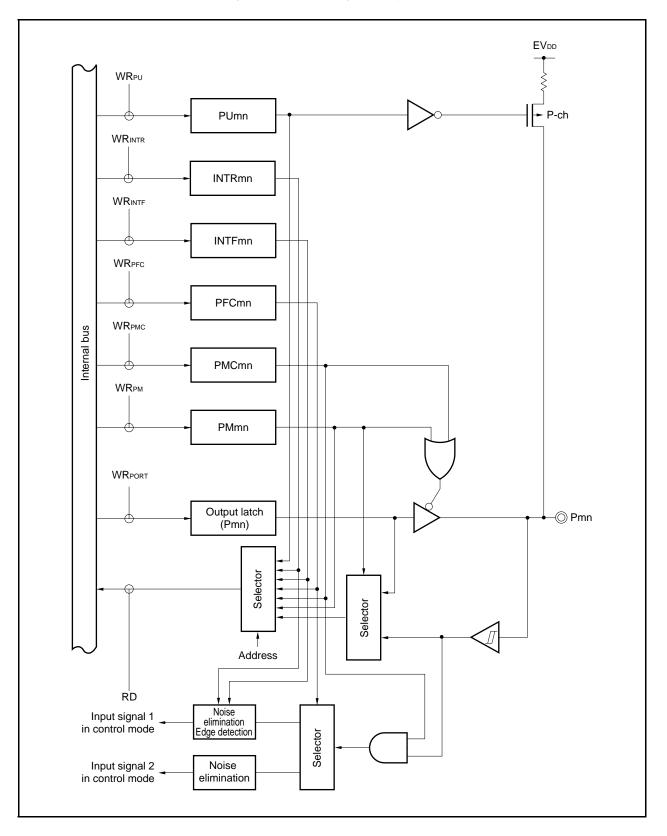

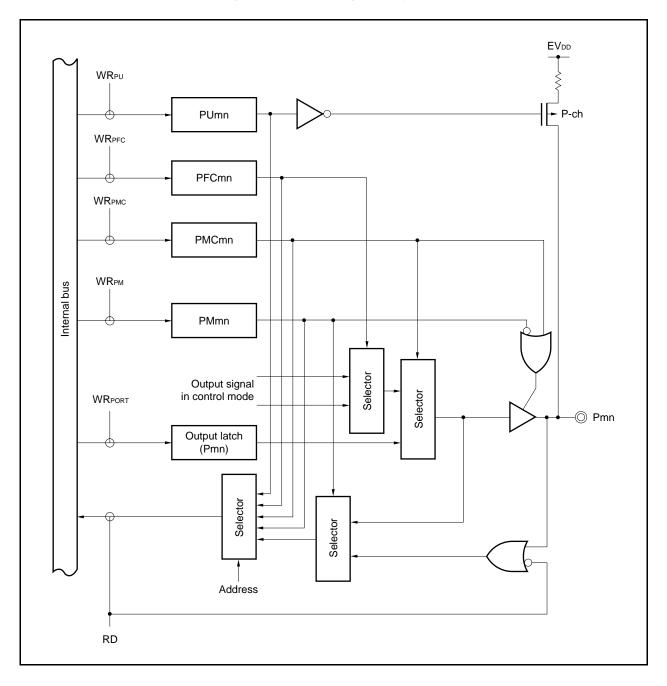

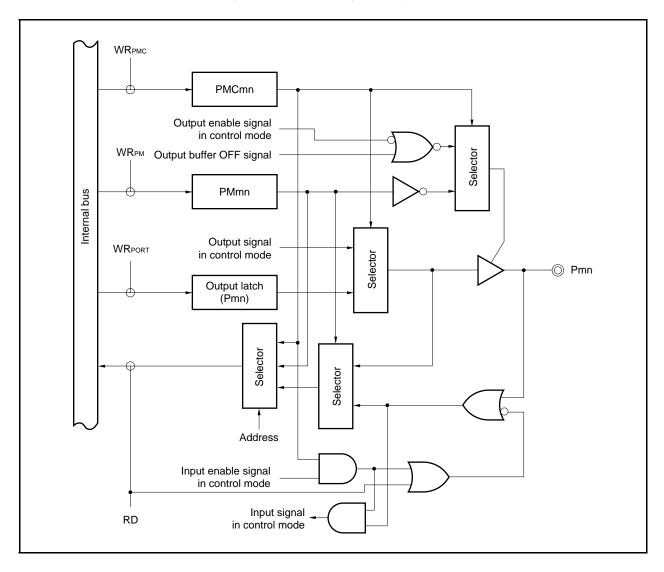

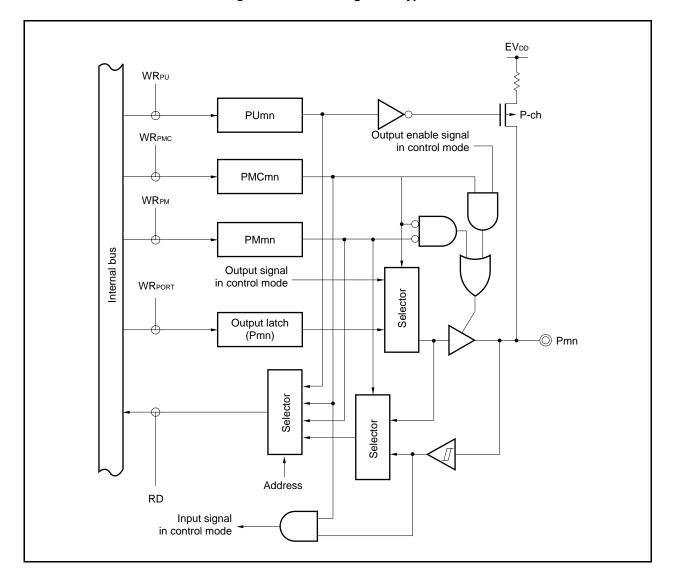

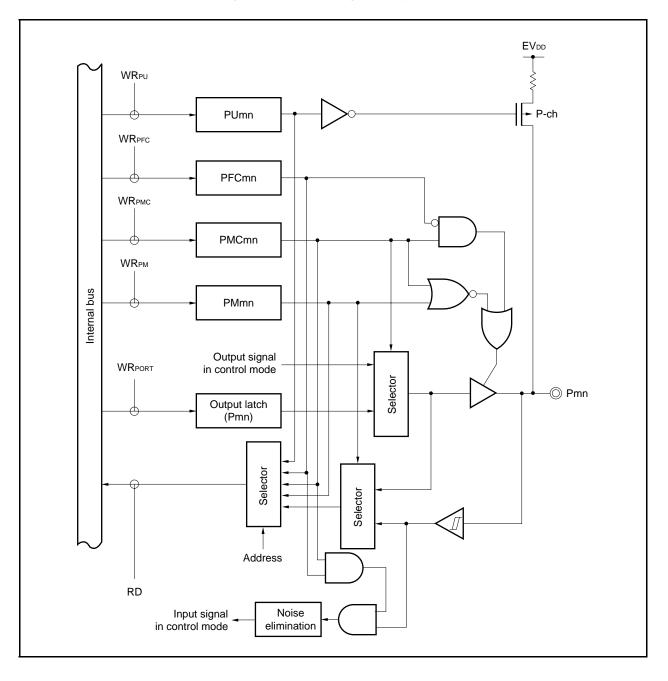

| 4.4    | Block Diagram                                                                           | 99  |

| 4.5    | Register Settings for Ports When Alternate Function Is Used                             | 114 |

| 4.6    | Cautions                                                                                |     |

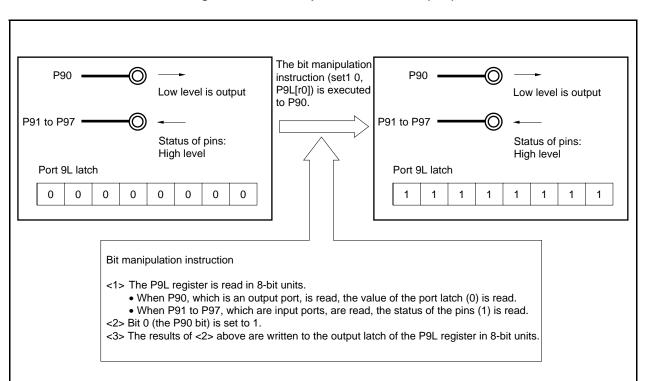

|        | 4.6.1 Cautions on bit manipulation instruction for port n register (Pn)                 | 120 |

| CHAPTE | R 5 BUS CONTROL FUNCTION                                                                | 121 |

| 5.1    | Features                                                                                |     |

| 5.2    | Bus Control Pins                                                                        |     |

|        | 5.2.1 Pin status when internal ROM, internal RAM, or on-chip peripheral I/O is accessed |     |

|        | 5.2.2 Pin status in each operation mode                                                 |     |

| 5.3    | Memory Block Function                                                                   | 123 |

|        | 5.3.1 Chip select control function                                                      |     |

| 5.4    | Bus Access                                                                              |     |

|        | 5.4.1 Number of clocks for access                                                       | 125 |

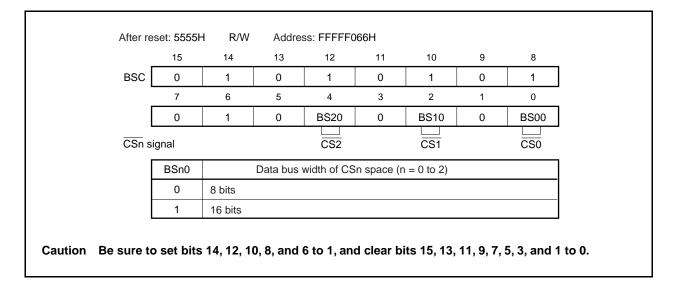

|        | 5.4.2 Bus size setting function                                                         | 125 |

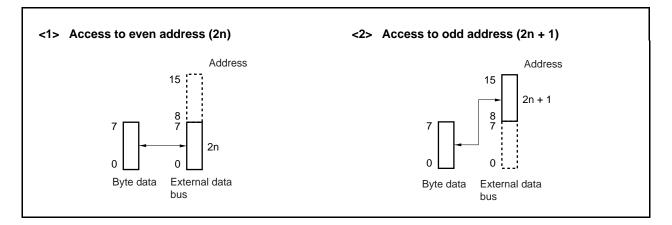

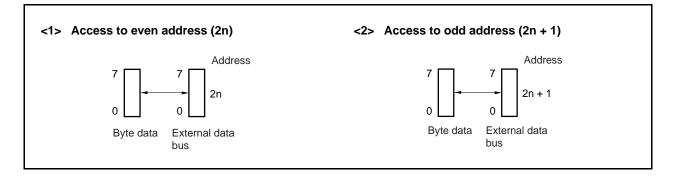

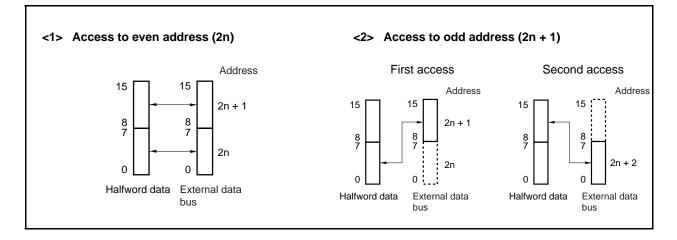

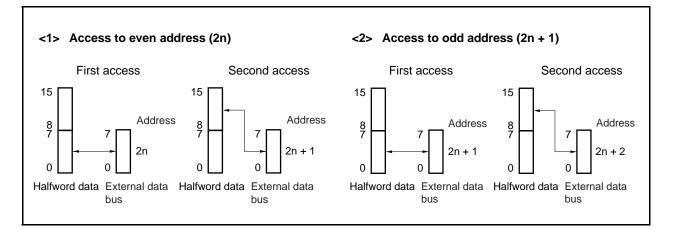

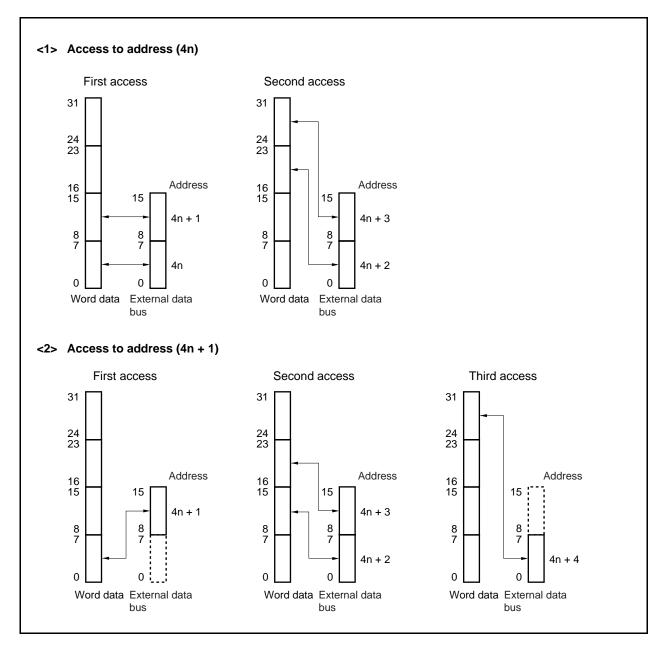

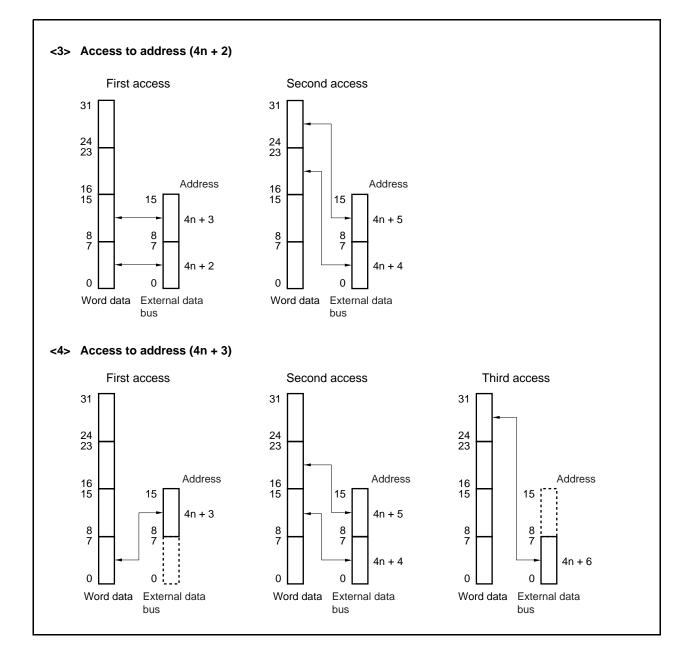

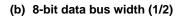

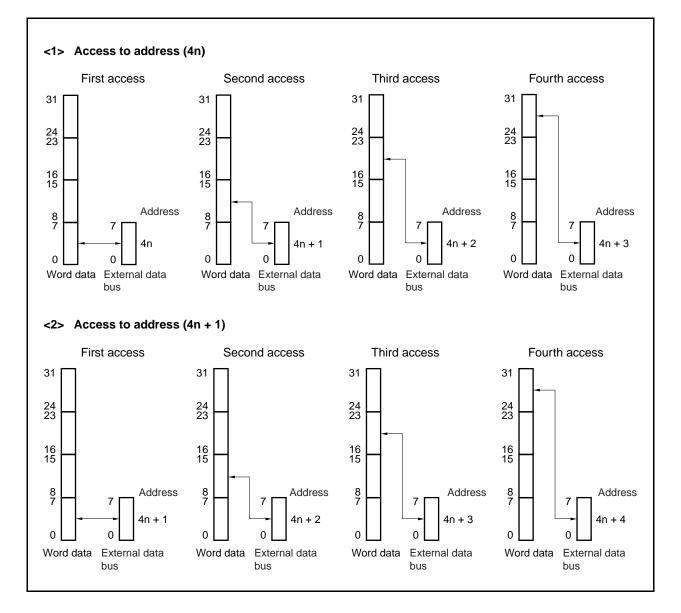

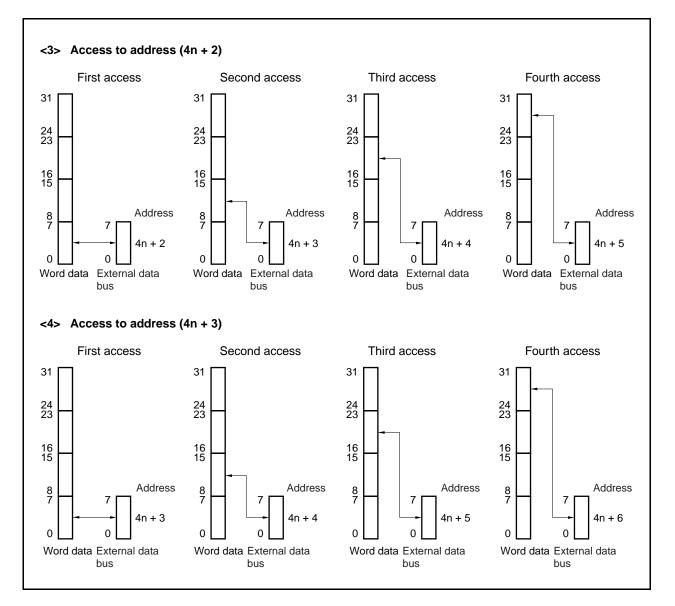

|        | 5.4.3 Access by bus size                                                                |     |

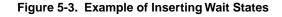

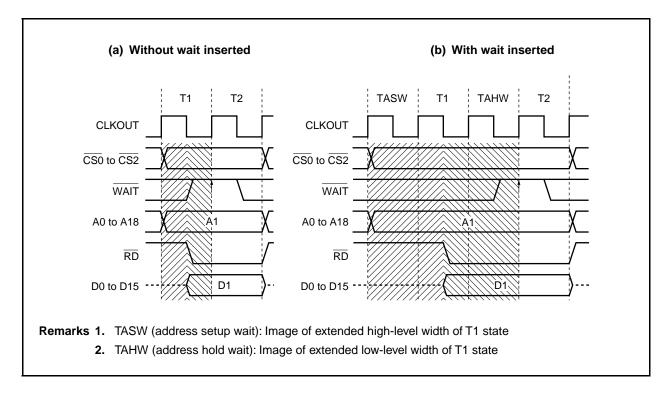

| 5.5    | Wait Function                                                                           | 133 |

|        | 5.5.1 Programmable wait function                                                        | 133 |

|        | 5.5.2 External wait function                                                            | 134 |

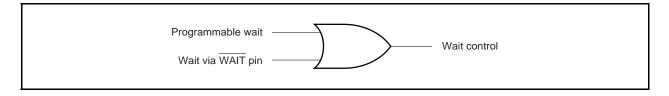

|        | 5.5.3 Relationship between programmable wait and external wait                          | 134 |

|        | 5.5.4 Programmable address wait function                                                | 135 |

| 5.6    | Idle State Insertion Function                                                           | 136 |

| 5.7    | Bus Priority                                                                            | 137 |

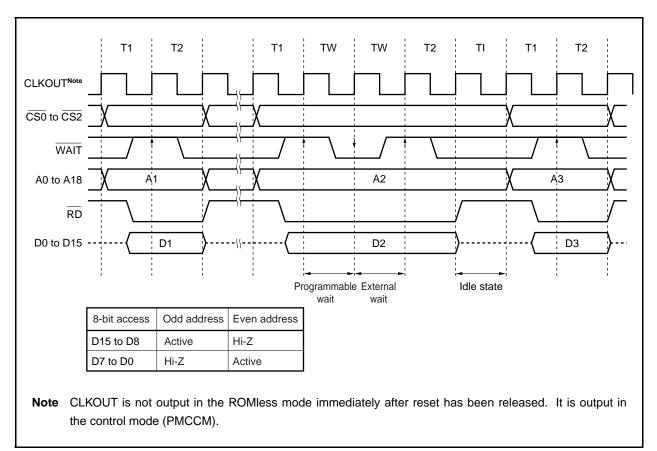

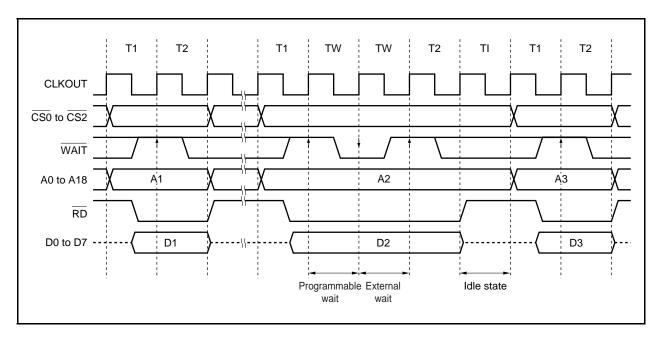

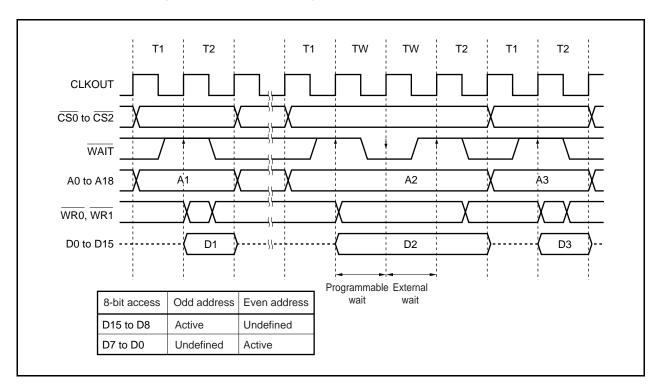

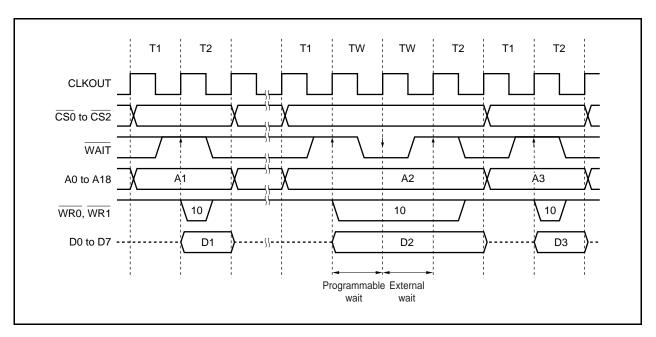

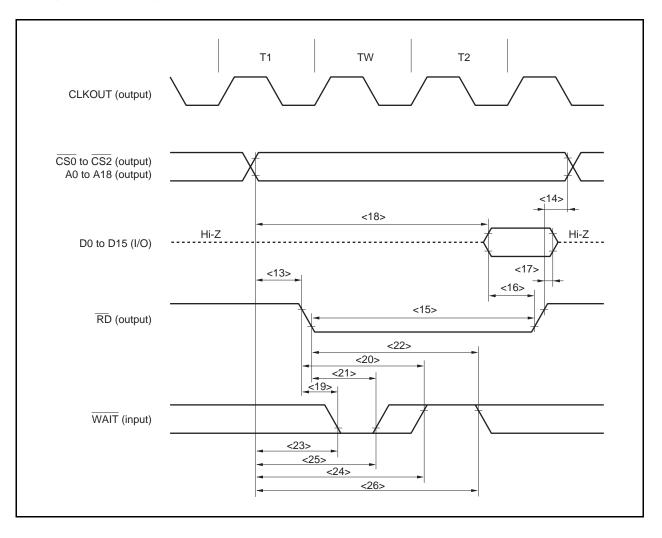

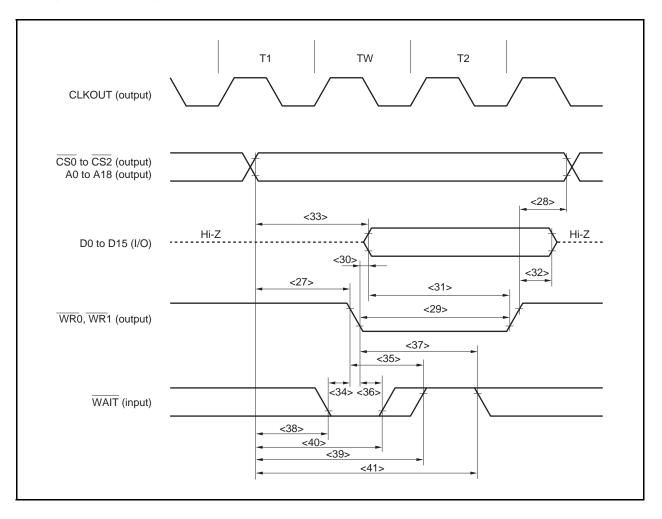

| 5.8    | Bus Timing                                                                              | 138 |

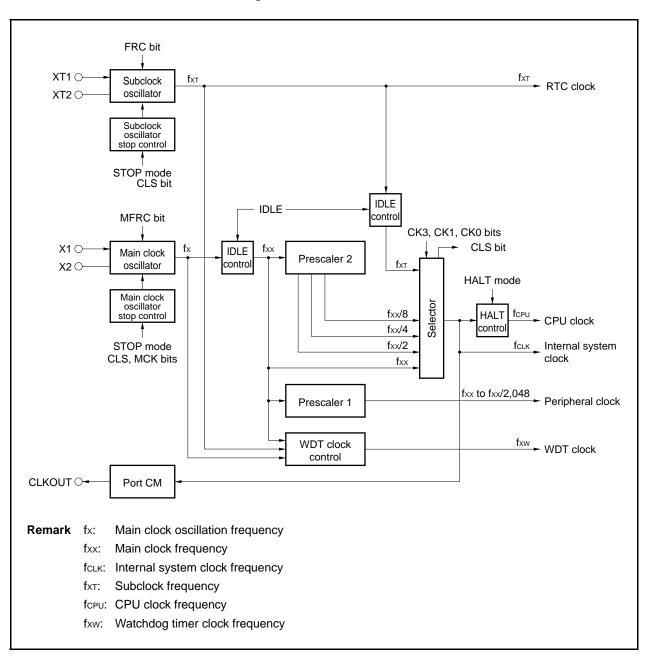

| CHAPTE | R 6 CLOCK GENERATION FUNCTION                                                           | 141 |

| 6.1    | Overview                                                                                | 141 |

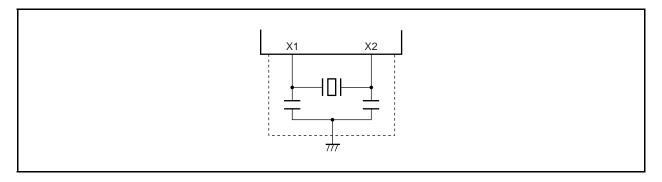

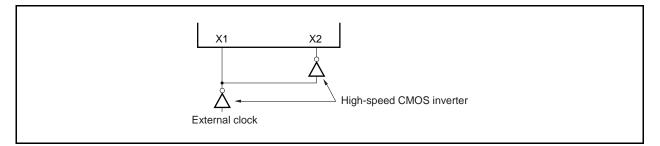

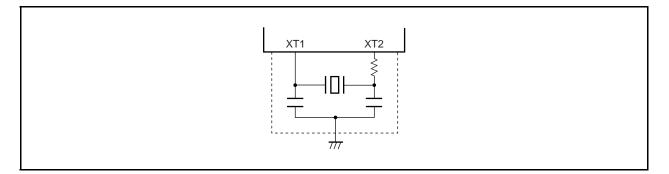

| 6.2    | Configuration                                                                           | 142 |

| 6.3    | Registers                                                                               | 144 |

| 6.4    | Operation                                                                               |     |

|        | 6.4.1 Operation of each clock                                                           |     |

|        | 6.4.2 Clock output function                                                             |     |

|        | 6.4.3 External clock input function                                                     | 147 |

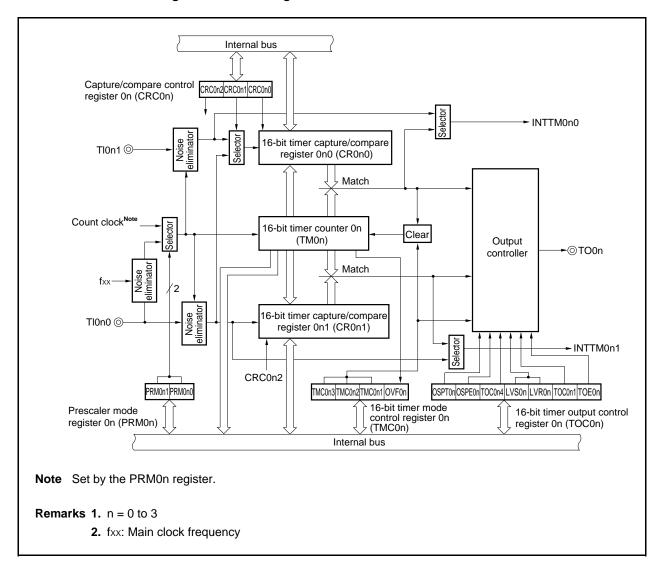

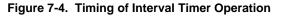

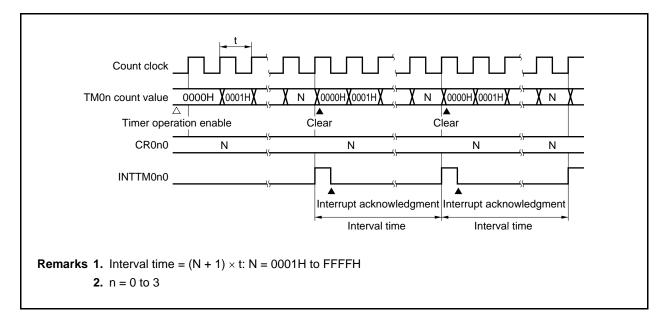

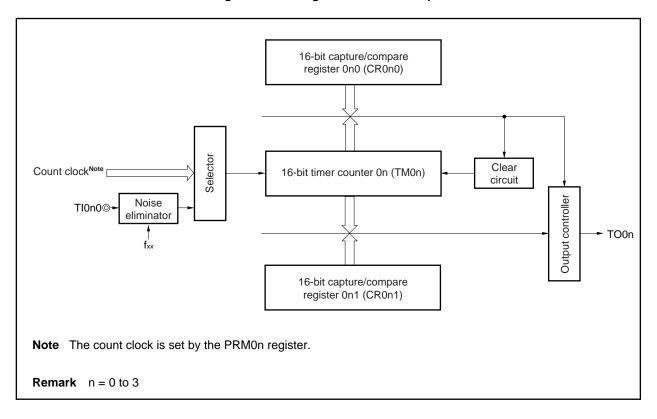

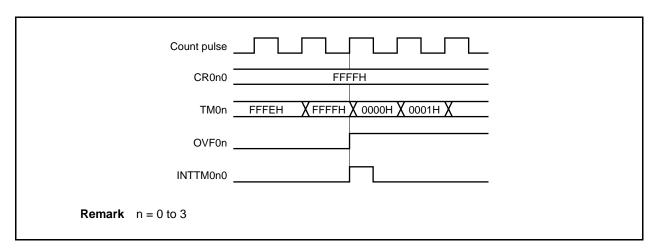

| CHAPTE | R 7 16-BIT TIMER/EVENT COUNTERS 00 TO 03                                                | 148 |

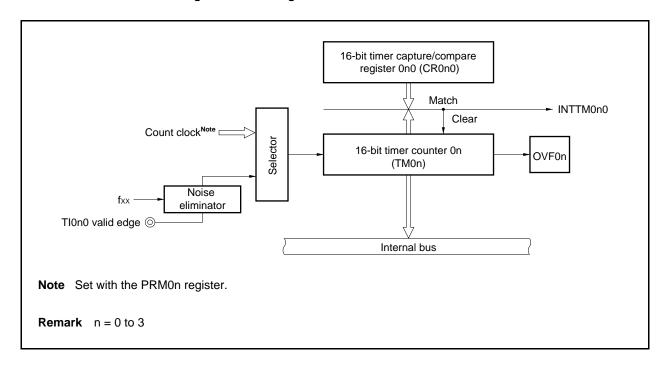

| 7.1    | Functions                                                                               | 148 |

| 7.2    | Configuration                                                                           |     |

| ••     |                                                                                         |     |

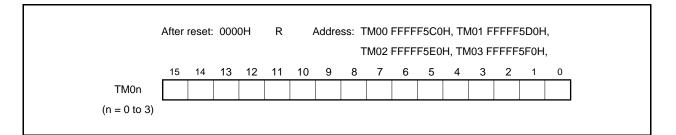

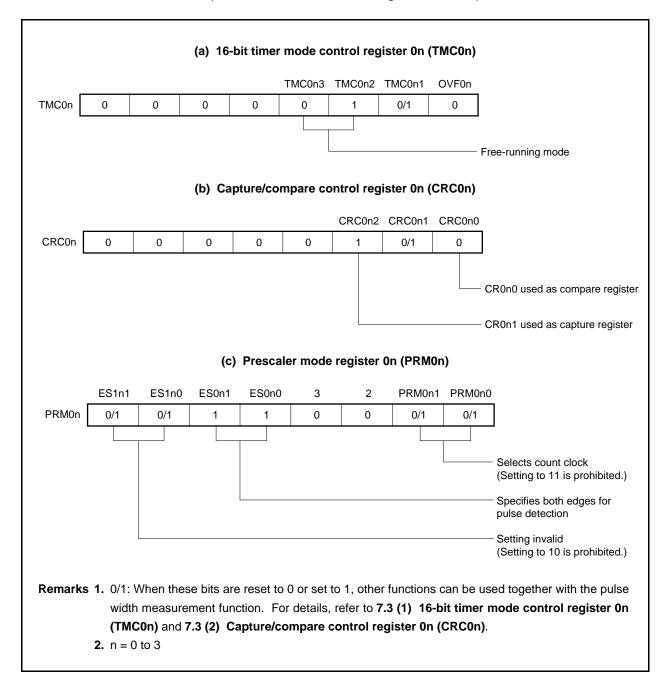

| 7.3    | Registers                                                                               | 153 |

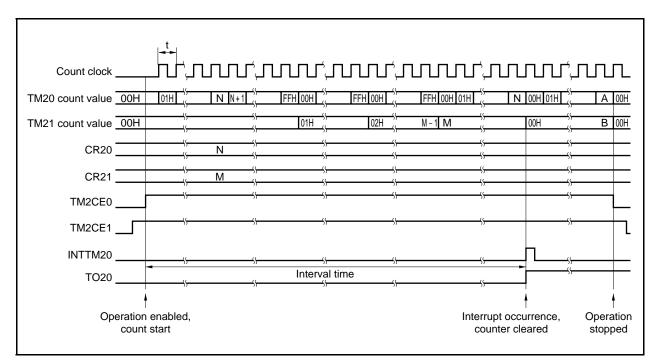

|        | Registers<br>Operation of 16-Bit Timer/Event Counter 0n                                 |     |

$\star$

$\star$

$\star$

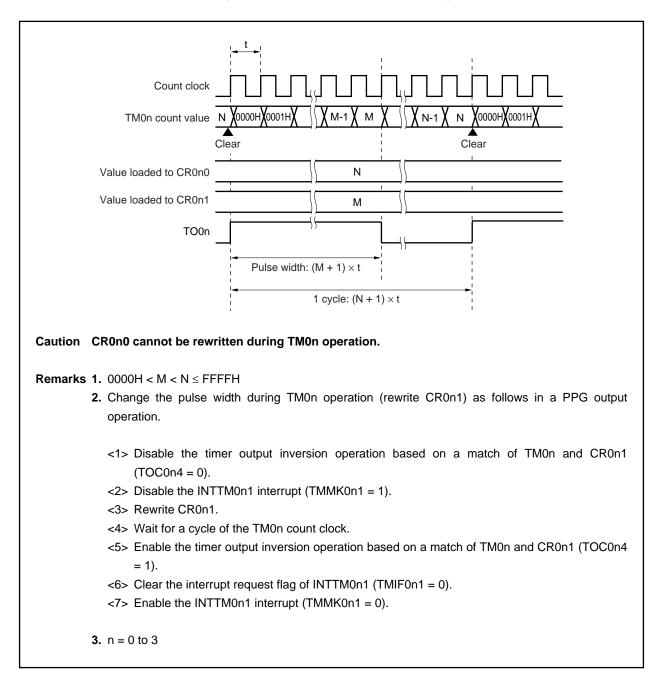

| 7.4.2 | PPG output operation                |  |

|-------|-------------------------------------|--|

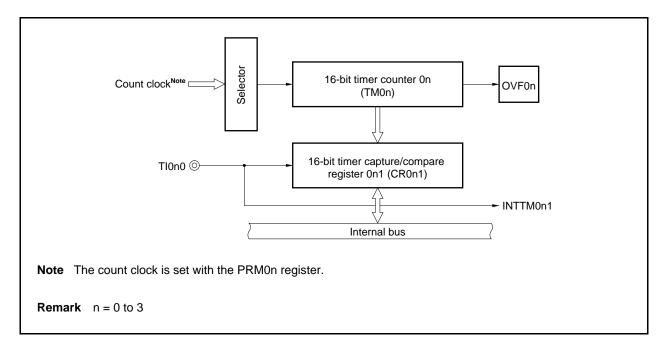

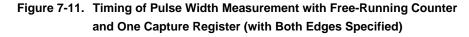

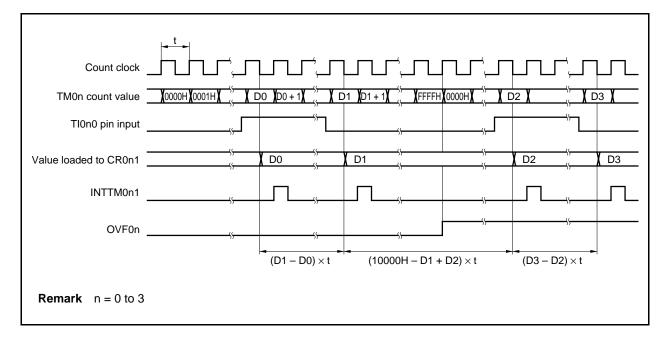

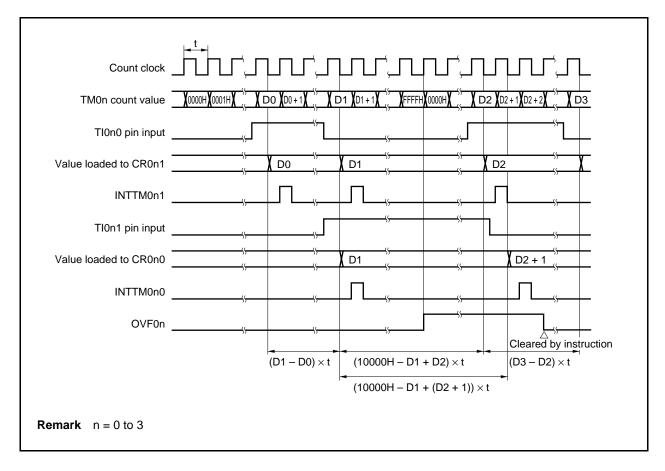

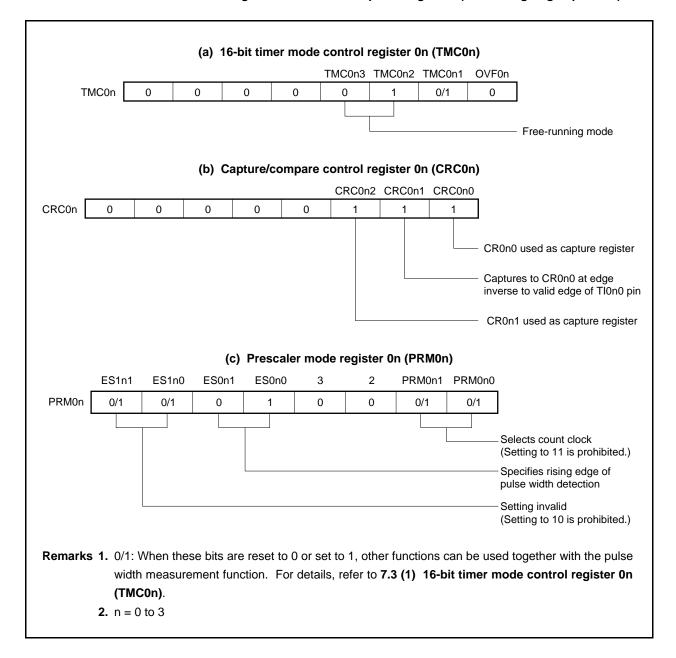

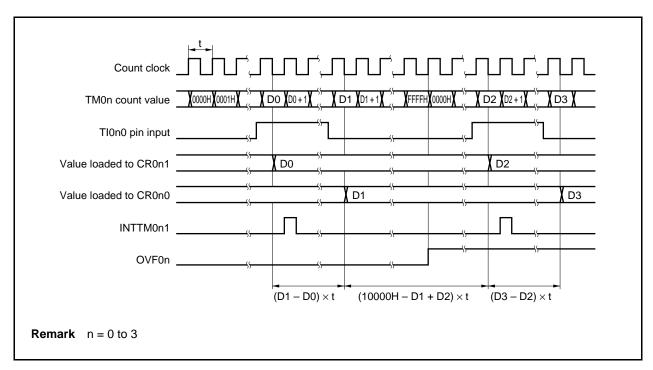

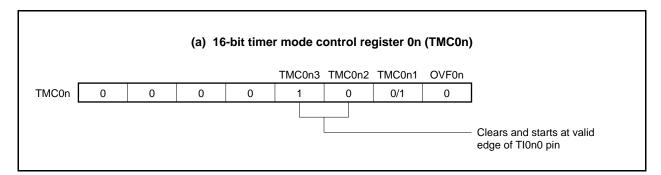

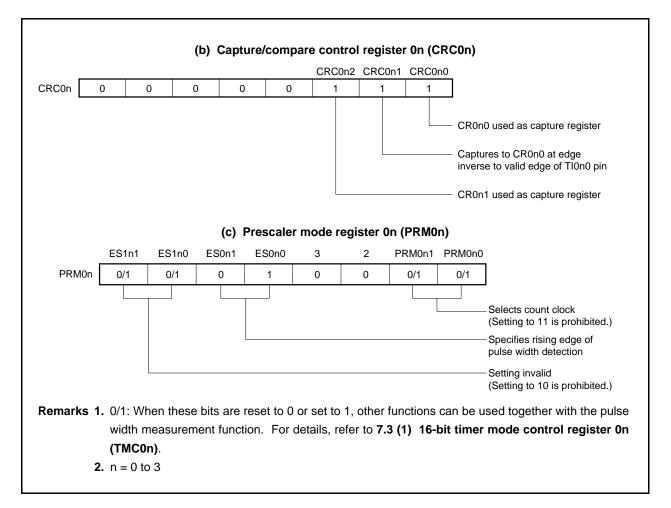

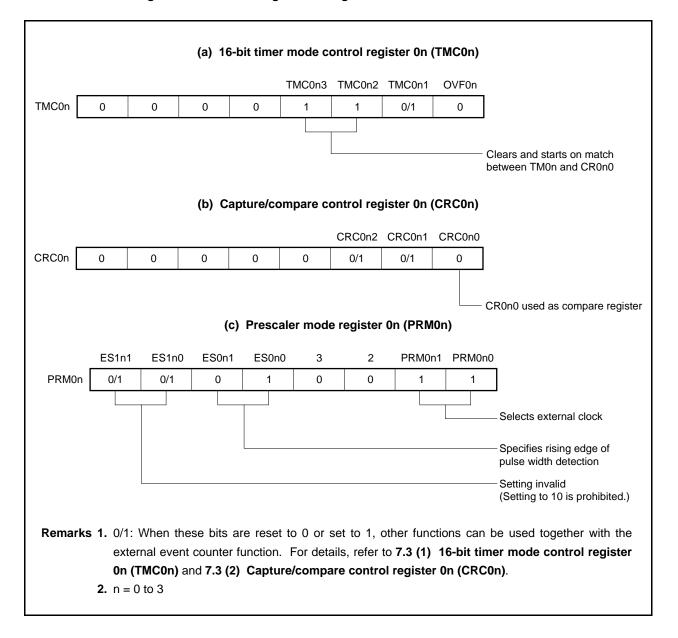

| 7.4.3 | Pulse width measurement             |  |

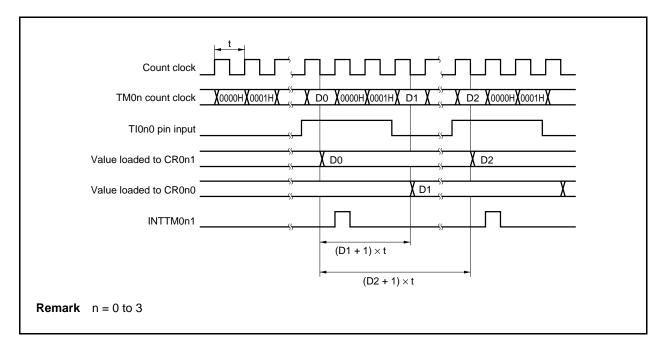

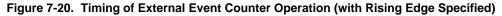

| 7.4.4 | Operation as external event counter |  |

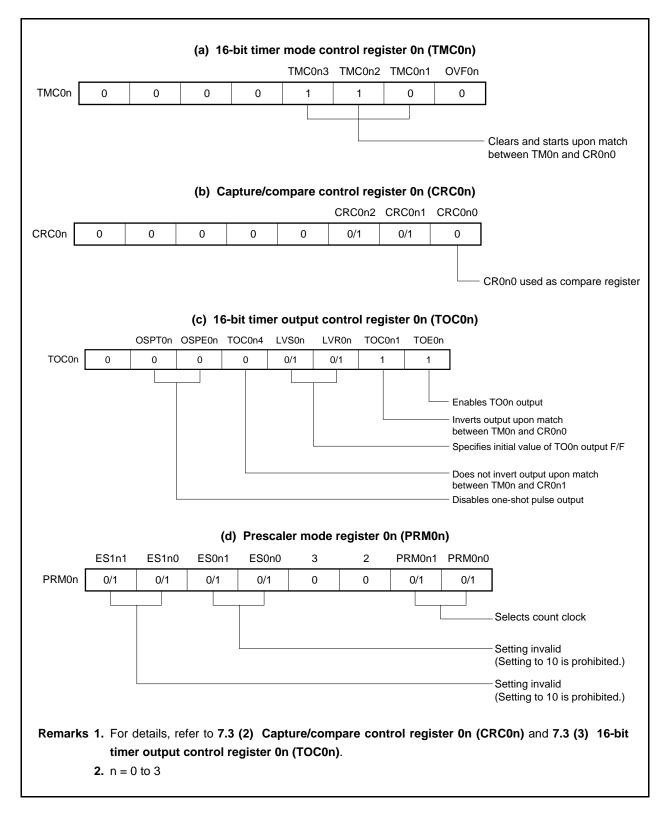

| 7.4.5 | Square-wave output operation        |  |

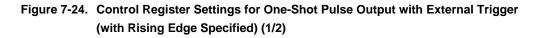

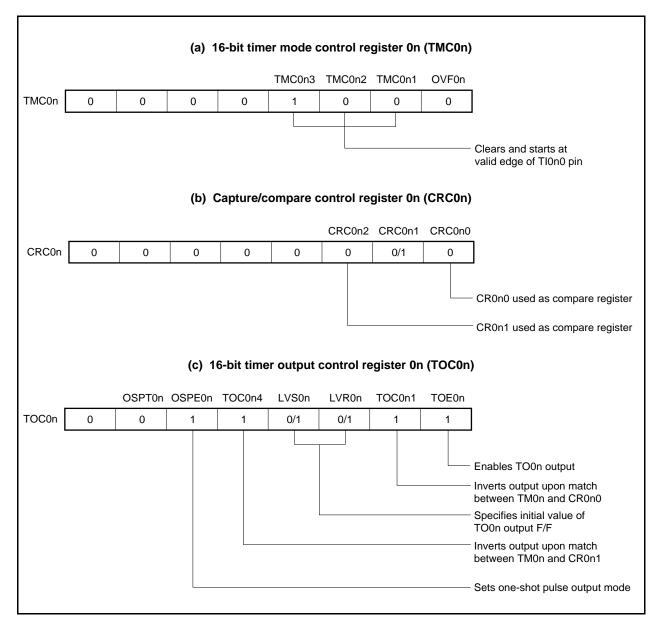

| 7.4.6 | One-shot pulse output operation     |  |

| 7.4.7 | Cautions                            |  |

|       |                                     |  |

|       |                                     |  |

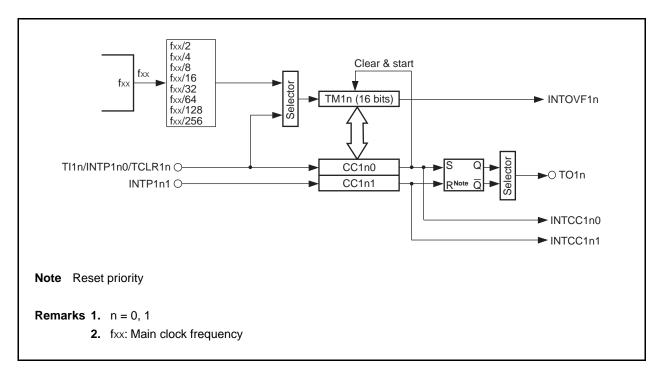

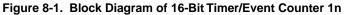

#

| 8.1 | Features             | 190 |

|-----|----------------------|-----|

| 8.2 | Function Overview    | 190 |

| 8.3 | Configuration        | 191 |

|     | Registers            |     |

|     | Operation            |     |

|     | Application Examples |     |

|     | Cautions             |     |

#### 9.1 9.2 9.3 9.4 9.4.1 9.4.2 9.4.3 Square-wave output operation (8-bit resolution)......228 9.4.4 9.4.5 as external event counter (46 bit-) ~ . .

|     | • a a a a |                                                  |     |

|-----|-----------|--------------------------------------------------|-----|

| 9.5 | Cautio    | ns                                               | 237 |

|     | 9.4.7     | Square-wave output operation (16-bit resolution) | 236 |

|     | 9.4.6     | Operation as external event counter (16 bits)    | 235 |

#

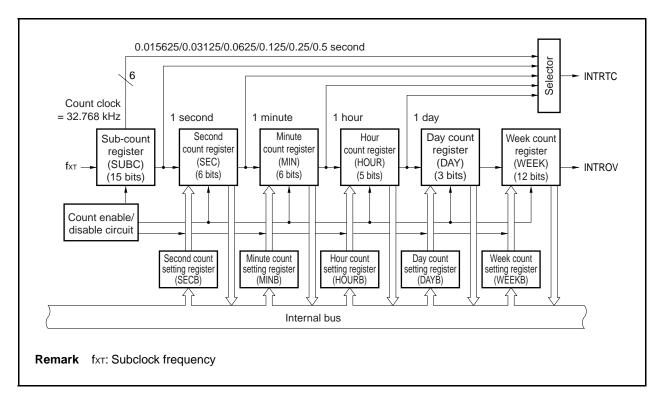

| 10.1 | Functi    | ons                                         | 238 |

|------|-----------|---------------------------------------------|-----|

| 10.2 | Config    | uration                                     |     |

|      | -         | ers                                         |     |

|      | Operation |                                             |     |

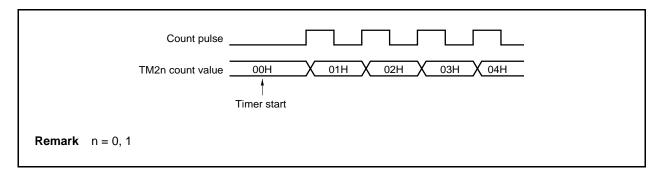

|      | 10.4.1    | Initializing counter and count-up           | 245 |

|      | 10.4.2    | Rewriting counter                           | 245 |

|      | 10.4.3    | Controlling interrupt request signal output | 245 |

|      | 10.4.4    | Notes                                       | 246 |

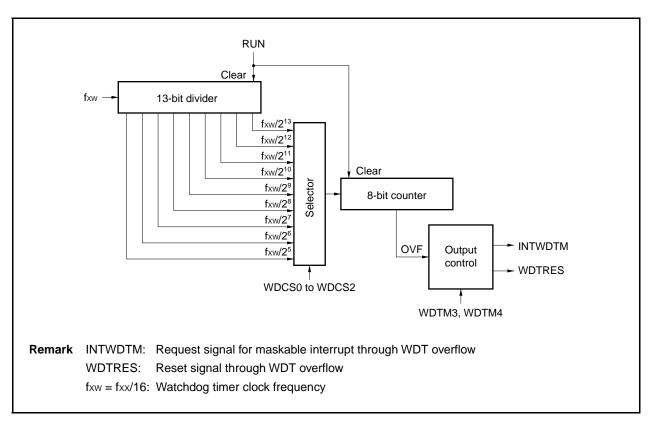

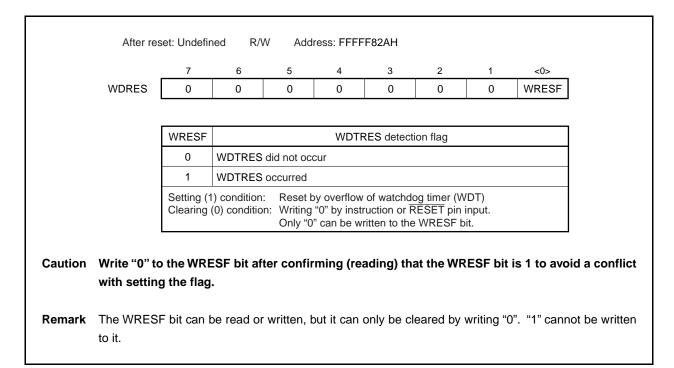

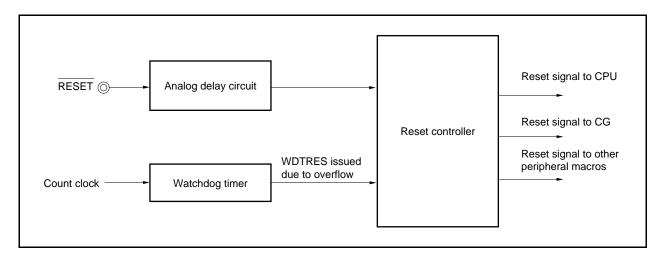

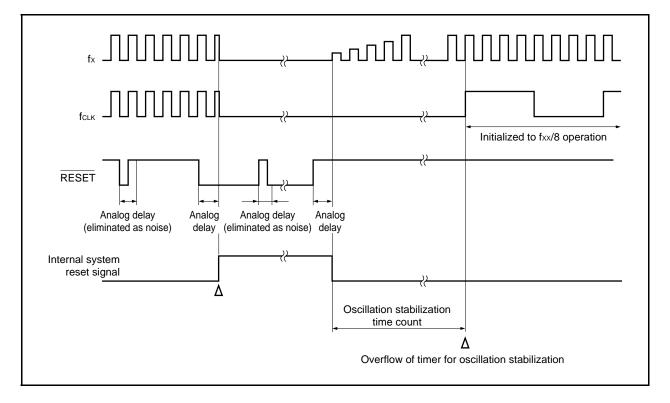

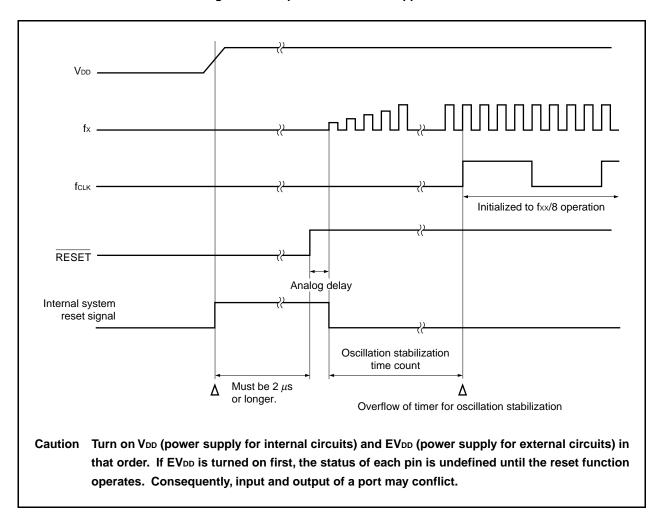

| CHAPTE | R 11 WATCHDOG TIMER FUNCTIONS | 247 |

|--------|-------------------------------|-----|

| 11.1   | Functions                     | 247 |

| 11.2   | Configuration                 | 248 |

|        | Registers                     |     |

| 11.4   | Operation                     | 251 |

|        |                               |     |

|         | 11.4.1  | Operation as watchdog timer              |     |

|---------|---------|------------------------------------------|-----|

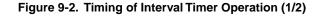

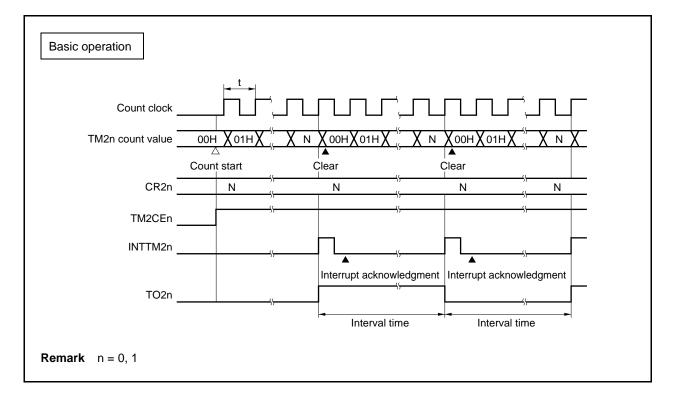

|         | 11.4.2  | Operation as interval timer              |     |

|         | 11.4.3  | Monitoring reset by watchdog timer (WDT) |     |

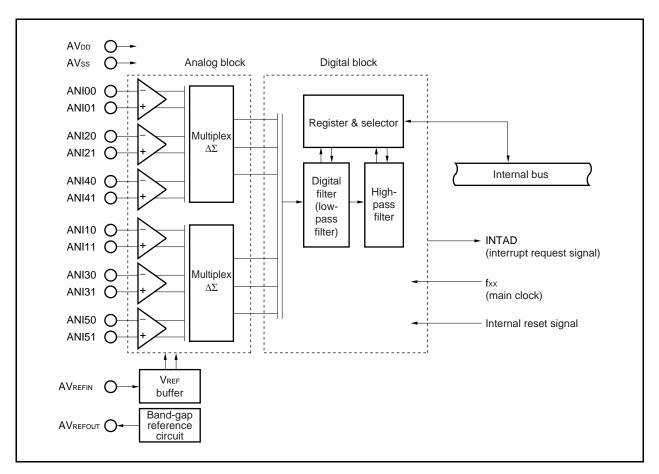

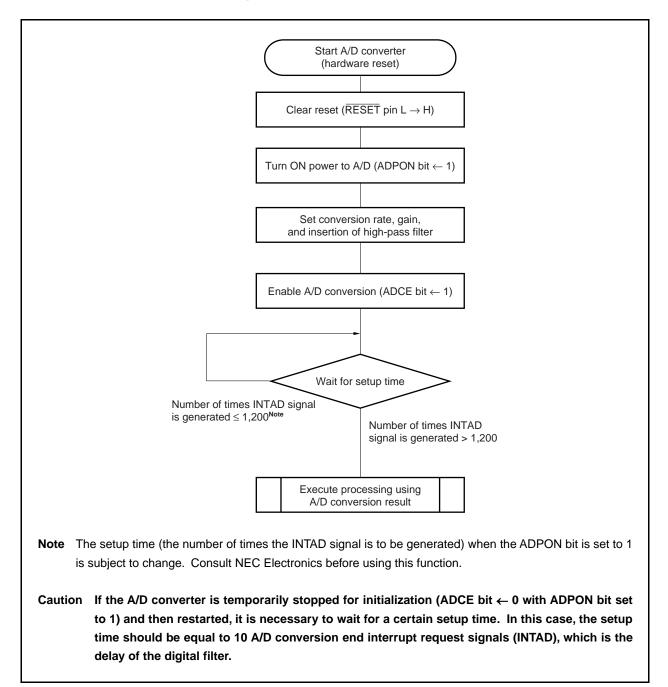

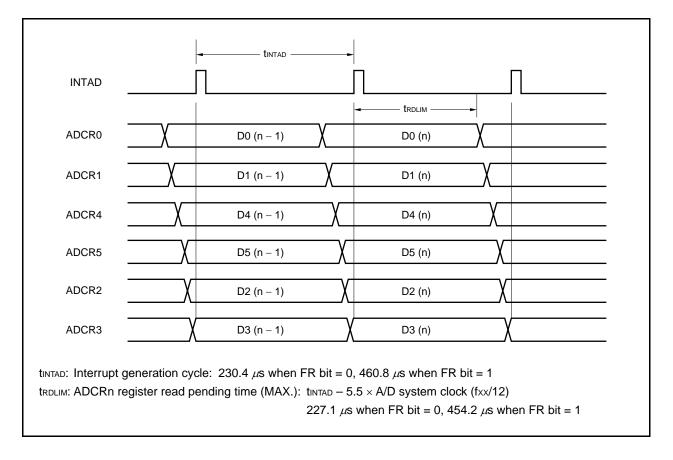

|         | ) 10 A  | /D CONVERTER                             | 254 |

|         |         |                                          |     |

| 12.1    |         | ons                                      |     |

| 12.2    | -       | juration                                 |     |

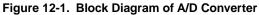

| 12.3    | -       | ers                                      |     |

| 12.4    | •       | tion                                     |     |

| 12.5    | Cautio  | ns                                       | 261 |

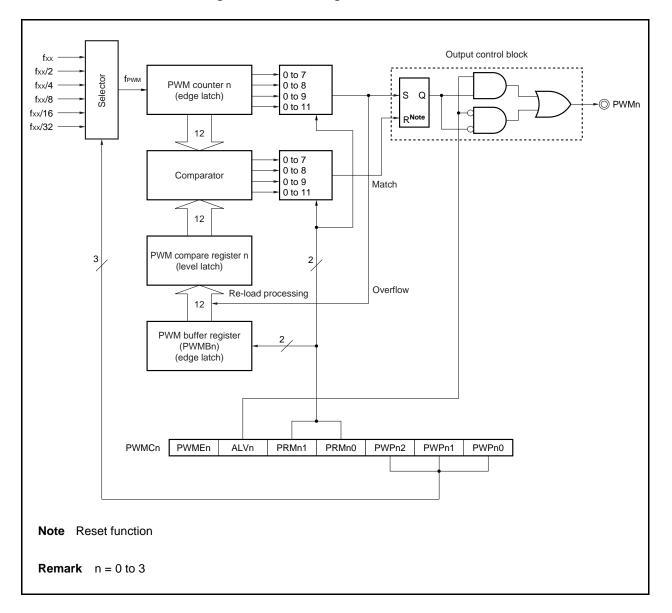

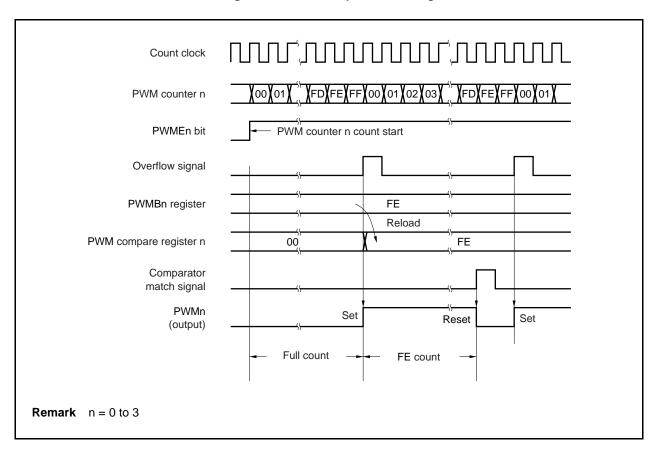

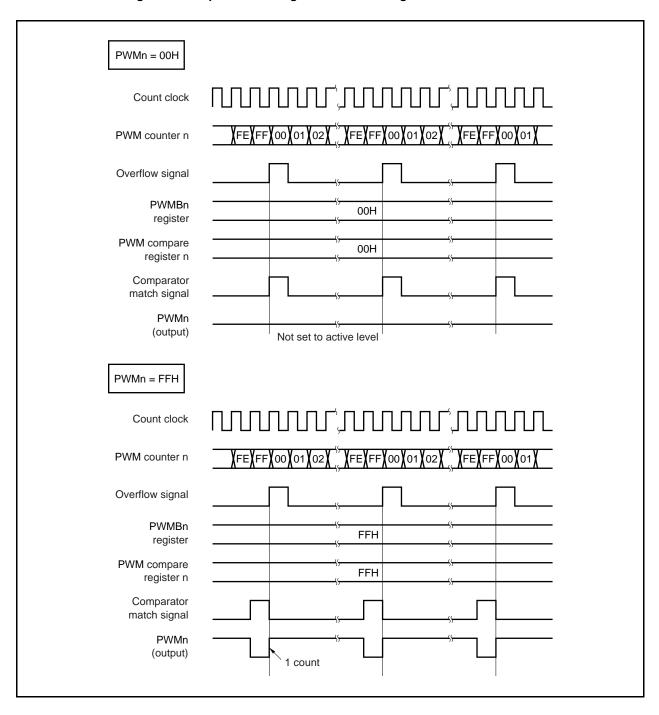

| CHAPTER | R 13 P  | WM FUNCTION                              |     |

| 13.1    | Featur  | es                                       |     |

| 13.2    | Config  | juration                                 |     |

| 13.3    | Regist  | ers                                      |     |

| 13.4    | Operat  | tion                                     |     |

|         | 13.4.1  | Basic operation                          |     |

|         | 13.4.2  | Repeat frequency                         |     |

| 13.5    | Cautio  | ns                                       |     |

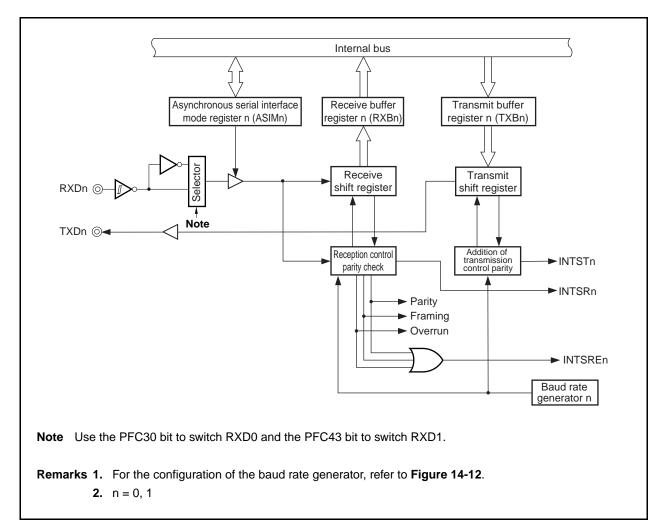

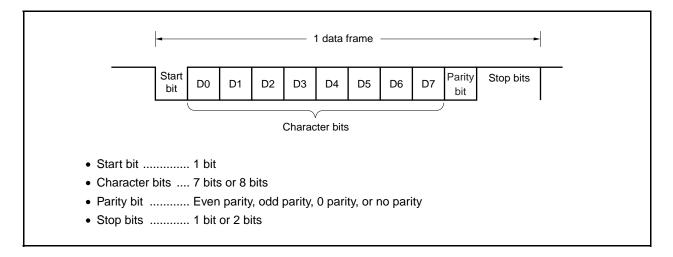

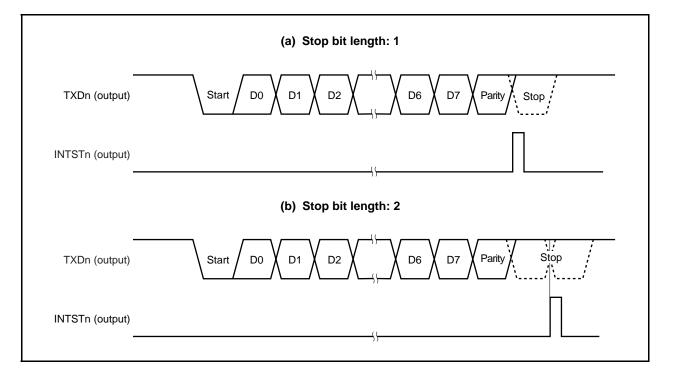

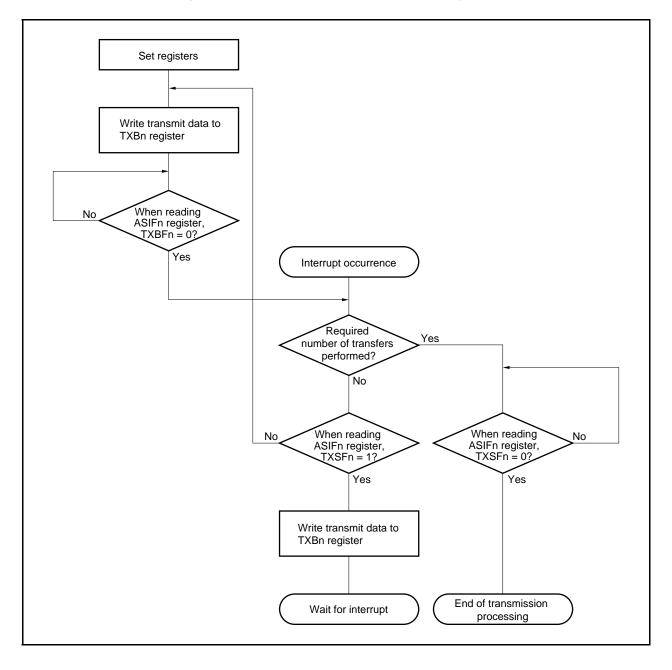

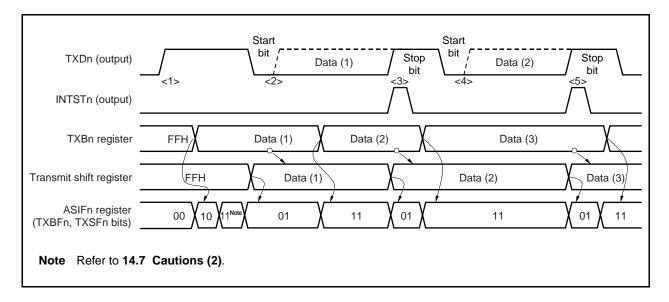

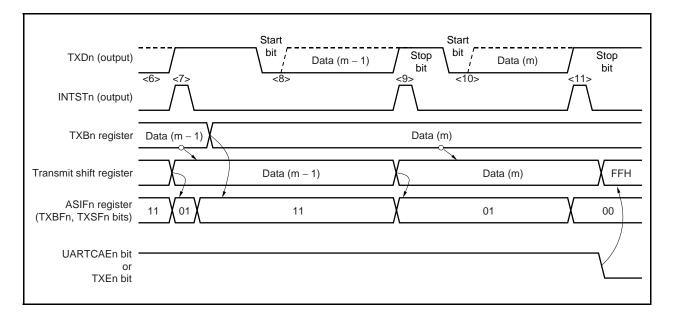

| CHAPTER | R 14 A  | SYNCHRONOUS SERIAL INTERFACE n (UARTn)   |     |

| 14.1    | Featur  | es                                       | 269 |

| 14.2    |         | juration                                 |     |

| 14.3    | -       | ers                                      |     |

| 14.4    | -       | ipt Requests                             |     |

| 14.5    |         | tion                                     |     |

| 14.6    | -       | ated Baud Rate Generator n (BRGn)        |     |

| 14.7    |         | ns                                       |     |

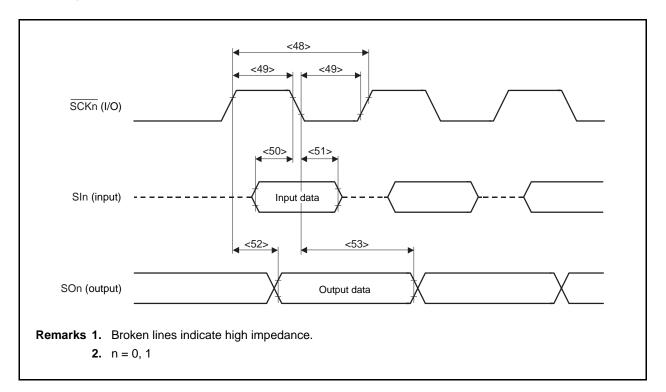

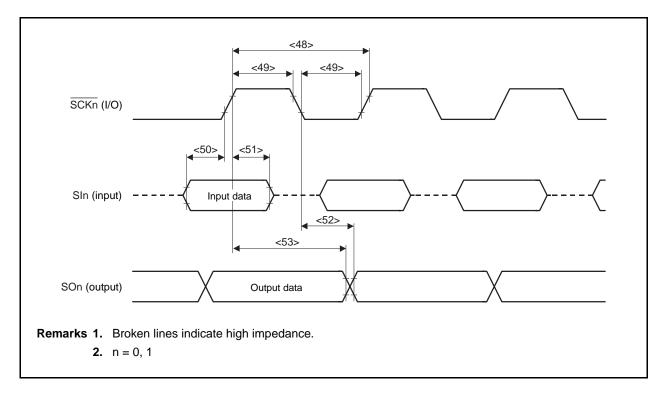

|         | 0 15 C  | LOCKED SERIAL INTERFACE n (CSIn)         | 300 |

|         |         |                                          |     |

| 15.1    |         | es                                       |     |

| 15.2    | -       | juration                                 |     |

|         | •       | ers                                      |     |

|         | -       | tion                                     |     |

|         | -       | t Pins                                   |     |

| 15.0    | Syster  | n Configuration Example                  |     |

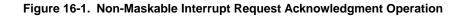

| CHAPTER | R 16 IN | TERRUPT/EXCEPTION PROCESSING FUNCTION    |     |

| 16.1    | Featur  | es                                       |     |

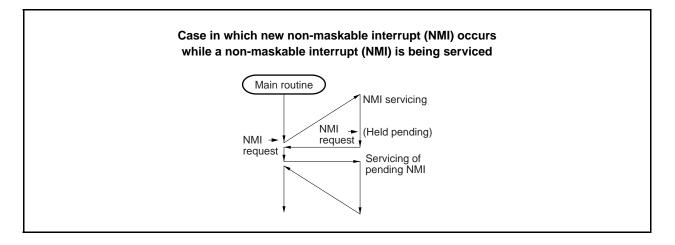

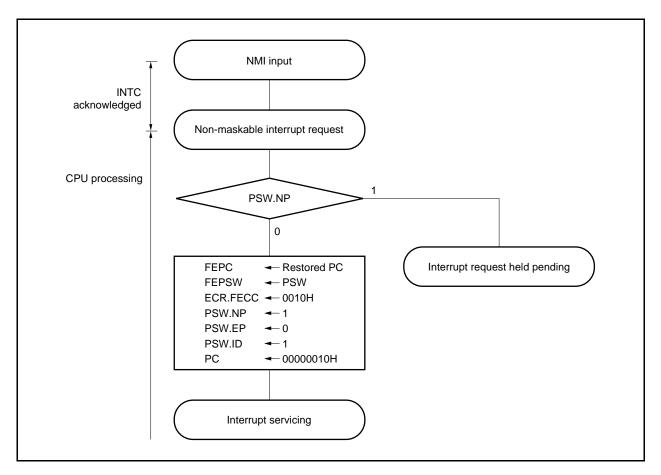

| 16.2    | Non-M   | askable Interrupts                       |     |

|         | 16.2.1  | Operation                                |     |

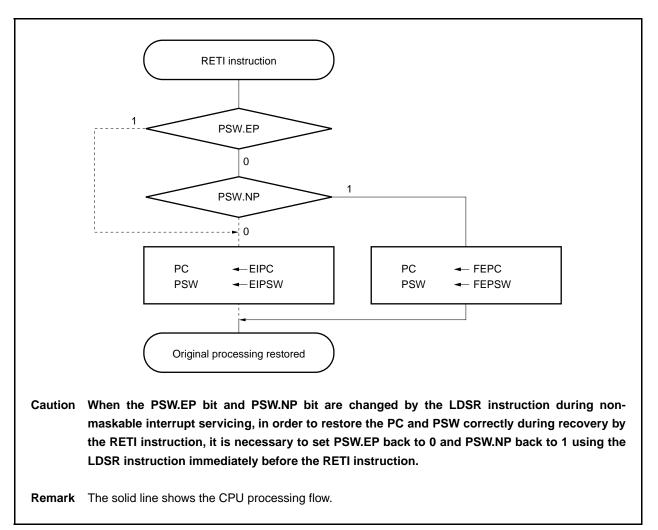

|         | 16.2.2  | Restore                                  |     |

|         | 16.2.3  | NP flag                                  |     |

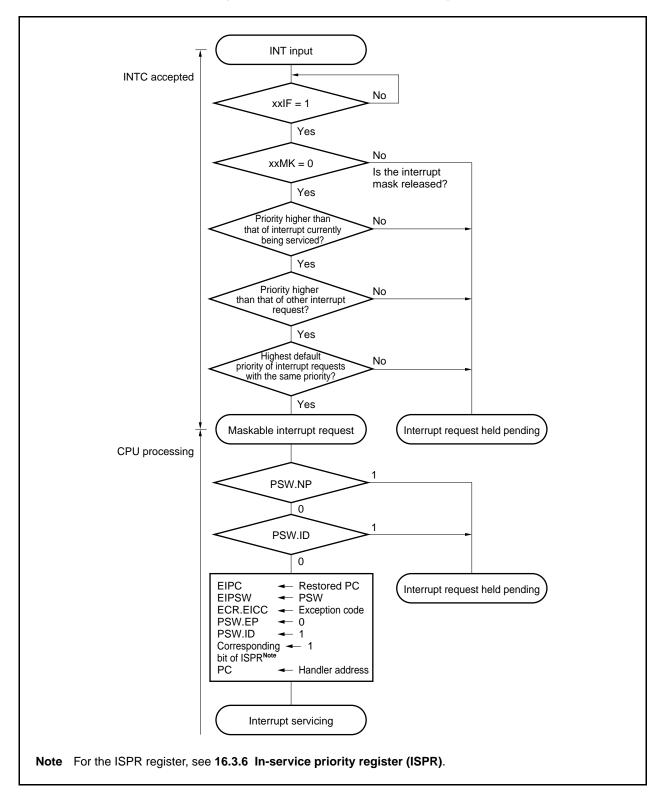

| 16.3    | Maska   | ble Interrupts                           |     |

|            |                                                                      | 16.3.1 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

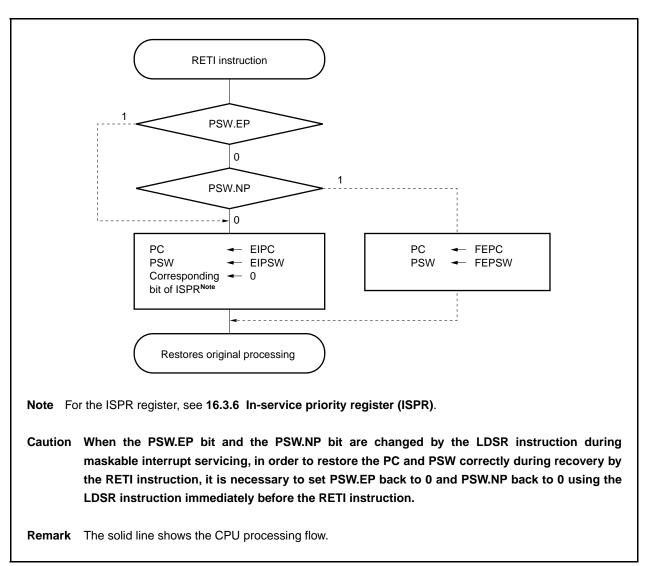

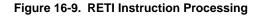

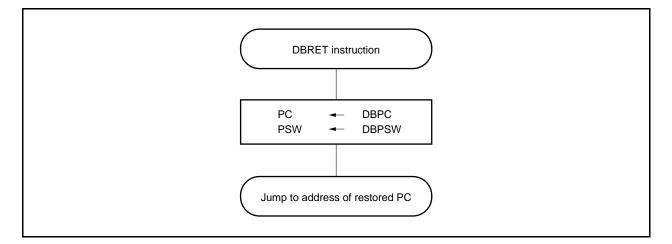

|            |                                                                      | 16.3.2 Restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

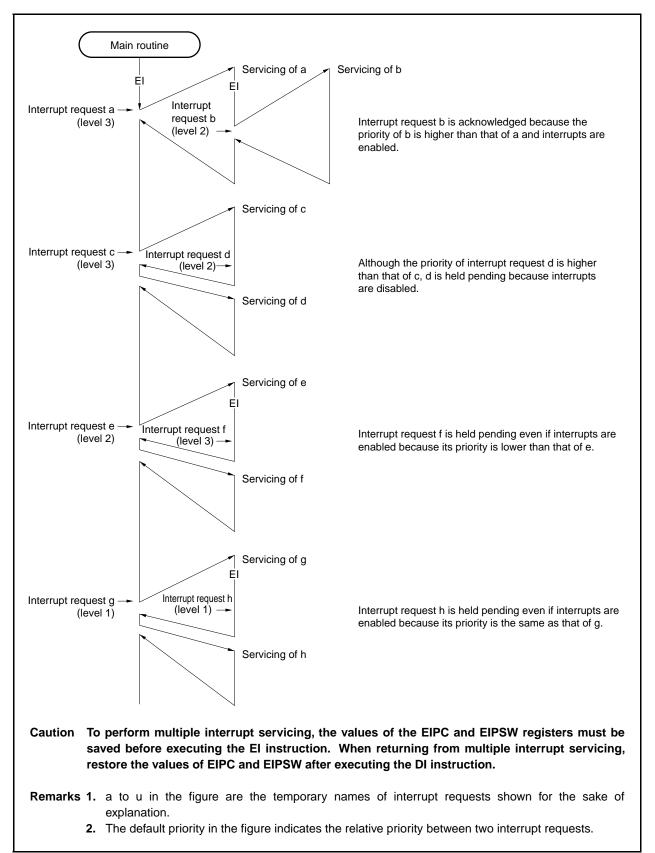

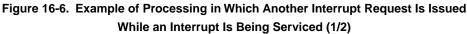

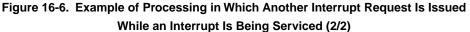

|            |                                                                      | 16.3.3 Priorities of maskable interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

|            |                                                                      | 16.3.4 Interrupt control register (xxICn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

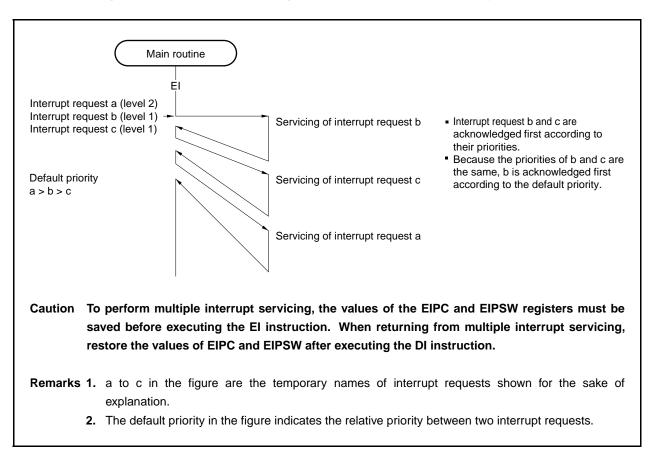

|            |                                                                      | 16.3.5 Interrupt mask registers 0, 1 (IMR0, IMR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|            |                                                                      | 16.3.6 In-service priority register (ISPR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

|            |                                                                      | 16.3.7 ID flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

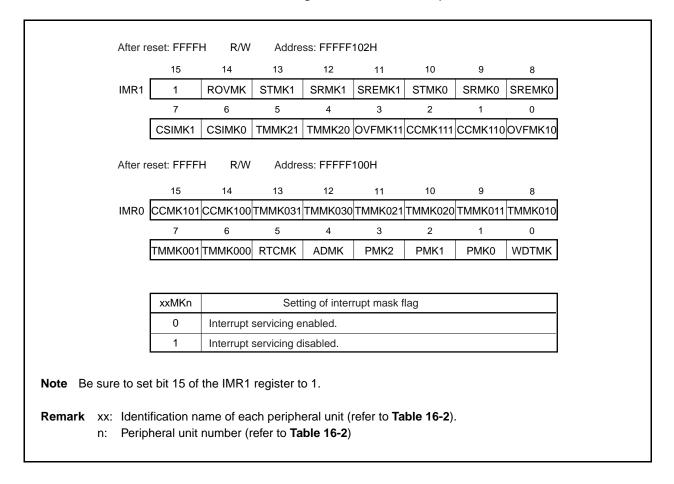

|            | 16.4                                                                 | External Interrupt Request Input Pins (NMI, INTP0 to INTP2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 330               |

|            |                                                                      | 16.4.1 Noise elimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

|            |                                                                      | 16.4.2 Edge detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

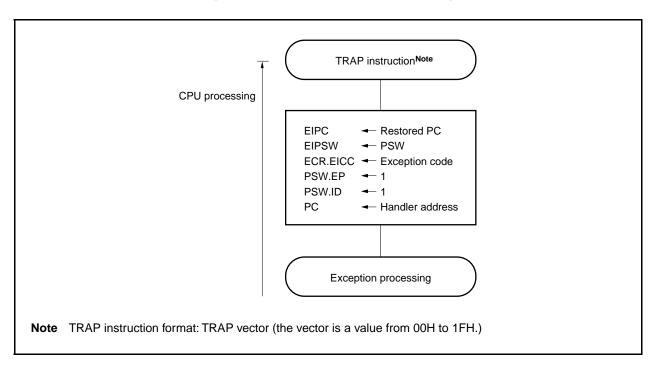

|            | 16.5                                                                 | Software Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 332               |

|            |                                                                      | 16.5.1 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|            |                                                                      | 16.5.2 Restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

|            |                                                                      | 16.5.3 Exception status flag (EP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

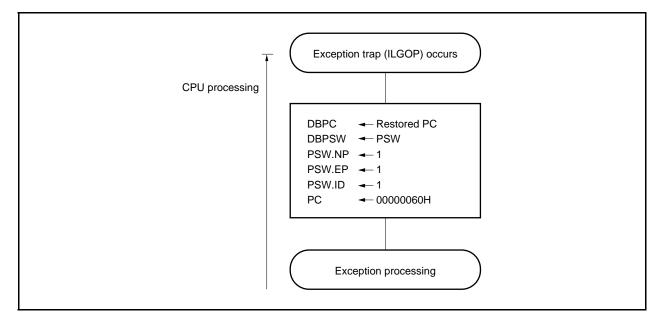

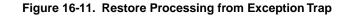

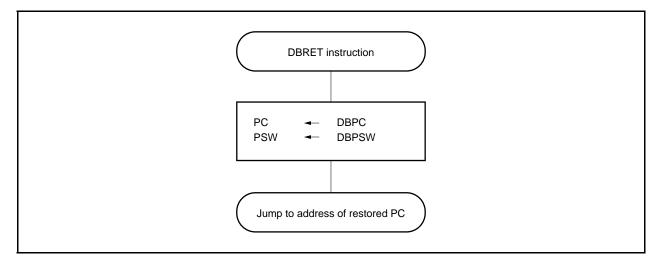

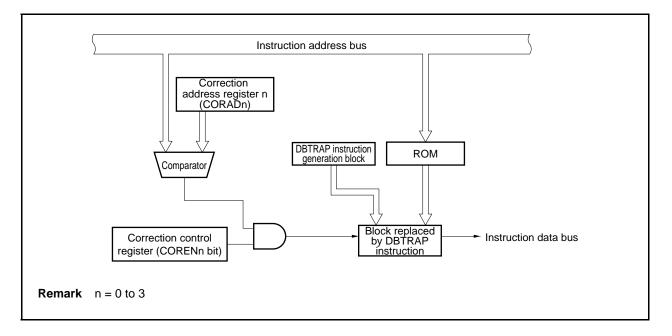

|            | 16.6                                                                 | Exception Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 335               |

|            |                                                                      | 16.6.1 Illegal opcode definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|            |                                                                      | 16.6.2 Debug trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

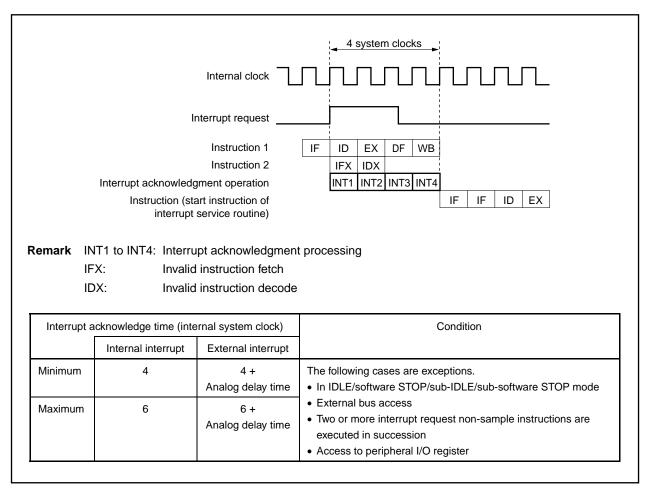

|            | 16.7                                                                 | Interrupt Acknowledge Time of CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 339               |

|            | 10.7                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 240               |

|            |                                                                      | Periods in Which Interrupts Are Not Acknowledged by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|            | 16.8                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| СНА        | 16.8                                                                 | Periods in Which Interrupts Are Not Acknowledged by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 341               |

| СНА        | 16.8<br>PTER                                                         | Periods in Which Interrupts Are Not Acknowledged by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

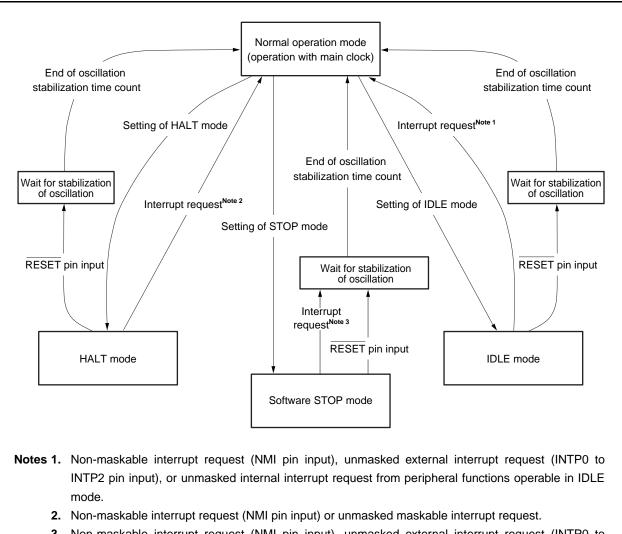

| СНА        | 16.8<br>PTER<br>17.1<br>17.2                                         | Periods in Which Interrupts Are Not Acknowledged by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 341<br>341<br>344 |

| СНА        | 16.8<br>PTER<br>17.1<br>17.2                                         | Periods in Which Interrupts Are Not Acknowledged by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| СНА        | 16.8<br>PTER<br>17.1<br>17.2                                         | Periods in Which Interrupts Are Not Acknowledged by CPU<br>17 STANDBY FUNCTION<br>Overview<br>Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| CHA        | 16.8<br>.PTER<br>17.1<br>17.2<br>17.3                                | Periods in Which Interrupts Are Not Acknowledged by CPU<br>17 STANDBY FUNCTION<br>Overview<br>Registers<br>HALT Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| CHA        | 16.8<br>.PTER<br>17.1<br>17.2<br>17.3                                | Periods in Which Interrupts Are Not Acknowledged by CPU<br>17 STANDBY FUNCTION<br>Overview<br>Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| CHA        | 16.8<br>.PTER<br>17.1<br>17.2<br>17.3                                | Periods in Which Interrupts Are Not Acknowledged by CPU<br>17 STANDBY FUNCTION<br>Overview<br>Registers<br>HALT Mode<br>17.3.1 Setting and operation status<br>17.3.2 Releasing HALT mode<br>IDLE Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4                         | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4                         | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status         17.4.2 Releasing IDLE mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4                         | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status         17.4.2 Releasing IDLE mode         Software STOP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4                         | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status         17.4.2 Releasing IDLE mode         Software STOP Mode         17.5.1 Setting and operation status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

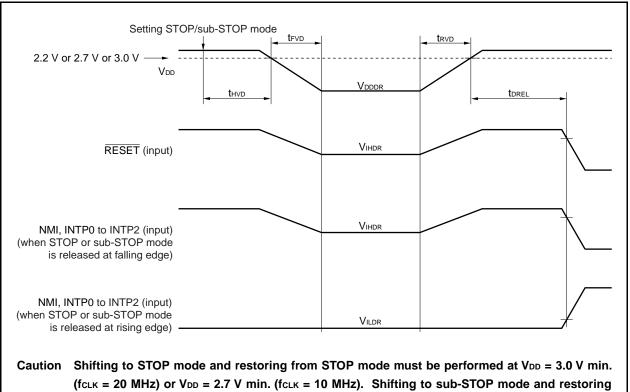

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4<br>17.5                 | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status         17.4.2 Releasing IDLE mode         Software STOP Mode         17.5.1 Setting and operation status         17.5.2 Releasing software STOP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4<br>17.5                 | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status         17.4.2 Releasing IDLE mode         Software STOP Mode         17.5.1 Setting and operation status         17.5.2 Releasing software STOP mode         Securing Oscillation Stabilization Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

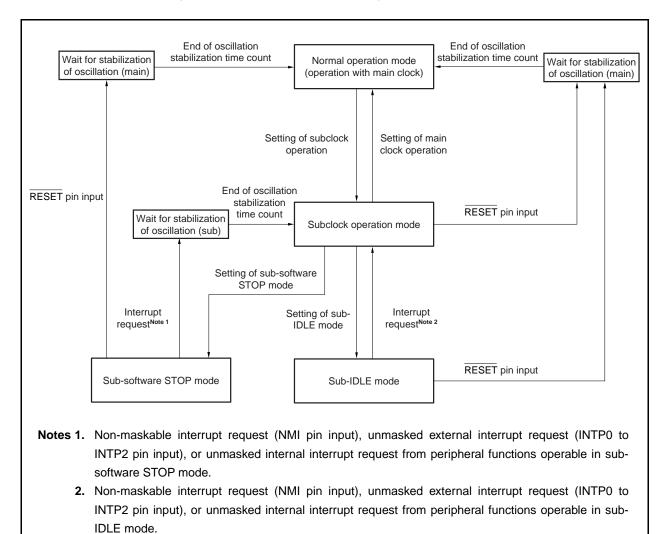

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4<br>17.5                 | Periods in Which Interrupts Are Not Acknowledged by CPU         17 STANDBY FUNCTION         Overview         Registers         HALT Mode         17.3.1 Setting and operation status         17.3.2 Releasing HALT mode         IDLE Mode         17.4.1 Setting and operation status         17.4.2 Releasing IDLE mode         Software STOP Mode         17.5.1 Setting and operation status         17.5.2 Releasing software STOP mode         Securing Oscillation Stabilization Time         Subclock Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

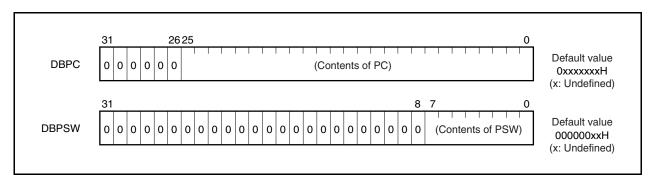

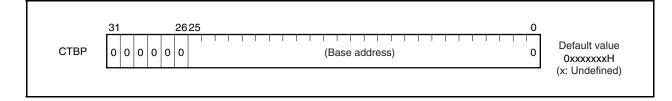

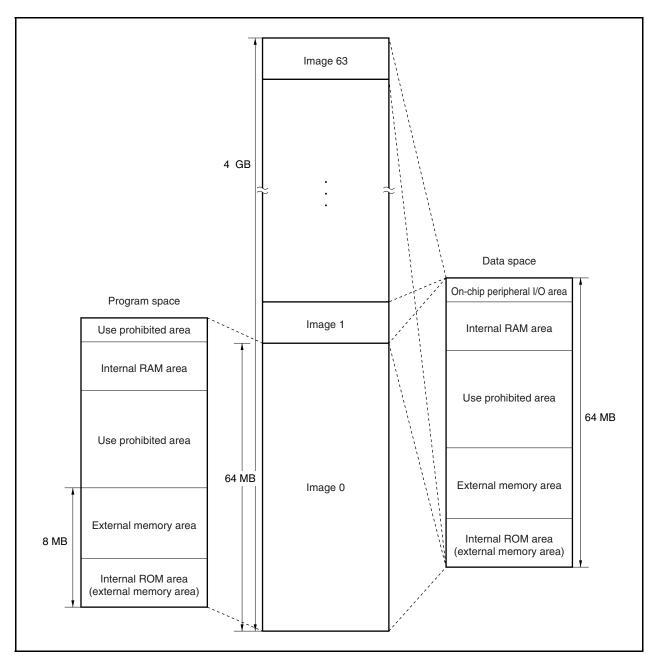

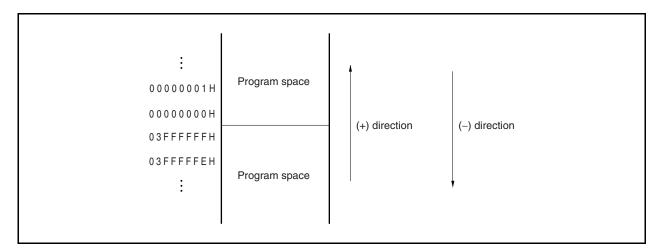

| CHA        | 16.8<br>PTER<br>17.1<br>17.2<br>17.3<br>17.4<br>17.5                 | Periods in Which Interrupts Are Not Acknowledged by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |