# AT&T CSP1088 GSM Conversion Signal Processor for Cellular Handset and Modem Applications v2.2

#### **Features**

- Seamless interface to the DSP1618 processor and W2020 RF transceiver

- Complete A/D and D/A functions for voiceband including digital audio interface

- Complete A/D and D/A functions for baseband

- Event timing and control state machine that monitors the internal quarter-bit counter and internal frame counter until a programmed time is reached, and then executes the control portion of the register and may issue an interrupt to the DSP

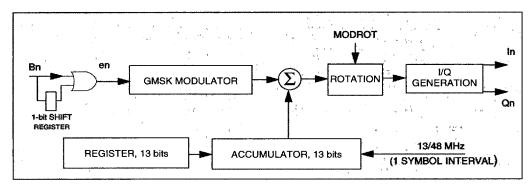

- GMSK modulator that takes 88 or 148 bits of burst data from an internal register and modulates it to GSM standards. Phase information is converted into I and Q output voltages that can be connected directly to a W2020 transceiver or RF modulator

- Received baseband I and Q signals are A/D converted and stored in a double buffer that holds 16 I and 16 Q samples before issuing an interrupt to the DSP to read the sample information

- 14 output control lines that can be used to control external circuits for such functions as power on/off or digital gain control

- Serial port that can be used to program an external RF frequency synthesizer

- Interrupt handling capabilities for voiceband samples, received baseband data as ciphering, timing and control interrupts, and for end of transmission notification

- Voiceband output connects directly to 15  $\Omega$

- Voiceband input connects directly to electret microphone

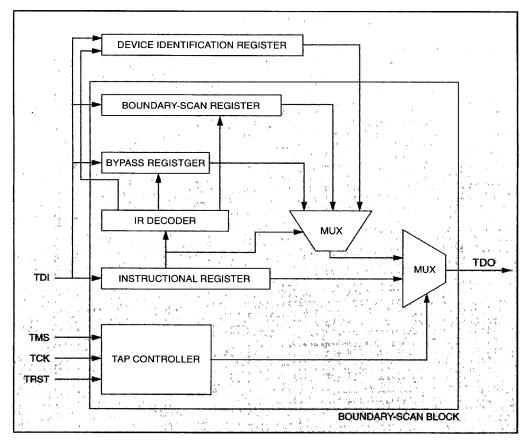

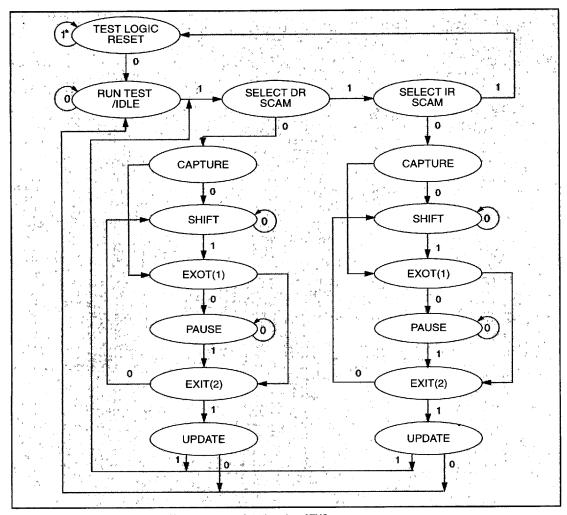

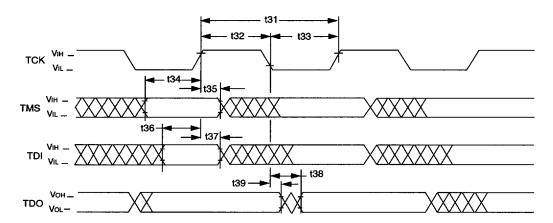

- IEEE\* 1149.1 JTAG controller and boundary scan register

- Hardware support for A5.1 and A5.2 ciphering

- Frequency synthesizer compatibility with DSP1618

# **Description**

The AT&T CSP1088 integrates the timing and control functions for GSM mobile application with the A/D and D/A functions. It serves as the interface that connects a DSP to the RF circuitry in a GSM mobile telephone.

For example, a DSP can load 148 bits of burst data into the AT&T CSP1088's internal register, and program the AT&T CSP1088's event timing and control register with the exact time to send the burst. When the timing portion of the event timing and control register matches the internal quarter-bit counter and internal frame counter, the 148 bits in the internal register are GMSK modulated to GSM standards, and the resulting phase information is translated into I and Q differential output voltages that can be connected directly to an RF modulator. An end-of-transmit interrupt notifies the DSP when the transmission is complete.

For receiving baseband data, a DSP can program the AT&T CSP1088's event timing and control register with the exact time to start receiving I and Q samples. When that time is reached, the control portion of the event timing and control register will start the baseband receive section converting I and Q sample pairs. The samples are stored in a double-buffered register until the register contains 16 sample pairs. The AT&T CSP1088 then issues an interrupt to the DSP which has ample time to read the information out before the next 16 sample pairs are stored.

The voiceband A/D converter issues an interrupt to the DSP whenever it finishes converting a 16-bit PCM word. The DSP then reads the new input sample and simultaneously loads the voiceband output D/A converter with a new PCM output word. The D/A output can be connected directly to a 15  $\Omega$  load or higher.

<sup>\*</sup> IEEE is a registered trade mark of The Institute of Electrical and Electronics Engineers, Inc.

# **Table of Contents**

| Contents Page                                                             | Contents                              | Page   |

|---------------------------------------------------------------------------|---------------------------------------|--------|

| Features13-1                                                              | Double-Buffered, 32-Sample I & Q Regi | sters, |

| Description13-1                                                           | RXBUFF[31:0]                          | 13-32  |

| Pin Information13-4                                                       | Frequency Synthesis                   |        |

| Architectural Information13-7                                             | Clock Output Control, CLKOCNTL        | 13-35  |

| Event Timing & Control State Machine13-7                                  | Baseband Input Section                |        |

| Send Burst Data13-7                                                       | Baseband Output and GMSK Modulation   |        |

| Receiving Burst Data13-8                                                  | Modulator Section                     |        |

| Voiceband Conversion13-9                                                  | Frequency Correction                  |        |

| Programming an External RF Frequency                                      | Output Timing and Power Ramp          |        |

| Synthesizer13-9                                                           | Output Common Mode                    |        |

| Output Control Lines13-9                                                  | Voiceband Input                       |        |

| Ciphering13-9                                                             | Analog Input Section                  |        |

| Frequency Synthesis13-9                                                   | A/D Modulator and Digital Filters     |        |

| Register Information13-11                                                 |                                       |        |

| Register Addresses (Memory Map)13-11                                      | Voiceband Output                      | 13-41  |

| General                                                                   | Programming an External RF            | 40.44  |

|                                                                           | Frequency Synthesizer                 |        |

| Interrupt Status and Interrupt Control Register, INS/INC13-11             | JTAG                                  |        |

| CSP1088 Control Register, CONTROL13-14                                    | Boundary-Scan Conformance             |        |

| Test Control Register, TEST13-17                                          | JTAG Test Port                        |        |

|                                                                           | DSP1600 Programming Examples          | 13-46  |

| Audio                                                                     | Device Characteristics                | 13-50  |

| Audio Input/Output Configuration Register,                                | Absolute Maximum Ratings              | 13-50  |

| AUDCONF13-18                                                              | Handling Precautions                  | 13-50  |

| Audio Input Double-Buffered Register,                                     | Recommended Operating Conditions      |        |

| AUDIN13-20 Audio Output Register, AUDOUT13-21                             | Package Thermal Considerations        | 13-50  |

| Audio Output Register, AODOOT                                             | Electrical Characteristics            | 13-51  |

| AUDFCR13-21                                                               | Voiceband Input                       |        |

| Audio Sampling Rate Example13-21                                          | Voiceband Output                      | 13-52  |

| Timing and Control                                                        | Baseband Receive Channel              |        |

| · ·                                                                       | Transmit Power Control                |        |

| Frame Counter Register, FC13-22                                           | Baseband Transmit Channel             |        |

| Quarter-Bit Counter Register, QBC13-22                                    | Small Signal Clock Applications       |        |

| QBC Jump, QBCJUMP[12:013-22 Timing and Control Register, TCNTRL13-23      | Differential Signals                  |        |

| Event Timing and Control Index Register,                                  | Digital Output Buffer Drive           |        |

| ETCI13-24                                                                 | Power Dissipation                     |        |

| Event Timing and Control Registers,                                       | Timing Characteristics                | 13-64  |

| ETC[14:0]13-24                                                            | CSP1088 Input Clock Generation and    | 40.05  |

| Frequency Selection Registers,                                            | Reset                                 |        |

| FREQ[5:0]13-28                                                            | Digital Audio Interface               |        |

| Baseband                                                                  | Data Read Timing                      |        |

|                                                                           | Data Write Timing<br>Serial Interface |        |

| Burst Data Registers, BRSTDATA[9:0]13-29                                  | JTAG I/O Specifications               |        |

| Ciphering13-29                                                            | Outline Diagram                       |        |

| Frequency Correction Register, FCR13-31 Ramp Level Register, RAMPLVL13-32 | <del>-</del>                          |        |

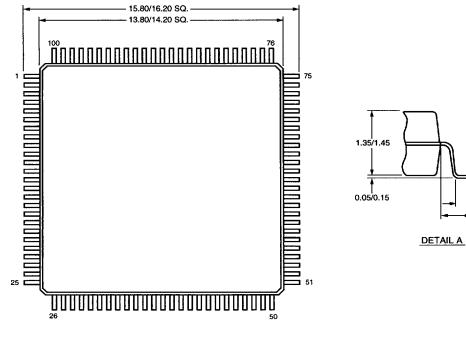

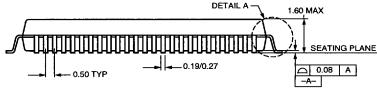

| Ramp Up and Ramp Down Levels Registers,                                   | 100-Pin Thin Quad Flat Pack TQFP      | 13-/1  |

| RAMPUP(15:0): RAMPDN(15:0)13-32                                           |                                       |        |

# **Description** (continued)

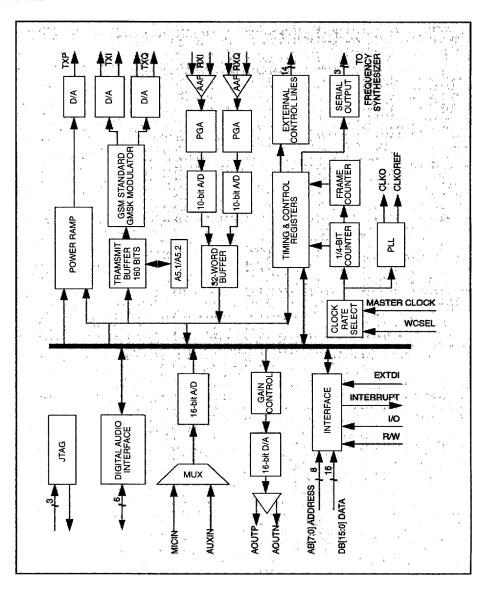

The AT&T CSP1088 is designed to interface a digital signal processor with analog audio and baseband signals, and programmable events, power timers, and filters. The device provides analog interfacing and timing for a GSM mobile cellular telecommunications terminal requiring low power consumption. Figure 1, is a block diagram of the AT&T CSP1088 v2.2.

Figure 1. AT&T CSP1088 Block Diagram v2.2

0050026 0017635 929

# Pin Information

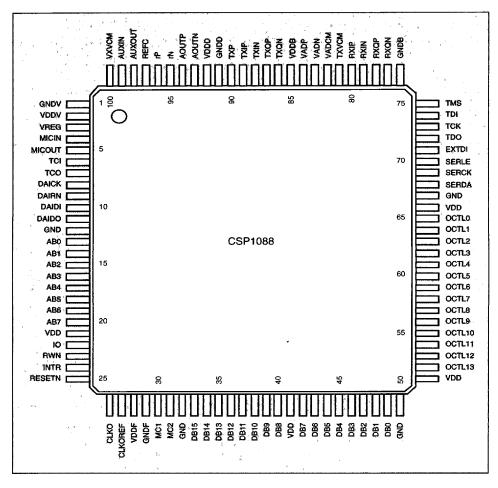

Figure 2. AT&T CSP1088 TQFP Pin Diagram v2.2

**---** 0050026 0017636 865 **---**

# Pin Information (continued)

Table 1. Pin Information

| 100-Pin<br>TQFP | Symbol   | Type*    | Description                                                                        |  |

|-----------------|----------|----------|------------------------------------------------------------------------------------|--|

| 4               | MICIN    | i, a     | Voiceband Microphone Input                                                         |  |

| 5               | MICOUT   | o, a     | Voiceband Microphone Output                                                        |  |

| 99              | AUXIN    | i, a     | Voiceband Auxiliary Input                                                          |  |

| 98              | AUXOUT   | o, a     | Voiceband Auxiliary Output                                                         |  |

| 100             | VXVCM    | i, a     | Voiceband External Bypass Capacitor, Reference                                     |  |

| 94              | AOUTP    | o, a     | Voiceband Positive Output                                                          |  |

| 93              | AOUTN    | o, a     | Voiceband Negative Output                                                          |  |

| 96              | rP       | nc       | No connect                                                                         |  |

| 95              | rN       | nc       | No connect                                                                         |  |

| 3               | VREG     | o, a     | Voiceband regulated voltage for electrect cond. microphone                         |  |

| 97              | REFC     | i, a     | Voiceband ext. cap. for int. voltage regulator                                     |  |

| 7               | TCO      | i, d, PD | Voiceband Digital Audio Interface, Test Control 0                                  |  |

| 6               | TC1      | i, d, PD | Voiceband Digital Audio Interface, Test Control 1                                  |  |

| 9               | DAIRN    | i, d, PD | Voiceband digital audio interface reset not, active-low                            |  |

| 10              | DAIDI    | i, d, PD | Voiceband digital audio interface data in                                          |  |

| 11              | DAIDO    | o, d     | Voiceband digital audio interface data out, reset state is low                     |  |

| 8               | DAICK    | o, d     | Voiceband digital audio interface clock, reset state is low                        |  |

| 89              | TXIP     | o, a     | Baseband Transmit I Component Positive Output                                      |  |

| 88              | TXIN     | o, a     | Baseband Transmit I Component Negative Output                                      |  |

| 87              | TXQP     | o, a     | Baseband Transmit Q Component Positive Output                                      |  |

| 86              | TXQN     | o, a     | Baseband Transmit Q Component Negative Output                                      |  |

| 90              | TXP      | o, a     | Baseband transmit power control                                                    |  |

| 81              | TXVCM    | i, a     | Baseband transmit external reference. It can set common modes of TXIP,N and TXQP,N |  |

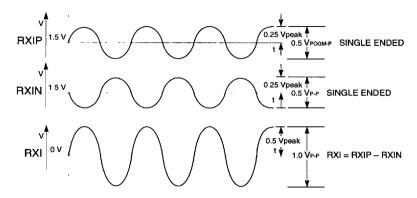

| 80              | RXIP     | i, a     | Baseband Receive I Component Positive Input                                        |  |

| 79              | RXIN     | i, a     | Baseband Receive I Component Negative Input                                        |  |

| 78              | RXQP     | i, a     | Baseband Receive Q Component Positive Input                                        |  |

| 77              | RXQN     | i, a     | Baseband Receive Q Component Negative Input                                        |  |

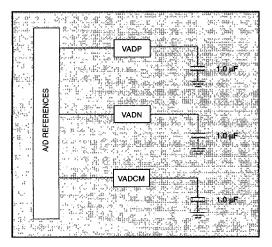

| 82              | VADCM    | i, a     | Baseband 2.4 V analog reference for A/D                                            |  |

| 84              | VADP     | i, a     | Baseband reference for A/D Positive                                                |  |

| 83              | VADN     | i, a     | Baseband reference for A/D Negative                                                |  |

| 30, 31          | MC[1:2]  | i,d      | Small Signal Master Clock Input                                                    |  |

| 3340            | DB[15:8] | i/o, d   | Data bus 15—8                                                                      |  |

| 42—49           | DB[7:0]  | i/o, d   | Data bus 7—0                                                                       |  |

| 20—13           | AB[7:0]  | i, d     | Address bus 7—0                                                                    |  |

| 23              | RWN      | i, d     | Read/write not (low = write, high = read)                                          |  |

| 22              | Ю        | i, d     | Chip select to enable data bus I/O                                                 |  |

| 24              | INTR     | o, d     | Interrupt output to DSP, active-high, reset state is low                           |  |

| 71              | EXTDI    | i, d, PD | External digital input, cleared prior to each Rx buffer                            |  |

| 25              | RESETN   | i, đ     | Reset not, active-low                                                              |  |

<sup>\*</sup> i = input, o = output, a = analog, d = digital, pwr = power, gnd = ground, and nc = no connect, PD = on-chip pull-down resistor, PU = on-chip pull-up resistor.

# Pin Information (continued)

Table 1. Pin Information (continued)

| 100-Pin<br>QFP | Symbol     | Type*   | Description                                                                              |  |

|----------------|------------|---------|------------------------------------------------------------------------------------------|--|

| 52—65          | OCTL[13:0] | o,d     | Output control pins 13 through 0, controlled by state machine, reset state               |  |

|                |            |         | is low                                                                                   |  |

| 69             | SERCK      | o,d     | Serial clock for Programming External Synthesizer, reset state is low                    |  |

| 68             | SERDA      | o,d     | Serial data out for Programming External Synthesizer, reset state is low                 |  |

| 70             | SERLE      | o,d     | Serial data latch for Programming External Synthesizer, active-low, reset state is high* |  |

| 26             | CLKO       | o,a     | Small Signal Clock Output from PLL, reset state is active                                |  |

| 27             | CLKOREF    | o,a     | Small Signal Clock Output Reference, low-pass filtered CLKO*                             |  |

| 72             | TDO        | o,d     | JTAG Test Data Output, reset state is tri-state*                                         |  |

| 73             | TCK        | i,d     | JTAG Test Clock                                                                          |  |

| 74             | TDI        | i,d, PU | JTAG Test Data Input                                                                     |  |

| 75             | TMS        | i,d, PU | JTAG Test Mode Select                                                                    |  |

| 2              | VDDV       | pwr     | 5 V analog supply voiceband                                                              |  |

| 1              | GNDV       | gnd     | 0 V analog ground voiceband                                                              |  |

| 28             | VDDF       | pwr     | 5 V analog supply PLL                                                                    |  |

| 29             | GNDF       | gnd     | Analog ground PLL                                                                        |  |

| 85             | VDDB       | pwr     | 5 V analog supply baseband                                                               |  |

| 76             | GNDB       | gnd     | Analog ground baseband                                                                   |  |

| 92             | VDDD       | pwr     | 5 V quiet digital supply                                                                 |  |

| 91             | GNDD       | gnd     | Quiet digital ground                                                                     |  |

| 21,41,51,66    | VDD[3:0]   | pwr     | 3 V digital supply                                                                       |  |

| 12,32,50,67    | GND[3:0]   | gnd     | Digital Ground                                                                           |  |

<sup>\*</sup> I = input, o = output, a = analog, d = digital, pwr = power, gnd = ground, and nc = no connect, PD = on-chip pull-down resistor, PU = on-chip pull-up resistor.

#### **Architectural Information**

Figure 1 on page 3 shows a block diagram of the AT&T CSP1088. The AT&T CSP1088 integrates the A/D and D/A functions of the voiceband and baseband channels along with a GMSK modulator, frequency synthesis (PLL), A5 Block Generator, and a timing and control state machine. The timing and control state machine monitors an internal quarter-bit counter and an internal frame counter to control both baseband receive and baseband transmit activity. The state machine can also control up to 14 external elements. The AT&T CSP1088 has a serial output that is designed to program an external frequency synthesizer. The 8-bit address, 16-bit data bus connects easily to the AT&T DSP1600 family.

#### **Event Timing & Control State Machine**

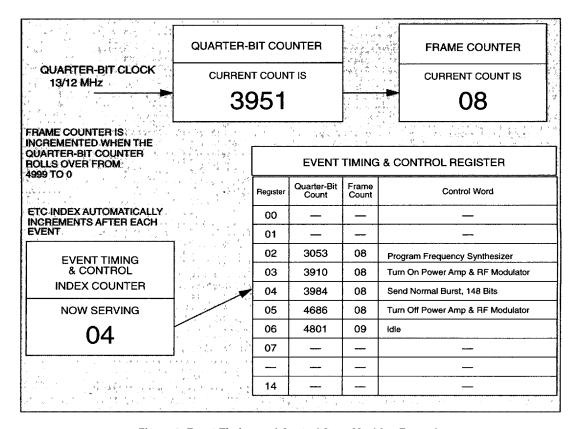

Figure 3 on page 8 illustrates the operation of the event timing and control (ETC) state machine by an example. In this example, the state machine has already executed the control word of ETC register 03, and the ETC index register is now pointing to ETC register 04. When the quarter-bit counter (which is currently at 3951) reaches 3984, the control portion of ETC register 04 will be executed. In this example, the AT&T CSP1088 will send a normal burst of 148 bits that are held in the burst data register.

After the match, the ETC index register will automatically be incremented to 05, and the next timing match will occur when the quarter-bit counter reaches 4686. The frame counter will be incremented to 09 when the quarter-bit counter rolls over from 4999 to 0. Depending upon the state of bit 13 of TCNTRL (INCQBCFC) the ETC registers can be programmed in different ways. If INCQBCFC = 0, the ETC index register will increment with every quarter bit counter timing match (the quarter-bit counter equaling the EQN bits from the current ETC register), regardless of the values of the EVEN and ODD bits in the current ETC register. This allows the ETC index register to increment when no event occurs (for example, a timing match occurs and the frame count is 08, but the EVEN/ ODD bits are programmed in the current ETC register such that this event only happens on odd frames; therefore, no event occurs). For INCQBCFC = 1, the ETC index register increments only when both the quarter bit timing match occurs and the EVEN/ODD bit criteria is satisfied. In this case, the ETCI register increments only when events occur.

No matter the state of INCQBCFC, the ETC index register is reset to 0 one half 13 MHz cycle after the ETC index register has taken on a value greater than or equal to the value of bits 3 to 0 (DPT [3:0]) in TCNTRL.

#### Send Burst Data

As an example of how these components work together, consider how the AT&T CSP1088 sends a normal burst of 148 bits to the RF modulator. The DSP synchronizes the AT&T CSP1088's quarter-bit counter with the base station. The DSP keeps track of exactly when the burst data should arrive at the mobile telephone's RF modulator so that the outgoing data is sent during its assigned time slot. The DSP loads this time into the timing portion of one of the AT&T CSP1088's ETC registers, and it puts the control word for sending a normal data burst into the control portion of that register. The DSP loads the AT&T CSP1088's transmit buffer with148 bits of data.

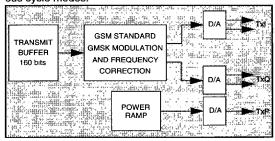

The AT&T CSP1088 keeps track of the bit count to an eighth-bit accuracy and keeps track of the frame number. When the timing portion of the indexed ETC register matches the bit and frame numbers, the control portion of the register is executed. In the case of a data burst, the control word will cause the AT&T CSP1088's GMSK modulator to process the data held in the transmit buffer. This modulator will convert the data stream into phase information that meets GSM modulation standards. A frequency correction term is added to the phase information, and then the phase is converted into I and Q components. The I and Q components are converted to analog voltages by the baseband D/A converters. The analog output voltages can be connected directly to the I and Q inputs of an RF modulator.

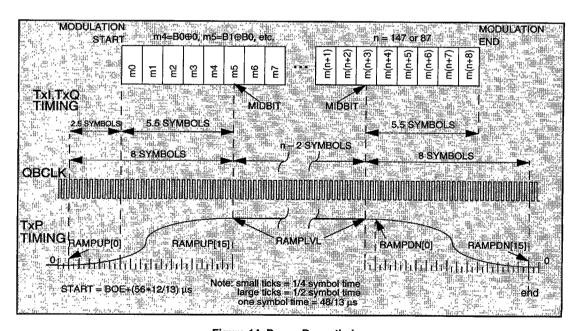

In addition to the I and Q outputs, a power ramp signal is generated to ramp the output power amplifier on and off to avoid frequency spectrum spreading. The power ramp shape is programmable, and the ramping is spread over 9-bit intervals, for both ramp up and ramp down.

# **Architectural Information** (continued)

Figure 3. Event Timing and Control State Machine Example

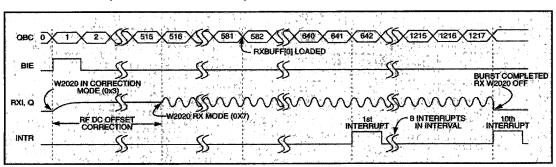

#### **Receiving Burst Data**

The DSP also has to keep track of exactly when its next burst of data will be arriving. The DSP loads a start time into the timing portion of one of the AT&T AT&T CSP1088's ETC registers, and it puts the control word for receiving a burst of data into the control portion of that register. Once this ETC register is indexed, the timing portion of the register is compared to the AT&T CSP1088's internal bit counter and frame counter. When the timing portion of the register matches, the control portion of the register is executed. After the analog dc offset calibration, the baseband A/D converters begin to convert the received I and Q signals into 10-bit digital words.

The AT&T CSP1088 stores the incoming I and Q data pairs in 32 internal double-buffered registers so that the DSP does not have to be interrupted so frequently (each interrupt to the DSP requires some overhead). Once the AT&T CSP1088 receives 16 I and Q data pairs, it issues an interrupt to the DSP to read the data. While the DSP is reading out the 16 I and Q data pairs, the AT&T CSP1088 continues to receive and convert I and Q data pairs which it stores in the other half of the double-buffered registers. The DSP has approximately 59 µs to read the 16 sample pairs before the other half of the double buffer fills.

# **Architectural Information (continued)**

#### **Voiceband Conversion**

The voiceband A/D converter generates 16-bit samples at an 8 kHz rate. When a new sample is ready, the AT&T CSP1088 sends an interrupt to the DSP. When the DSP services this interrupt, it should not only read the 16-bit sample from the voiceband input A/D converter, but it should also load a new sample into the voiceband output D/A converter.

The gain of the voiceband output can be lowered in 3 dB steps from 0 dB to -45 dB. The voiceband differential output can be connected directly to a load as low as 15  $\Omega$ , such as the earphone of a handset. A digital AUDIO interface is provided for testing. It conforms to GSM specifications.

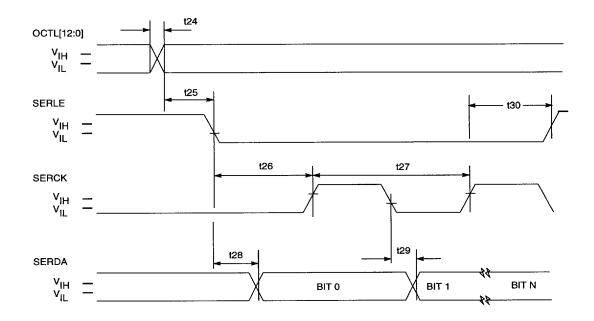

# Programming an External RF Frequency Synthesizer

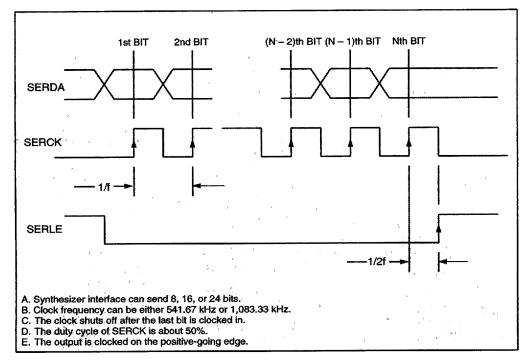

The AT&T CSP1088 has a serial output port which can be used to program an external frequency synthesizer. The DSP can load frequency information into six different frequency selection registers. The information in the register is sent out the serial port whenever the control portion of an ETC register loads that frequency selection register's address. The serial output can be either 8 bits, 16 bits, or 24 bits, the output rate can be either 1.08 Mbits/s or 0.54 Mbits/s, and the output data direction can be least significant bit or most significant bit first. The output length, output speed, and output data directions are controlled by the timing and control registers.

#### **Output Control Lines**

The AT&T CSP1088 has 14 output control pins. These pins are set to logic high or logic low by the control portion of an ETC register when the timing portion of that register matches the internal bit and frame counters. These control lines are typically used to turn on and off external circuits, and to change the gain of programmable amplifiers. They are reset to logic low on RESET. They can also be reset at the end of each TX and/or RX burst.

### Ciphering

The AT&T CSP1088 has hardware A5.1 and A5.2 used for ciphering. The transmit burst data buffer is initialized and then the cipher unit generates the output in two blocks under software control.

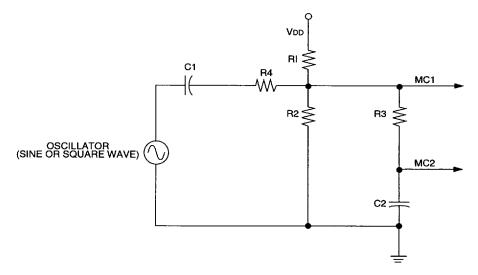

## **Frequency Synthesis**

An on-chip PLL connects directly to DSP16XX devices using a small signal clock input buffer. Several options are available for activating the PLL including automatic activation via the event timing and control state machine.

# **Architectural Information** (continued)

# Frequency Synthesis (continued)

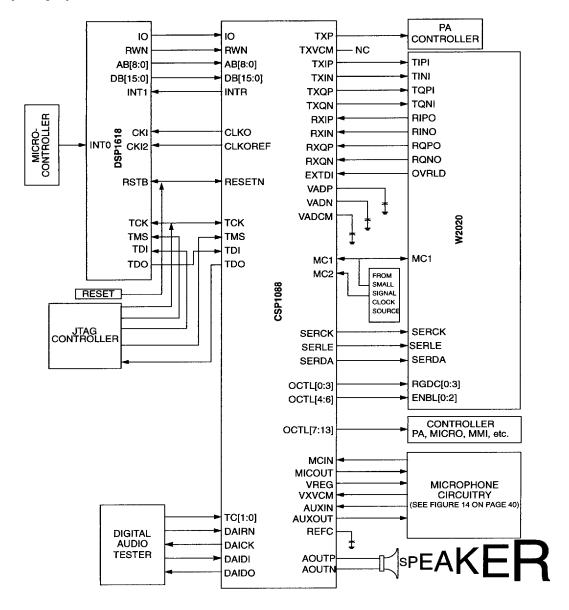

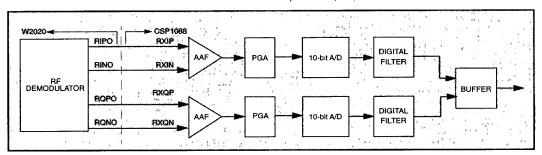

Figure 4. CSP1088 Connection Diagram to DSP1618 and W2020

**=** 0050026 0017642 069 **=**

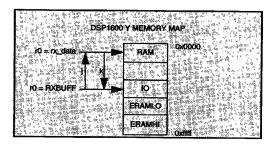

# **Register Information**

# Register Addresses (Memory Map)

WARNING: All unused and reserved register bits must be written with a logic low. Failure to do so may result in damage to the device or erratic behavior.

Table 2. Register Addresses (Memory Map)

| Register       | Access<br>Method | Hex<br>Address | Value on<br>Reset | Description                                               |

|----------------|------------------|----------------|-------------------|-----------------------------------------------------------|

| INS/INC        | R/W              | 0              | 0x0000            | Interrupt status on read, and interrupt control on write* |

| CONTROL        | R/W              | 0x1            | 0x0000            | CSP1088 control*                                          |

| TEST           | R/W              | 0x2            | 0x0000            | Test control*                                             |

| AUDCONF        | R/W              | 0x4            | 0x0000            | Audio input/output configuration*                         |

| AUDIN          | R                | 0x5            | Χ                 | Audio input data sample                                   |

| AUDOUT         | W                | 0x6            | Х                 | Audio output sample                                       |

| AUDFCR         | R/W              | 0x7            | 0x0000            | Audio sampling frequency correction                       |

| FC             | R/W              | 0x8            | 0x0000            | Frame counter value*                                      |

| QBC            | R/W              | 0x9            | 0x0000            | Quarter-bit counter value*                                |

| TCNTRL         | R/W              | 0xa            | 0x0000            | Timing and control section control word*                  |

| ETCI           | R/W              | 0xb            | 0x0000            | Event timing and control index*                           |

| QBCJUMP        | W                | Охс            | 0x0000            | Quarter-bit jump modification word                        |

| ETC [0:14]     | R/W              | 0x100x3c       | Х                 | Event time and control word storage                       |

| FREQ [0:5]     | R/W              | 0x400x4b       | X                 | Frequency word storage                                    |

| BRSTDATA [0:9] | R/W              | 0x50—0x59      | X                 | Burst data registers                                      |

| FCR            | W                | 0x5a           | Х                 | Transmit frequency correction register                    |

| RAMPLVL        | R/W              | 0x5f           | Х                 | Power ramp output nominal level value                     |

| RAMPUP [0:15]  | R/W              | 0x60—0x6f      | Х                 | Power ramp up values                                      |

| RXBUFF [0:31]  | R                | 0x70—0x8f      | Х                 | Receive data buffer for I, Q values                       |

| CLKOCNTL       | R/W              | 0x90           | 0x0000            | Clock output control word                                 |

| RAMPDN [0:15]  | R/W              | 0xe0—0xef      | Χ                 | Power ramp down values                                    |

<sup>\*</sup> There may be up to three 13 MHz cycles before the register is updated with a write. Back-to-back writes in less time should be avoided.

# Interrupt Status and Interrupt Control Register, INS/INC (Address 0x0)

Interrupt status and interrupt control registers are both located at address 0. When this register is read, it is considered the interrupt status register, and Table 3 on page 12 describes the meanings of its 16 bits. When this register is written to, it is considered the interrupt control register, and Table 4 on page 12 describes what happens to each bit during a write operation.

This register is designed such that when the DSP reads the interrupt register, it can write the same word back into the register to reset the serviced interrupt. Typically, the bits 1—7 should be reset to low after they are serviced, so writing a logic high to any of these bits will reset them to a logic low. Writing a logic low to any of these bits will leave them unchanged. Bit 0 does not change after an interrupt, so writing a logic high to this bit will set it high, and writing a logic low to this bit will reset it low.

# Interrupt Status and Interrupt Control Register, INS/INC (Address 0x0) (continued)

Table 3. Interrupt Status Register (Read Cycle)

| Name    | Bit Number | Description                                                                                     |

|---------|------------|-------------------------------------------------------------------------------------------------|

| EOTXIES | 0          | End of transmit interrupt enable status                                                         |

| EOTXI   | 1          | End of transmit interrupt                                                                       |

| RXBUFI  | 2          | Receive buffer interrupt                                                                        |

| AUDI    | 3          | Audio interrupt                                                                                 |

| A5I     | 4          | A5 Interrupt                                                                                    |

| TIMEI   | 5          | Time-out interrupt                                                                              |

| EXTOV   | 6          | External overflow indication, cleared when Rx starts, and at the start of each 16 receive pairs |

| INTOV   | 7          | Internal overflow indication                                                                    |

| A5IES   | 8          | A5 interrupt enable status                                                                      |

| r       | 9—15       | Reserved                                                                                        |

#### Table 4. Interrupt Control Register (Write Cycle)

| Name    | Bit Number | Description                                                                    |

|---------|------------|--------------------------------------------------------------------------------|

| EOTXIE  | 0          | End of transmit interrupt enable. Logic high sets; logic low resets            |

| CEOTXI  | 1          | Clear end of transmit interrupt. Logic high resets; logic low leaves unchanged |

| CRXBUFI | 2          | Clear receive interrupt. Logic high resets; logic low leaves unchanged         |

| CAUDI   | 3          | Clear audio interrupt. Logic high resets; logic low leaves unchanged           |

| CA5I    | 4          | Clear A5 Interrupt                                                             |

| CTIMEI  | 5          | Clear time-out interrupt. Logic high resets; logic low leaves unchanged        |

| Х       | 6          | This bit cannot be changed by an external write                                |

| Х       | 7          | This bit cannot be changed by an external write                                |

| A5IE    | 8          | A5 interrupt enable                                                            |

| r       | 915        | Reserved                                                                       |

#### **EOTXIES: End of Transmit Interrupt Enable Status**

When set to a logic high, the end of transmit interrupt, EOTXI, is enabled.

#### **EOTXI: End of Transmit Interrupt**

EOTXI is set to a logic high at the end of a transmitted burst if enabled by EOTXIES. The transmitted burst is considered ended on the clock cycle that the power ramping finishes on.

#### **RXBUFI: Receive Buffer Interrupt**

RXBUFI is set to a logic high when 16 receive I samples and 16 receive Q samples have been stored in the 32 double-buffered receive registers, RXBUFF[31:0]. The values of these registers must be read before the AT&T CSP1088 finishes receiving the next 16 I and 16 Q samples (which takes about 59 µs) or else the information could be overwritten and lost. Whenever a receive interrupt occurs, EXTOV and INTOV interrupt bits are also updated (see description below).

# Interrupt Status and Interrupt Control Register, INS/INC (Address 0x0) (continued)

#### **AUDI: Audio Interrupt**

AUDI is set to a logic high when a new sample from the audio input is written into the AUDIN register. This sample must be read before the next sample arrives (which is in about 125  $\mu s$ ). The AUDI interrupt is also considered a request for a new audio output sample, and a new audio output sample should be written to the AUDOUT register.

#### A5I

When logic high, A5I indicates that a block cipher, either BLOCK 1 or BLOCK 2, has finished.

#### **TIMEI: Time-Out Interrupt**

There are 15 event timing and control registers, ETC[14:0]. When the timing information of a selected ETC register matches the quarter-bit counter, QBC, and the frame counter, FC, the control portion of the word may set the DSP interrupt bit, DSPI. When DSPI is set to a logic high, an interrupt is issued, and the time-out interrupt bit, TIMEI, is set to a logic high. Also, if CLKO had been disabled, TIMEI asserting will enable CLKO; if CLKO has been enabled, CLKO remains enabled (see Table 43 on page 35).

#### **EXTOV: External Overflow Indication**

EXTOV is set to a logic high if an external overload condition occurred anytime during the previous 16-sample receive time period. An external overload condition is sensed whenever a logic high is applied to the EXTDI pin for at least one MC cycle. EXTOV is updated whenever a receive interrupt, RXBUFI, occurs.

#### INTOV: Internal Overflow Indication

INTOV is set to a logic high if an internal overload of the I or Q receive ADC occurs anytime during the 16-sample receive time period. INTOV is updated whenever a receive interrupt, RXBUFI, occurs.

#### **ASIES**

When logic high, the A5 interrupt, A5IE, is enabled (logic high).

#### **EOTXIE: End of Transmit Interrupt Enable**

When EOTXIE is set to a logic high, the end of transmit interrupt, EOTXI, is enabled. When EOTXIE is reset to a logic low, the end of transmit interrupt, EOTXI, is disabled.

#### **CEOTXI: Clear End of Transmit Interrupt**

When CEOTXI is set to a logic high, the end of transmit interrupt bit, EOTXI, is reset to a logic low (cleared). When CEOTXI is set to a logic low, EOTXI is unchanged.

#### CRXBUFI: Clear Receive Interrupt

When CRXBUFI is set to a logic high, the receive interrupt bit, RXBUFI, is reset to a logic low (cleared). When CRXBUFI is set to a logic low, RXBUFI is unchanged.

#### **CAUDI: Clear Audio Interrupt**

When CAUDI is set to a logic high, the audio interrupt bit, AUDI, is reset to a logic low (cleared). When CAUDI is set to a logic low, AUDI, is unchanged.

#### CA5I

When CA5I is written logic high, the A5I bit is reset to logic low (cleared). When CA5I is reset to logic low, A5I is unchanged.

#### CTIMEI: Clear Timing Interrupt

When CTIMEI is set to a logic high, the time-out interrupt bit, TIMEI, is reset to a logic low (cleared). When CTIMEI is set to a logic low, TIMEI is unchanged.

#### A5IE

When A5IE is set logic high, the A5 interrupt is enabled. After either BLOCK 1 or BLOCK 2 ciphers are generated, and A5IE was set logic high, the INTR pin is asserted, and A5I is set logic high.

# CSP1088 Control Register, CONTROL (Address 0x1)

The CONTROL register determines whether the output controls bits are cleared at the end of a transmit burst and/or at the end of a receive burst. The CONTROL register also determines whether the transmit output

modulation uses clockwise rotation or counter clockwise rotation, and the order in which I and Q samples are received. Table 5 describes how the CONTROL register regulates output control bits, transmit output modulation, and I and Q sample receiving.

The CONTROL register has additional bits specified for use in A5 block generation, device reset, MC disabling, and receive bandwidth selection.

Table 5. CSP1088 Control Register, CONTROL (Address 0x1)

| Name      | Bit Number | Description*                                                                                                                                                  |  |

|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CTLCLREOT | 0          | Logic high, output control bits OCTL[13:0] are reset low after transmit burst Logic low, output control bits OCTL[13:0] are not changed after transmit burst  |  |

| CTLCLREOR | 1          | Logic high, output control bits OCTL[13:0] are reset low after receive burst<br>Logic low, output control bits OCTL[13:0] are not changed after receive burst |  |

| MODROT    | 2          | Logic high, negative or clockwise modulation rotation  Logic low, normal or counterclockwise modulation rotation                                              |  |

| RBORD     | 3          | Logic high, receive buffer order first Q then I Logic low, receive buffer order first I then Q                                                                |  |

| RXDCCAL   | 4          | Logic high, initiates digital RX dc offset calibration                                                                                                        |  |

| RESET     | 5          | Logic high, generates software reset                                                                                                                          |  |

| MCSTOP    | 6          | Logic high, stops master clock at input pin                                                                                                                   |  |

| r         | 7          | Reserved                                                                                                                                                      |  |

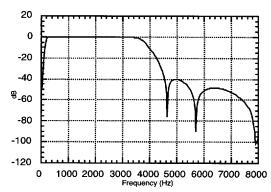

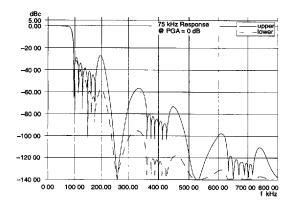

| RBWS      | 8          | Receive Filter Bandwidth Select: "0" = 75 kHz, "1" = 95 kHz                                                                                                   |  |

| r         | 910        | Reserved                                                                                                                                                      |  |

| A5ENBL    | 11         | A5 algorithm enabled (start) self resetting                                                                                                                   |  |

| A5TYPE    | 12         | Write logic high, A5.1 algorithm selected Write logic low, A5.2 algorithm selected                                                                            |  |

| A5DIR     | 13         | Write logic low, bits in reverse order to register bits Write logic high, bits in same order to register bits                                                 |  |

| A5BLOCK   | 14         | Write logic low, BLOCK 1 Write logic high, Generate BLOCK 2                                                                                                   |  |

| A5STAT    | 15         | Write logic low, no affect Write logic high, clear status to zero when read Read logic high, Block generation complete                                        |  |

<sup>\*</sup> All bits are exactly as described in the AT&T CSP1088 v2.0 data sheet except bit 8.

**■** 0050026 0017646 704 **■**

# CSP1088 Control Register, CONTROL (Address 0x1) (continued)

# Output Control Bits Clear at End of Transmit, CTLCLREOT

The output control bits are used to control various external circuits such as powering up the receiver, or the power amplifier. If the CTLCLREOT bit is set to a logic high, then the output control bits, OCTL[13:0], are reset to a logic low after the end of a transmit burst. If the CTLCLREOT bit is reset to a logic low, then the OCTL[13:0] are not reset at the end of a transmit burst.

# Output Control Bits Clear at End of Receive, CTL-CLREOR

The output control bits are used to control various external circuits such as powering up the transceiver, or the power amplifier. If the CTLCLREOR bit is set to a logic high, then the output control bits, OCTL[13:0], are reset to a logic low after the end of a receive burst. If the CTLCLREOR bit is reset to a logic low, then the OCTL[13:0] are not reset at the end of a receive burst.

#### **Modulation Rotation, MODROT**

When the modulation rotation bit, MODROT, is set to a logic high, then the rotation of the output phase at Txl and TxQ is clockwise, or negative. When MODROT is reset to a logic low, then the rotation of the output phase is in the normal counterclockwise direction.

#### Receive Buffer Order, RBORD

Sixteen I and Q sample pairs are stored in 32 double-buffered registers. When the receive buffer order bit, RBORD, is set to a logic high, then the received samples are stored first Q then I such that the lowest address (address 0) is Q0, and the next address (address 1) is I0, and so on until I15 is stored in the highest address (address 31). When RBORD is reset to a logic low, then the received samples are stored in the normal order of first I and then Q.

#### Receive Digital dc Offset Calibration, RXDCCAL

When the receive dc offset calibration bit, RXDCCAL is set high, both I and Q receive channels perform a dc offset calibration. This **must** be done once before using the receive channel for the first time. It is recommended that it be done prior to any other programming of the AT&T CSP1088. When read, RXDCCAL indicates that the dc offset calibration is completed if logic low, or that calibration is active if logic high.

#### System Reset, RESET

Setting this bit high resets the AT&T CSP1088. This reset is identical to a reset initiated by the reset pin. This bit clears itself when reset is complete, which requires approximately eight cycles.

#### Master Clock Stop Bit, MCSTOP

When the master clock stop bit, MCSTOP, is set high, the master clock (MC) is stopped at the input pin. Only the CONTROL register may be written to in this state, usually to turn the clock on again or reset the AT&T CSP1088.

#### **RBWS**

Receive bandwidth select (see page 16).

#### A5 Enable, A5ENBL

When set, A5ENBL enables the A5 algorithm. When reset, A5ENBL will immediately stop and reset the generator. Data should be in the TX buffer before enabling A5. After the BLOCK 2 has been generated, this bit self-resets.

#### A5 Type, A5TYPE

When set to logic high, A5TYPE selects the A5.1 algorithm generation. When set to logic low, A5TYPE selects A5.2 algorithm generation.

#### A5 Direction, A5DIR

When set to logic high, A5DIR selects key, count, and block bit ordering as given in Table 33, Table 34, and Table 36. When set logic low, the key, count and block bit ordering is as given in Table 31, Table 32, and Table 35.

#### A5 BLOCK Select, A5BLOCK

When set logic high, A5BLOCK selects BLOCK 2 generation. When set logic low, this selects BLOCK 1 generation. After the BLOCK 2 has been generated, this bit self-resets.

#### A5 Status and Control, A5STAT

When written logic high, A5STAT resets itself to logic low. This must be done prior to every block generation. When read, logic high indicates a block generation has completed, and logic low means a block generation has not started or is processing.

**III** 0050026 0017647 640 **III**

## CSP1088 Control Register, CONTROL (Address 0x1) (continued)

#### **Receive Bandwidth Selection (RBWS)**

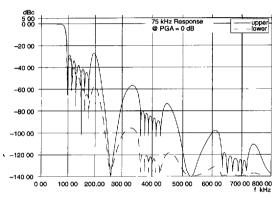

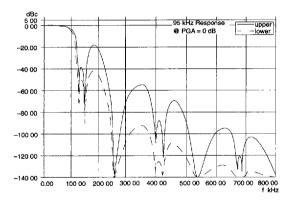

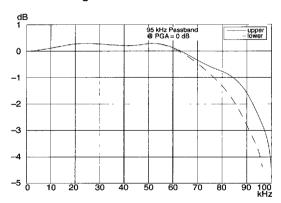

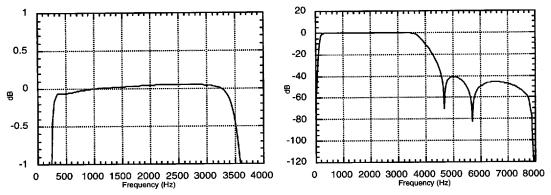

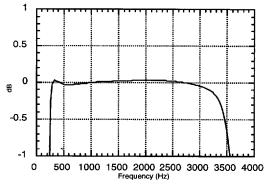

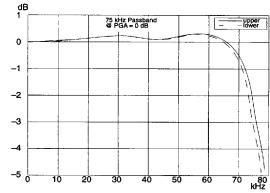

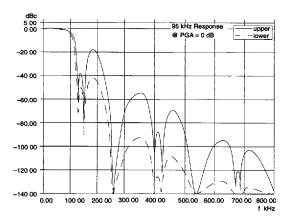

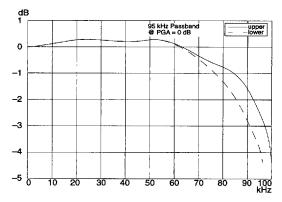

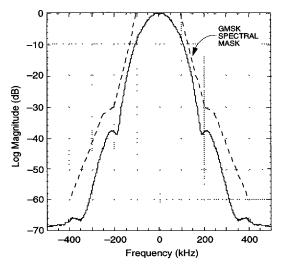

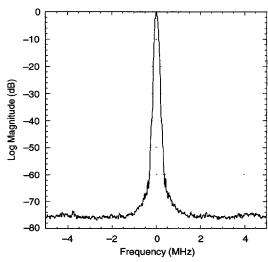

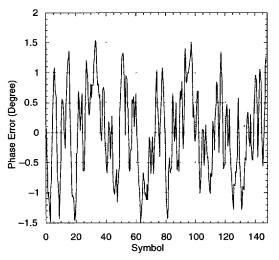

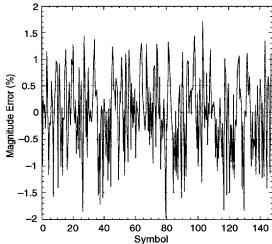

The receive digital filter 3 dB bandwidth is selectable from 75 kHz to 95 kHz. When logic 0, RBWS selects 75 kHz bandwidth; logic high selects 95 kHz bandwidth. Figures 5 and 7 illustrate a spectral response, including a passband, for the 75 kHz bandwidth, and Figures 6 and 8 illustrate a spectral response, including a passband, for the 95 kHz bandwidth. Selecting 75 kHz bandwidth attenuates a GSM modulated signal with ±200 kHz center frequency (the adjacent channel) by 20 dB, whereas the 95 kHz bandwidth attenuates that signal by 16 dB.

dB

1

75 kHz Passband

6 PGA = 0 dB

0

-1

-2

-3

-4

-5

0 10 20 30 40 50 60 70 80

Figure 5. 75 kHz Response

Figure 7. 75 kHz Passband

Figure 6. 95 kHz Response

Figure 8. 95 kHz Passband

### Test Control Register, TEST (Address 0x2)

The TEST register provides a serial interface for direct access to the audio input and output data streams. This interface is used to test the audio section of the AT&T CSP1088 and has four modes of operation: 1) normal, 2) speech decoder/DTX functions on downlink, 3) speech encoder/DTX functions on uplink, and 4) test of acoustic devices and A/D and D/A functions. The test register, TEST, selects the mode of the digital audio interface. This register also is used to stop continuous receive or transmit and to select the MC frequency.

Table 6. Test Register, TEST, Bit Definitions

| Name       | Bit Number | Description                                                                                                                                    |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| TCSOURCE   | 0          | Logic high, test control source is hardware pins TC[0:1] Logic low, test control source is software bits TESTC[0:1]                            |

| TESTC[0:1] | 12         | Selects the digital audio interface mode                                                                                                       |

| STOP       | 3          | When the CSP1088 is in a continuous transmit or receive mode, setting this bit to a logic high will stop the transmission or reception of data |

| r          | 4—11       | Reserved                                                                                                                                       |

| MCSEL      | 12         | Master clock frequency select                                                                                                                  |

| r          | 13—15      | Reserved                                                                                                                                       |

Table 7. Test Register, TEST, Bit Definitions

| TC 1 or TESTC 1 | TC 0 or TESTC 0 | Description                                              |

|-----------------|-----------------|----------------------------------------------------------|

| 0               | 0               | Normal operation of audio circuits                       |

| 0               | 1               | Output data emulating D/A samples (speech decoding test) |

| 1               | 0               | Input data emulating A/D samples (speech encoding test)  |

| 1               | 1               | Test of acoustic devices and A/D and D/A                 |

#### **Test Control Source Bit, TCSOURCE**

When the TEST control source bit, TCSOURCE, is set to a logic high, the digital audio interface is controlled by the values at the hardware pins TC[0:1]. When reset to a logic low, the digital audio interface is controlled by the values of bits TESTC[0:1]. Table 6 shows which test states are selected for a given input.

#### Test Control Bits (TESTC[0:1])

When the TCSOURCE is reset to a logic low, the TESTC[0:1] bits control the digital audio interface. Table 6 describes the different test states.

#### **Continuous Operation Stop Bit, STOP**

Setting the STOP bit to a logic high stops the mode of continuous transmitting and continuous receiving.

Resetting the STOP bit to a logic low allows the receive and transmit to operate normally. When transmitting, the STOP bit causes the current data symbol to finish, then the ramp down sequence, with guard bits, follows until transmission stops. When receiving, the current 32 sample buffer finishes filling and one last RXBUFI interrupt is generated, then the receive mode stops. This bit is not self-clearing and should be reset to logic low before using RX or TX.

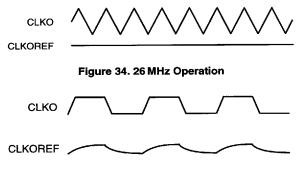

#### Master Clock Frequency Select Bit, MCSEL

The Master Clock Frequency is selectable between 26 MHz and 13 MHz. Setting MCSEL to logic 0, the reset state configures this device for 13 MHz input. Setting MCSEL to logic 1 configures this device for 26 MHz input.

**0050026 0017649 413**

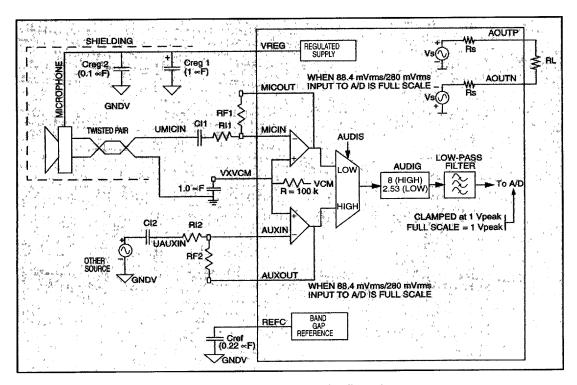

# Audio Input/Output Configuration Register, AUDCONF (Address 0x4)

The AUDCONF register controls the configuration of the voice input and voice output sections of the AT&T CSP1088. For the input section, this register selects the internal gain (18 dB or 8 dB), enables the input or not, and selects between MICIN and AUXIN inputs. For the output section, this register selects the gain from

-45 dB to 0 dB in 3 dB steps, enables the audio output or not, selects dithering or not, and mutes the audio output or not. Also, this register can select a loopback mode that takes the digital output of the input A/D converter, and loop it directly back to the digital output section for partial testing.

The Audio Output pins Aoutp and Aoutn support a wide variety of load impedances and power. Three programmable bits define a high or low bias condition and four voltage gains for the output drive stage. This is in addition to the programmable gain output over a 45 dB range.

Table 8. Audio I/O Configuration Register, AUDCONF, Bit Definitions

| Name        | Bit<br>Number | Description                                                                                                                             |  |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| AUDIE       | 0             | Audio Input Enable. Logic high enables audio input. Logic low disables audio input                                                      |  |

| AUDIG       | 1             | Audio Input Gain. Logic low selects 8 dB of internal gain before A/D converter. Logic high selects 18 dB of internal gain               |  |

| AUDIS       | 2             | Audio Input Select. Logic high selects AUXIN. Logic low selects MICIN                                                                   |  |

| AUDCHR      | 3             | Audio Input Charge. Charge external reference capacitor                                                                                 |  |

| AUDOE       | 4             | Audio Output Enable. Logic high enables audio output. Logic low disables audio output                                                   |  |

| AUDOG[0:3]  | 58            | Audio Output Gain. Gain of the audio output can be selected from -45 dB (all low) to 0 dB (all high) in 3 dB steps                      |  |

| AUDOM       | 9             | Audio Output Mute. Logic low mutes. Logic high unmutes                                                                                  |  |

| ADITH       | 10            | Audio Output Dithering. Logic low selects dithering to decorrelate periodic modular quantization noise. Logic high selects no dithering |  |

| r           | 11            | Reserved.                                                                                                                               |  |

| AUDPGA[1:0] | 13:12         | Audio PGA.                                                                                                                              |  |

| AUDHD       | 14            | Audio High Drive.                                                                                                                       |  |

| r           | 15            | Reserved. Reset to logic low                                                                                                            |  |

# Audio Input/Output Configuration Register, AUDCONF (Address 0x4) (continued)

#### Audio Input Enable, AUDIE

When the audio input enable, AUDIE, is set to a logic high, the audio input is enabled. When AUDIE is reset to a logic low, the audio input section is powered down.

#### **Audio Input Gain, AUDIG**

When the audio input gain bit, AUDIG, is reset to a logic low the internal gain before the A/D converter is 8 dB, with either MICIN or AUXIN selected. If AUDIG is set to a logic high, the internal gain of the audio input is 18 dB.

#### **Audio Input Select, AUDIS**

When the audio input select, AUDIS, is set to a logic high, the AUXIN input is selected. When AUDIS is reset to a logic low, the MICIN input is selected.

#### **Table 9. Audio Output Gain Bit Definition**

| Bit     | Description                                |

|---------|--------------------------------------------|

| AUDOG 0 | Logic high adds 3 dB. Logic low adds 0 dB  |

| AUDOG 1 | Logic high adds 6 dB. Logic low adds 0 dB  |

| AUDOG 2 | Logic high adds 12 dB. Logic low adds 0 dB |

| AUDOG 3 | Logic high adds 24 dB. Logic low adds 0 dB |

|         |                                            |

0050026 0017651 071

#### Audio Input Charge, AUDCHR

When the audio input charge, AUDCHR, is set to a logic high, the external reference capacitor is charged. When AUDCHR is reset to a logic low, the external reference capacitor is connected to the common mode through a 100  $k\Omega$  resistor. This bit should be logic high for 30 ms + 10 RICI time constants and then reset before using the voice input section.

#### **Audio Output Enable, AUDOE**

When the audio output enable, AUDOE, is set to a logic high, the audio output section is powered on. When AUDOE is set to a logic low, the audio output section is powered down.

#### Audio Output Gain, (AUDOG[0:3])

The audio output gain bits, AUDOG[0:3], vary the gain of the audio output section from -45 dB to 0 dB in 3 dB steps. Table 9 describes the gain added by each bit when set to a logic high.

# Audio Input/Output Configuration Register, AUDCONF (Address 0x4) (continued)

#### **Audio Output Mute, AUDOM**

When the audio output mute bit, AUDOM, is set to a logic low, the audio outputs, AOUTP and AOUTN, are muted. When AUDOM is set to a logic high, the audio outputs are not muted.

#### **Audio Output Dither, ADITH**

When the audio output dither bit, ADITH, is reset to a logic low, dithering is enabled. Dithering decorrelates the periodic modulator quantization noise of the output sigma-delta converter. If ADITH is set to a logic high, dithering is disabled.

#### Table 10. Audio PGA, AUDPGA [2.0], Bit Definition

#### Audio Loopback Mode, ALM

When audio loopback mode, ALM, is set to a logic high, the single-bit output of the audio-input sigma-delta A/D converter is looped back into the single-bit input of the audio-output delta-sigma D/A converter. Loopback mode is used for testing. When ALM is reset to logic low, loopback is disabled.

### Audio PGA, AUDPGA[1:0]

The audio output analog gain is selected by AUD-PGA[1:0]. The differential impedance of the load on pins Aoutp and Aoutn, and the requirement for distortion at the output, determine the settings for these bits. The minimum load depends on the maximum output current.

| AUDPGA1 | AUDPGA0 | Full-Scale Vout rms<br>at AUDOG[3:0]=0 dB<br>Setting | Minimum Load Impedance<br>(Max Distortion=1% for 1 kHz<br>Sine Wave Output) |

|---------|---------|------------------------------------------------------|-----------------------------------------------------------------------------|

| 0       | 0       | 1.5                                                  | 200 Ω                                                                       |

| 0       | 1       | 0.75                                                 | 80 Ω                                                                        |

| 1       | 0       | 0.375                                                | 30 Ω                                                                        |

| 1       | 1       | 0.1875                                               | 15 Ω*                                                                       |

<sup>\*</sup> It is recommended that audhd be set to a logic high for this condition.

#### Audio High Drive, AUDHD

Set to logic high, AUDHD places the audio output driver into high bias, which reduces the analog distortion by about half. When reset logic low, the driver dissipates about 3 mW less quiescent power. We recommend setting AUDHD to logic high for load impedances less than 30  $\Omega$ .

#### Audio Input Double-Buffered Register, AUDIN (Address 0x5)

Audio input is converted into 16-bit 2's complement numbers at an 8 kHz rate. As each 16-bit sample becomes available, it is stored in the double-buffered register AUDIN, an audio interrupt is initiated, and the audio interrupt bit in the interrupt status register, INS, is set to a logic high.

When the DSP reads the audio-input register, it should update the audio-output register, AUDOUT, also.

Table 11. Audio Input Double-Buffered Register, AUDIN

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Label | Al | Al | Al | Al | Ai | ΑI | Al | Al | Αl | ΑI | Al | Al | Al | Al | ΑI | Al |

|       | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

📟 0050026 0017652 TO8 📟

### Audio Output Register, AUDOUT (Address 0x6)

The audio output D/A converter takes linear 16-bit, 2's complement numbers at an 8 kHz rate. Each 16-bit number must be loaded into the audio output register, AUDOUT. The audio output register should be updated whenever an audio interrupt, AUDI, occurs.

Table 12. Audio Output Register, AUDOUT

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Label | AO |

|       | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

# Audio Frequency Correction Register, AUDFCR (Address 0x7)

Because the mobile's master clock frequency may differ from the serving cell's, adjustment to the audio sampling rate is necessary to match the serving cell's rate. The audio section's sampling frequency is modified through the AUDFCR register. The parts per million master clock cycles of correction is determined by the following equation:

$$ASFC_{ppm} = \frac{10^6}{13(8192 - MAG[12:0])(128 - 112 \cdot SFCR)}$$

0050026 0017653 944 1

**Table 13. AUDFCR Register Bit Definition**

| Bit # | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|-------|-------|-------|-------|-------|-------|-------|------|------|

| Label | MAG7  | MAG6  | MAG5  | MAG4  | MAG3  | MAG2  | MAG1 | MAG0 |

| Bit # | 15    | 14    | 13    | 12    | 11    | 10    | 9    | 8    |

| Label | ASFCE | ASFCR | ASFCS | MAG12 | MAG11 | MAG10 | MAG9 | MAG8 |

#### Audio Frequency Correction Magnitude, MAG[12:0]

The magnitude of the correction is determined by the MAG[12:0] bits, ranging from 0 to 8191.

#### **Audio Frequency Correction Sign, ASFCS**

The sign of frequency correction is defined by ASFCS. Set logic high, ASFCS makes the nominal 8 kHz sampling frequency lower by ASFCppm. Reset logic low, ASFCS makes the frequency higher.

#### **Audio Frequency Correction Range, ASFCR**

There are two ranges of audio frequency correction, high and low, defined by ASFCR. For low ppm correction, ASFCR should be reset logic low. For higher ppm correction, ASFCR should be set logic high.

#### Audio Frequency Correction Enable, ASFCE

Audio sampling frequency correction is enabled by ASFCE. Set logic high, frequency correction is enabled. If ASFCE is reset logic low, audio frequency correction is disabled, providing a sampling frequency of MC/1625 or MC/3250 depending on MCSEL in the test register.

#### **Audio Sampling Rate Example**

The AUDFER register allows adjustments to the audio rate (nominally 8 ks/s) over a range of ±20 ppm with a resolution of less than 0.1 ppm. To cover this range with the indicated resolution, the ASFCR bit should be set to ZERO to make adjustments within the ±7.5 ppm range and set to 1 otherwise. Given the desired ppm adjustment, the decimal value to be programmed into MAG[12:0] is given by:

$$MAG = 8192 - \frac{10^6}{13 \cdot ASFC_{ppm} (128 - 112 \cdot ASFCR)}$$

Example, if the desired correction is +1.7 ppm; ASFCR = 0, ASFCppm = 1.7, then Mag is 7838 from the equation above. The AUDFCR register should be programmed to 0x9e9e. If the desired correction had been -1.7 ppm, then the ASFCS bit would have been set to 1and AUDFCR register would have been programmed to 0xbe9e.

#### Frame Counter Register, FC (Address 0x8)

The frame counter register, FC, is either a modulus 51 counter, or else a modulus 26 counter, depending on the setting of the MFRAME bit in the timing control register, TCNTRL. When MFRAME is set high, the FC counter is modulus 51 (counter cycles 0 through 50 and then back to 0, i.e., frame MOD 51), and when MFRAME is reset low, the FC counter is modulus 26.

FC keeps track of the value of the frame number and can be preset to any number from 0 to decimal 50. FC increments when the quarter-bit counter, QBC, rolls over from 4999 to 0. The value of FC can be read at any time.

**Table 14. Frame Counter Register**

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|---|---|---|---|----|----|----|----|----|----|

| Label | Х  | Х  | Х  | Х  | Х  | X  | Х | Х | Х | Х | FC | FC | FC | FC | FC | FC |

|       |    |    |    |    |    |    |   |   |   |   | 5  | 4  | 3  | 2  | 1  | 0  |

#### Quarter-Bit Counter Register, QBC (Address 0x9)

The quarter-bit counter register is a modulus 5000 counter (cycles from 0 to 4999 and then back to 0) that counts in half-quarter (1/8) bit increments, or at a rate of 13/6 MHz. The counter can be preset to any number from 0 to decimal 4999, and can be read at any time. Note that the counter is written and read with quarter-bit accuracy, and the half-quarter (1/8) bit is only affected by the 13/6 MHz clock, or the INCR/DECR bits in TCNTRL.

Table 15. Quarter-Bit Counter Register Bit Definition

| E | Bit# | 15 | 14 | 13 | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|------|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| L | abel | Х  | Х  | Х  | QBC |

|   |      |    |    |    | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

### QBC Jump, QBCJUMP[12:0] (Address 0xC)

The AT&T CSP1088 supports synchronous QBC offset modification of the QBC register value for large offsets. The QBC register accepts unsigned magnitude values of 0 through 4999. When QBCJUMP is written, the QBC counter will change to its current value plus the QBC Jump value modulus 5000, i.e., (QBC + N) MOD 5000. Thus, if QBCJUMP is written N, then written 5000 – N, the original QBC timeline will remain exactly as if QBC Jump was never written, except for the time between writes. FC, the frame counter, is not affected by QBCJUMP. The delay from RWN rising edge to change in QBC value is no more than two quarter-bit clocks (i.e., half a symbol). The new QBC value is used immediately in the comparisons for time match given that TCNTRL remained constant.

**Table 16. QBCJUMP Register Bit Definition**

| Bit # | 7     | 6     | 5     | 4      | 3          | 2      | 1     | 0     |

|-------|-------|-------|-------|--------|------------|--------|-------|-------|

| Label | QBCJ7 | QBCJ6 | QBCJ5 | QBCJ4  | QBCJ3      | QBCJ2  | QBCJ1 | QBCJ0 |

| Bit # | 15    | 14    | 13    | 12     | <b>1</b> 1 | 10     | 9     | 8     |

| Label | r     | r     | r     | QBCJ12 | QBCJ11     | QBCJ10 | QBCJ9 | QBCJ8 |

#### Timing and Control Register, TCNTRL (Address 0xA)

The timing and control register, TCNTRL, sets the modulus of the ETCI counter and the modulus of the frame counter. It also can reset the quarter-bit and frame counters to 0, and it controls the serial output port, TCNTRL can also be used to increment or decrement the quarter-bit counter in eighth-bit steps.

Table 17, Description of the Timing and Control Register, TCNTRL

| Bit # | 7      | 6           | 5        | 4       | 3     | 2     | 1      | 0      |

|-------|--------|-------------|----------|---------|-------|-------|--------|--------|

| Label | SERSPE | SERLEN<br>1 | SERLEN 0 | SERDIR  | DPT 3 | DPT 2 | DPT 1  | DPT 0  |

|       |        |             |          | l       |       |       |        |        |

| Bit # | 15     | 14          | 13       | 12      | 11    | 10    | 9      | 8      |

| Label | r      | r           | INCQBCFC | TIMECLK | DECR  | INCR  | CRESET | MFRAME |

#### Depth (DPT[3:0]) Bits

The event timing and control index counter, ETCI, indexes which one of the 15 event timing and control registers. ETC[14:0], is active. The ETCl counter increments from 0 up to one less than the number specified in the depth bits, DPT[3:0], and then returns to 0 within two 13 MHz clock cycles. The depth bits, therefore, set the modules of the ETCI counter.

In the case of the DPT [3:0] bits all set to a logic low, none of the ETC[14:0] words are ever indexed, and no events are generated.

In the case of the DPT[3:0] bits set to 0001, the ETCl counter will only index Event Timing and Control Register 0 (ETC0). Given a nonmodified (no increment or decrement) quarter-bit counter scenario, a DPT[3:0] = 0001 condition will cause ETC0 to be executed six times when the EQN bit of ETC0 equals the quarter-bit counter. When this is happening, it may not be obvious for most ETC0 values, but when the DSPI bit is set in ETC, the INTR pin of the CSP1088 may behave abnormally, depending on the interrupt servicing latency of the software.

#### Serial Output Direction Bit, SERDIR

The frequency selection registers, FREQ[5:0], can be used to program an external frequency synthesizer via the serial output pins, SERCK, SERDA, and SERLE. The serial output direction bit, SERDIR, controls whether the data is clocked from LSB to MSB, or from MSB to LSB. When the SERDIR bit is set to a logic high, the data is transmitted from MSB to LSB. When the SERDIR bit is reset to a logic low, the data is clocked from the LSB to the MSB.

#### Serial Output Length Bits (SERLEN[1:0])

The frequency selection registers, FREQ[5:0], can be used to program an external frequency synthesizer via the serial output pins, SERCK, SERDA, and SERLE. The serial output length bits, SERLEN[1:0], control whether the output is 8 bits, 16 bits, or 24 bits long.

**Table 18. Serial Output Length Bit Definition**

| SERLEN 1 | SERLEN 0 | Description                   |

|----------|----------|-------------------------------|

| 0        | 0        | Send first 8 bits (FS[7:0])   |

| 0        | 1        | Send first 16 bits (FS[15:0]) |

| 1        | 0        | Send first 24 bits (FS[23:0]) |

| 1        | 1        | Reserved                      |

0050026 0017655 717

# Timing and Control Register, TCNTRL (Address 0xA) (continued)

#### Serial Output Speed Bit, SERSPE

The frequency selection registers, FREQ[5:0], can be used to program an external frequency synthesizer via the serial output pins, SERCK, SERDA, and SERLE. When the serial output speed bit, SERSPE, is set to a logic high, the serial output data rate is 1.08 Mbits/s. When SERSPE is reset to a logic low, the serial output data rate is 0.54 Mbits/s.

#### Modulus of Frame Counter Bit, MFRAME

When the MFRAME bit is set to a logic high, the frame counter, FC, is a modulus 51 counter (that is, the counter will cycle from 0 to 50 and back to 0 again). When the MFRAME bit is reset to a logic low, the frame counter is a modulus 26 counter and cycles from 0 to 25 and back to 0.

#### Counter Reset Bit, CRESET

When the counter reset bit CRESET is set from a logic low to a logic high, the frame counter, FC, and quarter bit counter (QBC) are reset to 0. The CRESET bit self-resets to 0, one 13 MHz clock cycle after the logic low to logic high transition has been synchronized to the AT&T CSP1088 internal clock. Resetting the CRESET bit to a logic low does not affect the frame counter or quarter bit counter.

#### **INCR/DECR**

The INCR and DECR bits, embedded in the TCNTRL register, adjust the QBC clock by 1/8 symbol. Each logic high write to INCR causes the QBC counter to advance by 1/8 of a symbol time; a logic low write to INCR has no affect on the QBC clock. Each logic high write to DECR causes the QBC counter to delay by 1/8 of a symbol time; a logic low write to DECR has no affect on the QBC clock.

Note that back-to-back writes of the INCR/DECR bits (to quickly increment or delay the QBC counter) need to be separated by two NOPs if the DSP is running at higher than 26 MIPS. For a DSP running at 26 MIPS or

lower, back-to-back writes need not be separated by NOPs. (Due to the asynchronous DSP-CSP interface.)

#### Timer Clock Enable Bit, TIMECLK

When the timer clock enable bit, TIMECLK, is set to a logic high, the clock to the quarter-bit counter is enabled. When reset to a logic low, the clock to the quarter-bit counter is disabled.

#### **ETCI Increment Control Bit, INCQBCFC**

When the ETCI increment control bit, INCQBCFC, is set to a logic high, the ETCI increments when both a quarter bit timing match occurs and the criteria defined by the current ETC register's EVEN/ODD bits are met. When reset to a logic low, the ETCI increments only when a quarter bit timing match occurs.

# Event Timing and Control Index Register, ETCI (Address 0xB)

The event timing and control index register, ETCI, points to one of 15 event timing and control registers, ETC[14:0]. See page 7, under Event Timing and Control State Machine, for ETCI increment criteria. The ETCI counter is programmable, and the depth that the ETCI counter counts to before resetting to 0 is set in the TCNTRL register.

# Event Timing and Control Registers, ETC[14:0] (Address 0x10—0x3C)

There are 15 event timing and control registers, each containing three 16-bit words, ETC0[14:0], ETC1[0:14], and ETC2[14:0]. The ETCI index counter points to which one (if any) of the 15 ETC registers is active. When the timing portion of the indexed register matches the quarter-bit counter, QBC, and the EVEN and ODD bit criteria are met, then the control portion of the indexed ETC register is executed. The ETCI counter is automatically incremented to point to the next ETC register.

Table 19. Event Timing and Control Index Register ETCI

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|-------|----|----|----|----|----|----|---|---|---|---|---|---|------|------|------|------|

| Label | Х  | Х  | Х  | Х  | Х  | X  | Х | Х | Х | Х | Х | Х | ETCI | ETCI | ETCI | ETCI |

|       |    |    |    |    |    |    |   |   |   |   |   |   | 3    | 2    | 1    | 0    |

**■** 0050026 0017656 653 **■**

# Event Timing and Control Registers, ETC[14:0] (Address 0x10—0x3C) (continued)

Table 20. Event Timing and Control Word 0, ETC0[0:14] Bit Definition

| Bit # | 7          | 6         | 5          | 4         | 3         | 2         | 1        | 0        |

|-------|------------|-----------|------------|-----------|-----------|-----------|----------|----------|

| Labei | EQN        | EQN       | EQN        | EQN       | EQN       | EQN       | EQN      | EQN      |

|       | 7          | 6         | 5          | 4         | 3         | 2         | 1        | 0        |

|       |            |           |            |           |           |           |          |          |

| Bit#  | 15         | 14        | 13         | 12        | 11        | 10        | 9        | 8        |

| Bit # | 15<br>DSPI | 14<br>ODD | 13<br>EVEN | 12<br>EQN | 11<br>EQN | 10<br>EQN | 9<br>EQN | 8<br>EQN |

#### Table 21. Event Timing and Control Word 1, ETC1[14:0] Bit Definition

| Bit # | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Label | BOE | BIE | EFN | EFN | EFN | EFN | EFN | EFN |

|       |     |     | 5   | 4   | 3   | 2   | 1   | 0   |

| Bit # | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| Label | r   | BIG | BIG | BIG | BIG | FR  | FR  | FR  |

|       |     | 3   | 2   | 1   | 0   | 2   | 1   | 0   |

#### Table 22. Event Timing and Control Word 2, ETC2[14:0] Bit Definition

| Bit # | 7               | 6        | 5          | 4    | 3          | 2    | 1         | 0         |

|-------|-----------------|----------|------------|------|------------|------|-----------|-----------|

| Label | OCTL            | OCTL     | OCTL       | OCTL | OCTL       | OCTL | OCTL      | OCTL      |

|       | 7               | 6        | 5          | 4    | 3          | 2    | 1         | 0         |

|       |                 |          |            |      |            |      |           |           |

| Bit # | 15              | 14       | 13         | 12   | 11         | 10   | 9         | 8         |

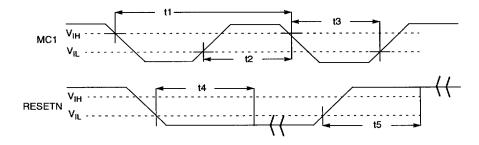

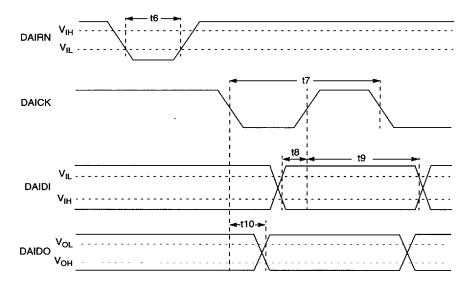

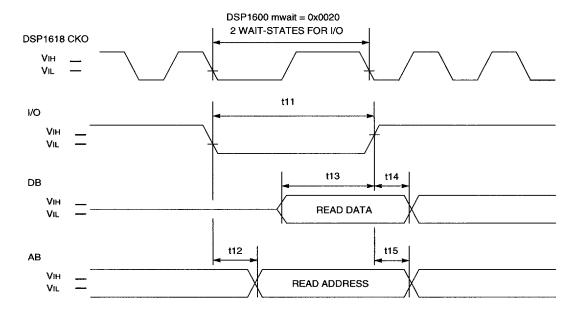

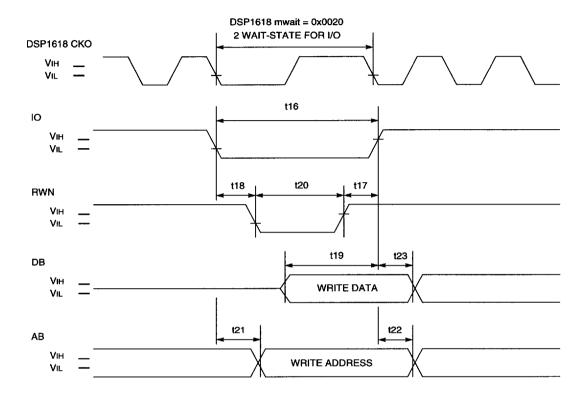

| Bit # | <b>15</b><br>BL | 14<br>BL | 13<br>OCTL |      | 11<br>OCTL |      | 9<br>OCTL | 8<br>OCTL |