# CMOS-4L 1.5-MICRON LOW-VOLTAGE **CMOS GATE ARRAYS**

February 1990

## Description

NEC's CMOS-4L family of 1.5-micron gate arrays are high-density, low-voltage application-specific integrated circuits (ASICs) that offer unique solutions for batterydriven circuits. Supply voltages ranging from 1.0 V to 5.5 V make this family ideal for such applications as portable communications equipment and measuring instruments.

The CMOS-4L family combines NEC's proprietary circuit architecture and advanced 1.5-micron silicon-gate CMOS technology in gate array sizes from 800 to 5600 cells. A variety of package options is available.

### **Features**

In addition to the advantages of low cost and high reliability, CMOS-4L gate arrays provide these features.

- □ Technology: 1.5-micron, silicon-gate CMOS; two-layer aluminum metallization

- □ Low power supply voltage: 1.0 to 5.5 V

- □ Low standby power consumption (typical):

- $0.01 \,\mu\text{A} \,(V_{DD} = 1.5 \,V)$

- □ High speed

- □ Internal gate, 2-input NAND:

- 2.2 ns (F/O = 3, L = 3 mm,  $V_{DD} = 5.0 \text{ V}$ )

- 10 ns (F/O = 3, L = 3 mm,  $V_{DD} = 1.5 \text{ V}$ )

High drive:  $I_{OL} = 3 \text{ mA} (V_{DD} = 1.5 \text{ V})$

- □ Ambient temperature: -10° to 85° C

- Block library with more than 120 macros

- Input buffers

- CMOS

- Schmitt

- Oscillator/multivibrator interface

- With pull-up or pull-down resistor

- Output buffers

- Normal

- Open-drain

- Three-state

- Bidirectional buffers

- Packages

- Plastic DIP: 40-pin, 64-pin

- Plastic QFP: 24-pin to 120-pin

- Direct access to NEC Design Centers through communication network or telephone dial-up

- Quick turnaround time: 3 to 6 weeks

Figure 1. Sample CMOS-4L Packages

# **Publications**

This data sheet contains specifications, package information, and operational data for CMOS-4L gate array devices. Additional design information is available in NEC's CMOS-4L Design Manual and CMOS-4L Block Library. Contact your local NEC Design Center or the NEC Literature Center for further ASIC design information; see the back of this data sheet for locations and phone numbers.

### Gate Array Sizes

| μ <b>PD</b> | Gates | Signal<br>Pins (Max) |

|-------------|-------|----------------------|

| 65007       | 858   | 62                   |

| 65014       | 1656  | 82                   |

| 65026       | 2457  | 100                  |

| 65033       | 3360  | 106                  |

| 65045       | 4320  | 120                  |

| 65052       | 5632  | 138                  |

- (1) Usable gate count is up to 95% of specified gate count.

- (2) Actual pin count is determined by package size and type.

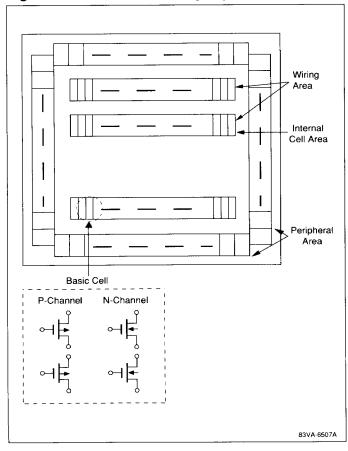

Figure 2. CMOS-4L Gate Array Layout

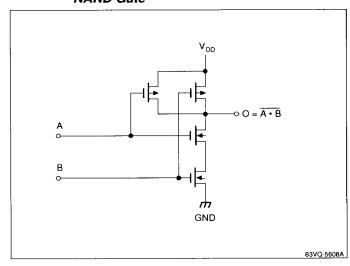

Figure 3. Cell Configured as a Two-Input NAND Gate

### **Circuit Architecture**

CMOS-4L gate arrays are built with NEC's proven channeled architecture. As shown in figure 2, CMOS gate array chips are divided into peripheral and internal cell areas. The peripheral area contains input and output buffers that isolate the internal cells from high-energy external signals. The internal cell area is an array of basic cells, each composed of two p-channel MOS transistors and two n-channel MOS transistors. These p-channel and n-channel transistors are sized to offer a superb ratio of speed to silicon area.

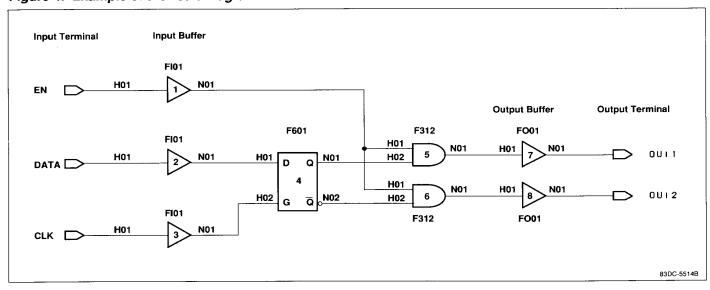

Figure 4. Example of a Circuit Diagram

# **Recommended Operating Conditions**

$T_A = -10 \text{ to } +85^{\circ} \text{ C}$

| Parameter                                        | Symbol                          | Min                  | Max                  | Unit | Conditions              |

|--------------------------------------------------|---------------------------------|----------------------|----------------------|------|-------------------------|

| Power supply voltage                             | V <sub>DD</sub>                 | 1.0                  | 5.5                  | ٧    | CMOS level              |

| Input voltage                                    | V <sub>I</sub>                  | 0                    | V <sub>DD</sub>      | ٧    | CMOS level              |

| Low-level input voltage                          | V <sub>IL</sub>                 | 0                    | 0.3 V <sub>DD</sub>  | ٧    | V <sub>DD</sub> ≥ 2.0 V |

|                                                  |                                 | 0                    | 0.2 V <sub>DD</sub>  | ٧    | V <sub>DD</sub> < 2.0 V |

| High-level input voltage                         | V <sub>IH</sub>                 | 0.7 V <sub>DD</sub>  | V <sub>DD</sub>      | V    | V <sub>DD</sub> ≥ 2.0 V |

|                                                  |                                 | 0.8 V <sub>DD</sub>  | V <sub>DD</sub>      | ٧    | V <sub>DD</sub> < 2.0 V |

| Input rise or fall time (Note 1)                 | t <sub>R</sub> , t <sub>F</sub> | 0                    | 300                  | ns   | Normal input            |

| Positive Schmitt-trigger voltage                 | V <sub>P</sub>                  | 0.35 V <sub>DD</sub> | 0.85 V <sub>DD</sub> | ٧    | V <sub>DD</sub> ≥ 2.0 V |

| Negative Schmitt-trigger voltage                 | V <sub>N</sub>                  | 0.15 V <sub>DD</sub> | 0.65 V <sub>DD</sub> | ٧    | V <sub>DD</sub> ≥ 2.0 V |

| Hysteresis voltage (Note 2)                      | V <sub>H</sub>                  | 0.2                  | 1.8                  | ٧    | V <sub>DD</sub> ≥ 2.0 V |

| Schmitt-trigger input rise or fall time (Note 1) | t <sub>R</sub> , t <sub>F</sub> | 0                    | 25                   | μs   |                         |

#### Notes:

- (1) Does not apply to CLK, SET, or RESET signals.

- (2) Hysteresis voltage is available only when V $_{DD} \ge 2.0$  V. V $_{H}$  (min) can be determined as follows: V $_{H}$  (min) = (V $_{DD} 1.5$ ) x 0.4 V.

# Input/Output Capacitance

| Terminal | Symbol           | Тур | Max | Unit | Conditions              |

|----------|------------------|-----|-----|------|-------------------------|

| Input    | C <sub>IN</sub>  | 10  | 20  | рF   | $V_{DD} = V_{I} = 0 V;$ |

| Output   | C <sub>OUT</sub> | 10  | 20  | pF   | f = 100 kHz             |

| I/O      | C <sub>I/O</sub> | 10  | 20  | pF   |                         |

# **Absolute Maximum Ratings**

$T_{A} = +25^{\circ}C$

| A                                       |                                   |

|-----------------------------------------|-----------------------------------|

| Power supply voltage, V <sub>DD</sub>   | -0.3 to +7.0 V                    |

| Input voltage, V <sub>I</sub>           | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Output current, I <sub>O</sub>          | 20 mA                             |

| Operating temperature, T <sub>OPT</sub> | −10 to +85° C                     |

| Storage temperature, T <sub>STG</sub>   | −65 to +150° C                    |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the Recommended Operating Conditions.

## **AC Characteristics**

$T_{\Delta} = 0 \text{ to } +70^{\circ} \text{ C}$

| Parameter                 | Symbol           | Min | Тур | Max | Unit | Conditions                                                              |

|---------------------------|------------------|-----|-----|-----|------|-------------------------------------------------------------------------|

| Toggle frequency          | f <sub>TOG</sub> |     |     | 5   | MHz  | F/O = 1; V <sub>DD</sub> = 1.5 V                                        |

| Delay time, internal gate | t <sub>PD</sub>  |     | 2.2 |     | ns   | F/O = 3; L = 3 mm; V <sub>DD</sub> = 5.0 V                              |

|                           |                  |     | 10  |     | ns   | F/O = 3; L = 3 mm; V <sub>DD</sub> = 1.5 V; T <sub>A</sub> = 25° C      |

|                           |                  |     | 88  |     | ns   | F/O = 3; L = 3 mm; V <sub>DD</sub> = 1.0 V                              |

| Delay time, buffer        |                  |     |     |     |      |                                                                         |

| Input                     | t <sub>PD</sub>  |     | 12  |     | ns   | F/O = 3; L = 3 mm; V <sub>DD</sub> = 1.5 V; T <sub>A</sub> = 25° C      |

| Output                    | t <sub>PD</sub>  |     | 24  |     | ns   | C <sub>L</sub> = 15 pF; V <sub>DD</sub> = 1.5 V; T <sub>A</sub> = 25° C |

### **CMOS-4L**

### **DC Characteristics**

$V_{DD}^{}= 1.0 \text{ to } 5.5 \text{ V; } T_{A}^{}= -10^{\circ} \text{ to } +85^{\circ} \text{ C}$

| Parameter                        | Symbol          | Min                  | Тур  | Max  | Unit | Conditions                                                  |

|----------------------------------|-----------------|----------------------|------|------|------|-------------------------------------------------------------|

| Static current (Note 1)          | IL              |                      | 0.01 | 80   | μА   | V <sub>I</sub> = V <sub>DD</sub> or GND (Notes 2 and 3)     |

| Input leakage current            |                 |                      |      |      |      |                                                             |

| Normal input                     | l <sub>i</sub>  |                      | 10 ⁴ | 1    | μА   | $V_I = V_{DD}$ or GND                                       |

| With pull-up                     | I <sub>I</sub>  | -0.01                | -3   | -200 | μΑ   | V <sub>I</sub> = GND                                        |

| With pull-down                   | I <sub>1</sub>  | 0.01                 | 3    |      | μА   | $V_{I} = V_{DD}$                                            |

| Oscillator block                 | I <sub>I</sub>  |                      | 0.2  |      | μА   | $V_1 = V_{DD}$ or GND                                       |

| Dynamic current                  | I <sub>DD</sub> |                      | 0.3  |      | μА   | Per cell per 100 kHz                                        |

| Off-state output leakage current | l <sub>oz</sub> |                      |      | 1    | μА   | $V_O = V_{DD}$ or GND                                       |

| Low-level output current         | l <sub>OL</sub> | 0.8                  | 3.0  |      | mA   | $V_{OL} = 0.4 \text{ V}; V_{DD} \ge 1.2 \text{ V}$          |

|                                  | l <sub>OL</sub> | 0.18                 |      |      | mA   | V <sub>OL</sub> = 0.4 V; V <sub>DD</sub> < 1.2 V            |

| High-level output current        | Гон             | -0.3                 | -1.0 |      | mA   | $V_{OH} = V_{DD} - 0.4 \text{ V}; V_{DD} \ge 1.2 \text{ V}$ |

|                                  | Гон             | -0.015               |      |      | mA   | $V_{OH} = V_{DD} - 0.4 \text{ V}; V_{DD} < 1.2 \text{ V}$   |

| Low-level output voltage         | V <sub>OL</sub> |                      |      | 0.1  | ٧    | I <sub>OL</sub> = 0 mA                                      |

| High-level output voltage        | V <sub>OH</sub> | V <sub>DD</sub> -0.1 |      |      | ٧    | I <sub>OH</sub> = 0 mA                                      |

#### Notes:

- (1) Not applicable to designs using oscillators or to interface blocks with pull-up or pull-down resistors.

- (2) Typical conditions:  $T_A = 25$  °C;  $V_{DD} = 1.5$  V, except as noted under Conditions.

- (3) Maximum conditions:  $T_A = 55^{\circ}C$ ;  $V_{DD} = 3.6 V$ .

# Package Plan

|                              | μ <b>ΡD65007</b> | μ <b>PD65014</b> | μ <b>PD65026</b> | μ <b>PD65033</b> | μ <b>PD65045</b> | μ <b>PD65052</b> |

|------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Plastic Shrink DIP (SDIP)    |                  |                  |                  |                  |                  |                  |

| 40-pin                       | ×                | X                | X                |                  |                  |                  |

| 64-pin                       | Х                | X                | Х                | X                | X                | Х                |

| Small-Outline Package (SOP)  |                  |                  |                  |                  |                  |                  |

| 24-pin                       | X                | X                | X                |                  |                  |                  |

| Plastic Flatpack (QFP)       |                  |                  |                  |                  |                  |                  |

| 44-pin                       | X                | x                | X                |                  |                  |                  |

| 52-pin                       | ×                | ×                | X                | X                |                  |                  |

| 64-pin                       | Х                | Х                | X                | х                | Х                | Х                |

| 80-pin                       |                  | x                | X                | x                | X                | Х                |

| 100-pin                      |                  |                  | X                | X                | X                | Х                |

| 120-pin                      |                  |                  |                  |                  | х                | Х                |

| 136-pin                      |                  |                  |                  |                  |                  | Х                |

| Thin Plastic Flatpack (TQFP) |                  |                  |                  |                  |                  |                  |

| 80-pin                       | X                | X                | X                | х                | Х                | Х                |

Note: All packages may not be available. For current package availability, please contact your nearest NEC ASIC Design Center.

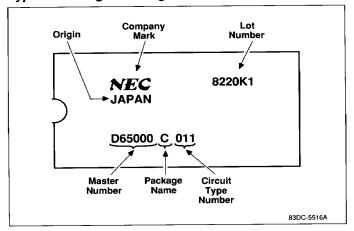

### Typical Package Marking

# **NEC's ASIC Design System**

CMOS-4L gate arrays are fully supported by NEC's network of ASIC Design Centers. (Design Centers are listed on the back of this data sheet.)

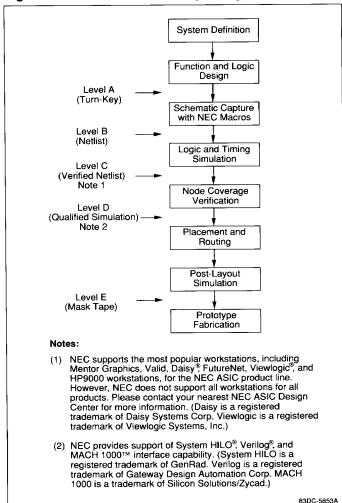

Design flow for CMOS-4L gate arrays is shown in figure 5. Users can enlist design center support at any step in the design flow before actual manufacturing. Figure 5 shows the various levels at which design center support may begin—anywhere from level A through level E. Level C, "Verified Netlist," is the most popular interface.

NEC supports its ASIC products with a comprehensive CAD system that significantly reduces the time and expense usually associated with the development of semi-custom devices. NEC's OpenCAD™ integration system supports tools for floor-planning, logic synthesis, automatic test generation, accelerated fault grading and full timing simulation, and advanced place-and-route algorithms. These advanced CAD tools ensure accurate designs.

Sample design kits are available at no charge to qualified users: contact an NEC ASIC Design Center for more information. (Software licensing required—NEC reserves the right to prioritize support based on user requirements.)

OpenCAD is a trademark of NEC Electronics Inc.

Figure 5. CMOS-4L Gate Array Design Flow

### **Block Library List**

#### Interface Blocks

| Block   |                                                                           |       |

|---------|---------------------------------------------------------------------------|-------|

| Name    | Description                                                               | Celis |

| Inputs  |                                                                           |       |

| FI01    | Input buffer (CMOS level)                                                 | 1     |

| FIS1    | Input buffer (CMOS-Schmitt level)                                         | 1     |

| FID1    | Input buffer (CMOS level), pull-down res.                                 | 1     |

| FIU1    | Input buffer (CMOS level), pull-up res.                                   | 1     |

| FDS1    | Input buffer (CMOS-Schmitt level), pull-down res.                         | 1     |

| FUS1    | Input buffer (CMOS-Schmitt level), pull-up res.                           | 1     |

| Outputs | 3                                                                         |       |

| B008    | Output buffer (3-state)                                                   | 1     |

| FO01    | Output buffer (normal), I <sub>OH</sub> , I <sub>OL</sub> = 0.015/0.18 mA | 1     |

# CMOS-4L

| Interface | Blocks | (Cont.) |

|-----------|--------|---------|

|-----------|--------|---------|

| Block<br>Name | Description                                                                   | Cells |

|---------------|-------------------------------------------------------------------------------|-------|

| Open Di       | rain Outputs                                                                  |       |

| EXT1          | Output buffer (N-ch), I <sub>OL</sub> = 0.18 mA                               | 1     |

| EXT2          | Output buffer (P-ch), I <sub>OH</sub> = 0.015 mA                              | 1     |

| EXT3          | Output buffer (N-ch); pull-up res., I <sub>OL</sub> = 0.18 mA                 | 1     |

| EXT4          | Output buffer (P-ch); pull-down res., $I_{OH} = 0.015 \text{ mA}$             | 1     |

| Three-S       | tate I/Os                                                                     |       |

| B003          | I/O buffer (CMOS level in)                                                    | 1     |

| BSI3          | 1/O buffer (CMOS-Schmitt level),                                              | 1     |

|               | I <sub>OH</sub> /I <sub>OL</sub> = 0.015/0.18 mA                              |       |

| B0D3          | I/O buffer (CMOS level); pull-down res.,                                      | 1     |

|               | $I_{OH/}I_{OL} = 0.015/0.18 \text{ mA}$                                       |       |

| B0U3          | I/O buffer (CMOS level); pull-up res.,                                        | 1     |

|               | $I_{OH}I_{OL} = 0.015/0.18 \text{ mA}$                                        |       |

| BSD3          | I/O buffer (CMOS-Schmitt level); pull-down res.,                              | 1     |

|               | I <sub>OH</sub> /I <sub>OL</sub> = 0.015/0.18 mA                              |       |

| BSU3          | I/O buffer (CMOS-Schmitt level); pull-up res.,                                | 1     |

|               | I <sub>OH</sub> ,I <sub>OL</sub> = 0.015/0.18 mA                              |       |

| Three-S       | tate Outputs                                                                  |       |

| B0D8          | Output buffer, pull-down res.,                                                | 1     |

|               | $I_{OH}/I_{OL} = 0.015/0.18 \text{ mA}$                                       |       |

| B0U8          | Output buffer, pull-up res., I <sub>OH</sub> ,I <sub>OL</sub> = 0.015/0.18 mA | 1     |

| Oscillat      | ors (Note 1)                                                                  |       |

| OSI1          | Oscillator input buffer                                                       | 1     |

| OSO1          | Oscillator output buffer                                                      | 1     |

| OSO3          | Oscillator output buffer                                                      | 1     |

| Others (      | Note 1)                                                                       |       |

| OSF1          | Feedback resistance for oscillator                                            | 1     |

| SHT1          | Monostable multivibrator                                                      | 1     |

| Inverter      | s                                                                             |       |

| F101          | Inverter, 1-in (F/O = 10)                                                     | 1     |

| F102          | Inverting buffer, 1-in (F/O = 20)                                             | 1     |

| F103          | Inverting buffer, 1-in (F/O = 30)                                             | 2     |

| F104          | Inverting buffer, 1-in (F/O = 40)                                             | 2     |

### Note:

(1) More than one oscillator pin must be used in combination. Some valid combinations are:

OSI1 + OSO1 OSI1 + OSO3 + OSF1

### **Function Blocks**

| Block<br>Name | Description                           | Cells |

|---------------|---------------------------------------|-------|

| Buffers       |                                       |       |

| F111          | Non-inverting buffer, 1-in (F/O = 10) | 1     |

| F112          | Non-inverting buffer, 1-in (F/O = 20) | 2     |

| F113          | Non-inverting buffer, 1-in (F/O = 30) | 2     |

| F114          | Non-inverting buffer, 1-in (F/O = 40) | 3     |

| F116          | Non-inverting buffer, 1-in (F/O = 64) | 5     |

| NOR G         | ates                                  |       |

| F202          | 2-Input NOR                           | 1     |

| F203          | 3-Input NOR                           | 2     |

| F208          | 8-Input NOR                           | 7     |

| OR Gat        | es                                    |       |

| F212          | 2-Input OR                            | 2     |

| F213          | 3-Input OR                            | 2     |

| NAND (        | Gates                                 |       |

| F302          | 2-Input NAND                          | 1     |

| F303          | 3-Input NAND                          | 2     |

| F304          | 4-Input NAND                          | 2     |

| F308          | 8-Input NAND                          | 7     |

| AND G         | ates                                  |       |

| F312          | 2-Input AND                           | 2     |

| F313          | 3-Input AND                           | 2     |

| F314          | 4-Input AND                           | 3     |

| AND-N         | OR Gates                              |       |

| F421          | 2-Wide, 1-2-input AND-OR inverter     | 2     |

| F422          | 3-Wide, 1-1-2-input AND-OR inverter   | 2     |

| F423          | 2-Wide, 1-3-input AND-OR inverter     | 2     |

| F424          | 2-Wide, 2-2-input AND-OR inverter     | 2     |

| F425          | 3-Wide, 2-2-2-input AND-OR inverter   | 3     |

| F426          | 2-Wide, 3-3-input AND-OR inverter     | 3     |

| F442          | 2-Wide, 4-4-input AND-OR inverter     | 4     |

| OR-NA         | ND Gates                              |       |

| F431          | 2-Wide, 1-2-input OR-AND inverter     | 2     |

| F432          | 3-Wide, 1-1-2-input OR-AND inverter   | 2     |

| F433          | 2-Wide, 1-3-input OR-AND inverter     | 2     |

| F434          | 2-Wide, 2-2-input OR-AND inverter     | 2     |

| F435          | 2-Wide, 2-3-input OR-AND inverter     | 3     |

| F436          | 2-Wide, 3-3-input OR-AND inverter     | 3     |

| F454          | 4-Wide, 2-2-2-input OR-AND inverter   | 4     |

| Functi        | on Blocks (Cont.)                    |          |

|---------------|--------------------------------------|----------|

| Block<br>Name | Description                          | Cells    |

| Drivers       |                                      |          |

| F501          | Clock driver                         | 1        |

| F502          | Dual clock driver                    | 2        |

| Exclusi       | ve-OR, Exclusive-NOR Gates           |          |

| F511          | EX-OR                                | 3        |

| F512          | EX-NOR                               | 3        |

| Full Ad       | ders                                 |          |

| F521          | Full adder                           | 7        |

| F523          | 4-Bit binary full adder              | 30       |

| Three-S       | state Buffers                        |          |

| F531          | Buffer with Enable                   | 3        |

| F532          | Buffer with Enable                   | 3        |

| Decode        | ers                                  |          |

| F561          | 2-to-4 Decoder                       | 6        |

| F981          | 2-to-4 Decoder with Enable           | 9<br>20  |

| F982          | 3-to-8 Decoder with Enable           |          |

| Multiple      | exers                                |          |

| F569          | 8-1 Multiplexer                      | 17       |

| F570          | 4-1 Multiplexer                      | 8<br>11  |

| F571<br>F572  | 2-1 Multiplexer Quad 2-1 Multiplexer | '''      |

| Parity (      | Generators                           |          |

| F581          | 8-Bit odd                            | 18       |

| F582          | 8-Bit even                           | 18       |

| Latche        | S                                    |          |

| F595          | R-S latch                            | 4        |

| F601          | D latch                              | 3        |

| F602          | D latch with Reset                   | 4        |

| F603          | D latch with Reset                   | 4        |

| F604          | D latch with G driver                | 3        |

| F605          | D latch with G driver, Reset         | 4        |

| F901<br>F902  | 4-Bit latch<br>8-Bit latch           | 10<br>18 |

| Flip-Flo      |                                      |          |

| F596          | Synchronous R-S F/F with Set-Reset   | 9        |

| F611          | D F/F                                | 5        |

| Functi        | Function Blocks (Cont.)                               |        |  |

|---------------|-------------------------------------------------------|--------|--|

| Block<br>Name | Description                                           | Cells  |  |

| Flip-Flo      | ps (Cont.)                                            |        |  |

| F614          | D F/F with Set-Reset                                  | 7      |  |

| F617          | D F/F with Set-Reset                                  | 7      |  |

| F631          | D F/F with C                                          | 5      |  |

| F637          | D F/F with C, Set-Reset                               | 5      |  |

| F641          | D F/F, buffered out                                   | 6      |  |

| F644          | D F/F with Set-Reset; buffered out                    | 8      |  |

| F647          | D F/F with Set-Reset; buffered out                    | 8      |  |

| F661          | D F/F with C; buffered out                            | 6      |  |

| F667          | D F/F with C, Set-Reset; buffered out                 | 8      |  |

| F922          | 4-Bit D F/F with Reset                                | 22     |  |

| F924          | 4-Bit D F/F                                           | 17     |  |

| Shift Re      | gisters                                               |        |  |

| F911          | 4-Bit register with Reset                             | 22     |  |

| F912          | 4-Bit serial/parallel register                        | 24     |  |

| F913          | 4-Bit parallel-in register with Reset                 | 31     |  |

| F914          | 4-Bit register                                        | 17     |  |

| Toggle        | Flip-Flops                                            |        |  |

| F714          | Toggle with Set-Reset                                 | 7      |  |

| F717          | Toggle with Set-Reset                                 | 7      |  |

| F737          | Toggle with Set-Reset                                 | 7      |  |

| F744          | Toggle with Set-Reset; buffered out                   | 8      |  |

| F747          | Toggle with Set-Reset; buffered out                   | 8      |  |

| F767          | Toggle with Set-Reset; buffered out                   | 8      |  |

| F791          | Toggle with Set-Reset Toggle Enable                   | 9      |  |

| F792          | Toggle with Set-Reset Toggle Enable                   | 9      |  |

| J-K Flip      | -Flops                                                |        |  |

| F771          | F/F, buffered out                                     | 9      |  |

| F774          | F/F with Set-Reset; buffered out                      | 11     |  |

| F777          | F/F with Set-Reset; buffered out                      | 11     |  |

| F781          | F/F with C, buffered out                              | 9      |  |

| F787          | F/F with C; Set-Reset, buffered out                   | 11<br> |  |

| Counte        | rs                                                    |        |  |

| F962          | 4-Bit synchronous binary up, with Reset; buffered out | 34     |  |

| Special       |                                                       |        |  |

| BUSA          | Bus array                                             | 0      |  |

| F091          | H, L level generator                                  | 1      |  |

| F093          | Interface block for oscillator buffer                 | 1      |  |

#### **NEC ASIC DESIGN CENTERS**

#### **WEST**

401 Ellis Street

P.O. Box 7241

Mountain View, CA 94039

TEL 415 965-6142 FAX 415 965-6130

10220 S.W. Greenburg Rd. Suite 125 Portland, OR 97223

TEL 503 245-1600 FAX 503 245-3716

200 E. Sandpointe, Bldg. 8, Suite 450 Santa Ana, CA 92707

TEL 714 546-0501 FAX 714 432-8793

### SOUTH CENTRAL/SOUTHEAST

16475 Dallas Parkway, Suite 380 Dallas, TX 75248

TEL 214 250-4522 FAX 214 931-8680

Research Triangle Park 2525 Meridian Parkway, Suite 320 Durham, NC 27713

TEL 919 544-4132 FAX 919 544-4109

## NORTH CENTRAL/NORTHEAST

1500 W. Shure Drive, Suite 240 Arlington Heights, IL 60004

TEL 312 398-3600 FAX 312 577-9219

One Natick Executive Park Natick, MA 01760

TEL 508 655-8833 FAX 508 872-8692

CORPORATE HEADQUARTERS

401 Ellis Street P.O. Box 7241 Mountain View, CA 94039 TEL 415-960-6000 TLX 3715792

©1990 NEC Electronics Inc./Printed in U.S.A.

For literature, call toll-free 8 a.m. to 4 p.m. Pacific time: 1-800-632-3531

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document. ID-76838 (290)

Document No. 70000-1

8

018394 🗹 \_ \_