## SANYO Semiconductors DATA SHEET

# LC07410LG – Monaural CODEC + Audio I/F + Video Driver

#### Overview

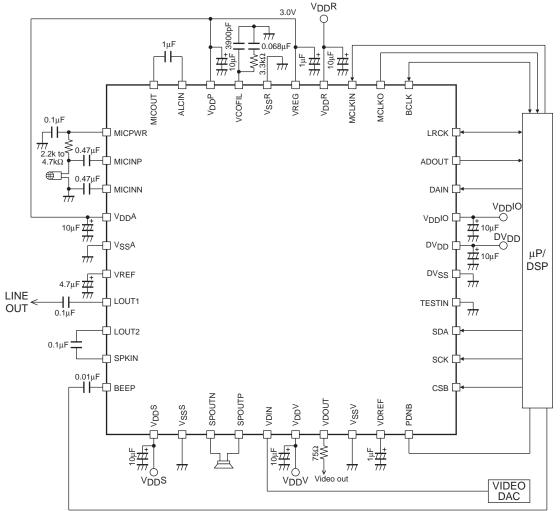

The LC07410LG is an IC that integrates a video driver with audio CODEC developed for digital still cameras and other portable equipment. Incorporating 16-bit A/D and D/A converters as well as a microphone amplifier and speaker driver that are necessary for audio recording and playback, the one-chip IC is ideal for use to create audio interfaces.

## Functions

#### Audio Block

- $\Delta\Sigma$  method 16-bit monaural A/D and D/A converters

- Generates bias voltage (2.3V) for microphone

- Supports microphone amplifier differential inputs (0/+20/+26dB)

- Amplifier with automatic level control (ALC) (-14dB to +34dB) for recording system

- Wind cut HPF

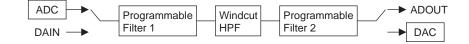

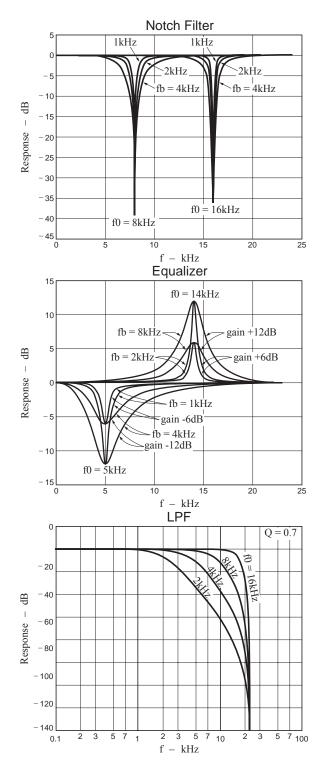

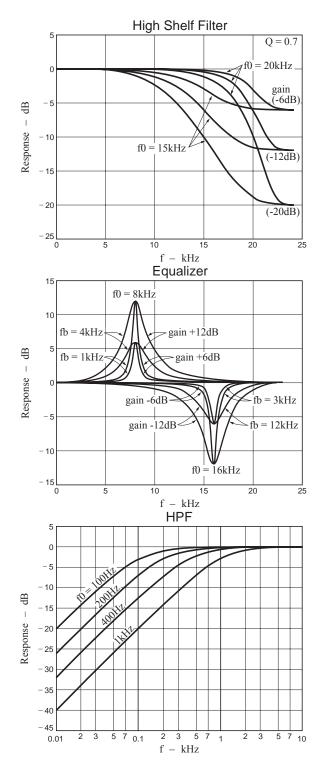

- Two programmable digital filter HSF/Notch filter/LPF/EQ

- Digital volume with automatic level control (ALC) for playback system Supports zerocross detection and soft switching

- Line output

- On-chip MUTE and POP-noise suppression circuits • Speaker driver

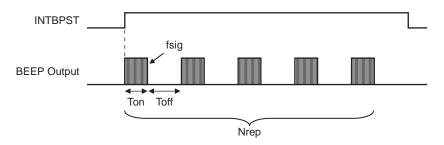

Supports  $V_{DDS} = 5V$  (piezoelectric speaker supported) BTL drive, rated output of 350mW at  $8\Omega$ ,  $V_{DDS} = 3V$ 1W at  $8\Omega$ ,  $V_{DDS} = 5V$ Idling current adjustable Supports BEEP input, volume level switchable

- Audio interfaces I<sup>2</sup>S, Left-justified mode, Right-justified mode

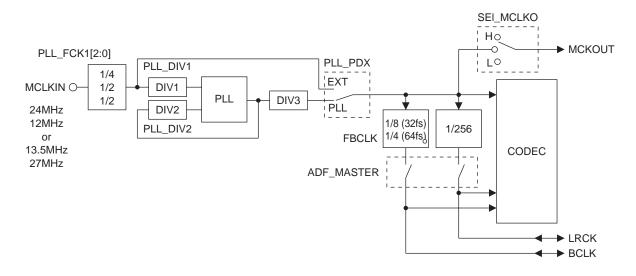

PLL

- Input: 12MHz, 13.5MHz, 24MHz, 27MHz Sampling frequency: 7.86kHz to 48kHz PLL master mode/slave (EXT) mode

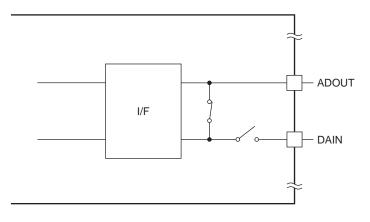

- Loopback: ADOUT to DAIN switch incorporated

#### Video Block

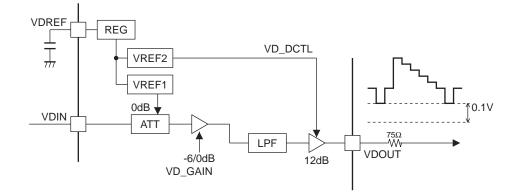

- DC direct coupling input/output

- Built-in 6th order low-pass filter (fc = 7.5MHz)

- Amplifier gain selectable (6dB or 12dB)

- Drive capacity 75 $\Omega$ , 1 system

Continued on next page.

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

SANYO Semiconductor Co., Ltd. http://semicon.sanyo.com/en/network Continued from preceding page.

#### REG Block

- 3.0V output linear regulator for Audio Block

- Overcurrent protective function (typ: 200mA)

- Quick discharge activity

- 3-line serial register control

- Digital I/O 1.8V supported

• Supply voltage

V<sub>DD</sub>IO = 1.8V/3.3V (1.71 to 3.6V) V<sub>DD</sub>A = V<sub>DD</sub>P =3 .0V (2.7 to 3.6V) V<sub>DD</sub>R = 3.3V (3.2 to 3.6V)

- $V_{DD}V = DV_{DD} = 3.3V (2.7 \text{ to } 3.6V)$

- $V_{DDS} = 3.3/5V (2.7 \text{ to } 5.5V)$

- Operating ambient temperature: -20 to +80°C

## Function comparison table of LC07410 and LC074146

| Function                | LC07410                              | LC074146                        |

|-------------------------|--------------------------------------|---------------------------------|

| Logic I/O 1.8V accepted | 0                                    | ×                               |

| 3V Regulator            | 0                                    | ×                               |

| BEEP sound generator    | 0                                    | ×                               |

| PLL frequencies         | flexible                             | Pre-fix                         |

| EXT-BEEP GAIN           | 0dB, -15/-18/-21dB                   | -12/-15/-18/-21dB               |

| ALC attack speed        | 2step variable                       | monotonic                       |

| ALC recovery speed      | 3step variable                       | monotonic                       |

| ALC noise gate function | 0                                    | ×                               |

| Digital filters         | Wind cut HPF +2 programmable filters | Wind cut HPF + EQ (HSF) + Notch |

## **Specifications**

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                             | Symbol                  | Conditions                                                                | Ratings     | unit |

|---------------------------------------|-------------------------|---------------------------------------------------------------------------|-------------|------|

| Maximum supply voltage<br>(5V system) | V <sub>DD</sub> 5 max   | V <sub>DD</sub> S                                                         | -0.3 to 7.0 | V    |

| Maximum supply voltage<br>(3V system) | V <sub>DD</sub> 3 max   | Other than V <sub>DD</sub> S                                              | -0.3 to 4.0 | V    |

| Input voltage                         | V <sub>IN</sub> max     |                                                                           | -0.3 to 4.0 | V    |

| Output voltage                        | V <sub>OUT</sub> max    |                                                                           | -0.3 to 4.0 | V    |

| Input/output voltage                  | V <sub>IO</sub> max     |                                                                           | -0.3 to 4.0 | V    |

| Allowable operating voltage           | V <sub>DD</sub> SRANGE  | V <sub>DD</sub> S                                                         | 2.7 to 5.5  | V    |

| range                                 | V <sub>DD</sub> RRANGE  | V <sub>DD</sub> R                                                         | 3.2 to 3.6  | V    |

|                                       | V <sub>DD</sub> ARANGE  | V <sub>DD</sub> A, V <sub>DD</sub> P, V <sub>DD</sub> V, DV <sub>DD</sub> | 2.7 to 3.6  | V    |

|                                       | V <sub>DD</sub> IORANGE | V <sub>DD</sub> IO                                                        | 1.71 to 3.6 | V    |

| Allowable power dissipation           | Pd max                  | Ta = 80°C *                                                               | 500         | mW   |

| Operating ambient temperature         | Topr                    |                                                                           | -20 to +80  | °C   |

| Storage ambient temperature           | Tstg                    |                                                                           | -55 to +125 | °C   |

\* Mounted on a specified board: 40mm×50mm×0.8mm, glass epoxy board 2S2P (4-layer board)

| Parameter                 | Symbol              | Conditions                               | Ratings                |         |                        |      |

|---------------------------|---------------------|------------------------------------------|------------------------|---------|------------------------|------|

| Falameter                 | Symbol              | Conditions                               | min                    | typ     | max                    | unit |

| Supply voltage            | V <sub>DD</sub> IO  | V <sub>DD</sub> IO pin                   | 1.71                   | 3.3     | 3.6                    | V    |

|                           | DVDD                | DV <sub>DD</sub> pin                     | 2.7                    | 3.3     | 3.6                    | V    |

|                           | V <sub>DD</sub> ana | V <sub>DD</sub> P, V <sub>DD</sub> A pin | 2.7                    | 3.0     | 3.6                    | V    |

|                           | V <sub>DD</sub> V   | V <sub>DD</sub> V pin                    | 2.7                    | 3.3     | 3.6                    | V    |

|                           | V <sub>DD</sub> R   | V <sub>DD</sub> R                        | 3.2                    | 3.3     | 3.6                    | V    |

|                           | V <sub>DD</sub> S   | V <sub>DD</sub> S pin                    | 2.7                    | 3.3/5.0 | 5.5                    | V    |

| Supply voltage gap        | V <sub>DD</sub> DV  | DV <sub>DD</sub> -V <sub>DD</sub> V      |                        |         | 0.3                    | V    |

|                           | V <sub>DD</sub> DR  | DV <sub>DD</sub> -V <sub>DD</sub> R      |                        |         | 0.3                    | V    |

|                           | V <sub>DD</sub> ID  | V <sub>DD</sub> IO-DV <sub>DD</sub>      |                        |         | 0.3                    | V    |

|                           | V <sub>DD</sub> PR  | V <sub>DD</sub> P-V <sub>DD</sub> R      |                        |         | 0.3                    | V    |

|                           | V <sub>DD</sub> PA  | V <sub>DD</sub> P-V <sub>DD</sub> A      |                        |         | 0.3                    | V    |

|                           | V <sub>DD</sub> AS  | V <sub>DD</sub> A-V <sub>DD</sub> S      |                        |         | 0.3                    | V    |

|                           | V <sub>DD</sub> VS  | V <sub>DD</sub> V-V <sub>DD</sub> S      |                        |         | 0.3                    | V    |

| Inpupt high level voltage | VIH                 | (*1)                                     | 0.8×V <sub>DD</sub> IO |         | V <sub>DD</sub> IO     | V    |

| Input low level voltage   | VIL                 | (*1)                                     | DV <sub>SS</sub>       |         | 0.2×V <sub>DD</sub> IO | V    |

| Input clock frequency     | fMCLK               | MCLKIN pin                               | 2.012                  |         | 27                     | MHz  |

| Input clock duty          | DutyMCLK            | MCLKIN pin                               | 0.45                   | 0.50    | 0.55                   | %    |

(\*1) Applicable pins: PDNB, CSB, SCK, SDA, TESTIN, DAIN, MCLKIN, BCLK, LRLK (in input mode)

## $\begin{array}{l} \textbf{Electrical Characteristics} \text{ at } Ta = 25 \pm 2^{\circ}\text{C}, \text{ } \text{V}_{DD}\text{IO} = 1.71 \text{ to } 3.6\text{V}, \text{ } \text{V}_{DD}\text{A} = \text{V}_{DD}\text{P} = \text{V}_{DD}\text{V} = \text{D}\text{V}_{DD} = 2.7 \text{ to } 3.6\text{V}, \\ \text{V}_{DD}\text{R} = 3.2 \text{ to } 3.6\text{V}, \text{ } \text{V}_{SS}\text{S} = 2.7 \text{ to } 5.5\text{V}, \text{ } \text{V}_{SS}\text{V} = \text{D}\text{V}_{SS}\text{R} = \text{V}_{SS}\text{A} = 0\text{V} \\ \end{array}$

| Parameter                 | Sumbol            |                             |                        |     |                        |      |  |

|---------------------------|-------------------|-----------------------------|------------------------|-----|------------------------|------|--|

| Parameter                 | Symbol            | Conditions                  | min                    | typ | max                    | unit |  |

| Input high level current  | IIН               | $V_{I} = V_{DD}IO(*1)$      |                        |     | +1                     | μA   |  |

| Inputp low level current  | ۱ <sub>IL</sub>   | $V_{I} = DV_{SS}$ (*1)      | -1                     |     |                        | μA   |  |

| Output high level voltage | V <sub>OH</sub> 1 | I <sub>OH</sub> = -1mA (*2) | 0.8×V <sub>DD</sub> IO |     |                        | V    |  |

| Output low level voltage  | V <sub>OL</sub> 1 | I <sub>OL</sub> = 1mA (*2)  |                        |     | 0.2×V <sub>DD</sub> IO | V    |  |

(\*1) Applicable pins: PDNB, CSB, SCK, SDA, TESTIN, DAIN, MCLKIN, BCLK, LRCK (in input mode)

(\*2) Applicable pins: ADOUT, BCLK, LRCK (in output mode)

#### Analog Characteristics at Ta = 25°C, V<sub>DD</sub>A = V<sub>DD</sub>P = 3.0V, V<sub>DD</sub>IO = DV<sub>DD</sub> = V<sub>DD</sub>S = V<sub>DD</sub>V = V<sub>DD</sub>R = 3.3V, fs=48kHz

| Developmenter                      | Cumbal              |                                                                                                                                                  |      |      |      |      |

|------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Parameter                          | Symbol              | Conditions                                                                                                                                       | min  | typ  | max  | unit |

| Current drain                      |                     |                                                                                                                                                  |      |      |      |      |

| REC time                           | I <sub>DD</sub> RA1 | REG/PLL/MIC/PGA/ADC on, no input signal                                                                                                          | 9.0  | 13.8 | 18.0 | mA   |

| PB (LINE) time                     | I <sub>DD</sub> PA2 | REG/PLL/DAC/LINE on, no input signal                                                                                                             | 8.0  | 12.2 | 16.0 | mA   |

| PB (SPK) time                      | I <sub>DD</sub> PA3 | REG/PLL/DAC/SPK on, no input signal                                                                                                              | 11.0 | 15.2 | 21.0 | mA   |

| Video block 1                      | I <sub>DD</sub> V1  | V <sub>DD</sub> V, no input signal                                                                                                               | 4.0  | 6.1  | 8.0  | mA   |

| Video block 2                      | I <sub>DD</sub> V2  | V <sub>DD</sub> V, Video in = white 50%                                                                                                          | 8.0  | 12.8 | 16.0 | mA   |

| Power down time current            | I <sub>DD</sub> PD  | V <sub>DD</sub> A+V <sub>DD</sub> P+V <sub>DD</sub> R+V <sub>DD</sub> S+V <sub>DD</sub> V+DV <sub>DD</sub> +V <sub>DD</sub> IO,<br>clock stopped |      | 1.0  | 10   | μA   |

| MIC                                |                     |                                                                                                                                                  |      |      |      |      |

| MIC amplifier gain                 | V <sub>G</sub> mic  | V <sub>IN</sub> = -30dBV, 1kHz, MGAIN[1:0] = 01                                                                                                  | -1   | 0    | 1    | dB   |

|                                    |                     | V <sub>IN</sub> = -30dBV, 1kHz, MGAIN[1:0] = 10                                                                                                  | 19   | 20   | 21   | dB   |

|                                    |                     | V <sub>IN</sub> = -30dBV, 1kHz, MGAIN[1:0] = 11                                                                                                  | 25   | 26   | 27   |      |

| MIC amplifier output<br>THD+N      | THDNmic             | V <sub>IN</sub> = -30dBV, 1kHz, MGAIN[1:0] = 11                                                                                                  |      | -80  | -70  | dB   |

| MIC amplifier output noise voltage | V <sub>NO</sub> mic | MIC IN no signal, A-weighted, MGAIN[1:0] = 11 -88                                                                                                |      | -82  | dBV  |      |

| MIC bias output voltage            | Vmicpwr             | $R_L = 5k\Omega$                                                                                                                                 | 2.2  | 2.3  | 2.4  | V    |

Continued on next page.

## LC07410LG

| Deremeter                   | Cumphed              | Conditions                                 | Ratings |                       |     | unit |

|-----------------------------|----------------------|--------------------------------------------|---------|-----------------------|-----|------|

| Parameter Symbol            |                      | Conditions                                 | min     | typ                   | max | unit |

| ALC                         |                      |                                            |         |                       |     |      |

| Gain change                 | DGalc                |                                            |         | 1                     |     | dB   |

| Gain control range          | VGalc                |                                            | -14     |                       | +34 | dB   |

| ADC: ALCIN input, ALCOFI    | F, PGA Gain = 0      | dB                                         |         |                       |     |      |

| Analog input voltage        | Vinad                | 0dBFS, 1kHz                                |         | 0.6×V <sub>DD</sub> A |     | Vp-p |

| THD+N                       | THDNad               | -1dBFS, 1kHz                               |         | -80                   | -74 | dB   |

| Dynamic range               | DRad                 | -60dBFS, A-weighted                        | 80      | 86                    |     | dB   |

| S/N ratio                   | SNad                 | ALCIN no signal, A-weighted                | 80      | 86                    |     | dB   |

| DAC                         |                      |                                            |         |                       |     |      |

| Digital volume change       | DGvol1               | +12dB to -10dB                             |         | 0.5                   |     | dB   |

|                             | DGvol2               | -11dB to -42dB                             |         | 1                     |     | dB   |

|                             | DGvol3               | -44dB to -64dB                             |         | 2                     |     | dB   |

| LINE: DAC→LINE Gain = 0     | dB, DVOL = 0dl       | 3                                          |         |                       |     |      |

| Analog output voltage       | Voutda               | 0dBFS, 1kHz                                |         | 0.6×V <sub>DD</sub> A |     | Vp-p |

| THD+N                       | THDNda               | 0dBFS, 1kHz                                |         | -83                   | -74 | dB   |

| Dynamic range               | DRda                 | -60dBFS, A-weighted                        | 80      | 88                    |     | dB   |

| S/N ratio                   | SNda                 | A-weighted                                 | 80      | 88                    |     | dB   |

| SPK                         |                      |                                            | •       |                       | •   |      |

| SPK amplifier gain          | VGsp                 | SPKIN = -9dBV, 1kHz , BTL, $R_L = 8\Omega$ | 11      | 12                    | 13  | dB   |

| SPK output distortion       | HDsp                 | SPKIN = -9dBV, 1kHz                        |         | 0.2                   | 1   | %    |

| SPK output noise voltage    | VNOsp                | SPKIN no signal, $R_L = 8\Omega$           |         | -86                   | -80 | dBV  |

| SPK maximum rated<br>output | VOMsp                | R <sub>L</sub> = 8Ω, THD = 3%              | 300     | 350                   |     | mW   |

| BEEP gain                   | VGbp                 | BTL, $R_L = 8\Omega$ BPVOL[1:0] = 00       | -2      | 0                     | 2   | dB   |

|                             |                      | BTL, R <sub>L</sub> = 8Ω BPVOL[1:0] = 01   | -16     | -15                   | -14 | dB   |

|                             |                      | BTL, R <sub>L</sub> = 8Ω BPVOL[1:0] = 10   | -19     | -18                   | -17 | dB   |

|                             |                      | BTL, R <sub>L</sub> = 8Ω BPVOL[1:0] = 11   | -22     | -21                   | -20 | dB   |

| Regulator                   |                      |                                            |         |                       |     |      |

| Regulator output voltage    | VOreg                | I <sub>OUT</sub> = 20mA                    | 2.9     | 3.0                   | 3.1 | V    |

| Video driver                |                      |                                            | •       |                       | •   |      |

| Video amplifier gain        | V <sub>G</sub> video | VGAIN[1:0] = 00, VDIN = 1Vp-p 100% white   | 5       | 6                     | 7   | dB   |

|                             |                      | VGAIN[1:0] = 10, VDIN = 0.5Vp-p 100% white | 11      | 12                    | 13  | dB   |

| Frequency characteristics   | Fva                  | f = 8MHz/100kHz                            |         | -4.5                  | 0   | dB   |

|                             |                      | f = 20MHz/100kHz                           |         | -40                   | -35 | dB   |

| Input impedance             | Rvin                 |                                            | 100     | 120                   |     | kΩ   |

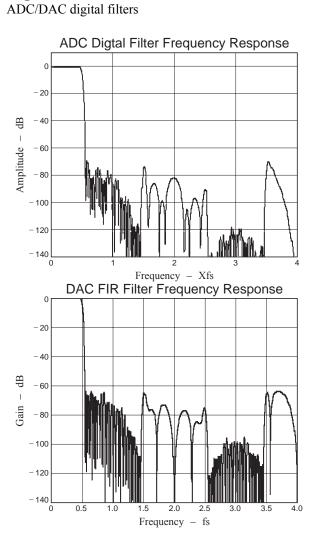

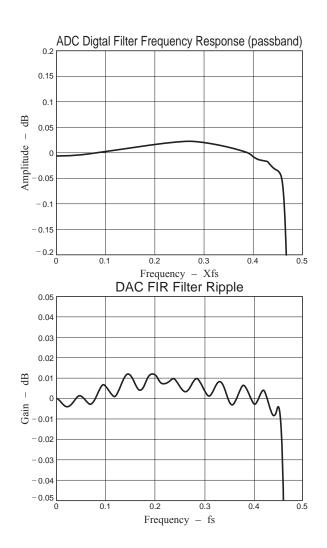

## **ADC Filter Characteristics**

| Parameter            | Conditions |          | Ratings     |          | unit | Remarks            |

|----------------------|------------|----------|-------------|----------|------|--------------------|

| Parameter            | Conditions | min      | typ         | max      | unit | Remarks            |

| Resolution           |            |          | 16          |          | Bit  |                    |

| Passband             | ±0.045dB   | 0        |             | 0.4535fs |      | 21.8kHz@fs = 48kHz |

| Stopband             |            | 0.5465fs |             |          |      | 26.2kHz@fs = 48kHz |

| Passband ripple      | 0 to 20kHz |          |             | ±0.045   | dB   |                    |

| Stopband attenuation |            | -69      |             |          | dB   |                    |

| Output data delay    |            |          | 58          |          | 1/fs |                    |

| HPF cutoff frequency | -3dB       |          | 0.0000385fs |          | Hz   | 1.85Hz@fs = 48kHz  |

#### **DAC Filter Characteristics**

| Parameter            | Conditions |          | Ratings     |          | unit | Remarks            |

|----------------------|------------|----------|-------------|----------|------|--------------------|

| Farameter            | Conditions | min      | typ         | max      | unit | Remarks            |

| Resolution           |            |          | 16          |          | Bit  |                    |

| Passband             | ±0.015dB   | 0        |             | 0.4535fs |      | 21.8kHz@fs = 48kHz |

| Stopband             |            | 0.5465fs |             |          |      | 26.2kHz@fs = 48kHz |

| Passband ripple      |            |          |             | ±0.015   | dB   |                    |

| Stopband attenuation |            | -63      |             |          | dB   |                    |

| Output data delay    |            |          | 48          |          | 1/fs |                    |

| HPF cutoff frequency | -3dB       |          | 0.0000385fs |          | Hz   | 1.85Hz@fs = 48kHz  |

#### **Switching Characteristics**

| Demonster                        | Complexel |                                            |       | Ratings |        |      |  |

|----------------------------------|-----------|--------------------------------------------|-------|---------|--------|------|--|

| Parameter                        | Symbol    | Conditions                                 | min   | typ     | max    | unit |  |

| PLL                              |           |                                            |       |         |        |      |  |

| CKIN frequency                   | fCKI      | PLL used                                   | 12    |         | 27     | MHz  |  |

|                                  |           | EXT input present                          | 2.012 |         | 24.576 | MHz  |  |

| BCLK frequency                   | fBCK      | FBCLK = 0                                  |       | 64fs    |        |      |  |

|                                  |           | FBCLK = 1                                  |       | 32fs    |        |      |  |

| BCLK duty cycle                  | dtBK      |                                            | 45    | 50      | 55     | %    |  |

| LRCK frequency                   | fLR       |                                            | 7.86  |         | 48     | kHz  |  |

| LRCK duty cycle                  | dtLR      |                                            | 45    | 50      | 55     | %    |  |

| CLK transition time $\uparrow$   | trCK      | Rise time, MCLKIN/BCLK/LRCK inputs present |       |         | 10     | ns   |  |

| CLK transition time $\downarrow$ | tfCK      | Fall time, MCLKIN/BCLK/LRCK inputs present |       |         | 10     | ns   |  |

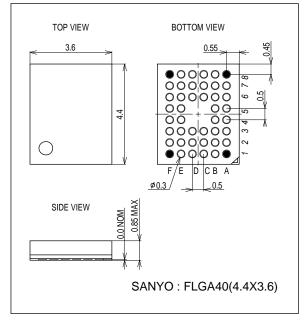

## Package Dimensions

unit : mm (typ)

3370

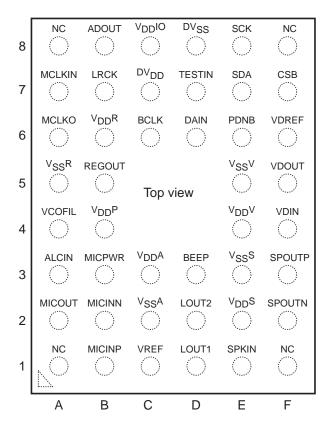

## **Pin Assignment**

#### 3.0V 3.3V $\frac{1}{2}$ + $\frac{1}{m}$ VDDP[ VREG ALCIN, VDDR MICOUT VCOFIL VSSR LDO MICPWR MIC PLL Power MCLKIN MICINP MCLKO MIC 14 to +34dB Digital Ð AMP ADC BCLK MICINN \_\_\_\_\_H filter LRCK 0/+20/+26dB ADOUT <sup>₩</sup> VDDA 0-DAIN 1.8V or 3.3V -0-I/F JV<sub>SS</sub>A ॑ ALC CTL μΡ/ DSP VREF ₩H. VREF VDDIO 0/4/6/8dB 3.3V ⊬┥┝<u>"</u> LINE OUT <sup>←</sup> LOUT MUTE DVDD DAC VOL DVSS 0/6dB \_\_\_\_\_ LOUT2 TESTIN[ BEEP GEN 7 SDA +6/+12dB SPKIN MODE SPK AMP SCK LPF CTL REF BEEP +CSB SPOUTN SPOUTP VDREF VDOUT VSSS PDNB /DDS /DG/ SSV VDIN -1.8V or Ş 3.3V Ч -1 3.3V $\downarrow$ + # Ŧ ₩ Y ↓ <del>///</del> Video out 777 VIDEO DAC 3.3V or Li+ batt.

## **Block Diagram**

## LC07410LG

| Pin Fu  | unction           | (   | Note) I/O: I => input, Is => Schmitt inpu       | t, O => output, IO s=> Schmitt input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|-------------------|-----|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin name          | I/O | Function                                        | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B3      | MICPWR            | 0   | Microphone power supply output (2.3V)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B1      | MICINP            | 1   | Microphone amplifier input (+ side)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B2      | MICINN            | 1   | Microphone amplifier input (- side)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C3      | V <sub>DD</sub> A | -   | Analog block power supply (3V)                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C1      | VREF              | 0   | 3V analog power supply reference voltage output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C2      | V <sub>SS</sub> A | -   | Analog block ground (0V)                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D1      | LOUT1             | 0   | Line output 1                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D2      | LOUT2             | 0   | Line output 2                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D3      | BEEP              | I   | BEEP signal input, mixed to speaker amplifier   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| E1      | SPKIN             | 1   | Speaker amplifier input                         | $ \begin{array}{c} \begin{array}{c} \begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array}\\ \end{array}\\ \end{array}\\ \end{array}\\ \end{array} \\ \begin{array}{c} \end{array}$ $\begin{array}{c} \end{array}\\ \begin{array}{c} \end{array}\\ \end{array}$ $\begin{array}{c} \end{array}\\ \begin{array}{c} \end{array}\\ \end{array}$ $\begin{array}{c} \end{array}$ $\end{array}$ $\begin{array}{c} \end{array}$ $\begin{array}{c} \end{array}$ $\end{array}$ $\begin{array}{c} \end{array}$ $\begin{array}{c} \end{array}$ $\end{array}$ $\begin{array}{c} \end{array}$ $\end{array}$ $Continued on next page.$ |

Continued on next page.

Continued from preceding page. I/O Pin No. Pin name Function Equivalent circuit Speaker analog power supply E2 V<sub>DD</sub>S \_ F2 SPOUTN 0 Speaker output (-) SPOUTP F3 0 Speaker output (+) E3 V<sub>SS</sub>S \_ Speaker analog ground E4 VDDV \_ Video driver analog power supply F4 VDIN I Video signal input 120kΩ ╢Ӗ VDOUT F5 0 Video signal output ١E F6 VDREF 0 Video VREF 500Ω≷ 500Ω 50kΩ ₹ +E5 VSSV \_ Video driver ground PDNB E6 ls Reset (negative polarity) CSB F7 Chip select (negative polarity) Microcontroller IF ls schmitt SCK E8 ls Serial clock Microcontroller IF E7 SDA ls Serial data input Microcontroller IF D8 DVSS \_ Digital ground (0V) C7 Digital power supply (3.3V) DVDD \_ C8 Digital I/O power supply (3.3V/1.8V) V<sub>DD</sub>IO \_ D7 TESTIN T Test input (V<sub>SS</sub> fixed in normal operation) DAIN D6 Т DAC serial data input B8 ADOUT 0 ADC serial data output

Continued on next page.

Continued from preceding page.

| Pin No. | Pin name          | I/O | Function                                                                           | Equivalent circuit                                                                     |

|---------|-------------------|-----|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| B7      | LRCK              | IOs | LR clock input                                                                     | schmitt<br>———————————————————————————————————                                         |

| C6      | BCLK              | IOs | Bit clock input                                                                    |                                                                                        |

| A6      | MCLKO             | 0   | Master clock output (Default: Set to Low, serial setting enables output/Addr: 16h) |                                                                                        |

| A7      | MCLKIN            | I   | Master clock input                                                                 |                                                                                        |

| B6      | V <sub>DD</sub> R | -   | Regulator power supply input (3.3V)                                                |                                                                                        |

| B5      | REGOUT            | 0   | Regulator output pin                                                               | 144kΩ<br>100kΩ<br>100kΩ<br>100kΩ<br>100kΩ<br>100kΩ<br>100kΩ<br>100kΩ<br>100kΩ<br>100kΩ |

| A5      | V <sub>SS</sub> R | -   | Regulator block ground                                                             |                                                                                        |

| A4      | VCOFIL            | 0   | VCO filter pin                                                                     |                                                                                        |

| B4      | V <sub>DD</sub> P | -   | PLL block supply (3.0V)                                                            |                                                                                        |

| A3      | ALCIN             | I   | ALC amplifier input                                                                |                                                                                        |

| A2      | MICOUT            | 0   | Microphone amplifier output                                                        |                                                                                        |

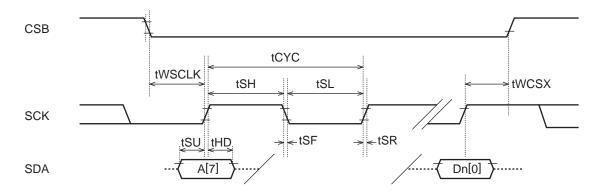

#### **Interface Timing Characteristics**

| D to                                    |        |     | Ratings   |     |      |  |  |  |

|-----------------------------------------|--------|-----|-----------|-----|------|--|--|--|

| Parameter                               | Symbol | min | typ       | max | unit |  |  |  |

| Microcontroller serial interface timing |        |     |           |     |      |  |  |  |

| SCLK cycle time                         | tCYC   | 4T  | 8T        |     | ns   |  |  |  |

| SCLK high period                        | tSH    | 2T  | 4T        |     | ns   |  |  |  |

| SCLK low period                         | tSL    | 2T  | 4T        |     | ns   |  |  |  |

| Data setup time                         | tSU    | 2T  | 4T        |     | ns   |  |  |  |

| Data hold time                          | tHD    | 2T  | 4T        |     | ns   |  |  |  |

| CSX rise to SCLK wait time              | tWSCLK | 0T  | 2T        |     | ns   |  |  |  |

| SCLK to CSX rise wait time              | tWCSX  | 4T  | 6T        |     | ns   |  |  |  |

| Rise time                               | tSR    |     |           | 50  | ns   |  |  |  |

| Fall time                               | tSF    |     |           | 50  | ns   |  |  |  |

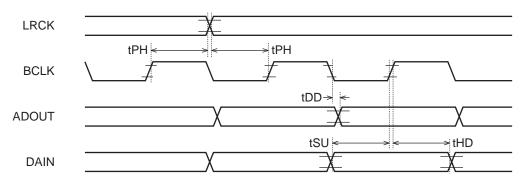

| Audio data timing                       |        |     |           |     |      |  |  |  |

| Clock phase (Note 2)                    | tPH    | 75  |           |     | ns   |  |  |  |

| Clock phase (Note 3)                    | tPH    |     | 1/(128fs) |     | ns   |  |  |  |

| Data delay time                         | tDD    | 0   |           | 75  | ns   |  |  |  |

| Data setup time                         | tSUA   | 1T  |           |     | ns   |  |  |  |

| Data hold time                          | tHDA   | 1T  |           |     | ns   |  |  |  |

Note 1: T = 1/fMCLK, fMCLK: Frequency of MCLKIN pin; example: when fMCLK = 10MHz, T = 100ns, 2T = 200ns

Note 2: LRCK and BCLK are inputs in Slave mode.

The MCLK timing needs only to be synchronized with LRCK and BCLK and its phase is irrelevant. Note 3: In master mode, LRCK and BCLK are output in master mode and fs is the sampling frequency. Note 4: The load of output pin: 30pF.

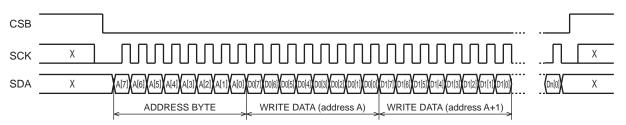

#### Microcontroller Serial Interface Timing Diagram

#### Audio Data Timing Diagram

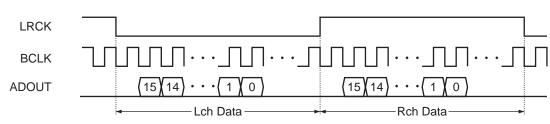

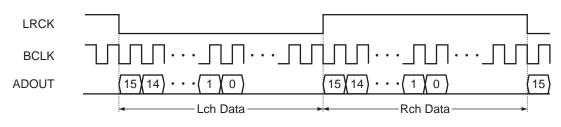

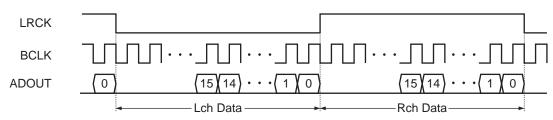

#### Audio Data Formats

#### • Left-justified mode

#### • Right-justified mode

#### PLL/BCLK/LRCK Master/Slave

| Pin No. | Pin Name | Slave Mode (PLL: OFF)     | Master Mode (PLL: ON)      |

|---------|----------|---------------------------|----------------------------|

| A7      | MCLKIN   | Input                     | Input                      |

| A6      | MCLKO    | Output (through)          | Output (PLL = 256fs)       |

|         |          |                           |                            |

| Die Me  | Din Nome | Slave Made (ADE MASTED 0) | Moster Mede (ADE MACTED 1) |

| Pin No. | Pin Name | Slave Mode (ADF_MASTER = 0) | Master Mode (ADF_MASTER = 1) |

|---------|----------|-----------------------------|------------------------------|

| B7      | LRCK     | Input                       | Output                       |

| C6      | BCLK     | Input                       | Output                       |

#### **Microcontroller Serial Interface**

The internal registers values are written by the serial interface consisting of the three CSB, SCK, and SDA lines. When the CSB pin is set low, the LC07410LG is switched into the mode that enables operation. The data is received on a byte basis with MSB first.

Continuous access (burst access) is also possible, and the addresses incremented by 1 are accessed in sequence with each byte following access to the register specified by the address byte. If the size of data exceeding the highest address (39h) is accessed in this process, the data concerned is treated as invalid. In other word, the address never wraps around to 00h.

| Transferring data to or | e address                                             |   |

|-------------------------|-------------------------------------------------------|---|

| -                       | A[7:0] : Designated address<br>D[7:0] : Register data |   |

|                         | X : Invalid                                           |   |

| CSB                     |                                                       |   |

| SCK X                   |                                                       | Х |

| SDA X                   |                                                       | Х |

|                         | ADDRESS BYTE WRITE DATA (address A)                   |   |

#### Transferring data to contiguous addresses

## **Specification Details**

#### Power down/system reset

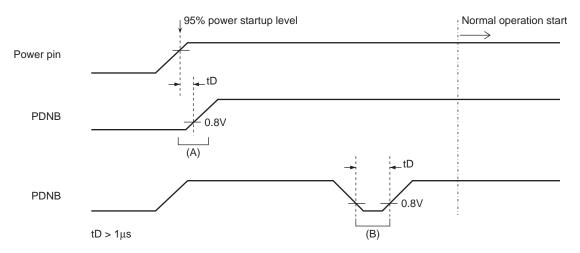

When the PDNB pin is set to 0, all the circuits are set to power down mode regardless of the power down settings for each block. A 0 on the PDNB pin also triggers a system reset.

After the power is first applied, the system must be reset without fail.

[See the section on "Checkpoint\_2) Resetting"]

After resetting, the contents of the serial port register are initialized.

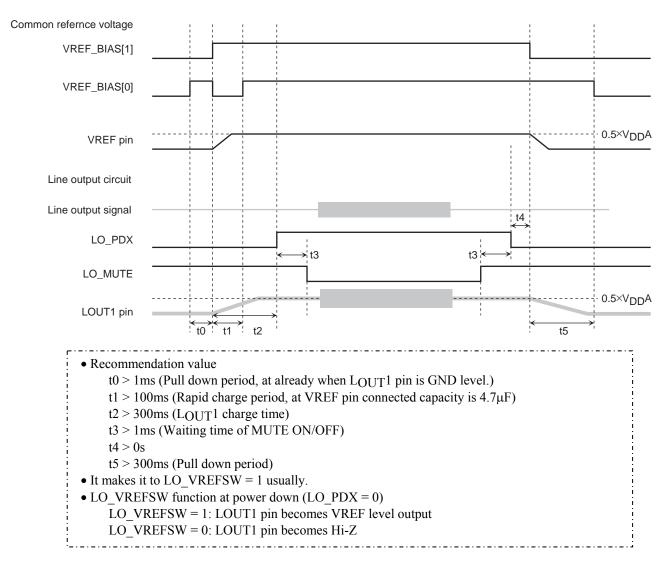

The VREF buffer is activated by releasing power down mode by setting the PDNB pin from 0 to 1, and then by setting VREF\_BIAS[1:0] to 01. When VREF\_BIAS [1:0] is set to 10, VREF starts. Along with the start of VREF, the LINE output pin is biased to  $1/2V_{DD}A$ . Once the VREF voltage has stabilized, VREF\_BIAS [1:0] must be set to 11 (normal state).

#### Reference voltage generator circuit

VREF\_BIAS: Voltage Reference Bias

\* Bold letters indicate initial settings.

| ADRS | Bit   | Name      | Init | Description                                                                                                                                  |

|------|-------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 01h  | [5:4] | VREF_BIAS | 00b  | Sets the reference voltage circuit (VREF pin).<br>11: Normal operation (standard resistor value)<br>10: Quick rise to reference voltage <*1> |

|      |       |           |      | 01: Activates IREF bias, VREF OFF 00: Power down                                                                                             |

<\*1> The target voltage is reached quickly by connecting a low-resistance element in the "reference voltage generation circuit." During normal operation, a standard resistance is recommended in order to save power.

#### **Power Control**

| ADRS | Bit | Name        | Init | Description                                          |

|------|-----|-------------|------|------------------------------------------------------|

| 00h  | [7] | MIC_PDX     | 0b   | MIC amplifier circuit, power control                 |

|      |     |             |      | 1: power on 0: power down                            |

|      | [6] | MIC_PWR_PDX | 0b   | MIC power circuit (MIC_PWR pin), power control       |

|      |     |             |      | 1: power on <u>0: power down</u>                     |

|      | [5] | PGA_PDX     | 0b   | PGA circuit, power control                           |

|      |     |             |      | 1: power on <u>0: power down</u>                     |

|      | [4] | ADC_PDX     | 0b   | ADC circuit, power control                           |

|      |     |             |      | 1: power on 0: power down                            |

|      | [3] | DAC_PDX     | 0b   | DAC circuit, power control                           |

|      |     |             |      | 1: power on 0: power down                            |

|      | [2] | SEL_PDX     | 0b   | Selector (L <sub>OUT</sub> 2) circuit, power control |

|      |     |             |      | 1: power on 0: power down                            |

|      | [1] | LO_PDX      | 0b   | Line out circuit (LOUT1) circuit, power control      |

|      |     |             |      | 1: power on 0: power down                            |

|      | [0] | SP_PDX      | 0b   | Speaker amplifier circuit, power control             |

|      |     |             |      | 1: power on 0: power down                            |

| 01h  | [2] | PLL_PDX     | 0b   | PLL circuit, power control                           |

|      |     |             |      | 1: power on <u>0: power down</u> (PLL-EXT mode)      |

|      | [1] | REG_PDX     | 0b   | Regulator circuit, power control                     |

|      |     |             |      | 1: power on 0: power down                            |

|      | [0] | VD_PDX      | 0b   | Video driver circuit, power control                  |

|      |     |             |      | 1: power on 0: power down                            |

#### **Sampling Frequency Setting**

Set sampling frequency used by FS [4:0] register. This is necessary to make it for correctly setting digital frequency characteristic and ALC damping time constant. The setting is adjusted to a value that is the closest to fs used.

| ADRS | Bit   | Name | Init  | Description                                            |

|------|-------|------|-------|--------------------------------------------------------|

| 15h  | [3:0] | FS   | 1000b | Sampling Frequency Setting                             |

|      |       |      |       | 1000: 48kHz/0111: 44.1kHz/0110: 32kHz/0101: 24kHz      |

|      |       |      |       | 0100: 22.05kHz/0011: 16kHz/0010: 12kHz/0001: 11.025kHz |

|      |       |      |       | 0000: 8kHz                                             |

Note: This setting doesn't synchronize with PLL setting. It is necessary to set it individually respectively. Refer to the page of PLL function explanation for PLL setting.

#### 3V Regulator

Built-in 3V Regulator for V<sub>DD</sub>A,V<sub>DD</sub>P. The regulator starts by setting as REG\_PDX = 1. Output current is 100mA (typ). It provides with max 200mA (typ) output current limiter for over-current protective function.

#### • Microphone (MIC) amplifier

The microphone amplifier has a differential input and a gain of +26dB (typ).

Its gain can also be set to +20dB or 0dB by register MGAIN [1:0]. Its input resistance is 70k $\Omega$  (typ). The MICPWR is a power output pin for the microphone, and its output voltage is 2.3V (typ 0.767×VDDA).

The maximum output current is 20mA.

The microphone amplifier is placed in the power down mode by setting MIC\_PDX to 0.

When MIC\_PWR\_PDX is set to 0, the microphone power supply circuit is placed in the power down mode.

| ADRS | Bit   | Name     | Init | Description                                                                     |

|------|-------|----------|------|---------------------------------------------------------------------------------|

| 02h  | [5:4] | MIC_GAIN | 01b  | MIC amplifier circuit, gain setting<br>11: 26dB 10: 20dB <b>01: 0dB</b> 00: 0dB |

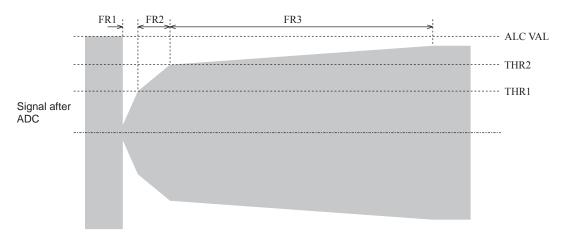

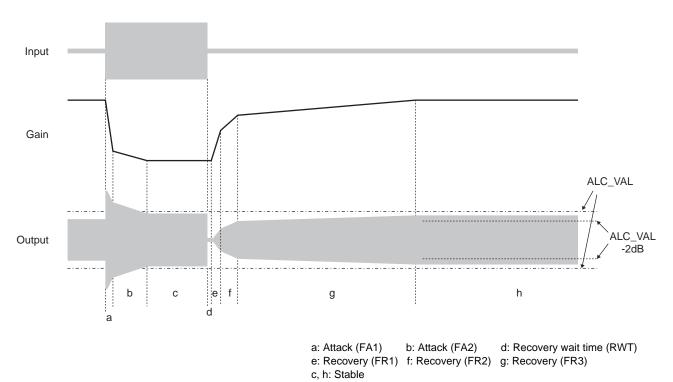

#### • Recording system automatic level control (ALC)

The amplifier gain of the PGA (Programmable Gain Amplifier) must be automatically adjusted so that the A/D converter output audio level is setup to the predetermined value. The gain can be varied within a range (maximum) of -14dB to +34dB.

When using ALC in the recording system, set REC\_ALC to 1 and PB\_ALC to 0 (recording system ALC mode). When REC\_ALC is set to 0 and PB\_ALC is set to 0 (ALC off mode), the PGA is placed in the manual mode, and the amplifier gain is fixed to the value of the ALC\_GAIN register setting.

When PGA\_PDX is set to 0, the PGA is placed in the power down mode. During normal use, the state of PGA\_PDX must be switched at the same time as ADC\_PDX.

For further details on operation, refer to "Description of ALC/limiter (Automatic Level Control) operation." Any of eight recording ALC levels (in 1dB steps from -3dBFS to -10dBFS) can be set using the ALC\_VAL register.

| ADRS | Bit   | Name       | Init | Description                                                                                                                                               |  |

|------|-------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 03h  | [6:4] | ALC_VAL    | 001b | Set the ALC limiter level                                                                                                                                 |  |

|      |       |            |      | 000: -3dBFS 001: -4dBFS 010: -5dBFS 011: -6dBFS                                                                                                           |  |

|      |       |            |      | 100: -7dBFS 101: -8dBFS 110: -9dBFS 111: -10dBFS                                                                                                          |  |

|      | [2:0] | ALC_FA1    | 010b | Attack coefficient 1 setting                                                                                                                              |  |

| 04h  | [6:4] | ALC_THA    | 010b | Set the attack speed switch over thresh                                                                                                                   |  |

|      | [2:0] | ALC_FA2    | 100b | Attack coefficient 2 setting                                                                                                                              |  |

| 05h  | [6:4] | ALC_THR1   | 011b | Set the recovery speed switch over thresh1                                                                                                                |  |

|      | [2:0] | ALC_FR1    | 100b | Recovery coefficient 1 setting                                                                                                                            |  |

| 06h  | [6:4] | ALC_THR2   | 011b | Set the recovery speed switch over thresh2                                                                                                                |  |

|      | [2:0] | ALC_FR2    | 100b | Recovery coefficient 2 setting                                                                                                                            |  |

| 07h  | [2:0] | ALC_FR3    | 100b | Recovery coefficient 3 setting                                                                                                                            |  |

| 08h  | [7]   | ALC_FULLEN | 0b   | <ul><li>Sets the full scale detection mode</li><li>1: Performs attack operation regardless of the ALCZCD setting when a full scale is detected.</li></ul> |  |

|      |       |            |      |                                                                                                                                                           |  |

|      |       |            |      | 0: Normal operation                                                                                                                                       |  |

|      | [6]   | ALC_ZCD    | 1b   | Controls the gain change operation at zerocross timing.                                                                                                   |  |

|      |       |            |      | <u>1: Changes the gain at zerocross timing.</u>                                                                                                           |  |

|      |       |            |      | 0: Changes the gain without waiting for a zerocross timing.                                                                                               |  |

|      | [5:4] | ALC_ZCDTM  | 01b  | Set the zerocross detection timeout time. Valid when [ALC_ZCD] = 1.                                                                                       |  |

|      |       |            |      | 11: 8192/fs 10: 4096/fs 01: 2048/fs 00: 1024/fs                                                                                                           |  |

|      |       |            |      | * It becomes the above-mentioned 1/4 times at fs 8k to12kHz,                                                                                              |  |

|      |       |            |      | It becomes the above-mentioned 1/2 times at fs 16k to 24kHz.                                                                                              |  |

|      | [3:2] | ALC_TLIM   | 01b  | Set the inter-zerocross attack limit.                                                                                                                     |  |

|      |       |            |      | 11: 4dB 10: 2dB <u>01: 1dB</u> 00: 0.5dB                                                                                                                  |  |

|      |       |            |      | Valid when [ALC_ZCD] = 1                                                                                                                                  |  |

|      | [1:0] | ALC_RWT    | 10b  | Set the recovery alert time                                                                                                                               |  |

|      |       |            |      | 11: 1024/fs 10: 512/fs 01: 256/fs 00: 128/fs                                                                                                              |  |

|      |       |            |      | * It becomes the above-mentioned 1/4 times at fs 8k to 12kHz,                                                                                             |  |

|      |       |            |      | It becomes the above-mentioned 1/2 times at fs 16k to 24kHz.                                                                                              |  |

Continued on next page.

## LC07410LG

#### Continued from preceding page.

| ADRS | Bit   | Name              | Init | Description                                                                                                                                         |  |

|------|-------|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

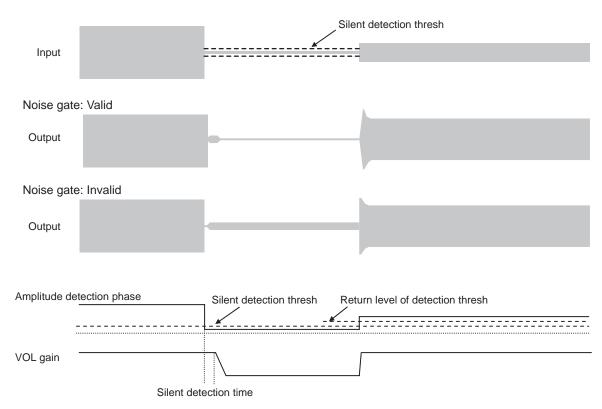

| 09h  | [7]   | ALC_NGEN          | 0b   | Set the noise gate function 1: Valid <b>0: Invalid</b>                                                                                              |  |

|      | [6:4] | ALC_NGTH          | 100b | Set the noise gate silent detection thresh level                                                                                                    |  |

|      | [3:2] | ALC_NGDT          | 10b  | Set the noise gate silent detection time/See the gain attenuation time                                                                              |  |

|      | [1:0] | ALC_NGRT          | 01b  | Set the noise gate reset time                                                                                                                       |  |

| 0Bh  | [5:0] | ALC_VMAX          | 0Eh  | Set the maximum PGA gain value (Init value = 0Eh: 0dB)<br>Refer to "ALC Circuit Gain Setting Table."                                                |  |

| 0Ch  | [5:0] | ALC_GAIN          | 0Eh  | Set the manual mode PGA gain value (Init value = 0Eh: 0dB)<br>Refer to "ALC Circuit Gain Setting Table."                                            |  |

| 0Dh  | [1:0] | REC_ALC<br>PB_ALC | 10b  | ALC mode setting<br><u>10: REC ALC, PB manual gain setting</u><br>01: PB ALC, REC manual gain setting<br>00/11: ALC OFF, REC/PB manual gain setting |  |

See the section on "Description of ALC Operation."

#### • Attack coefficient 1

| FA1[2:0]   | 1dB<br>Attenuation time* | fs = 48kHz<br>24kHz<br>12kHz |

|------------|--------------------------|------------------------------|

| 000        | 1/fs                     | 20.83µs                      |

| 001        | 2/fs                     | 41.67µs                      |

| <u>010</u> | <u>4/fs</u>              | <u>83.33µs</u>               |

| 011        | 8/fs                     | 166.7μs                      |

| 100        | 16/fs                    | 333.3µs                      |

| 101        | 32/fs                    | 666.6µs                      |

| 110        | 64/fs                    | 1.333ms                      |

| 111        | 128/fs                   | 2.666ms                      |

#### • Attack coefficient 2

| FA2[2:0]   | 1dB<br>Attenuation time* | fs = 48kHz<br>24kHz<br>12kHz |

|------------|--------------------------|------------------------------|

| 000        | 1/fs                     | 20.83µs                      |

| 001        | 2/fs                     | 41.67µs                      |

| 010        | 4/fs                     | 83.33µs                      |

| 011        | 8/fs                     | 166.7µs                      |

| <u>100</u> | <u>2º/fs</u>             | <u>10.66ms</u>               |

| 101        | 2 <sup>10</sup> /fs      | 21.33ms                      |

| 110        | 2 <sup>11</sup> /fs      | 42.67ms                      |

| 111        | 2 <sup>12</sup> /fs      | 85.33ms                      |

\* At fs = 32k to 48kHz, setting. 1/4 times at 8k to 12kHz, 1/2 times at 16k to 24kHz, (48kHz, 24kHz, 12kHz become the same speed).

#### • Attack speed switch over thresh level

| THA[2:0]   | Level to ALC_VAL |

|------------|------------------|

| 000        | +1dB             |

| 001        | +2dB             |

| <u>010</u> | <u>+3dB</u>      |

| 011        | +4dB             |

| 100        | +5dB             |

| 101        | +6dB             |

| 110        | +7dB             |

| 111        | +8dB             |

• Recovery coefficient 1

Recovery coefficient 2

| • Recovery c | coefficient 3 |

|--------------|---------------|

|--------------|---------------|

| FR1[2:0]   | FS/s*        |

|------------|--------------|

| 000        | 13.2         |

| 001        | 6.6          |

| 010        | 3.3          |

| 011        | 1.65         |

| <u>100</u> | <u>0.828</u> |

| 101        | 0.424        |

| 110        | 0.212        |

| 111        | 0.106        |

| FR2[2:0]   | FS/s*        |

|------------|--------------|

| 000        | 3.3          |

| 001        | 1.65         |

| 010        | 0.828        |

| 011        | 0.424        |

| <u>100</u> | <u>0.212</u> |

| 101        | 0.106        |

| 110        | 0.053        |

| 111        | 0.026        |

|            |              |

| FR3[2:0]   | FS/s*        |

|------------|--------------|

| 000        | 0.828        |

| 001        | 0.424        |

| 010        | 0.212        |

| 011        | 0.106        |

| <u>100</u> | <u>0.053</u> |

| 101        | 0.026        |

| 110        | 0.013        |

| 111        | 0.006        |

\* Value at fs = 48kHz, 24kHz, 12kHz

## LC07410LG

#### • Recovery speed switch over thresh level 1

| THR1[2:0]  | Level to ALC_VAL |

|------------|------------------|

| 000        | -26dB            |

| 001        | -24dB            |

| 010        | -22dB            |

| <u>011</u> | <u>-20dB</u>     |

| 100        | -18dB            |

| 101        | -16dB            |

| 110        | -14dB            |

| 111        | Prohibition      |

| • Recovery speed switch over thresh level 2 |                  |  |  |  |  |

|---------------------------------------------|------------------|--|--|--|--|

| THR2[2:0]                                   | Level to ALC_VAL |  |  |  |  |

| THR2[2:0]  | Level to ALC_VAL |

|------------|------------------|

| 000        | -20dB            |

| 001        | -18dB            |

| 010        | -16dB            |

| <u>011</u> | <u>-14dB</u>     |

| 100        | -12dB            |

| 101        | -10dB            |

| 110        | -8dB             |

| 111        | Prohibition      |

#### • Zerocross timeout period

#### • Recovery alert time

| ZCDTM[1:0] | Timeout period* | fs = 48k/24k/12kHz |  | RWT[1:0]  | Standby time  | fs = 48k/24k/12kHz |

|------------|-----------------|--------------------|--|-----------|---------------|--------------------|

| 00         | 1024/fs         | 21.33ms            |  | 00        | 128/fs        | 2.67ms             |