### M80C186EB-16, -13, -8 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSOR

- Full Static Operation

- True CMOS Inputs and Outputs

- -55°C to + 125°C Operating Temperature Range

- Integrated Feature Set

- Low-Power Static CPU Core

- Two Independent UARTs each with

- an Integral Baud Rate Generator

- Two 8-Bit Multiplexed I/O Ports

- Programmable Interrupt Controller

- Three Programmable 16-Bit

- Timer/Counters

- Clock Generator

- Ten Programmable Chip Selects with Integral Wait-State Generator

- Memory Refresh Control Unit

- System Level Testing Support (ONCE Mode)

- Direct Addressing Capability to 1 Mbyte Memory and 64 Kbyte I/O

- Speed Versions Available:

- 16 MHz (M80C186EB-16)

- 13 MHz (M80C186EB-13)

- 8 MHz (M80C186EB-8)

- Low-Power Operating Modes:

- Idle Mode Freezes CPU Clocks but keeps Peripherals Active

- Powerdown Mode Freezes All Internal Clocks

- Complete System Development Support

- ASM86 Assembler, PL/M 86, Pascal 86, Fortran 86, C-86, and System Utilities

- In-Circuit Emulator (ICE<sup>™</sup>-186EB)

- Supports M80C187 Numeric Coprocessor Interface

- Available In:

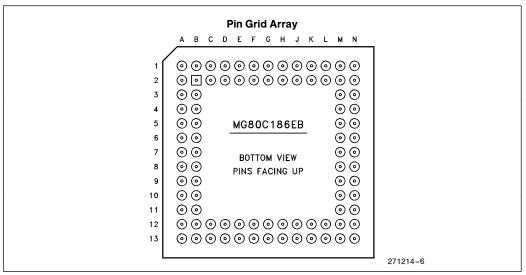

88-Lead Pin Grid Array (MG80C186EB)

The M80C186EB is a second generation CHMOS High-Integration microprocessor. It has features that are new to the M80C186 family and include a STATIC CPU core, an enhanced Chip Select decode unit, two independent Serial Channels, I/O ports, and the capability of Idle or Powerdown low power modes.

### M80C186EB-16, -13, -8 16-Bit High-Integration Embedded Processor

| CONTENTS                                                                                          | PAGE                                         |

|---------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                   | 4                                            |

| OVERVIEW<br>M80C186EB Core Architecture<br>Register Set<br>Instruction Set<br>Memory Organization | 4<br>4<br>5<br>5                             |

| Addressing Modes<br>Data Types<br>Interrupts<br>Bus Interface Unit                                | 7<br>7<br>9                                  |

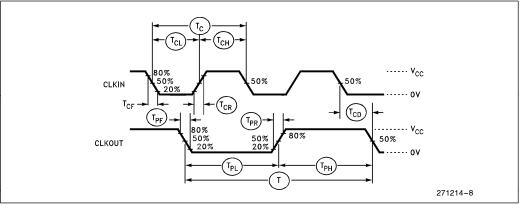

| Clock Generator                                                                                   | 10<br>10<br>10<br>12<br>12<br>13<br>13<br>13 |

| ONCE Test Mode PACKAGE INFORMATION                                                                |                                              |

| Pin Descriptions                                                                                  |                                              |

| M80C186EB PINOUT                                                                                  | 19                                           |

| ELECTRICAL SPECIFICATIONS Absolute Maximum Ratings                                                |                                              |

| OPERATING CONDITIONS                                                                              | 21                                           |

| RECOMMENDED CONNECTIONS                                                                           | 21                                           |

| DC SPECIFICATIONS<br>I <sub>CC</sub> versus Frequency and Voltage<br>PDTMR Pin Delay Calculation  | 23                                           |

| CONTENTS                                                                                                                  | PAGE     |

|---------------------------------------------------------------------------------------------------------------------------|----------|

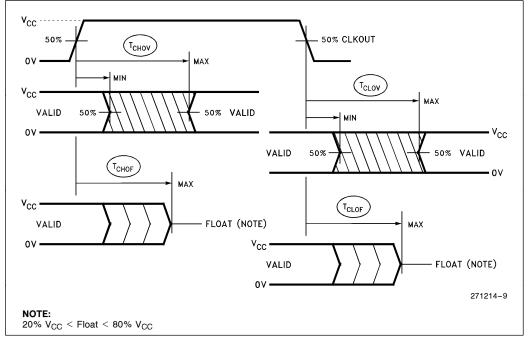

| AC SPECIFICATIONS<br>AC Characteristics—M80C186EB-16<br>AC Characteristics—M80C186EB-13<br>AC Characteristics—M80C186EB-8 | 24<br>25 |

| Relative Timings<br>(M80C186EB-16, -13, -8)<br>Serial Port Mode 0 Timings                                                 | 27       |

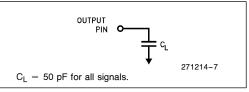

| (M80C186EB-16, -13, -8)<br>AC TEST CONDITIONS                                                                             | 29       |

| AC TIMING WAVEFORMS                                                                                                       | 29       |

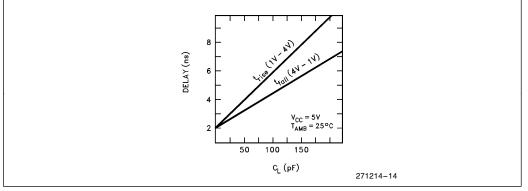

| DERATING CURVES                                                                                                           | 32       |

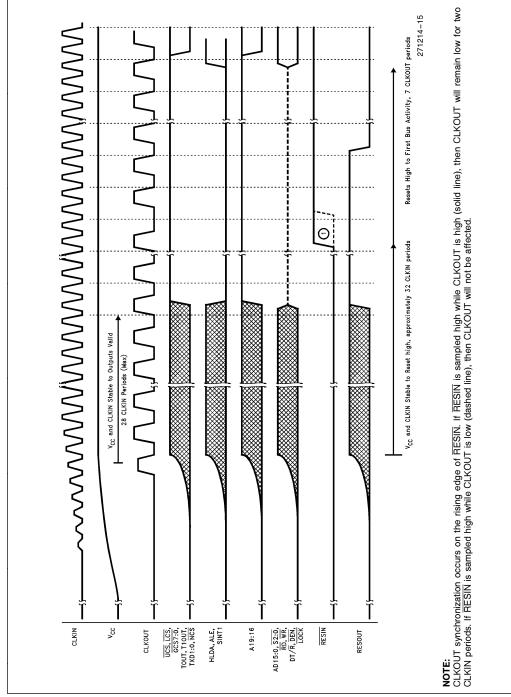

| RESET                                                                                                                     | 33       |

| COLD RESET WAVEFORMS                                                                                                      | 34       |

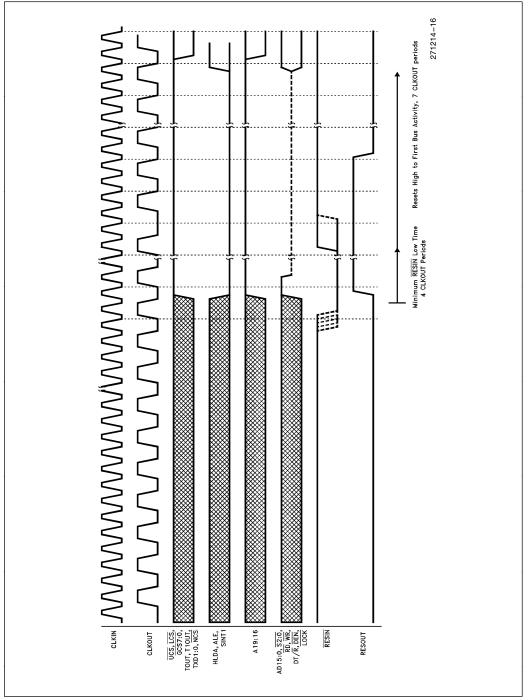

| WARM RESET WAVEFORMS                                                                                                      | 35       |

| BUS CYCLE WAVEFORMS                                                                                                       | 36       |

| REGISTER BIT SUMMARY                                                                                                      | 44       |

| M80C186EB EXECUTION TIMINGS                                                                                               | 48       |

| INSTRUCTION SET SUMMARY                                                                                                   | 49       |

| FOOTNOTES                                                                                                                 | 54       |

| 88-LEAD CERAMIC PIN GRID ARRAY<br>PACKAGE                                                                                 |          |

| ERRATA                                                                                                                    | 56       |

| REVISION HISTORY                                                                                                          | 56       |

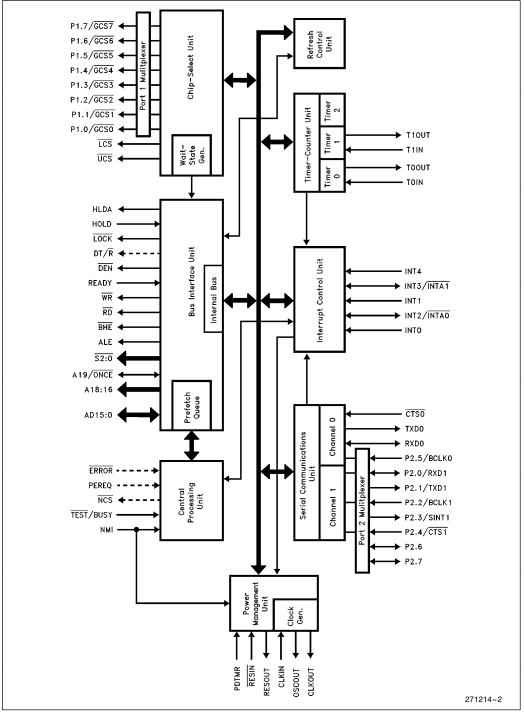

Figure 1. M80C186EB Block Diagram

### INTRODUCTION

The M80C186EB is the first product in a new generation of low-power, high-integration microprocessors. It enhances the existing 186 family by offering new features and new operating modes. The M80C186EB is object code compatible with the M80C186/M80C188 microprocessors.

The feature set of the M80C186EB meets the needs of low power, space critical applications. Low-Power applications benefit from the static design of the CPU core and the integrated peripherals. Minimum current consumption is achieved by providing a Powerdown mode that halts operation of the device, and freezes the clock circuits. Peripheral design enhancements ensure that non-initialized peripherals consume little current.

Space critical applications benefit from the integration of commonly used system peripherals. Two serial channels are provided for services such as diagnostics, inter-processor communication, modem interface, terminal display interface, and many others. A flexible chip select unit simplifies memory and peripheral interfacing. The interrupt unit provides sources for up to 129 external interrupts and will prioritize these interrupts with those generated from the on-chip peripherals. Three general purpose timer/counters and sixteen multiplexed I/O port pins round out the feature set of the M80C186EB.

### OVERVIEW

Figure 1 shows a block diagram of the M80C186EB. The Execution Unit (EU) is an enhanced M8086 CPU core that includes: dedicated hardware to speed up effective address calculations, enhance execution speed for multiple-bit shift and rotate instructions and for multiple and divide instructions, string move instructions that operate at full bus bandwidth, ten new instruction, and full static operation. The Bus Interface Unit (BIU) is the same as that found on the original 186 family products, except the queue-status mode has been deleted and buffer interface control has been changed to ease system design timings. An independent internal bus is used to allow communication between the BIU and internal peripherals.

### M80C186EB Core Architecture

#### REGISTER SET

The M8086, M8088, M80186, M80C186 and M80C188 all contain the same basic set of registers, instructions, and addressing modes. The M80C186EB is upward compatible with all of these microprocessors.

The M80C186EB base architecture has fourteen 16-bit registers as shown in Figure 2. There are eight general purpose registers which may be used for arithmetic and logic operands. Four of these registers (AX, BX, CX and DX) can be used as 16-bit registers or split into pairs of separate 8-bit registers. The other four registers (BP, SI, DI and SP) may also be used to determine offset addresses of operands in memory. These registers may contain base addresses or indexes to particular locations within a segment. The addressing mode selects the specific registers for operand and address calculations.

Another four 16-bit registers (CS, DS, ES, SS) select the segments of memory that are immediately addressable for code, stack, and data. There are two remaining special purpose registers (IP and F) that record or alter certain aspects of the M80C186EB processor state.

|  | 15                  |           |     |  |  |

|--|---------------------|-----------|-----|--|--|

|  | AH                  | AL        | AX  |  |  |

|  | BH                  | BL        | BX  |  |  |

|  | СН                  | CL        | CX  |  |  |

|  | DH                  | DL        | DX  |  |  |

|  | Source              | e Index   | SI  |  |  |

|  | Destinat            | ion Index | DI  |  |  |

|  | Base Pointer        |           | BP  |  |  |

|  | Stack Pointer       |           | SP  |  |  |

|  |                     |           |     |  |  |

|  | Code Segment        |           | CS  |  |  |

|  | Stack Segment       |           | SS  |  |  |

|  | Data Segment        |           | DS  |  |  |

|  | Extra Segment       |           | ES  |  |  |

|  |                     |           |     |  |  |

|  | Instruction Pointer |           | IP  |  |  |

|  | Flags               |           | F   |  |  |

|  | FIE                 | ags       | ] - |  |  |

Figure 2. M80C186EB Register Set

#### INSTRUCTION SET

The instruction set is divided into seven categories: data transfer, arithmetic, shift/rotate/logical, string manipulation, control transfer, high-level instructions, and processor control. These categories are summarized in Figure 4.

An M80C186EB instruction can reference anywhere from zero to several operands. An operand can reside in a register, in the instruction itself, or in memory.

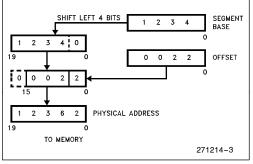

#### MEMORY ORGANIZATION

Memory is organized in sets of segments. Each segment is a linear contiguous sequence of up to 64K  $(2^{16})$  8-bit bytes. Memory is addressed using a twocomponent address (a pointer) that consists of a 16-bit base segment and a 16-bit offset. The 16-bit base segment values are contained in one of four internal segment registers (code, data stack, extra). The physical address is calculated by shifting the base value left by four bits and adding the 16-bit offset value to yield a 20-bit physical address (see Figure 3). The resulting 20-bit address allows for a 1 Mbyte address range.

Figure 3. Two Component Address

All instructions that address operands in memory must specify the base segment and the 16-bit offset value. For speed and compact instruction encoding, the segment register used for a physical address generation is implied by the addressing mode used (see Table 1). Special segment override instruction prefixes allow the implicit segment register selection rules to be overridden for special cases. The code, stack, data, and extra segments may coincide for simple programs.

| Memory<br>Reference<br>Needed | Segment<br>Register<br>Used | Implicit Segment<br>Selection Rule                                                            |

|-------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------|

| Instructions                  | Code (CS)                   | Instruction prefetch and immediate data                                                       |

| Stack                         | Stack (SS)                  | All stack pushes and pops;<br>any memory references<br>which use the BP register<br>as a base |

| External                      | Extra (ES)                  | All String instruction<br>references which use the<br>DI register as an index                 |

| Local Data                    | Data (DS)                   | All other data references                                                                     |

### Table 1. Segment Register Selection Rules

#### ADDRESSING MODES

The M80C186EB provides eight categories of addressing modes to specify operands. Two addressing modes are provided for instructions that operate on register or immediate operands:

- *Register Operand Mode:* The operand is located in one of the 8- or 16-bit general registers.

- *Immediate Operand Mode:* The operand is included in the instruction.

Six modes are provided to specify the location of an operand in a memory segment. A memory operand address consists of two 16-bit components: a segment base and an offset. The segment base is supplied by a 16-bit segment register either implicitly chosen by the addressing mode or explicitly chosen by a segment override prefix. The offset, also called the effective address, is calculated by summing any combination of the following three address elements:

- the *displacement* (an 8- or 16-bit immediate value contained in the instruction);

- the *base* (contents of either the BX or BP base registers); and

- the *index* (contents of either the SI or DI index registers).

| GENERAL PURPOSE | DIVISION                    | NO OPERATION            |

|-----------------|-----------------------------|-------------------------|

| MOV<br>PUSH     | DIV<br>IDIV                 | NOP                     |

| POP             | AAD                         | HIGH LEVEL INSTRUCTIONS |

| PUSHA           | CBW                         |                         |

| POPA            | CWD                         | ENTER                   |

| XCHG            |                             | LEAVE                   |

| XLAT            | STRING OPERATIONS           | BOUND                   |

| INPUT/OUTPUT    | MOVS<br>INS                 | CONDITIONAL TRANSFERS   |

| IN              | OUTS                        | JA/JNBE                 |

| OUT             | CMPS                        | JAE/JNB                 |

|                 | SCAS                        | JB/JNAE                 |

| ADDRESS OBJECT  | LODS<br>STOS                | JBE/JNA<br>JC           |

| LEA             | REP                         | JE/JZ                   |

| LDS             | REPE/REPZ                   | JG/JNLE                 |

| LES             | REPNE/REPNZ                 | JGE/JNL                 |

|                 |                             | JL/JNGE                 |

| FLAG TRANSFER   | LOGICALS                    | JLE/JNG                 |

| LAHF            | NOT                         | JNC<br>JNE/JNZ          |

| SAHF            | AND                         | JNO                     |

| PUSHF           | OR                          | JNP/JP0                 |

| POPF            | XOR                         | JNS                     |

|                 | TEST                        | JO                      |

| ADDITION        | 0                           | JP/JPE                  |

| ADD             | SHIFTS                      | JS                      |

| INC             | SHL/SAL                     | UNCONDITIONAL TRANSFERS |

| AAA             | SHR                         |                         |

| DAA             | SAR                         | CALL                    |

|                 |                             | RET                     |

| SUBSTRACTION    | ROTATES                     | JMP                     |

| SUB             | ROL                         | ITERATION CONTROLS      |

| SBB             | ROR                         |                         |

| DEC             | RCL                         | LOOP                    |

| NEG             | RCR                         | LOOPE/LOOPZ             |

| CMP             |                             | LOOPNE/LOOPNZ           |

| AAS<br>DAS      | FLAG OPERATIONS             | JCXZ                    |

| Di la           | STC                         | INTERRUPTS              |

| MULTIPLICATION  | CLC                         |                         |

|                 | CMC                         | INT                     |

| MUL             | STD                         | INTO                    |

| IMUL            | CLD                         | IRET                    |

| AAM             | STI<br>CLI                  |                         |

|                 |                             |                         |

|                 | EXTERNAL<br>SYNCHRONIZATION |                         |

|                 | HLT                         |                         |

|                 | WAIT                        |                         |

|                 | LOCK                        |                         |

|                 |                             |                         |

Figure 4. M80C186EB Instruction Set

Any carry out from the 16-bit addition is ignored. 8-bit displacements are sign extended to 16-bit values.

Combinations of these three address elements define the six memory addressing modes, described below.

- *Direct Mode:* The operand's offset is contained in the instruction as an 8- or 16-bit displacement element.

- *Register Indirect Mode:* The operand's offset is in one of the registers SI, DI, BX, or BP.

- Based Mode: The operand's offset is the sum of an 8- or 16-bit displacement and the contents of a base register (BX or BP).

- Indexed Mode: The operand's offset is the sum of an 8- or 16-bit displacement and the contents of an index register (SI or DI).

- *Based Indexed Mode:* The operand's offset is the sum of the contents of a base register and an index register.

- Based Indexed Mode with Displacement: The operand's offset is the sum of a base register's contents, an index register's contents, and an 8- or 16-bit displacement.

#### DATA TYPES

The M80C186EB directly supports the following data types:

- Integer: A signed binary numeric value contained in an 8-bit byte or 16-bit word. All operations assume a 2's complement representation. Signed 32- and 64-bit integers are supported using the M80C187 Numerics Coprocessor.

- Ordinal: An unsigned binary numeric value contained in an 8-bit byte or 16-bit word.

- Pointer: A 16- or 32-bit quantity, composed of a 16-bit offset component, or a 16-bit segment base component and a 16-bit offset component.

- String: A contiguous sequence of bytes or words. A string may contain from 1 Kbyte to 64 Kbytes.

- ASCII: A byte representation of alphanumeric and control characters using the ASCII standard of character representation.

- *BCD:* A byte (unpacked) representation of the decimal digits 0–9.

- Packed BCD: A byte (packed) representation of two decimal digits (0-9). One digit is stored in each nibble (4 bits) of the byte.

- *Floating Point:* A signed 32-, 64- or 80-bit real number representation. Floating point operands are supported when using the M80C187 Numeric Coprocessor.

In general, individual data elements must fit within defined segment limits.

#### INTERRUPTS

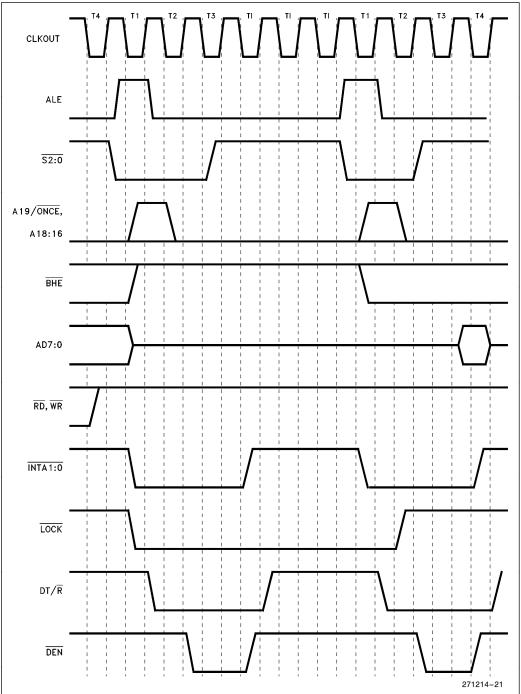

An interrupt transfers execution to a new program location. The old program address (CS:IP) and machine state (F) are saved on the stack to allow resumption of the interrupted program. Interrupts fall into three classes: hardware initiated, software (program) initiated, and instruction exception initiated. Hardware initiated interrupts occur in response to an external or internal input and are classified as non-maskable or maskable.

Programs may cause an interrupt by executing the "INT" instruction. Instruction exceptions occur when an illegal opcode has been fetched into the queue and is read by the execution unit. Another type of exception can be generated when executing an "ESC" instruction.

For all cases except the "ESC" exception, the return address from an exception will point at the instruction immediately following the instruction causing the exception. The return address after an "ESC" exception will point back to the ESC instruction causing the exception, or to the segment override prefix immediately preceding the ESC instruction if the prefix was present.

A table containing up to 256 pointers defines the proper interrupt service routine for each interrupt. Interrupts 0–31 are reserved by Intel. Table 2 shows the M80C186EB predefined type and default priority levels. For each interrupt, an 8-bit vector (Vector Type) identifies the appropriate table entry. Multiplying the 8-bit vector by 4 defines the vector address. INT instructions contain or imply the vector type and allow access to all 256 interrupts.

| Table 2. M80C186EB Interrupt Vector | Table 2. | M80C186EB | Interrupt | Vectors |

|-------------------------------------|----------|-----------|-----------|---------|

|-------------------------------------|----------|-----------|-----------|---------|

| Interrupt<br>Name         | Vector<br>Type | Vector<br>Address | Default<br>Priority | Related<br>Instructions |

|---------------------------|----------------|-------------------|---------------------|-------------------------|

| Divide Error              | 0              | 00H               | 1                   | DIV, IDIV               |

| Single Step Interrupt     | 1              | 04H               | 1A                  | All                     |

| Non-Maskable Interrupt    | 2              | 08H               | 1                   | INT 2 or NMI            |

| One Byte Interrupt        | 3              | 0CH               | 1                   | INT                     |

| Interrupt on Overflow     | 4              | 10H               | 1                   | INT0                    |

| Array Bounds Check        | 5              | 14H               | 1                   | BOUND                   |

| Invalid OP-Code           | 6              | 18H               | 1                   | Illegal Inst            |

| ESC OP-Code Interrupt     | 7              | 1CH               | 1                   | ESC OP-Codes            |

| Timer 0 Interrupt         | 8              | 20H               | 2                   |                         |

| Reserved                  | 9–11           | 24H-2CH           |                     |                         |

| INT0 Interrupt            | 12             | 30H               | 5                   |                         |

| INT1 Interrupt            | 13             | 34H               | 6                   |                         |

| INT2 Interrupt            | 14             | 38H               | 7                   |                         |

| INT3 Interrupt            | 15             | 3CH               | 8                   |                         |

| Numerics Exception        | 16             | 40H               | 1                   | ESC OP-Codes            |

| INT4 Interrupt            | 17             | 44H               | 4                   |                         |

| Timer1 Interrupt          | 18             | 48H               | 2A                  |                         |

| Timer2 Interrupt          | 19             | 4CH               | 2B                  |                         |

| UART 0 Receive Interrupt  | 20             | 50H               | 3                   |                         |

| UART 0 Transmit Interrupt | 21             | 54H               | ЗA                  |                         |

| Reserved                  | 22-31          | 58H-7CH           |                     |                         |

#### **BUS INTERFACE UNIT**

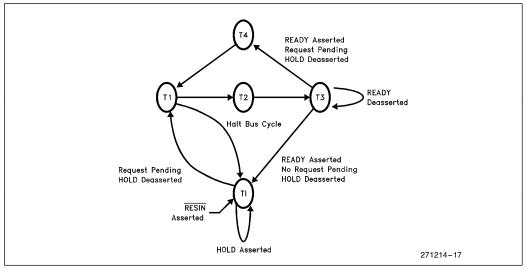

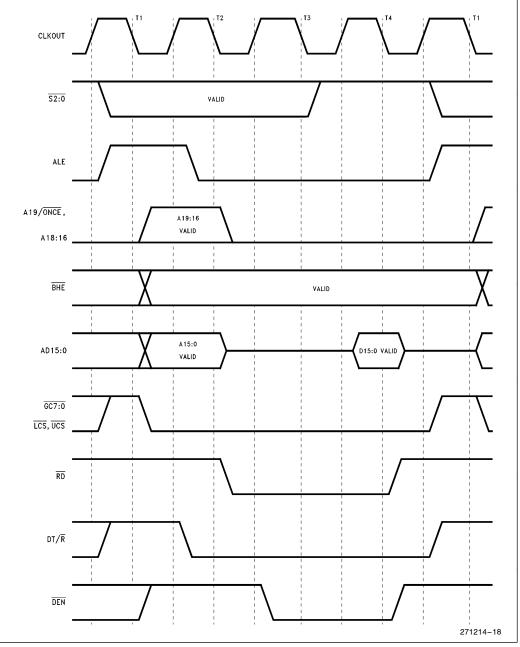

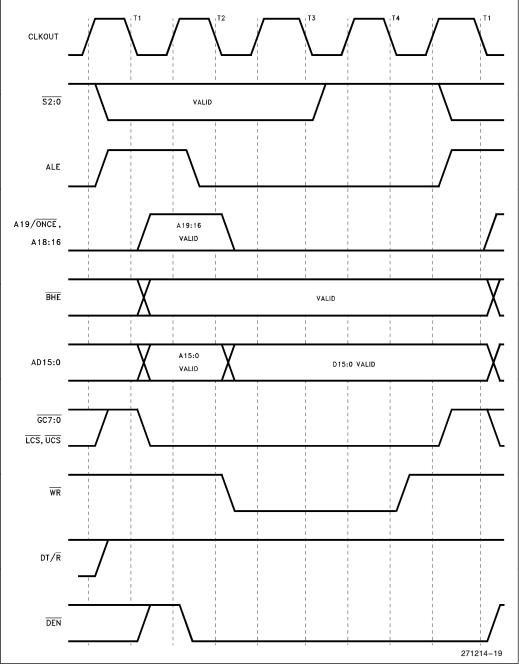

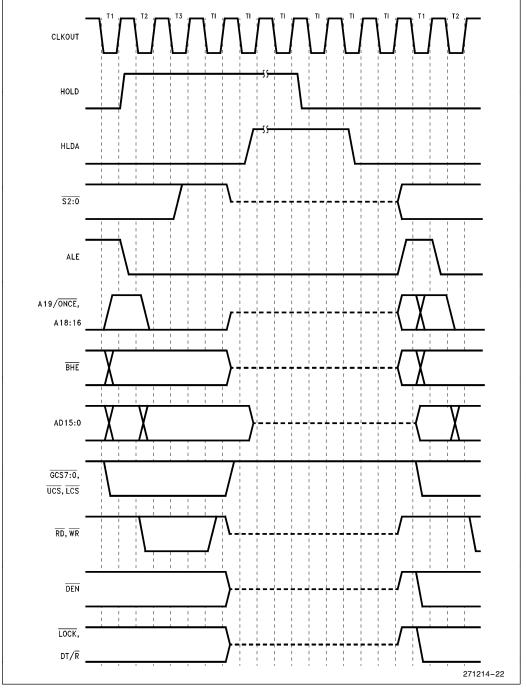

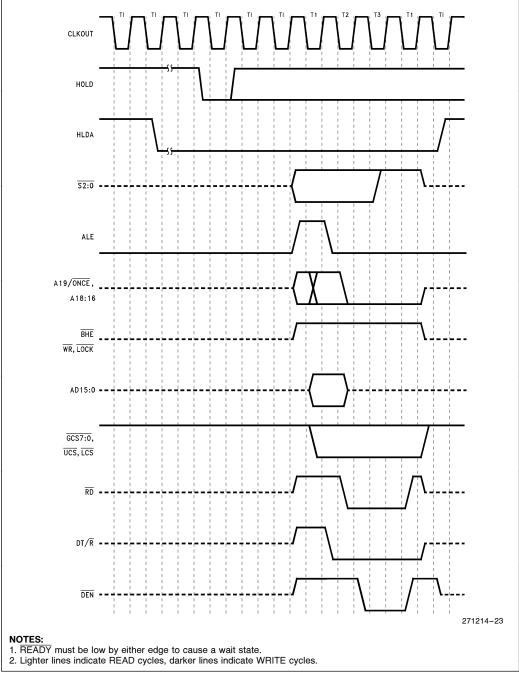

The M80C186EB core incorporates a bus controller that generates local bus control signals. In addition, it employs a HOLD/HLDA protocol to share the local bus with other bus masters.

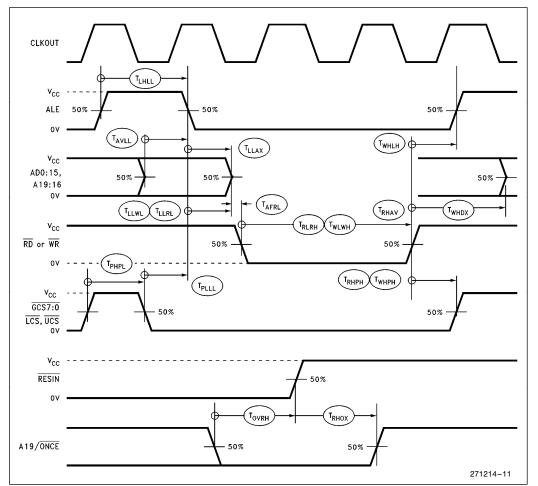

The bus controller is responsible for generating 20 bits of address, read and write strobes, bus cycle status information, and data (for write operations) information. It is also responsible for reading data off the local bus during a read operation. A READY input pin is provided to extend a bus cycle beyond the minimum four states (clocks).

A HOLD/HLDA protocol is provided by the local bus controller to allow multiple bus masters to share the same local bus. When the M80C186EB relinquishes control of the local bus, it floats certain bus control signals to allow another bus master to drive these pins directly. Refer to the Pin Description section to determine which pins the M80C186EB will float during a HOLD/HLDA bus exchange.

The M80C186EB local bus controller also generates two control signals ( $\overline{\text{DEN}}$  and DT/R) when interfacing to external transceiver chips. This capability allows the addition of transceivers for simple buffering of the mulitplexed address/data bus.

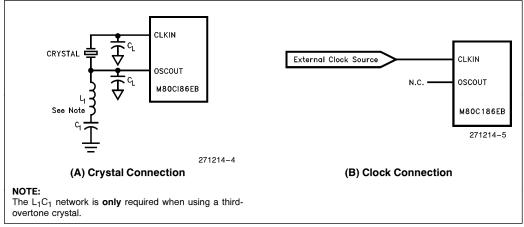

#### **CLOCK GENERATOR**

The M80C186EB provides an on-chip clock generator for both internal and external clock generation. The clock generator features a crystal oscillator, a divide-by-two counter, and two low-power operating modes.

The oscillator circuit is designed to be used with either a **parallel resonant** fundamental or third-overtone mode crystal network. Alternatively, the oscillator circuit may be driven from an external clock source. Figure 5 shows the various operating modes of the M80C186EB oscillator circuit.

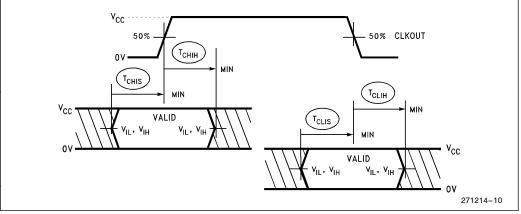

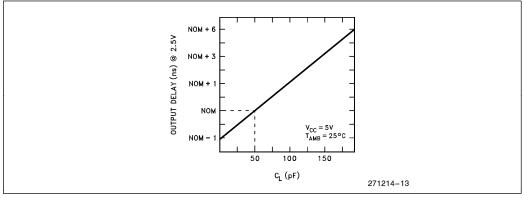

The crystal or clock frequency chosen must be twice the required processor operating frequency due to the internal divide-by-two counter. This counter is used to drive all internal phase clocks and the external CLKOUT signal. CLKOUT is a 50% duty cycle processor clock and can be used to drive other system components. All AC timings are referenced to CLKOUT.

The following parameters are recommended when choosing a crystal:

Figure 5. M80C186EB Clock Configurations

### M80C186EB Peripheral Architecture

The M80C186EB has integrated several common system peripherals with a CPU core to create a compact, yet powerful system. The integrated peripherals are designed to be flexible and provide logical interconnections between supporting units (e.g., the interrupt control unit supports interrupt requests from the timer/counters or serial channels).

The list of integrated peripherals include:

- 7-Input Interrupt Control Unit

- 3-Channel Timer/Counter Unit

- 2-Channel Serial Communications Unit

- 10-Output Chip-Select Unit

- I/O Port Unit

- Refresh Control Unit

- · Power Management Unit

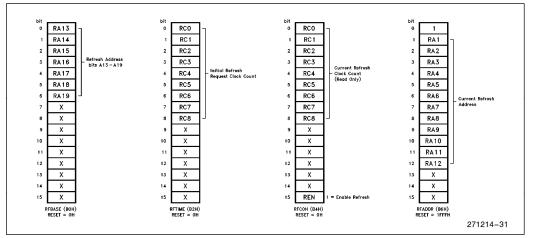

The registers associated with each integrated periheral are contained within a 128 x 16 register file called the Peripheral Control Block (PCB). The PCB can be located in either memory or I/O space on any 256 Byte address boundary. During bus cycles that access the PCB, the bus controller will signal the operation externally (i.e., the RD, WR, status, address, data, etc., lines will be driven as in a normal bus cycle). However, READY is ignored and the contents of the data bus during a read operation is ignored.

The starting address of the PCB is controlled by a relocation register and can overlap any of the memory or I/O regions programmed into the Chip Select Unit. In this case, the overlapped chip select will not go active when the PCB is read or written.

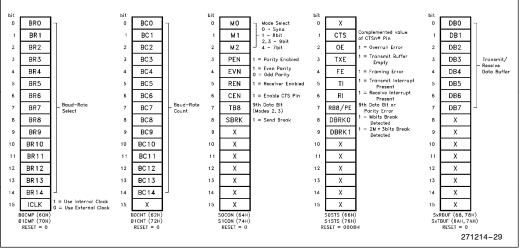

Figure 6 provides a list of the registers associated with the PCB. The Register Bit Summary at the end of this specification individually lists all of the registers and identifies each of their programming attributes.

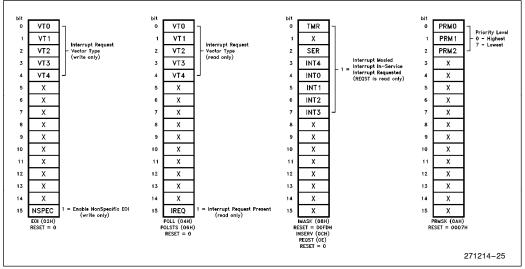

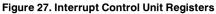

#### INTERRUPT CONTROL UNIT

The M80C186EB can receive interrupts from a number of sources, both internal and external. The interrupt control unit serves to merge these requests on a priority basis, for individual service by the CPU. Each interrupt source can be independently masked by the Interrupt Control Unit (ICU) or all interrupts can be globally masked by the CPU. Internal interrupt sources include the Timers and Serial channel 0. External interrupt sources come from the five input pins INT4:0. The NMI interrupt pin is not controlled by the ICU and is passed directly to the CPU. Although the Timer and Serial channel each have only one request input to the ICU, separate vector types are generated to service individual interrupts within the Timer and Serial channel units.

The M80C186EB ICU provides a mechanism for expanding the number of external interrupt sources. Two pairs of pins can be independently configured to support an external slave interrupt controller (82C59A). Each pair of external pins can be expanded to support 64 interrupts, making it possible for the M80C186EB to support a total of 129 external interrupts.

The ICU may be used in a polled mode if interrupts are undesirable. When polling, the processor disables interrupts and then polls the ICU whenever it is convenient.

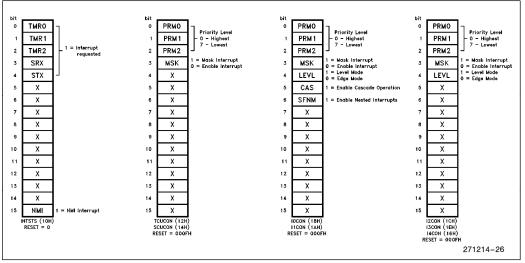

#### TIMER/COUNTER UNIT

The M80C186EB Timer/Counter Unit (TCU) provides three 16-bit programmable timers. Two of these are highly flexible and are connected to external pins for control or clocking. A third timer is not connected to any external pins and can only be clocked internally. However, it can be used to clock the other two timer channels. The TCU can be used to count external events, time external events, generate non-repetitive waveforms, generate timed interrupts, etc.

Each timer has at least one 16-bit compare register and one 16-bit count register. Timers 0 and 1 each have an additional 16-bit compare register. The count register is incremented every fourth CPU clock cycle (internal clocking), every time Timer2 expires (Timers 0 and 1 only), or every Low-to-High transition on the timer input pin (Timers 0 and 1 only). The input clock to Timers 0 and 1 must not exceed one fourth the operating frequency of the M80C186EB. When the count register matches the value programmed into the compare register, several operations may happen.

All three timers can generate an interrupt when the compare register matches the value in the count register. Additionally, Timers 0 and 1 have an output pin that can change state or pulse when the compare condition occurs.

| PCB<br>Offset | Function          | PCB<br>Offset | Function        | PCB<br>Offset | Function        | PCB<br>Offset | Function |

|---------------|-------------------|---------------|-----------------|---------------|-----------------|---------------|----------|

| 00H           | Reserved          | 40H           | Timer2 Count    | 80H           | GCS0 Start      | COH           | Reserved |

| 02H           | End Of Interrupt  | 42H           | Timer2 Compare  | 82H           | GCS0 Stop       | C2H           | Reserved |

| 04H           | Poll              | 44H           | Reserved        | 84H           | GCS1 Start      | C4H           | Reserved |

| 06H           | Poll Status       | 46H           | Timer2 Control  | 86H           | GCS1 Stop       | C6H           | Reserved |

| 08H           | Interrupt Mask    | 48H           | Reserved        | 88H           | GCS2 Start      | C8H           | Reserved |

| 0AH           | Priority Mask     | 4AH           | Reserved        | 8AH           | GCS2 Stop       | CAH           | Reserved |

| 0CH           | In-Service        | 4CH           | Reserved        | 8CH           | GCS3 Start      | ССН           | Reserved |

| 0EH           | Interrupt Request | 4EH           | Reserved        | 8EH           | GCS3 Stop       | CEH           | Reserved |

| 10H           | Interrupt Status  | 50H           | Reserved        | 90H           | GCS4 Start      | D0H           | Reserved |

| 12H           | Timer Control     | 52H           | Port0 Pin       | 92H           | GCS4 Stop       | D2H           | Reserved |

| 14H           | Serial Control    | 54H           | Port0 Control   | 94H           | GCS5 Start      | D4H           | Reserved |

| 16H           | INT4 Control      | 56H           | Port0 Latch     | 96H           | GCS5 Stop       | D6H           | Reserved |

| 18H           | INT0 Control      | 58H           | Port1 Direction | 98H           | GCS6 Start      | D8H           | Reserved |

| 1AH           | INT1 Control      | 5AH           | Port1 Pin       | 9AH           | GCS6 Stop       | DAH           | Reserved |

| 1CH           | INT2 Control      | 5CH           | Port1 Control   | 9CH           | GCS7 Start      | DCH           | Reserved |

| 1EH           | INT3 Control      | 5EH           | Port1 Latch     | 9EH           | GCS7 Stop       | DEH           | Reserved |

| 20H           | Reserved          | 60H           | Serial0 Baud    | A0H           | LCS Start       | E0H           | Reserved |

| 22H           | Reserved          | 62H           | Serial0 Count   | A2H           | LCS Stop        | E2H           | Reserved |

| 24H           | Reserved          | 64H           | Serial0 Control | A4H           | UCS Start       | E4H           | Reserved |

| 26H           | Reserved          | 66H           | Serial0 Status  | A6H           | UCS Stop        | E6H           | Reserved |

| 28H           | Reserved          | 68H           | Serial0 RBUF    | A8H           | Relocation      | E8H           | Reserved |

| 2AH           | Reserved          | 6AH           | Serial0 TBUF    | AAH           | Reserved        | EAH           | Reserved |

| 2CH           | Reserved          | 6CH           | Reserved        | ACH           | Reserved        | ECH           | Reserved |

| 2EH           | Reserved          | 6EH           | Reserved        | AEH           | Reserved        | EEH           | Reserved |

| 30H           | Timer0 Count      | 70H           | Serial1 Baud    | B0H           | Refresh Base    | F0H           | Reserved |

| 32H           | Timer0 Compare A  | 72H           | Serial1 Count   | B2H           | Refresh Time    | F2H           | Reserved |

| 34H           | Timer0 Compare B  | 74H           | Serial1 Control | B4H           | Refresh Control | F4H           | Reserved |

| 36H           | Timer0 Control    | 76H           | Serial1 Status  | B6H           | Refresh Address | F6H           | Reserved |

| 38H           | Timer1 Count      | 78H           | Serial1 RBUF    | B8H           | Power Control   | F8H           | Reserved |

| ЗАН           | Timer1 Compare A  | 7AH           | Serial1 TBUF    | BAH           | Reserved        | FAH           | Reserved |

| ЗСН           | Timer1 Compare B  | 7CH           | Reserved        | BCH           | Step ID         | FCH           | Reserved |

| 3EH           | Timer1 Control    | 7EH           | Reserved        | BEH           | Reserved        | FEH           | Reserved |

Figure 6. M80C186EB Peripheral Control Block Registers

### M80C186EB

Other timer programming options include:

- All three timers can be set to halt or continue after a compare match.

- Timers 0 and 1 can be reset or retriggered using their respective input pins.

- TCU registers can be read or written at any time.

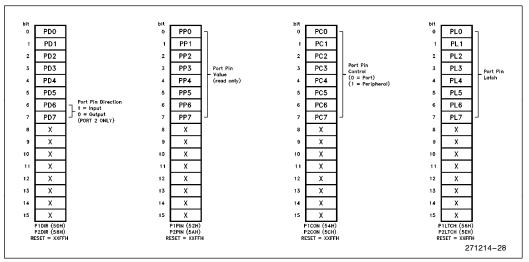

### SERIAL COMMUNICATIONS UNIT

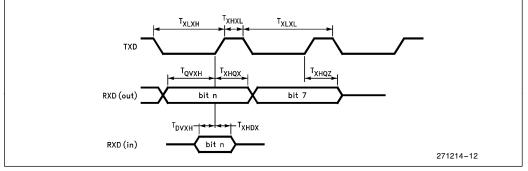

The Serial Control Unit (SCU) of the M80C186EB contains two independent channels. Each channel is identical in operation except that only channel 0 is supported by the integrated interrupt controller (channel 1 has an external interrupt pin). Each channel has its own baud rate generator that is independent of the Timer/Counter Unit, and can be internally or externally clocked at up to one half the M80C186EB operating frequency.

Each serial channel supports one synchronous and four asynchronous modes of operation and is compatible with the serial ports of the MCS®-51 and MCS®-96 family of products. Data field length can be 7-, 8-, or 9-bits with optional odd or even parity (generated and checked) and one stop bit (generated and checked). The 9-bit mode has an optional "addressing" feature to simplify interprocessor communication. Each serial port is doubled buffered in both transmit and receive operation (data can be read or written to a buffer register while data is shifted into or out of a shifting register, respectively).

A Clear-To-Send input pin can be programmed to prevent data transmission if the pin is sampled inactive. Serial channel 0 is supported by the integrated interrupt controller, providing separate receive and transmit vector types. Serial channel 1 has an external interrupt pin which OR's the receive and transmit interrupts. This external interrupt pin can be routed to either the external pins of the ICU, the NMI pin, or any other external system interrupt controller. Status bits are provided to allow polling of the serial channels if interrupts are not desired.

Independent baud rate generators are provided for each of the serial channels. For the asynchronous modes, the generator supplies an 8x baud clock to both the receive and transmit register logic. A 1x baud clock is provided in the synchronous mode. Additional features of the SCU include:

- Framing error, receive buffer overrun error, and parity error detection.

- Break detect.

- Break send.

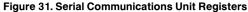

### CHIP-SELECT UNIT

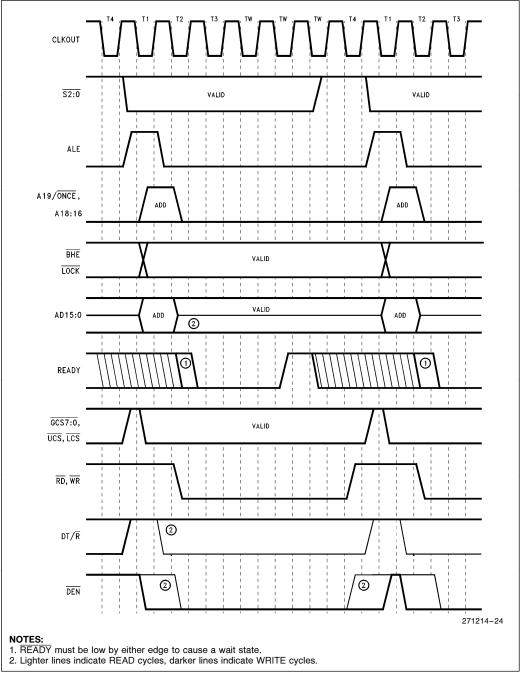

The M80C186EB Chip-Select Unit (CSU) integrates logic which provides up to ten programmable chipselects to access both memories and peripherals. In addition, each chip-select can be programmed to automatically insert additional clocks (wait-states) into the current bus cycle and automatically terminate a bus cycle independent of the condition of the READY input pin.

Each of the chip-selects can be programmed to go active for either memory or I/O accesses. UCS is the only chip-select that is active after a reset and is enabled for memory addresses in the range OFFC00H to OFFFFFH (this allows a boot-ROM to be accessed using UCS). Every chip-select has a programmable start and stop register that defines the active region for the chip-select, and the ready characteristics for the region.

The start and stop address fields are 10 bits in length and are matched against the upper 10 bits of either the memory or I/O address. A 10-bit compare results in a granularity of 1 Kbytes for memory accesses and 64 bytes for I/O accesses. Each chip select can be disabled by programming its start address greater than its stop address or by clearing its enable bit.

Each chip-select can be programmed to automatically insert wait-states, and to control whether the external READY input is to be ignored or used. The M80C186EB bus controller will wait the programmed number of wait-states before the external READY pin can be used to extend or terminate the bus cycle.

Overlapping of chip-selects is allowed. However, each one that overlaps will go active. If any overlapping chip-select has been programmed to use external ready, the bus control unit will insert the least amount of programmed wait-states programmed before the external ready pin is used. If all overlapped chip-selects ignore external ready, the bus controller will insert the maximum number of programmed wait-states. Any chip-select that overlaps the Peripheral Control Block (PCB) will not go active for that portion of the address range allocated to the PCB.

The Generic Chip-Selects (GCS7:0) are multiplexed with an output only Port function. Any channel that is being used as a chip-select must be disabled as a port pin by correctly programming the port pin control registers (see the following section).

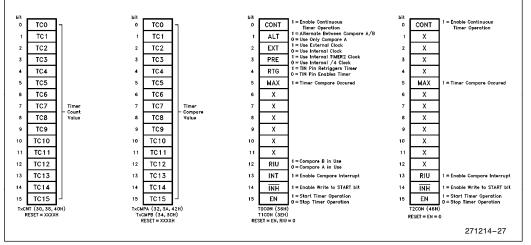

#### **I/O PORT UNIT**

The I/O Port Unit (IPU) on the M80C186EB supports two 8-bit channels of input, output, or input/output operation. Port 1 is multiplexed with the chip select pins and is output only. Most of Port 2 is multiplexed with the serial channel pins. Port 2 pins are limited to either an output or input function depending on the operation of the serial pin it is multiplexed with.

Two bits of Port 2 are not multiplexed with any other peripheral functions and can be used as either an input or an output function. A port direction register is used to define the function of the port pin. The output for these two pins are open drain.

Besides a direction register, each port channel has a data latch register, port pin register, and a port multiplexer control register.

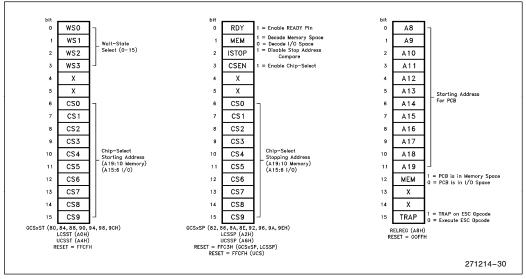

#### **REFRESH CONTROL UNIT**

The Refresh Control Unit (RCU) automatically generates a periodic memory read bus cycle to keep dynamic or pseudo-static memory refreshed. A 9-bit counter controls the number of clocks between refresh requests.

A 12-bit address generator is maintained by the RCU and is presented on the A12:1 address lines during the refresh bus cycle. The address generator is incremented only after the refresh bus cycle is run. This ensures that all address combinations will be presented to the memory array even if the refresh bus cycle is not run before another request is generated. Address bits A19:13 are programmable to allow the refresh address block to be located on any 8 Kbyte boundary.

The chip-select unit is active during refresh bus cycles. This means that a chip-select will go active if the refresh address is within the limits specified for the channel. In addition,  $\overline{BHE}$  and A0 are both driven high during refresh bus cycles (this is normally an invalid bus condition). Data on the AD15:0 bus is ignored. A pending refresh request will attempt to abort a HOLD/HLDA bus exchange. HLDA is deasserted when a refresh request is pending and a bus HOLD is already in progress. HOLD must then be released in order for the M80C186EB to execute the refresh bus cycle.

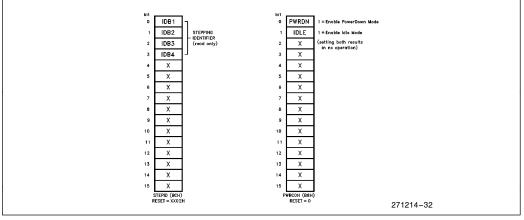

#### POWER MANAGEMENT UNIT

The M80C186EB Power Management Unit (PMU) is provided to control the power consumption of the device. The PMU provides three power modes: Active, Idle, and Powerdown.

Active Mode indicates that all units on the M80C186EB are functional and the device consumes maximum power (depending on the level of peripheral operation). Idle Mode freezes the clocks of the Execution and Bus units at a logic zero state (all peripherals continue to operate normally). An unmasked interrupt, NMI, or reset will cause the M80C186EB to exit the Idle mode.

The Powerdown mode freezes all internal clocks at a logic zero level and disables the crystal oscillator. All internal registers hold their values provided  $V_{CC}$  is maintained. Current consumption is reduced to just transistor junction leakage. An NMI or processor reset will cause the M80C186EB to exit the Powerdown Mode. A timing pin is provided to establish the length of time between exiting Powerdown and resuming device operation. (Length of time depends on startup time of crystal oscillator and is application dependent.)

### M80C187 Interface

The M80C186EB supports the direct connection of the M80C187 Numerics Coprocessor.

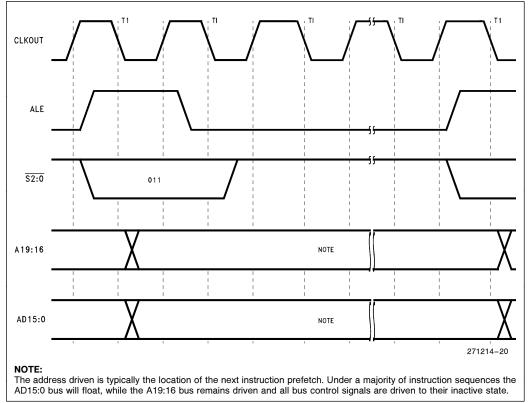

### **ONCE Test Mode**

To facilitate testing and inspection of devices when fixed into a target system, the M80C186EB has a test mode available which forces all output and input/output pins to be placed in the high-impedance state. ONCE stands for "ON Circuit Emulation". The ONCE mode is selected by forcing the A19/ONCE pin LOW (0) during a processor reset (this pin is weakly held to a HIGH (1) level) while RESIN is active.

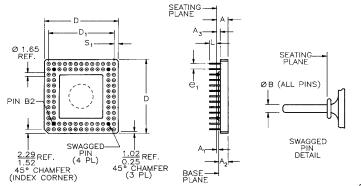

### PACKAGE INFORMATION

This section describes the pins, pinouts, and thermal characteristics for the M80C186EB PGA package. For complete package specifications and information, see the Intel Packaging Outlines and Dimensions Guide (Order Number: 231369).

### **Pin Descriptions**

The M80C186EB pins are described in this section. Table 3 presents the legend for interpreting the pin descriptions in Table 4. Figure 7 provides an example pin description entry. The "I/O" signifies that the pins are bidirectional (i.e., have both an input and output function). The "S" indicates that, as an input, the signal is synchronized to CLKOUT for proper operation. The "H(Z)" indicates that these pins will float while the processor is in the Hold Acknowledge state. R(Z) indicates that these pins will retain its current value when Idle or Powerdown Modes are entered.

All pins float while the processor is in the ONCE Mode, except OSCOUT (OSCOUT is required for crystal operation).

| Name   | Туре                                | Description                                                                                                                                                                                                                                                                                      |

|--------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD15:0 | I/O<br>S(L)<br>H(Z)<br>R(Z)<br>P(X) | These pins provide a multiplexed<br>ADDRESS and DATA bus. During<br>the address phase of the bus<br>cycle, address bits 0 through 15<br>are presented on the bus and can<br>be latched using ALE. 8- or 16-bit<br>data information are transferred<br>during the data phase of the bus<br>cycle. |

**Table 3. Pin Description Nomenclature**

| Symbol | Description                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I      | Input Only Pin                                                                                                                                                                                              |

| 0      | Output Only Pin                                                                                                                                                                                             |

| 1/0    | Pin can be either input or output                                                                                                                                                                           |

|        | Pin "must be" connected as described                                                                                                                                                                        |

| S()    | Synchronous. Input must meet setup and<br>hold times for proper operation of the<br>processor. The pin is:<br>S(E) edge sensitive<br>S(L) level sensitive                                                   |

| A()    | Asynchronous. Input must meet setup and<br>hold only to guarantee recognition. The<br>pin is:<br>A(E) edge sensitive<br>A(L) level sensitive                                                                |

| H()    | While the processor's bus is in the Hold<br>Acknowledge state, the pin:<br>$H(1)$ is driven to $V_{CC}$<br>$H(0)$ is driven to $V_{SS}$<br>H(Z) floats<br>H(Q) remains active<br>H(X) retains current state |

| R()    | While the processor's $\overline{\text{RES}}$ line is low, the pin:<br>R(1) is driven to V <sub>CC</sub><br>R(0) is driven to V <sub>SS</sub><br>R(Z) floats<br>R(WH) weak pullup<br>R(WL) weak pulldown    |

| P()    | While Idle or Powerdown modes are<br>active, the pin:<br>P(1) is driven to $V_{CC}$<br>P(0) is driven to $V_{SS}$<br>P(Z) floats<br>P(Q) remains active <sup>(1)</sup><br>P(X) retains current state        |

#### NOTE:

Any pin that specifies P(Q) are valid for Idle Mode. All pins are P(X) for Powerdown Mode.

### Table 4. M80C186EB Pin Descriptions

| Name               | Туре                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>    |                                      | <b>POWER</b> connections consist of four pins which must be shorted externally to a $V_{CC}$ board plane.                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub>    |                                      | $\mbox{GROUND}$ connections consist of six pins which must be shorted externally to a $V_{SS}$ board plane.                                                                                                                                                                                                                                                                                                                                      |

| CLKIN              | l<br>A(E)                            | <b>CLock INput</b> is an input for an external clock. An external oscillator operating at two times the required M80C186EB operating frequency can be connected to CLKIN. For crystal operation, CLKIN (along with OSCOUT) are the crystal connections to an internal Pierce oscillator.                                                                                                                                                         |

| OSCOUT             | 0<br>H(Q)<br>R(Q)<br>P(Q)            | <b>OSCillator OUTput</b> is only used when using a crystal to generate the external clock. OSCOUT (along with CLKIN) are the crystal connections to an internal Pierce oscillator. This pin is not to be used as 2X clock output for non-crystal applications (i.e., this pin is N.C. for non-crystal applications). OSCOUT does not float in ONCE mode.                                                                                         |

| CLKOUT             | 0<br>H(Q)<br>R(Q)<br>P(Q)            | <b>CLock OUTput</b> provides a timing reference for inputs and outputs of the processor, and is one-half the input clock (CLKIN) frequency. CLKOUT has a 50% duty cycle and transistions every falling edge of CLKIN.                                                                                                                                                                                                                            |

| RESIN              | I<br>A(L)                            | <b>RESet IN</b> causes the M80C186EB to immediately terminate any bus cycle in progress and assume an initialized state. All pins will be driven to a known state, and RESOUT will also be driven active. The rising edge (low-to-high) transition synchronizes CLKOUT with CLKIN before the M80C186EB begins fetching opcodes at memory location 0FFFF0H.                                                                                       |

| RESOUT             | O<br>H(0)<br>R(1)<br>P(0)            | <b>RESet OUTput</b> that indicates the M80C186EB is currently in the reset state. RESOUT will remain active as long as RESIN remains active.                                                                                                                                                                                                                                                                                                     |

| PDTMR              | I/O<br>A(L)<br>H(WH)<br>R(Z)<br>P(1) | <b>Power-Down TiMeR</b> pin (normally connected to an external capacitor) that determines the amount of time the M80C186EB waits after an exit from power down before resuming normal operation. The duration of time required will depend on the startup characteristics of the crystal oscillator.                                                                                                                                             |

| NMI                | l<br>A(E)                            | Non-Maskable Interrupt input causes a TYPE-2 interrupt to be serviced by the CPU. NMI is latched internally.                                                                                                                                                                                                                                                                                                                                     |

| TEST/BUSY          | l<br>A(E)                            | <b>TEST</b> is used during the execution of the WAIT instruction to suspend CPU operation until the pin is sampled active (LOW). TEST is alternately known as BUSY when interfacing with an M80C187 numerics coprocessor.                                                                                                                                                                                                                        |

| AD15:0             | I/O<br>S(L)<br>H(Z)<br>R(Z)<br>P(X)  | These pins provide a multiplexed <b>Address</b> and <b>Data</b> bus. During the address phase of the bus cycle, address bits 0 through 15 are presented on the bus and can be latched using ALE. 8- or 16-bit data information is transferred during the data phase of the bus cycle.                                                                                                                                                            |

| A18:16<br>A19/ONCE | H(Z)<br>R(WH)<br>P(X)                | These pins provide multiplexed <b>Address</b> during the address phase of<br>the bus cycle. Address bits 16 through 19 are presented on these<br>pins and can be latched using ALE. These pins are driven to a logic 0<br>during the data phase of the bus cycle. During a processor reset<br>(RESIN active), A19/ONCE is used to enable ONCE mode. A18:16<br>must not be driven low during reset or improper M80C186EB<br>operation may result. |

### M80C186EB

| Name         | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>\$2:0</u> | 0<br>H(Z)<br>R(Z)<br>P(1)    | Bus cycle Status       are encoded on these pins to provide bus transaction information. S2:0 are encoded as follows:         S2       S1       S0       Bus Cycle Initiated         0       0       0       Interrupt Acknowledge         0       0       1       Read I/O         0       1       0       Write I/O         0       1       1       Processor HALT         1       0       0       Queue Instruction Fetch         1       0       1       Read Memory         1       1       0       Write Memory         1       1       1       Passive (no bus activity) |

| ALE          | O<br>H(0)<br>R(0)<br>P(0)    | <b>Address Latch Enable</b> output is used to strobe address information into a transparent type latch during the address phase of the bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BHE          | O<br>H(Z)<br>R(Z)<br>P(X)    | Byte High Enable output to indicate that the bus cycle in progress is<br>transferring data over the upper half of the data bus. BHE and A0 have the<br>following logical encoding:A0BHEEncoding00Word Transfer01Even Byte Transfer10Odd Byte Transfer11Refresh Operation                                                                                                                                                                                                                                                                                                        |

| RD           | O<br>H(Z)<br>R(Z)<br>P(1)    | <b>ReaD</b> output signals that the accessed memory or I/O device must drive data information onto the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WR           | O<br>H(Z)<br>R(Z)<br>P(1)    | <b>WRite</b> output signals that data available on the data bus are to be written into the accessed memory or I/O device.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| READY        | l<br>A(L)<br>S(L)            | <b>READY</b> input to signal the completion of a bus cycle. READY must be active to terminate any M80C186EB bus cycle, unless it is ignored by correctly programming the Chip-Select Unit.                                                                                                                                                                                                                                                                                                                                                                                      |

| DEN          | O<br>H(Z)<br>R(Z)<br>P(1)    | <b>Data ENable</b> output to control the enable of bi-directional transceivers when buffering a M80C186EB system. DEN is active only when data is to be transferred on the bus.                                                                                                                                                                                                                                                                                                                                                                                                 |

| DT/R         | O<br>H(Z)<br>R(Z)<br>P(X)    | <b>Data Transmit/Receive</b> output controls the direction of a bi-directional buffer when buffering an M80C186EB system.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LOCK         | I/O<br>H(Z)<br>R(WH)<br>P(1) | <b>LOCK</b> output indicates that the bus cycle in progress is not to be interrupted. The M80C186EB will not service other bus requests (such as HOLD) while LOCK is active. This pin is configured as a weakly held high input while RESIN is active and must not be driven low.                                                                                                                                                                                                                                                                                               |

### Table 4. M80C186EB Pin Descriptions (Continued)

| Table 4. M80C186EB Pin I | Descriptions (Continued) |

|--------------------------|--------------------------|

|--------------------------|--------------------------|

| Name                                                                                                 | Туре                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD                                                                                                 | l<br>A(L)                           | <b>HOLD</b> request input to signal that an external bus master wishes to gain control of the local bus. The M80C186EB will relinquish control of the local bus between instruction boundaries not conditioned by a LOCK prefix.                                                                                                                                                                                                        |

| HLDA                                                                                                 | O<br>H(1)<br>R(0)<br>P(0)           | <b>HoLD Acknowledge</b> output to indicate that the M80C186EB has relinquish control of the local bus. When HLDA is asserted, the M80C186EB will (or has) floated its data bus and control signals allowing another bus master to drive the signals directly.                                                                                                                                                                           |

| NCS                                                                                                  | O<br>H(1)<br>R(1)<br>P(1)           | Numerics Coprocessor Select output is generated when accessing a numerics coprocessor.                                                                                                                                                                                                                                                                                                                                                  |

| ERROR                                                                                                | l<br>A(L)                           | <b>ERROR</b> input that indicates the last numerics coprocessor operation resulted in an exception condition. An interrupt TYPE 16 is generated if ERROR is sampled active at the beginning of a numerics operation.                                                                                                                                                                                                                    |

| PEREQ                                                                                                | l<br>A(L)                           | <b>CoProcessor REQuest</b> signals that a data transfer between an External Numerics Coprocessor and Memory is pending.                                                                                                                                                                                                                                                                                                                 |

| UCS                                                                                                  | O<br>H(1)<br>R(1)<br>P(1)           | <b>Upper Chip Select</b> will go active whenever the address of a memory or I/O bus cycle is within the address limitations programmed by the user. After reset, UCS is configured to be active for memory accesses between 0FFC00H and 0FFFFFH.                                                                                                                                                                                        |

| ĪCS                                                                                                  | O<br>H(1)<br>R(1)<br>P(1)           | <b>Lower Chip Select</b> will go active whenever the address of a memory bus cycle is within the address limitations programmed by the user. LCS is inactive after a reset.                                                                                                                                                                                                                                                             |

| P1.0/GCS0<br>P1.1/GCS1<br>P1.2/GCS2<br>P1.3/GCS3<br>P1.4/GCS4<br>P1.5/GCS5<br>P1.6/GCS6<br>P1.7/GCS7 | O<br>H(X)/H(1)<br>R(1)<br>P(X)/P(1) | These pins provide a multiplexed function. If enabled, each pin can provide<br>a <b>Generic Chip Select</b> output which will go active whenever the address of<br>a memory or I/O bus cycle is within the address limitations programmed by<br>the user. When not programmed as a Chip-Select, each pin may be used as<br>a general purpose output <b>Port.</b> As an output port pin, the value of the pin<br>can be read internally. |

| T0OUT<br>T1OUT                                                                                       | O<br>H(Q)<br>R(1)<br>P(Q)           | <b>Timer OUTput</b> pins can be programmed to provide a single clock or continuous waveform generation, depending on the timer mode selected.                                                                                                                                                                                                                                                                                           |

| TOIN<br>T1IN                                                                                         | l<br>A(L)<br>A(E)                   | <b>Timer INput</b> is used either as clock or control signals, depending on the timer mode selected.                                                                                                                                                                                                                                                                                                                                    |

| Table 4. M80C186EB Pin Descri | ptions (Continued) |

|-------------------------------|--------------------|

|-------------------------------|--------------------|

| Name                     | Туре                                    | Description                                                                                                                                                                                                                                                                                               |

|--------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT0<br>INT1<br>INT4     | l<br>A(E,L)                             | Maskable <b>INTerrupt</b> input will cause a vector to a specific Type interrupt routine. To allow interrupt expansion, INT0 and/or INT1 can be used with INTA0 and INTA1 to interface with an external slave controller.                                                                                 |

| INT2/INTAO<br>INT3/INTA1 | I/O<br>A(E,L)<br>/H(1)<br>R(Z)<br>/P(1) | These pins provide a multiplexed function. As inputs, they provide a maskable <b>INTerrupt</b> that will cause the CPU to vector to a specific Type interrupt routine. As outputs, each is programmatically controlled to provide an INTERRUPT ACKNOWLEDGE handshake signal to allow interrupt expansion. |

| P2.7<br>P2.6             | I/O<br>A(L)<br>H(X)<br>R(Z)<br>P(X)     | Bidirectional, open-drain <b>Port</b> pins.                                                                                                                                                                                                                                                               |

| CTSO<br>P2.4/CTS1        | l<br>A(L)                               | <b>Clear-To-Send</b> input is used to prevent the transmission of serial data on their respective TXD signal pin. CTS1 is multiplexed with an input only port function.                                                                                                                                   |

| TXD0<br>P2.1/TXD1        | O<br>H(X)/H(Q)<br>R(1)<br>P(X)/P(Q)     | <b>Transmit Data</b> output provides serial data information. TXD1 is multiplexed with an output only <b>Port</b> function. During synchronous serial communications, TXD will function as a clock output.                                                                                                |

| RXD0<br>P2.0/RXD1        | I/O<br>A(L)<br>R(Z)<br>H(Q)<br>P(X)     | <b>Receive Data</b> input accepts serial data information. RXD1 is multiplexed with an input only <b>Port</b> function. During synchronous serial communications, RXD is bi-directional and will become an output for transmission or data (TXD becomes the clock).                                       |

| P2.5/BCLK0<br>P2.2/BCLK1 | l<br>A(L)/A(E)                          | <b>Baud CLocK</b> input can be used as an alternate clock source for each of the integrated serial channels. BCLKx is multiplexed with an input only <b>Port</b> function, and cannot exceed a clock rate greater than one-half the operating frequency of the M80C186EB.                                 |

| P2.3/SINT1               | O<br>H(X)/H(Q)<br>R(0)<br>P(X)/P(Q)     | <b>Serial INTerrupt</b> output will go active to indicate serial channel 1 requires service. SINT1 is multiplexed with an output only <b>Port</b> function.                                                                                                                                               |

### M80C186EB

### M80C186EB PINOUT

Table 5 lists the M80C186EB pin names with package location for the 88-Lead Pin Grid Array (PGA) component. Figure 8 depicts the complete M80C186EB pinout as viewed from the bottom side of the component.

| PLCC | PGA | Name            |

|------|-----|-----------------|------|-----|-----------------|------|-----|-----------------|------|-----|-----------------|

| 11   | 1A  | DEN             | 74   | 1M  | AD5             | -    | 12N | N/C             | _    | 13B | N/C             |

| 10   | 2B  | <del>S0</del>   | 73   | 1N  | AD12            | 53   | 13N | RXD0            | 32   | 13A | INT1            |

| 9    | 1B  | <del>S1</del>   | 72   | 2N  | AD4             | 52   | 13M | TXD0            | 31   | 12A | INT0            |

| 8    | 2C  | <del>S</del> 2  | 71   | ЗM  | AD11            | 51   | 12L | CTS0            | 30   | 11B | UCS             |

| 7    | 1C  | BHE             | 70   | ЗN  | AD3             | 50   | 13L | P2.6            | 29   | 11A | LCS             |

| 6    | 2D  | ALE             | 69   | 4M  | AD10            | 49   | 12K | P2.7            | 28   | 10B | P1.0/GCS0       |

| 5    | 1D  | WR              | 68   | 4N  | AD2             | 48   | 13K | T1IN            | 27   | 10A | P1.1/GCS1       |

| 4    | 2E  | RD              | 67   | 5M  | AD9             | 47   | 12J | T1OUT           | 26   | 9B  | P1.2/GCS2       |

| 3    | 1E  | ERROR           | 66   | 5N  | AD1             | 46   | 13J | TOIN            | 25   | 9A  | P1.3/GCS3       |

| 2    | 2F  | V <sub>SS</sub> | 65   | 6M  | V <sub>SS</sub> | 45   | 12H | TOOUT           | 24   | 8B  | P1.4/GCS4       |

| 1    | 1F  | V <sub>CC</sub> | 64   | 6N  | V <sub>CC</sub> | 44   | 13H | CLKOUT          | 23   | 8A  | V <sub>CC</sub> |

| 84   | 2G  | V <sub>SS</sub> | 63   | 7M  | V <sub>SS</sub> | 43   | 12G | V <sub>SS</sub> | 22   | 7B  | V <sub>SS</sub> |

| 83   | 1G  | A19/ONCE        | _    | 7N  | N/C             | 42   | 13G | V <sub>CC</sub> | 21   | 7A  | P1.5/GCS5       |

| 82   | 2H  | A18             | 62   | 8M  | AD8             | 41   | 12F | CLKIN           | 20   | 6B  | P1.6/GCS6       |

| 81   | 1H  | A17             | 61   | 8N  | AD0             | 40   | 13F | OSCOUT          | 19   | 6A  | P1.7/GCS7       |

| 80   | 2J  | A16             | 60   | 9M  | NCS             | 39   | 12E | PEREQ           | 18   | 5B  | READY           |

| 79   | 1J  | AD15            | 59   | 9N  | P2.2/BCLK1      | 38   | 13E | RESOUT          | 17   | 5A  | NMI             |

| 78   | 2K  | AD7             | 58   | 10M | P2.1/TXD1       | 37   | 12D | RESIN           | 16   | 4B  | DRT/R           |

| 77   | 1K  | AD14            | 57   | 10N | P2.0/RXD1       | 36   | 13D | PDTMR           | 15   | 4A  | LOCK            |

| 76   | 2L  | AD6             | 56   | 11M | P2.4/CTS1       | 35   | 12C | INT4            | 14   | 3B  | TEST/BUSY       |

| 75   | 1L  | AD13            | 55   | 11N | P2.3/SINT1      | 34   | 13C | INT3            | 13   | ЗA  | HOLD            |

| _    | 2M  | N/C             | 54   | 12M | P2.5/BLCK0      | 33   | 12B | INT2            | 12   | 2A  | HLDA            |

### Table 5. MG80C186EB Pin Assignments

Figure 8

### ELECTRICAL SPECIFICATIONS

### **Absolute Maximum Ratings**

| Parameter                                                   | Maximum Rating        |

|-------------------------------------------------------------|-----------------------|

| Storage Temperature                                         | -65°C to +150°C       |

| Case Temp Under Bias                                        | -55°C to +125°C       |

| Supply Voltage with respect to V <sub>SS</sub>              | 0.5V to +6.5V         |

| Voltage on other Pins<br>with respect to V <sub>SS</sub> 0. | 5V to $V_{CC}$ + 0.5V |

NOTICE: This data sheet contains information on products in the sampling and initial production phases of development. It is valid for the devices indicated in the revision history. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### **OPERATING CONDITIONS**

| Symbol          | Parameter                                             | Min | Max         | Units |

|-----------------|-------------------------------------------------------|-----|-------------|-------|

| V <sub>CC</sub> | Supply Voltage                                        | 4.5 | 5.5         | V     |

| Τ <sub>F</sub>  | Input Clock Frequency<br>M80C186EB-16<br>M80C186EB-13 | 0   | 32<br>26.08 | MHz   |

| T <sub>C</sub>  | M80C186EB-8<br>Case Temperature Under Bias            | 0   | 16<br>+ 125 | °C    |

### **RECOMMENDED CONNECTIONS**