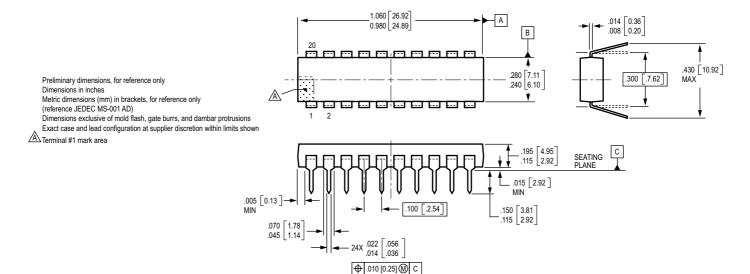

#### Package A, 20-pin DIP

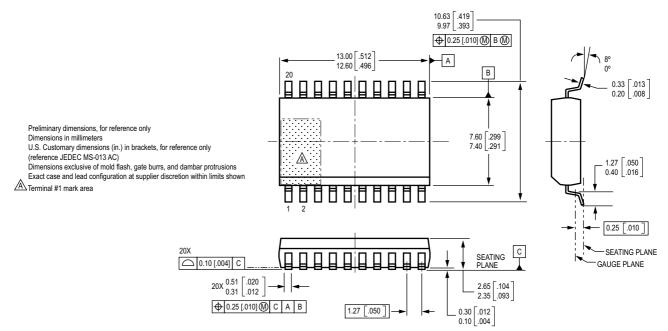

Package LW, 20-pin SOIC-W

#### **Features**

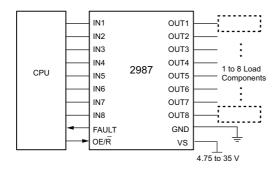

- 4.75 to 35 V driver supply voltage

- Output enable-disable (OE/R)

- 350 mA output source current

- Overcurrent protected

- Internal ground clamp diodes

- Output Breakdown Voltage 35 V minimum

- TTL, DTL, PMOS, or CMOS compatible inputs

- Internal Thermal Shut Down (TSD)

#### **Applications**

- Relavs

- Motors

- Solenoids

- LEDs

- Incandescent lamps

### **Typical Application**

## UDN2987x-6

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

Providing overcurrent protection for each of its eight sourcing outputs, the UDN2987A-6 and UDN2987LW-6 drivers are used as an interface between standard low-level logic and relays, motors, solenoids, LEDs, and incandescent lamps. These devices include thermal shut down and output transient protection/clamp diodes for use with sustaining voltages to 35 V.

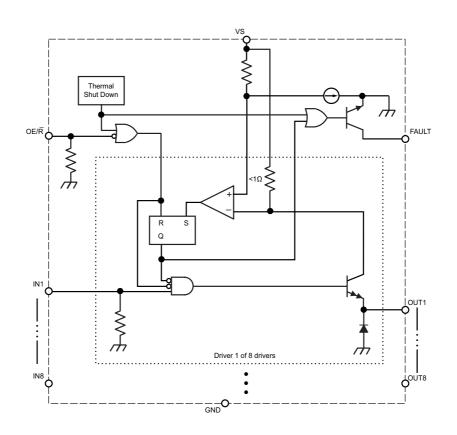

In these drivers, each channel includes a latch to turn off that channel if the maximum channel current is exceeded. All channels are disabled if the thermal shutdown is activated. A common FAULT output is used to indicate either chip thermal shutdown or any overcurrent condition. All outputs are enabled by pulling the common OE/R input high. When OE/ $\overline{R}$  is low, all outputs are inhibited and the eight latches are reset. The OE/ $\overline{R}$  function can be especially important during power-up, in preventing floating inputs from turning on the outputs.

Under normal operating conditions, each of eight outputs will source in excess of 100 mA continuously at an ambient temperature of 25°C and a supply of 35 V. The over-current fault circuit will protect the device from short-circuits to ground with supply voltages of up to 30 V.

The inputs are compatible with 5 and 12 V logic systems: TTL, Schottky TTL, DTL, PMOS, and CMOS. In all cases, the output is switched ON by an active high input level. Compared to their predecessor devices, the UDN2987A and UDN2987LW, the UDN2987A-6 and UDN2987LW-6 have a significantly faster  $T_{PHL}$  (200 ns typical) and a lower driver supply voltage rating (4.75 V), which allows the use of 5 V logic.

The UDN2987A-6 is supplied in a 20-pin dual in-line plastic (DIP) package; the UDN2987LW-6 is supplied in a 20-lead small-outline (SOIC-W) plastic package. The Pb (lead) free versions have 100% matte-tin leadframe plating.

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

### Selection Guide

| Part Number     | Pb-free* | Packing                 | Package                |

|-----------------|----------|-------------------------|------------------------|

| UDN2987A-6-T    | Yes      | 18 pieces/tube          | 20-pin DIP             |

| UDN2987LW-6-T   | Yes      | 37 pieces/tube          | 20 pin COIC wide hady  |

| UDN2987LWTR-6-T | Yes      | 1000 pieces/13-in. reel | 20-pin SOIC, wide body |

<sup>\*</sup>Pb-based variants are being phased out of the product line. The variants cited in this footnote are in production but have been determined to be LAST TIME BUY. This classification indicates that sale of this device is currently restricted to existing customer applications. The variants should not be purchased for new design applications because obsolescence in the near future is probable. Samples are no longer available. Status change: October 31, 2006. Deadline for receipt fo LAST TIME BUY orders: April 27, 2007. These variants include: UDN2987A-6, UDN2987LW-6, and UDN2987LWTR-6.

### **Absolute Maximum Ratings**

| Parameter                   | Symbol           | Conditions                                    | Min. | Max. | Units |

|-----------------------------|------------------|-----------------------------------------------|------|------|-------|

| Supply Voltage              | V <sub>S</sub>   |                                               | _    | 35   | V     |

| Continuous Output Current*  | I <sub>OUT</sub> | Outputs are disabled at approximately –500 mA | -500 | _    | mA    |

| FAULT Output Voltage        | V <sub>CE</sub>  |                                               | _    | 35   | V     |

| FAULT Output Current        | I <sub>C</sub>   |                                               | _    | 30   | mA    |

| Input Voltage               | V <sub>IN</sub>  |                                               | -0.3 | 14   | ٧     |

| Junction Temperature        | T <sub>J</sub>   |                                               | _    | 150  | °C    |

| Storage Temperature Range   | T <sub>S</sub>   |                                               | -55  | 150  | °C    |

| Operating Temperature Range | T <sub>A</sub>   |                                               | -20  | 85   | °C    |

<sup>\*</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

## Functional Block Diagram

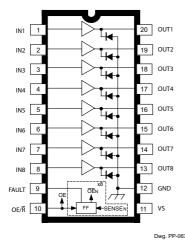

## Pin-Out Diagram

Package A (DIP) shown. Package LW (SOIC-W) is electrically identical and has the same terminal number assignment.

#### **Terminal List Table**

| Number | Name  | Description                             |  |  |

|--------|-------|-----------------------------------------|--|--|

| 1      | IN1   | Logic input 1                           |  |  |

| 2      | IN2   | Logic input 2                           |  |  |

| 3      | IN3   | Logic input 3                           |  |  |

| 4      | IN4   | Logic input 4                           |  |  |

| 5      | IN5   | Logic input 5                           |  |  |

| 6      | IN6   | Logic input 6                           |  |  |

| 7      | IN7   | Logic input 7                           |  |  |

| 8      | IN8   | Logic input 8                           |  |  |

| 9      | FAULT | Fault output                            |  |  |

| 10     | OE/R  | Logic input for Output Enable and Reset |  |  |

| 11     | VS    | Supply voltage                          |  |  |

| 12     | GND   | Supply ground                           |  |  |

| 13     | OUT8  | Output 8 to load                        |  |  |

| 14     | OUT7  | Output 7 to load                        |  |  |

| 15     | OUT6  | Output 6 to load                        |  |  |

| 16     | OUT5  | Output 5 to load                        |  |  |

| 17     | OUT4  | Output 4 to load                        |  |  |

| 18     | OUT3  | Output 3 to load                        |  |  |

| 19     | OUT2  | Output 2 to load                        |  |  |

| 20     | OUT1  | Output 1 to load                        |  |  |

## DABIC-5 8-Channel Source Driver with Overcurrent Protection

### ELECTRICAL CHARACTERISTICS, valid at $T_A = 25$ °C, $V_{OER} = 2.4$ V, $V_S = 35$ V, unless otherwise noted

| Characteristic                           | Symbol                | Test Conditions                                                  | Min. | Typ.1 | Max. | Units |

|------------------------------------------|-----------------------|------------------------------------------------------------------|------|-------|------|-------|

| Supply Voltage Functional Range          | V <sub>S</sub>        |                                                                  | 4.75 | _     | 35   | V     |

| Output Leakage Current <sup>2</sup>      | I <sub>OUTCEX</sub>   | V <sub>IN</sub> = 0.4 V, all inputs simultaneously               | -200 | <-5.0 | _    | μA    |

| Output Sustaining Voltage                | V <sub>OUT(sus)</sub> | I <sub>OUT</sub> = –350 mA, L = 2.0 mH                           | 35   | _     | _    | V     |

| Output Saturation Voltage                |                       | V <sub>IN</sub> = 2.4 V, I <sub>OUT</sub> = -100 mA              | _    | 1.6   | 1.8  | V     |

|                                          | V <sub>OUT(SAT)</sub> | V <sub>IN</sub> = 2.4 V, I <sub>OUT</sub> = -225 mA              | _    | 1.7   | 1.9  | V     |

|                                          |                       | V <sub>IN</sub> = 2.4 V, I <sub>OUT</sub> = -350 mA              | _    | 1.8   | 2.0  | V     |

| Channel Shut Down Threshold <sup>2</sup> | I <sub>M</sub>        | V <sub>IN</sub> = 2.4 V, V <sub>s</sub> = 30 V                   | _    | -500  | -370 | mA    |

| FAULT Leakage Current                    | I <sub>CEX</sub>      | V <sub>CC</sub> = 35 V                                           | _    | <1.0  | 100  | μA    |

| FAULT Saturation Voltage                 | V <sub>CE(SAT)</sub>  | I <sub>C</sub> = 30 mA                                           | _    | 0.3   | 0.8  | V     |

| Input Voltage                            | V <sub>IN(ON)</sub>   |                                                                  | 2.4  | _     | _    | V     |

|                                          | V <sub>IN(OFF)</sub>  |                                                                  | _    | _     | 0.4  | V     |

| Input Current: INx, OE/R pins            |                       | V <sub>IN</sub> = 2.4 V                                          | _    | _     | 100  | μA    |

|                                          | I <sub>IN(ON)</sub>   | V <sub>IN</sub> = 5.0 V                                          | _    | _     | 600  | μA    |

|                                          |                       | V <sub>IN</sub> = 12 V                                           | _    | _     | 1000 | μA    |

|                                          | I <sub>IN(OFF)</sub>  | V <sub>IN</sub> = 0.4 V                                          | _    | _     | 15   | μA    |

| Clamp Diode Leakage Current              | I <sub>R</sub>        | V <sub>R</sub> = 35 V, T <sub>A</sub> = 70°C                     | _    | _     | 50   | μA    |

| Clamp Diode Forward Voltage              | V <sub>F</sub>        | I <sub>F</sub> = 350 mA                                          | _    | 1.5   | 1.8  | V     |

| Supply Current                           | I <sub>S(ON)</sub>    | V <sub>IN</sub> = 2.4 V, all inputs simultaneously; outputs open | _    | 7.0   | 18   | mA    |

| Supply Current                           | I <sub>S(OFF)</sub>   | V <sub>IN</sub> = 0.4 V, all inputs simultaneously               | _    | 6.0   | 12   | mA    |

| Thermal Shut Down                        | T <sub>JTSD</sub>     |                                                                  | _    | 165   | _    | °C    |

| Thermal Hysteresis                       | T <sub>JTSDhys</sub>  |                                                                  | _    | 15    | _    | °C    |

| Reset Pulse Duration                     | t <sub>RPD</sub>      |                                                                  | 1.0  | _     | _    | μs    |

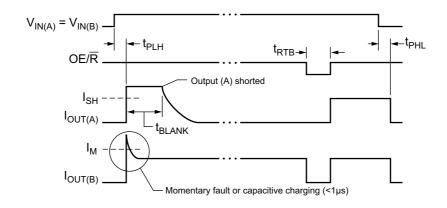

|                                          | t <sub>PLH</sub>      | $V_S = 35 \text{ V}, R_L = 100 \Omega, C_{LOAD} = 30 \text{ pF}$ | _    | 100   | 600  | ns    |

| Propagation Delay Time                   | t <sub>PHL</sub>      | $V_S = 35 \text{ V}, R_L = 100 \Omega, C_{LOAD} = 30 \text{ pF}$ | _    | 200   | 1000 | ns    |

| Blank Time                               | t <sub>BLANK</sub>    |                                                                  | _    | 1.0   | _    | μs    |

<sup>&</sup>lt;sup>1</sup>Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

<sup>&</sup>lt;sup>2</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

## DABIC-5 8-Channel Source Driver with Overcurrent Protection

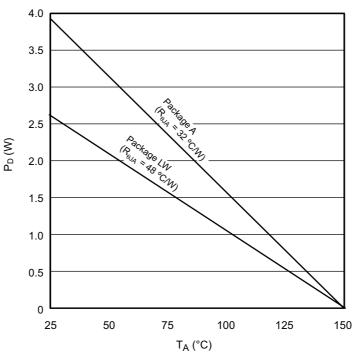

#### THERMAL CHARACTERISTICS

| Characteristics             | Symbol          | Test Conditions                                      | Rating | Unit |

|-----------------------------|-----------------|------------------------------------------------------|--------|------|

| Dackage Thermal Desigtence* | $R_{\theta JA}$ | Package A, on 4-layer board based on JEDEC standard  | 32     | °C/W |

| Package Thermal Resistance* |                 | Package LW, on 4-layer board based on JEDEC standard | 48     | °C/W |

<sup>\*</sup>Additional thermal information is available on the Allegro Web site.

#### **Power Dissipation versus Ambient Temperature**

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

#### Characteristic Performance

### **Output Current Waveshapes**

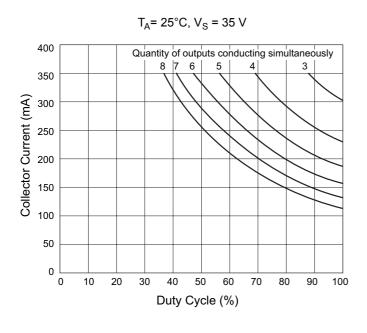

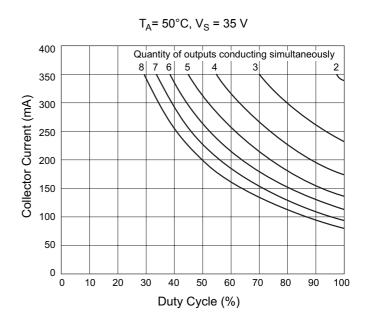

### **Allowable Output Current as a Function of Duty Cycle**

(UDN2987A-6 shown, multiply by 78% for UDN2987LW-6)

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

### Applications Information and Circuit Description

As with all power integrated circuits, the UDN2987A-6 and UDN2987LW-6 have a maximum allowable output current rating. The 500 mA rating does not imply that operation at that value is permitted or even obtainable. The channel output current trip point is specified as –370 mA, minimum; therefore, attempted operation at current levels greater than –370 mA may cause a fault indication and channel shut down. The device is tested at a maximum of –350 mA and that is the recommended maximum output current per driver. It provides protection for current overloads or shorted loads up to 30 V.

All outputs are enabled by pulling the  $OE/\overline{R}$  input high. When  $OE/\overline{R}$  is low or allowed to float (internal pull-down), all outputs are inhibited and the latches are reset. Note that the reset pulse duration ( $OE/\overline{R}$  low) should be at least 1  $\mu$ s. This will ensure safe operation under attempted reset conditions with a shorted load. The latches are also reset during power-up, regardless of the state of the  $OE/\overline{R}$  input.

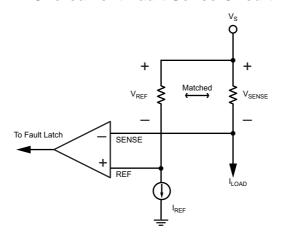

The load current causes a small voltage drop across the internal low-value sense resistor. This voltage is com-

pared to the voltage drop across a reference resistor with a constant current. The two resistors are matched to eliminate errors due to manufacturing tolerances or temperature effects. Each channel includes a comparator and its own latch. An overcurrent fault ( $V_{\rm SENSE} > V_{\rm REF}$ ) will set the affected latch and shut down only that channel. All other channels will continue to operate normally. The latch includes a 1  $\mu$ s blanking delay,  $t_{\rm BLANK}$ , to prevent unwanted triggering due to crossover currents generated when switching inductive loads. For an abrupt short circuit, the blanking and output switching times will allow a brief, permissable current in excess of the trip current before the output driver is turned off.

A common thermal shut down disables all outputs if the chip temperature exceeds 165°C. At thermal shut down, all latches are reset. The outputs are disabled until the chip cools down to approximately 150°C (thermal hysteresis).

In the event of an overcurrent condition on any channel, or chip thermal shut down, the FAULT open-collector output is pulled low (turned on).

#### **Overcurrent Fault Sense Circuit**

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

## Package A, 20-Pin DIP

## Package LW, 20-pin SOIC-W

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283; 5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719; 5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copyright©2006, Allegro MicroSystems, Inc.