## **Product Specification**

# AHA4525

## IEEE 802.16a Compliant Turbo Product Code Encoder/Decoder

This product is covered under multiple patents held or licensed by Comtech AHA Corporation.

This product is covered by a Turbo Code Patent License from France Telecom - TDF - Groupe des ecoles des telecommunications.

PS4525\_0204

A subsidiary of Comtech Telecommunications Corporation

## Table of Contents

| 1.0 | Intro | oduction                                                           |     |

|-----|-------|--------------------------------------------------------------------|-----|

|     | 1.1   | Features                                                           | . 1 |

|     | 1.2   | Glossary of Terms                                                  |     |

|     | 1.3   | Document Conventions                                               |     |

| 2.0 | Data  | a and Configuration Input/Output                                   | .3  |

|     | 2.1   | Configuration Writes                                               |     |

|     | 2.2   | Configuration Reads                                                | .4  |

|     | 2.3   | Configuration Cycle Format                                         | .5  |

|     | 2.4   | Decoder Status Output                                              |     |

|     | 2.5   | Decoder Status Output Format                                       |     |

|     | 2.6   | Encoder and Decoder - Synchronous I/O - Full Duplex                | .6  |

|     | 2.7   | Encoder and Decoder Synchronous - Half Duplex                      | .9  |

|     | 2.8   | Bus Mode - Half Duplex                                             |     |

|     | 2.9   | Decoder Bus Interface, Encoder Synchronous Interface - Full Duplex | 13  |

| 3.0 | Enc   | oder                                                               | 14  |

|     | 3.1   | CRC Encoder                                                        | 14  |

|     | 3.2   | Scrambler                                                          | 15  |

|     | 3.3   | TPC Encoder                                                        | 16  |

|     |       | 3.3.1 Encoder Code Shortening                                      | 16  |

|     |       | 3.3.2 Helical Interleaver                                          | 16  |

|     |       | 3.3.3 Internal Buffering                                           | 17  |

|     |       | 3.3.4 Encoder Latency                                              | 17  |

| 4.0 | Dec   | oder                                                               | 18  |

|     | 4.1   | Channel Interface                                                  |     |

|     |       | 4.1.1 Channel Input Formatting                                     |     |

|     | 4.2   | TPC Decoder                                                        |     |

|     |       | 4.2.1 Helical Deinterleaver                                        |     |

|     |       | 4.2.2 Code Configuration                                           |     |

|     |       | 4.2.3 Decoder Code Shortening                                      |     |

|     |       | 4.2.4 Corrections Count                                            |     |

|     |       | 4.2.5 Descrambler                                                  |     |

|     |       | 4.2.6 CRC Checking                                                 |     |

|     |       | 4.2.7 Decoder Latency                                              |     |

|     |       | 4.2.8 Code Performance                                             |     |

| 5.0 |       | se Lock Loop                                                       |     |

| 6.0 |       | eral Output Signals                                                |     |

| 7.0 | Reg   | ister Descriptions                                                 |     |

|     | 7.1   | Configuration Sequence                                             |     |

|     | 7.2   | Register List                                                      |     |

|     | 7.3   | User Data Formatting Registers                                     |     |

|     |       | 7.3.1 CRC and Scrambler Configuration                              |     |

|     | 7.4   | Code Configuration Registers                                       |     |

|     |       | 7.4.1 TPC Constituent Code                                         |     |

|     |       | 7.4.2 Block Size                                                   |     |

|     |       | 7.4.3 Buffer Configuration (Encoder Only)                          |     |

|     |       | 7.4.4 Shortening Configuration                                     |     |

|     |       | 7.4.5 Feedback (Decoder Only)                                      |     |

|     | 75    | 7.4.6 Iterations (Decoder Only)                                    |     |

|     | 7.5   | Channel Interface Registers                                        |     |

|     |       | 7.5.1 Quantization (Decouer Only)                                  | ונ  |

A subsidiary of Comtech Telecommunications Corporation

i

|      | 7.6   | Data Input/Output Configuration                  |   |

|------|-------|--------------------------------------------------|---|

|      |       | 7.6.1 Transfer Word Size                         | 1 |

|      | 7.7   | Control and Status                               | 2 |

|      |       | 7.7.1 Control                                    |   |

|      |       | 7.7.2 Status and Correction Count (Decoder Only) |   |

|      |       | 7.7.3 Actual Iterations (Decoder Only)           |   |

|      | 7.8   | Miscellaneous                                    |   |

|      |       | 7.8.1 Version                                    | 3 |

| 8.0  | Sigr  | nal Descriptions                                 |   |

|      | 8.1   | System Control and Miscellaneous                 |   |

|      | 8.2   | Unencoded Data Interface                         |   |

|      | 8.3   | Encoded Data Interface                           |   |

|      | 8.4   | Channel Data Interface                           |   |

|      | 8.5   | Decoded Data Interface                           |   |

| 9.0  | Pinc  | out                                              | 7 |

| 10.0 | DC    | Electrical Specifications                        | 8 |

|      | 10.1  | Operating Conditions                             | 8 |

|      | 10.2  | ? Absolute Maximum Stress Ratings                | 8 |

|      |       | 3 Test Conditions                                |   |

| 11.0 | AC    | Electrical Specifications                        | 0 |

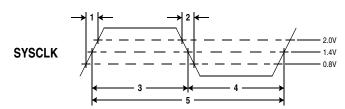

|      |       | SYSCLK Clock Timing                              |   |

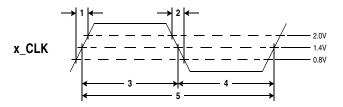

|      | 11.2  | 2 U_CLK, E_CLK, C_CLK, D_CLK Clock Timing4       | 1 |

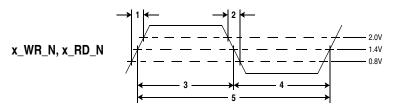

|      |       | 3 U_WR_N, E_RD_N, C_WR_N, D_RD_N Strobe Timing4  |   |

|      |       | Synchronous Data Interface                       |   |

|      |       | Bus Interface                                    |   |

|      |       | Reset_n Timing                                   |   |

| 12.0 |       | kage Specifications                              |   |

|      | 12.1  | Package Dimensions                               | 2 |

| 13.0 | Ord   | ering Information                                | 3 |

|      |       | Available Parts                                  |   |

|      | 13.2  | Part Numbering                                   | 3 |

| 14.0 | Rela  | ated Technical Publications                      | 4 |

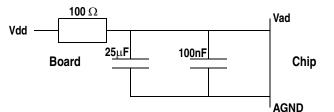

| Арр  | endix | x A: Vad Recommendations                         | 5 |

m

10

- N. I.

ii

# List of Figures

| Figure 1:  | Pinout                                                                 | 1  |

|------------|------------------------------------------------------------------------|----|

| Figure 2:  | AHA4525 Functional Block Diagram                                       | 2  |

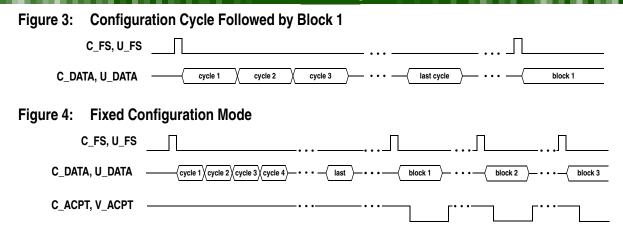

| Figure 3:  | Configuration Cycle Followed by Block 1                                | 4  |

| Figure 4:  | Fixed Configuration Mode                                               | 4  |

| Figure 5:  | Configuration Example for Gaps Between Configuration Writes            | 4  |

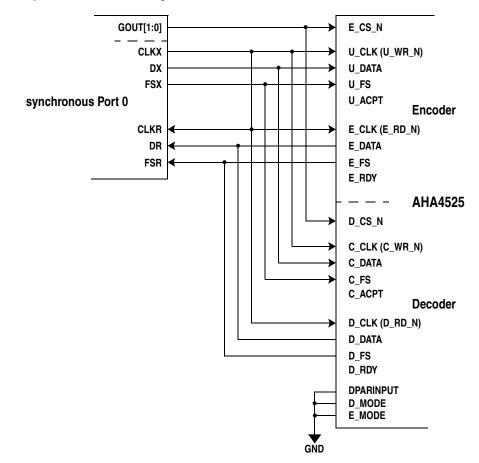

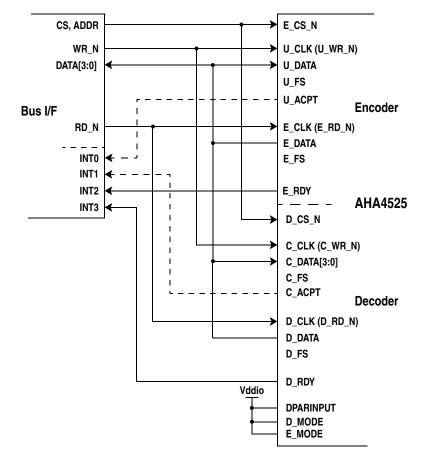

| Figure 6:  | Full Duplex Connection Diagram                                         |    |

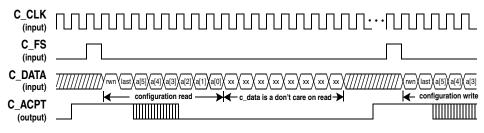

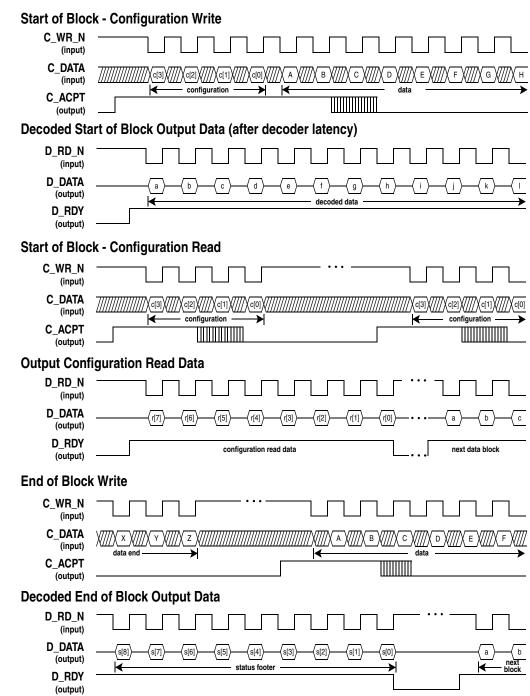

| Figure 7:  | Synchronous Data/Configuration Communication Timing - Start of Block   | 8  |

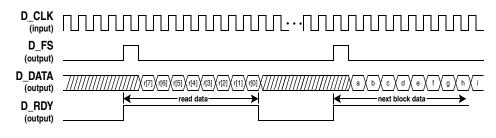

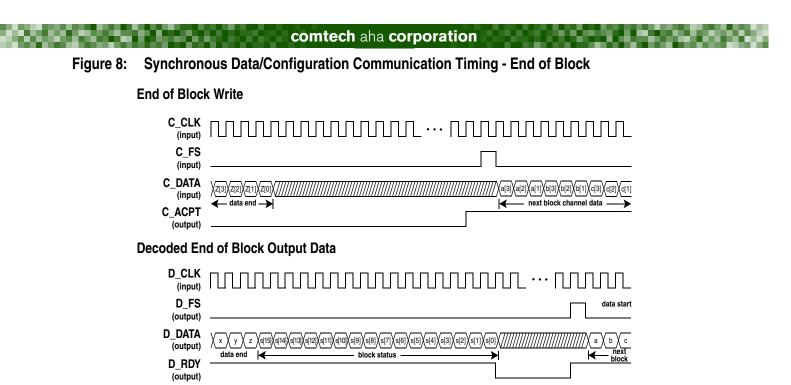

| Figure 8:  | Synchronous Data/Configuration Communication Timing - End of Block     | 9  |

| Figure 9:  | Half Duplex Connection Diagram                                         | 9  |

| Figure 10: | Half Duplex Connection Diagram                                         | 10 |

| Figure 11: | Bus Interface Data/Configuration Communication Timing - Start of Block | 12 |

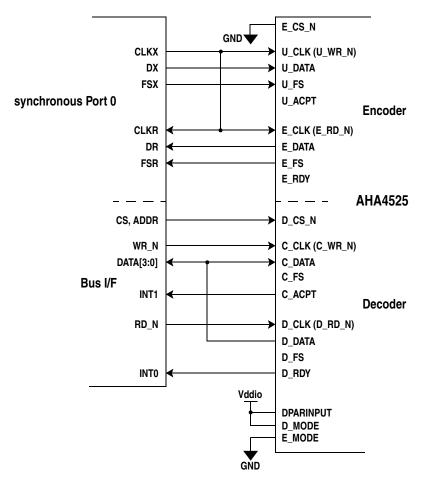

| Figure 12: | Full Duplex Connection Diagram                                         |    |

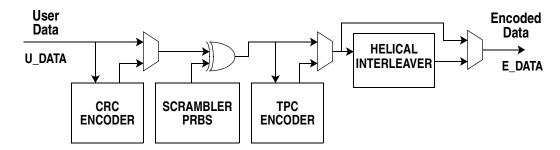

| Figure 13: | Encoder Block Diagram                                                  | 14 |

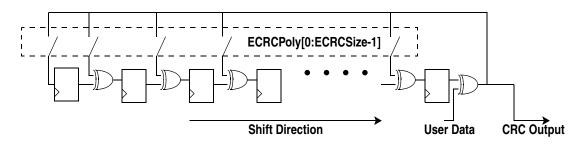

| Figure 14: | CRC Encoder                                                            | 14 |

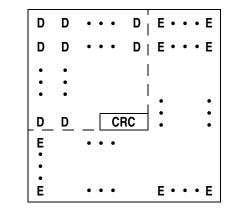

| Figure 15: | 2D TPC Encoded Block with CRC                                          | 15 |

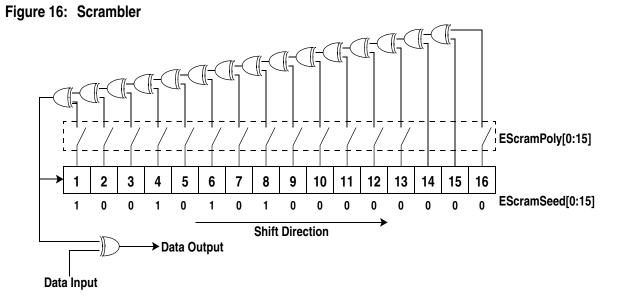

| Figure 16: | Scrambler                                                              | 15 |

| Figure 17: | Structure of Shortened Code                                            | 16 |

| Figure 18: | Input Block                                                            | 17 |

| Figure 19: | 2D Interleaving                                                        | 17 |

| Figure 20: | Encoded/Interleaved Data Output                                        | 17 |

| Figure 21: | C_DATA Interface                                                       | 18 |

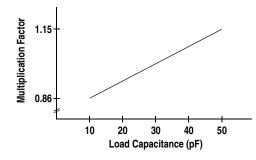

| Figure 22: | Signal Timing vs. Output Load                                          | 39 |

| Figure 23: | SYSCLK Clock Timing                                                    | 40 |

| Figure 24: | Clock Timing                                                           | 41 |

| Figure 25: | Strobe Timing                                                          | 41 |

| Figure 26: | Encoder Interface Data Input Timing                                    | 42 |

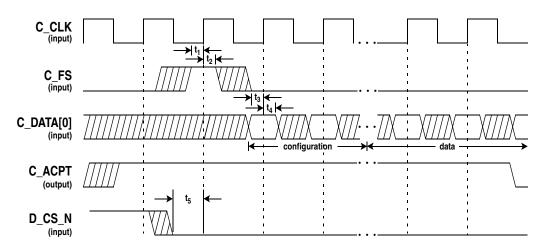

| Figure 27: | Decoder Interface Data Input Timing                                    | 43 |

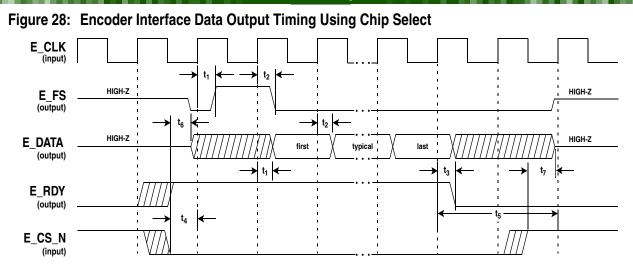

| Figure 28: | Encoder Interface Data Output Timing Using Chip Select                 | 44 |

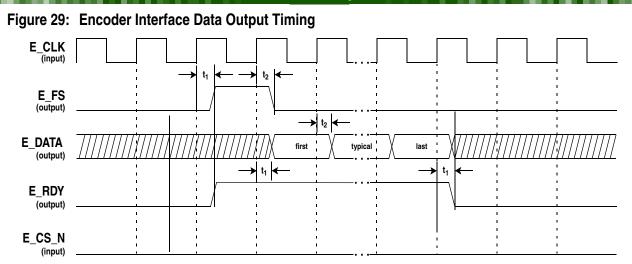

| Figure 29: | Encoder Interface Data Output Timing                                   |    |

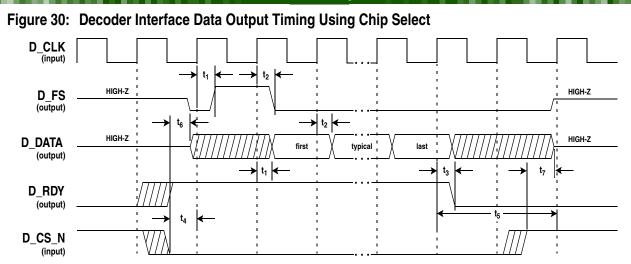

| Figure 30: | Decoder Interface Data Output Timing Using Chip Select                 | 46 |

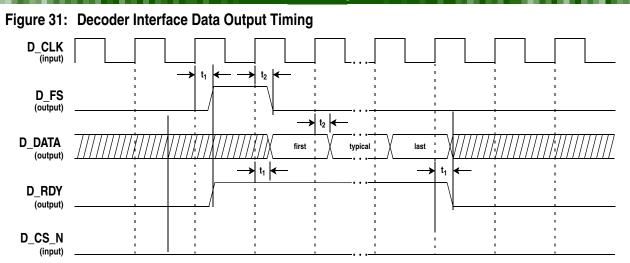

| Figure 31: | Decoder Interface Data Output Timing                                   | 47 |

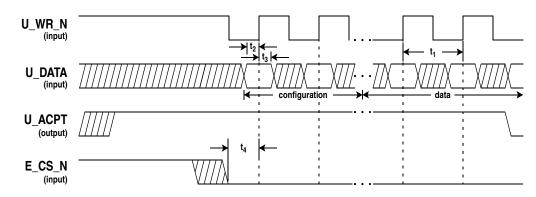

| Figure 32: | Encoder Bus Interface Data Input Timing                                | 48 |

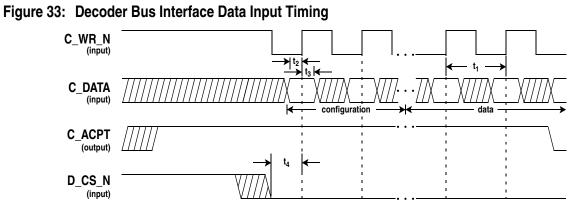

| Figure 33: | Decoder Bus Interface Data Input Timing                                | 49 |

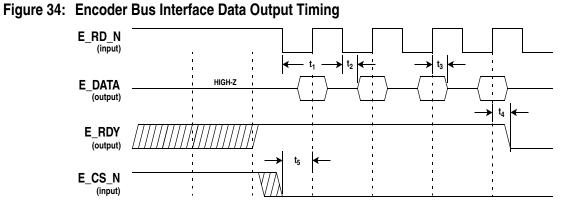

| Figure 34: | Encoder Bus Interface Data Output Timing                               | 50 |

| Figure 35: | Decoder Bus Interface Data Output Timing                               | 50 |

| Figure 36: | RESET_N Timing                                                         |    |

| Figure 37: | Package Dimensions - Top View                                          | 52 |

| Figure 38: | Package Dimensions - Cross Section View                                |    |

| Figure A1: | Example External Circuit Component Configuration                       | 55 |

## List of Tables

| Table 1:  | Recommended CRC Polynomials                               | 15 |

|-----------|-----------------------------------------------------------|----|

| Table 2:  | Partial Code List and Decoder Datapath Latency            | 21 |

| Table 3:  | Partial Code List and Performance - Synchronous Interface | 21 |

| Table 4:  | Partial Code List and Performance - Bus Interface         |    |

| Table 5:  | Register Bits - Alphabetical                              | 23 |

| Table 6:  | Summary of Code Shortening Rules                          | 29 |

| Table 7:  | Pinout - Pin Number Order                                 | 37 |

| Table 8:  | SYSCLK Clock Timing with PLLBYPASS = 0                    |    |

| Table 9:  | SYSCLK Clock Timing with PLLBYPASS = 1                    | 40 |

| Table 10: | Clock Timing                                              | 41 |

| Table 11: | Clock Timing<br>Strobe Timing with PLLBYPASS = 0          | 41 |

| Table 12: | Encoder Interface Data Input Timing                       | 42 |

| Table 13: | Decoder Interface Data Input Timing                       | 43 |

|           | Encoder Interface Data Output Timing Using Chip Select    |    |

| Table 15: | Encoder Interface Data Output Timing                      | 45 |

| Table 16: | Decoder Interface Data Output Timing Using Chip Select    | 46 |

|           | Decoder Interface Data Output Timing                      |    |

| Table 18: | Encoder Bus Interface Data Input Timing                   | 48 |

| Table 19: | Decoder Bus Interface Data Input Timing                   | 49 |

| Table 20: | Encoder Bus Interface Data Output Timing                  | 50 |

| Table 21: | Decoder Bus Interface Data Output Timing                  | 50 |

|           | RESET_N Timing                                            |    |

| Table 23: | TQFP (Thin Quad Flat Pack) 7 x 7 mm Package Dimensions    | 53 |

## 1.0 INTRODUCTION

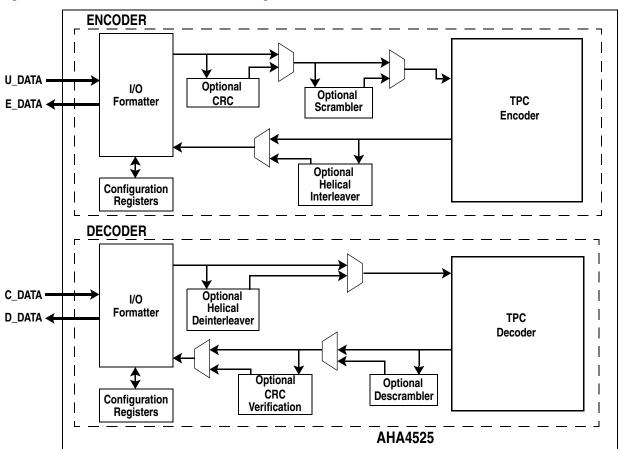

The AHA4525 device is a single-chip Turbo Product Code (TPC) Forward Error Correction (FEC) Encoder/Decoder. This device integrates independent TPC encoder and decoder functions, and can be configured for full or half duplex operation.

The encoder and decoder accept data and configuration through a synchronous 3-wire DSP type interface or asynchronous data bus.

Encoder and decoder configuration registers are written and read through the same interface as the data. Configuration registers are accessible after a reset and before the chip is enabled for data transfers.

The encode datapath, after configuration for any of the IEEE 802.16a BTC coding options, inputs data on UDATA, calculates and inserts error correction code (ECC) bits, and outputs the data on the EDATA interface. The decoder datapath is the reverse of the encoder datapath. The received data is input either serially or one soft metric per transfer at the CDATA interface, decoded with ECC bits removed, then output in a serial bit stream on the DDATA bus.

The Input/Output data interfaces each have a separate clock input. This coupled with an on-chip PLL for the 4x internal system clock allow flexibility in the system and lower on-board clock frequencies. This device implements the same code shortening schemes defined in the IEEE 802.16a standard. Removing X axis rows, Y axis columns, and bits from the beginning of the original message are easily programmed configuration register parameters.

## 1.1 FEATURES

#### PERFORMANCE:

- 60 Mbit/sec channel rate and 50 Mbit/sec payload data rate for (64,57)x(64,57) code with 3 iterations

- Supports all IEEE 802.16a BTC code configurations

#### FLEXIBILITY:

- Code rates from 0.25 to 0.97

- Encoded block sizes from 64 bits to 4K bits

- Programmable code shortening supports exact block sizes

- Programmable decoder input quantization for up to 4 bit wide soft metrics

- · Programmable iterations up to 255 per block

- On chip PLL allows low frequency system clock

#### CHANNEL INTERFACE:

- Synchronous 3-wire input and output ports designed to be compatible with DSP serial ports

- Bus mode input and output ports designed to be compatible with a DSP bus

- Chip selects on encoder and decoder ports for full or half-duplex operation

- Pin selectable interface control signal polarity

- Decoder supports up to 4 bit parallel soft metric input data for fast decode operation

#### SYSTEM INTERFACE:

• Configuration registers are accessed through the data ports

#### ELECTRICAL:

- 3.3V I/O, 1.8V core operation

- 5V tolerant inputs

- TTL signal compatible

- 64 pin TQFP Package

- Commercial or Industrial temperature rating

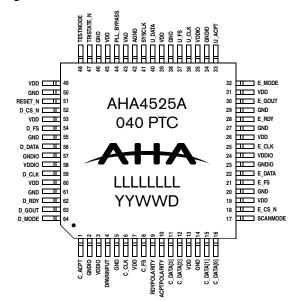

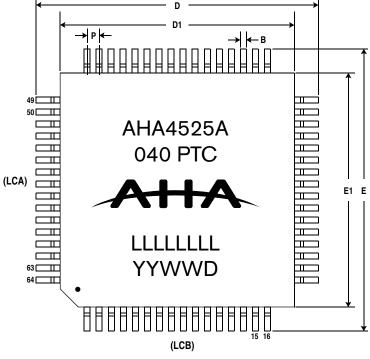

#### Figure 1: Pinout

Note: YYWWD = Date Code; LLLLLLL = Lot Number

## 1.2 GLOSSARY OF TERMS

#### Block (TPC) -

A TPC error correction block, including user data bits, CRC bits, and TPC error correction bits.

#### **Channel Rate -**

The bit rate output from the encoder, or input to the decoder, including all user data bits, CRC bits, and TPC error correction bits.

#### Data Rate -

The bit rate input to the encoder, or output from the decoder, including only user data bits. This is sometimes referred to as the payload data rate.

## 1.3 DOCUMENT CONVENTIONS

The following are formatting examples for specific document elements.

- SIGNAL OR PINS Electrical connections available to the system.

- Register Bit Bit(s) within a register. When the same register exists in both the encoder and decoder, an 'x' is used to designate both register bits, as in ECRCEnable and DCRCEnable.

- Hex values are represented with a prefix of "0x," such as Register "0x00." Binary values are represented with a prefix of "0b".

- Active low signals have "\_N" appended to the signal name, as in **E\_RD\_N**.

- Signals labelled "= 1" are tied to Vddio. Signals labelled "= 0" are tied to ground.

- "configuration header or footer bit" -Configuration header control bits are listed in quotes, as in "last" or "rwn".

#### Figure 2: AHA4525 Functional Block Diagram

## 2.0 DATA AND CONFIGURATION INPUT/OUTPUT

The input/output ports of the AHA4525 chip may be configured to operate in synchronous mode or bus mode. Synchronous mode signals consist of a continuous port clock, a frame sync signal, and data. Bus mode signals consist of a read or write strobe and data.

Bus mode is selected for the encoder when pin  $E_MODE = 1$  on the rising edge of  $RESET_N$ , and is selected for the decoder when pin  $D_MODE = 1$ on the rising edge of  $RESET_N$ . Synchronous mode is selected for the encoder when pin  $E_MODE = 0$  and for the decoder when pin  $D_MODE = 0$ .

The interface modes are independent. The encoder is not required to use the same interface mode as the decoder. The input port cannot be configured to use a different mode than the output port within the encoder or decoder.

The interfaces into and out of the encoder and out of the decoder are always serial in either mode. The soft decision channel data into the decoder may be input symbol per transfer, up to 4 bits parallel, in either mode. The parallel channel input is selected when pin **DPARINPUT** = 1 on the rising edge of **RESET\_N**. When pin **DPARINPUT** = 0, the channel data is input serially.

A summary of the differences between synchronous and bus interface modes is:

- 1)Synchronous mode requires a continuous not gated - port clock. Bus mode uses a data strobe.

- 2)Synchronous mode requires a frame sync signal to assert 1 clock before data on each block. Bus mode does not require a frame sync.

- 3)Data input and output can be faster in the synchronous mode than in bus mode. The bus mode data strobe is limited to the SYSCLK frequency and the synchronous port clock allows an input clock rate of 1.9\*SYSCLK (refer to Section 11.2 U\_CLK, E\_CLK, C\_CLK, D\_CLK Clock Timing and Section 11.3 U\_WR\_N, E\_RD\_N, C\_WR\_N, D\_RD\_N Strobe Timing).

With the exception of the 4 bit parallel channel input to the decoder, the encoder interface is identical to the decoder interface. The following sections describe the interface in terms of the decoder, but all control descriptions and signal timing, except where explicitly stated, apply to the encoder signals. The encoder and decoder are shown on all connection diagrams.

## 2.1 CONFIGURATION WRITES

The AHA4525 configuration registers are split into 2 sets of register banks: one for the encoder datapath functions and one for the decoder datapath functions.

All encoder configuration registers are written through the encoder unencoded data input port. All decoder configuration registers are written through the decoder channel data input port. The configuration registers can be written before the start of a block transfer - not during a block transfer.

Configuration data is written in a 16 bit configuration cycle format (refer to Section 2.3 *Configuration Cycle Format*). When writing configuration data to the decoder and the decoder is configured for a parallel input by setting pin **DPARINPUT** = 1, the configuration data must be input 4 bits per transfer. When writing the configuration in parallel, the first of 4 data transfers expects bit 15 to be input on **CDATA[3]** down to bit 12 input on **CDATA[0]**. All 4 **CDATA** inputs are always used when writing configuration data in parallel.

The configuration cycle starts with a "rwn" bit to indicate whether the current configuration cycle is a read or write cycle and is followed by the "last" bit to indicate that the current configuration cycle is the last configuration write cycle. Configuration cycles are expected to continue until a cycle is received with the "last" bit set.

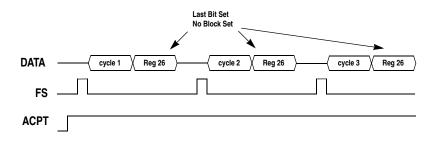

If the "last" bit is set, the AHA4525 expects data to immediately follow the current configuration cycle unless the last configuration cycle writes a one to the **NoBlock** bit (see configuration Section 7.7.1 *Control*). An example of the configuration cycle is shown in Figure 3.

PS4525\_0204

Figure 5: Configuration Example for Gaps Between Configuration Writes

The "last" bit is followed by a 6 bit address and then 8 bits of data to be written to the specified address. Refer to Section 7.0 *Register Descriptions* for configuration register functions and addresses.

The AHA4525 is configured for a fixed configuration mode with only 1 block code. An example of this configuration mode is shown in Figure 4.

If system constraints make it necessary to allow for dead time in between configuration writes you may use the configuration timing shown in Figure 5. Cycle 1, 2, 3 are normal configuration writes followed by a register 0x26 write. Register 0x26 must have the "**last**" bit set and the **xNoBlock** bit set.

The fixed configuration mode is selected during the initial configuration following **RESET\_N**. When a 1 is written to the **xNoConfig** bit in the control register (Refer to Section 7.7.1 *Control*), all data blocks are received as config 0. After the chip is configured, there is no access to the configuration registers until **RESET N** is asserted.

## 2.2 CONFIGURATION READS

All encoder configuration read requests are written through the encoder unencoded data input port. All decoder configuration read requests are written through the decoder channel data input port.

The encoder configuration registers can only be read when the encoder datapath is empty. The

decoder configuration registers can only be read when the decoder datapath is empty. The AHA4525 has a general output pin that may be used to monitor the datapath empty status (refer to Section 7.7.1 *Control*).

All encoder configuration registers are read from the encoder encoded data output port. All decoder configuration registers are read from the decoder decoded data output port.

A configuration data read request is written in a 16 bit configuration cycle format (refer to Section 2.3 *Configuration Cycle Format*). The configuration cycle starts with a "rwn" bit to indicate whether the current configuration cycle is a read or write cycle. When the "rwn" bit is set, the configuration cycle is a read request and it is by default the last configuration cycle. The "last" bit is irrelevant in a configuration read because each read must wait for the read data to be output before a new read can be requested. Data cannot directly follow a read configuration request.

The "last" bit is followed by a 6 bit address to specify which register to read. The 8 bits of data that follow the address field of the configuration read cycle are don't cares, but they must be input to finish the configuration cycle (refer to Section 7.0 *Register Descriptions* for configuration register functions and addresses).

## 2.3 CONFIGURATION CYCLE FORMAT

Bit 15 is input first, bit 0 is input last.

|     |      |      | bit12 |      |      |      |      |      |      |      |      |      |      |      |      |

|-----|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|------|

| rwn | last | a[5] | a[4]  | a[3] | a[2] | a[1] | a[0] | d[7] | d[6] | d[5] | d[4] | d[3] | d[2] | d[1] | d[0] |

- "rwn" Read/Write\_not. When "rwn" = 1, the configuration cycle is a read cycle. When "rwn" = 0, the configuration cycle is a write cycle.

- "last" Last configuration cycle. When set, the current configuration cycle is the last configuration cycle before data begins. When cleared, the current configuration cycle will be followed by another configuration cycle.

- "a[5:0]" Configuration address. Address of configuration read or write.

- "d[7:0]" Configuration data. When "rwn" = 0, this is the data to be written to the addressed configuration register. When "rwn" = 1, this data is a don't care.

## 2.4 DECODER STATUS OUTPUT

The AHA4525 has the option to output status information with each decoded block. There is no option to output any status information with encoded blocks.

The status of a decoded block is output as 16 bits at the end of every decoded block when the **DStatus** configuration bit is set to 1 (see Section 7.7.1 *Control*). The structure of the status output is shown in Section 2.5 *Decoder Status Output Format*. The status is output in serial, msb first.

The status includes a parity error flag "perr" which is asserted when the CRC is enabled and the output block failed the CRC verification.

The last status information is the number of corrections "c[11:0]". This is a count of the number of bit errors corrected in the current block, including user data, inserted CRC bits, and ECC bits.

## 2.5 DECODER STATUS OUTPUT FORMAT

Bit 15 is output first, bit 0 is output last.

| bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 | bit7         | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|-------|-------|-------|-------|-------|------|------|--------------|------|------|------|------|------|------|------|

|       | res   |       | perr  | c[11] | c[10] | c[9] | c[8] | <b>c</b> [7] | c[6] | c[5] | c[4] | c[3] | c[2] | c[1] | c[0] |

"perr" - Parity error. Asserted when CRC is enabled and the output block failed the CRC verification.

"c[11:0]" - Correction count. The number of bit errors corrected in the current block including user data, inserted CRC bits, and ECC bits.

## 2.6 ENCODER AND DECODER - SYNCHRONOUS I/O - FULL DUPLEX

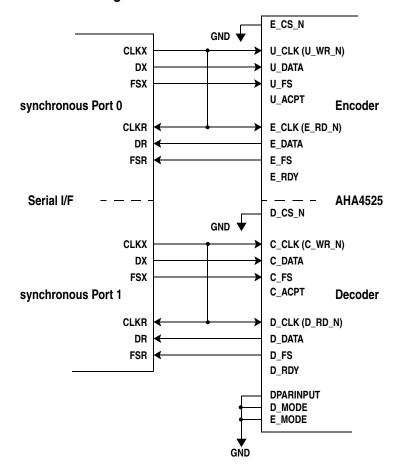

An AHA4525 synchronous interface full duplex connection diagram is shown in Figure 6. Data blocks and configuration information are input through the U\_DATA port when encoding or the C\_DATA port when decoding.

The soft decision channel data into the decoder is serially input when **DPARINPUT** = 0 on the rising edge of **RESET\_N**, which reduces the input rate by up to a factor of 4 when a 4 bit soft metric is used. The channel input port may be configured to allow 4 bit parallel input on **C\_DATA** when **DPARINPUT** = 1 on the rising edge of **RESET\_N**. When **DPARINPUT** = 1, the **C\_DATA** port is configured in parallel mode and the configuration data is expected to be received in 4 bit parallel. When **DPARINPUT** = 0, the **C\_DATA** port resets into serial mode and expects to receive configuration data serially. The synchronous interface timing for the decoder signals is shown in Figures 7 and 8. The signal timing for the encoder is similar.

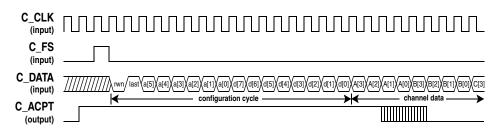

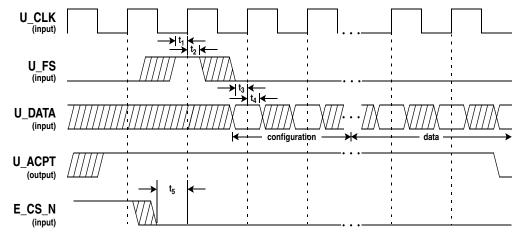

A data or configuration write is started when C\_FS is asserted for one C\_CLK cycle. The C\_FS signal is a sync signal that is asserted once for every block when the **DWordEqBlk** configuration bit is set to 1 or asserted once for every word when the **DWordEqBlk** configuration bit is set to 0 (see Section 7.6.1 *Transfer Word Size*). The word size is configured using the **DWordSize[4:0]** register also shown in Section 7.6.1 *Transfer Word Size*. The **DWordSize[4:0]** register resets to 16 bits per word. Figure 27 shows the input timing requirements for C\_FS.

#### Figure 6: Full Duplex Connection Diagram

#### comtech aha corporation

All AHA4525 configuration is done immediately following the first **C\_FS** of a block and the interface remains in the configuration mode until a configuration cycle is input with the "last" bit set. The structure of a configuration cycle is shown in Section 2.3 *Configuration Cycle Format* and in the timing diagram Figure 7 in the **C\_DATA** input data stream.

In Figure 7, A[3:0] and B[3:0] following the configuration cycle indicate the start of the data block where A is a 4 bit soft metric and B is a 4 bit soft metric.

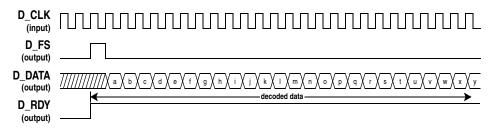

If the configuration cycle is a read request, the read data is available on **D\_DATA** on the **D\_CLK** cycle following when the **D\_FS** output signal is asserted for one **D\_CLK** cycle. Data cannot follow a configuration read and decoder configuration reads are only allowed when the decoder datapath is empty. The read data must be read from the **D\_DATA** port before another configuration cycle is started.

The **D\_FS** signal timing is shown in Figures 7 and 8 and the electrical characteristics are shown in Figure 30. **D\_FS** asserts to indicate that the block is finished processing and the output data will start on the next **D\_CLK** cycle. The **D\_FS** signal is a sync signal that is asserted once for every block when the **DWordEqBlk** configuration bit is set to 1 or asserted once for every word when the

**DWordEqBlk** configuration bit is set to 0 (see Section 7.6.1 *Transfer Word Size*). The word size is configured using the **DWordSize[4:0]** register also shown in Section 7.6.1 *Transfer Word Size*. The **DWordSize[4:0]** register resets to 16 bits per word. The output data is read serially through the **D\_DATA** port. **D\_RDY** asserts with the **D\_FS** at the start of a block and stays asserted until the last data, including block status, is clocked out of the decoder (see Figures 7 and 8). Note that the encoder does not output a block status footer. **D\_RDY** is not required for systems where the receive port is set up to expect a certain output block size, but it may be used in systems that do not count the bits in the received block.

C\_ACPT asserts when the input buffer is ready to accept a block and is deasserted after the data portion of the block transfer is started or a configuration read is started (see Figures 7 and 8). This signal may be used to allow the decoder to process more than one block at a time. C\_ACPT is not required for systems that process one block at a time (i.e. the first block is input, processed, and output before a second block is input).

The synchronous interface requires continuous port clocks **C\_CLK** and **D\_CLK**. Gated port clocks are not allowed. The continuous **D\_CLK** automatically fills any padding required by a serial receive port.

The following timing diagrams Figure 7 and Figure 8 show a block input and output through the decoder in serial mode (**DPARINPUT** = 0). The **C\_FS** and **D\_FS** signals shown in the following diagrams are shown assuming **DWordEqBlk** is set.

#### Figure 7: Synchronous Data/Configuration Communication Timing - Start of Block

Start of Block

#### Decoded Start of Block - Output Data (after decoder latency)

#### Start of Block - Configuration Read

#### **Output Configuration Read Data**

## 2.7 ENCODER AND DECODER SYNCHRONOUS - HALF DUPLEX

This interface is the same as the full duplex synchronous mode except the **E\_CS\_N** and **D\_CS\_N** inputs are used to switch between the encoder and decoder.

#### Figure 9: Half Duplex Connection Diagram

A subsidiary of Comtech Telecommunications Corporation

The differences in the communication timing between the full duplex and half duplex synchronous configurations are the tristated **D\_FS** and **D\_DATA** outputs when the decoder **D\_CS\_N** is not asserted, and the tristated **E\_FS** and **E\_DATA** outputs when the encoder **E\_CS\_N** is not asserted. Refer to the full duplex synchronous configuration Section 2.6 *Encoder and Decoder - Synchronous I/ O - Full Duplex* for communication timing diagrams.

#### 2.8 BUS MODE - HALF DUPLEX

The AHA4525 bus interface half duplex connection diagram is shown in Figure 10. The bus interface is selected for the encoder when  $E_MODE = 1$  and is selected for the decoder when **D\_MODE** = 1. Data blocks and configuration information are input through the **U\_DATA** port when encoding or the **C\_DATA** port when decoding.

The bus mode interface allows a 4 bit parallel channel input through the C\_DATA port to allow soft metrics to be written to the decoder at a rate of one symbol per transfer. The interfaces to D\_DATA, U\_DATA, and E\_DATA are serial. When bus mode is selected at reset, the status of the DPARINPUT pin determines if the C\_DATA port is configured in serial or 4 bit parallel mode. When DPARINPUT = 1 at reset, the C\_DATA port is configured in 4 bit parallel mode and the first configuration cycle is expected to be received in 4 bit parallel.

#### Figure 10: Half Duplex Connection Diagram

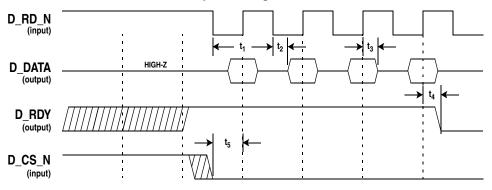

The bus interface timing for the decoder signals is shown in Figure 11. The signal timing for the encoder is typical.

A data or configuration write cycle is started when C\_WR\_N is asserted low. There is no block start signal in bus mode. The C\_WR\_N signal is a write strobe signal, with data being registered on the rising edge (see Figure 33).

All configuration is done immediately following reset. The AHA4525 counts the number of input data bits and compares the input count to the **DBlockSize** configuration setting (see Section 7.4.2 *Block Size*) to find the end of an input block.

The interface remains in the configuration mode until a configuration cycle is input with the "last" bit set. The structure of a configuration cycle is shown in Section 2.3 Configuration Cycle *Format*. The configuration cycle is shown as c[3:0] in Figure 11 in the C DATA input stream. Note that the encoder does not have the parallel input option and all configuration bits must be input serially. The first 16 bits (4 writes) in the C DATA stream are configuration write bits with bits (15:11) written first and bits (3:0) written last. The configuration starts with a "rwn" (read/write not) bit and is followed by a "last" bit which indicates that the current configuration cycle is the last configuration cycle. The "last" bit is followed by a 6 bit address a[5:0] and then the data d[7:0] to be written to the address.

The AHA4525 expects data to immediately follow the last configuration write cycle unless the last configuration cycle writes a one to the **NoBlock** bit (see configuration Section 7.7.1 *Control*). A and B following the configuration cycle indicate the start of the data block where A is a 4 bit soft metric and B is a 4 bit soft metric.

If the configuration cycle is a read request, the read data is available on **D\_DATA** when **D\_RDY** is asserted. The configuration data is read when **D\_RD\_N** is asserted low and the data is valid until the **D\_RD\_N** rising edge (see Figure 35). Data cannot follow a configuration read and decoder configuration reads are only allowed when the decoder datapath is empty. Each configuration read is considered a last configuration cycle similar to a last configuration write cycle with the **NoBlock** bit set. The read data must be read from the **D\_DATA** port before another configuration cycle is started.

**D\_RDY** asserts when valid data is available to be read at the output and stays asserted until the last data, including block status, is strobed out of the decoder (see Figure 11). **D\_RDY** can be monitored to know when to start an output read, or the output can be read after decoder block latency number of **SYSCLK**s. The decoder latency calculations are shown in Section 4.2.7 *Decoder Latency*. Any **D\_RD\_N** strobes beyond the end of a block are ignored until the **D\_RDY** signal is asserted.

C\_ACPT asserts when the input buffer is ready to accept a block and deasserts after the data portion of the block transfer is started or a configuration read is started (see Figure 11). This signal may be used to allow the decoder to process more than one block at a time. C\_ACPT is not required for systems that process one block at a time (i.e. the first block is input, processed, and output before a second block is input).

The status of the decoded block is output in 16 bits at the end of every decoded block when the **DStatus** configuration bit is set to 1 (see control Section 7.7.1 *Control*). The structure of the status output is shown in Section 2.5 *Decoder Status Output Format* and partially in the timing diagram Figure 11 in the **D\_DATA** output data stream as s[8:0] (s[15:9] are not shown). There is not an option to output status information at the end of encoded blocks.

In bus mode, the AHA4525 is a slave to the system. The C\_WR\_N and D\_RD\_N signals are both inputs to AHA4525. Blocks do not need to be read or written in a continuous stream in bus mode.

The signal differences between synchronous mode and bus mode are:

- a) the C\_CLK and U\_CLK inputs become C\_WR\_N and U\_WR\_N in bus mode,

- b) the D\_CLK and E\_CLK inputs become D\_RD\_N and E\_RD\_N inputs in bus mode,

- c) the **D\_DATA** bus is tristated when **D\_RD\_N** is not asserted, and

- d) the **E\_DATA** bus is tristated when **E\_RD\_N** is not asserted.

## Figure 11: Bus Interface Data/Configuration Communication Timing - Start of Block

PS4525\_0204

# 2.9 DECODER BUS INTERFACE, ENCODER SYNCHRONOUS INTERFACE - FULL DUPLEX

The full duplex connection diagram shown in Figure 12 is used to show the flexibility of the AHA4525 interface. The decoder uses the bus connection with a 4 bit parallel channel input while the encoder uses the synchronous port. In this configuration, the **C\_ACPT** output is used to signal that the **C\_DATA** input is ready to accept data. The AHA4525 decoder resets into 4 bit parallel mode when **DPARINPUT** = 1, so the first decoder configuration write must be done in 4 bit parallel.

## 3.0 ENCODER

Figure 13: Encoder Block Diagram

Figure 13 shows a block diagram of the encode path. Note that all of the blocks in the encode path except the helical interleaver operate by only inserting or modifying data in the stream. Therefore, the entire encode path has low latency.

Data is input serially through U\_DATA. The CRC engine computes a CRC over each block of data which is inserted at the end of the uncoded data block. This data is scrambled by exclusive-ORing with the output of a Pseudo Random Binary Sequence (PRBS) generator. The scrambler ensures adequate bit transitions in the data stream, which are often required to allow improved DC balance and to accelerate clock recovery in the demodulator. The scrambled data is input to a TPC encoder, which computes ECC bits and inserts them at the appropriate locations in the data stream.

The helical interleaver improves burst error performance of the decoder. However, it adds a one block latency to the datapath. The encoded block is serially output through **E DATA**.

#### 3.1 CRC ENCODER

The cyclic redundancy check (CRC) encoder is a 32 bit linear feedback shift register with a programmable polynomial. Figure 14 shows a diagram of the shift register. Each TPC block has a separate CRC encoded with the resultant CRC bits appended to the block.

The polynomial for the CRC encoder is written into the **ECRCPoly** register. The highest order of the polynomial (defined by **ECRCSize**) is assumed to be a 1, and bit 0 of the polynomial register corresponds to the 0th order of the polynomial, as shown in Figure 14. The desired size of the CRC, in bits, is written into the **ECRCSize** register.

Table 1 gives a suggested list of polynomials for various length CRCs. The POLY column of table 1 gives the value to program into the **ECRCPoly** register. The detection capability column gives the probability that an incorrect block will be detected and flagged as incorrect by the CRC decoder.

#### Figure 14: CRC Encoder

#### Table 1: Recommended CRC Polynomials

| CRC   | SIZE<br>(bits) | <b>POLY</b><br>Program Value<br>(hex)* | DETECTION<br>CAPABILITY** |

|-------|----------------|----------------------------------------|---------------------------|

| 4     | 4              | 1f                                     | 0.9375                    |

| 8     | 8              | 1d5                                    | 0.99609                   |

| 12    | 12             | 180f                                   | 0.999756                  |

| ANSI  | 16             | 18005                                  | 0.999985                  |

| CCITT | 16             | 11021                                  | 0.999985                  |

| SDLC  | 16             | 1a097                                  | 0.999985                  |

| 24    | 24             | 1805101                                | 0.9999999404              |

| 32A   | 32             | 1404098e2                              | 0.99999999953             |

| 32B   | 32             | 104c11db7                              | 0.99999999977             |

Notes:

\*\*

The leading '1' in these values is assumed by the device and should not be written to the register.

This detection capability is the probability that an incorrect block is marked in error. The probability of an undetected block is computed by multiplying the block error rate by (1 - Detection Capability).

The shift register is reset to all 0s at the beginning of each TPC block. Data from the block is shifted into the circuit until the number of bits programmed into **EBlkSize** is reached. Note that the value written into **EBlkSize** does not include the CRC bits. After the entire TPC block is shifted into the CRC encoder, the data input and feedback of the CRC shifter are disabled, and the contents of the CRC registers are shifted out and inserted into the data stream.

Figure 15 shows the location of the CRC word inserted in a 2D TPC encoded block. D denotes data bits and E denotes computed error correction bits.

Figure 15: 2D TPC Encoded Block with CRC

#### 3.2 SCRAMBLER

The scrambler is built with a 16 bit pseudo-random binary sequence generator with programmable polynomial, length, and initialization seed. Figure 16 shows the configuration of the scrambler. The shift register is clocked once for each bit. As shown in Figure 16, the output of the shift register is exclusive-ORed with the data to be scrambled.

Figure 16 shows an example configuration for the generator polynomial sequence:

## $1 + X^{14} + X^{15}$

This sequence is programmed into the **EScramPoly** register as 0b0110000000000000. The seed for the shift register that is shown in the diagram is programmed into **EScramSeed** as 0b0000000010101001. Every time the scrambler is reset it is initialized with this seed value.

PS4525 0204

Note that the length of the generator is directly determined by the polynomial configuration. The sequence shown here is generated by a 15 stage shift register. Since the highest order of the polynomial is 15, the 16th bit XOR feedback will be disabled and only 15 bits of the shift register are used. Also note that the 0th order of the polynomial is assumed to be 1.

The scrambler is reset at the beginning of every TPC block.

## 3.3 TPC ENCODER

The TPC encoder supports 2D codes with constituent code lengths of up to 64 bits and overall block size up to 4096 bits. The encoder supports both extended Hamming and parity only constituent codes. See Section 7.4.1 *TPC Constituent Code* for a description of supported codes and shortening configurations.

#### 3.3.1 ENCODER CODE SHORTENING

There are two methods of shortening product codes. The first method is to remove an entire row or column from a 2D code. This is equivalent to shortening the constituent codes that make up the product code and is accomplished by writing the amount to shorten into the **xShortX** and **xShortY** registers (see Section 7.4.4 *Shortening Configuration*). This method enables a coarse granularity on shortening and at the same time maintaining the highest code rate possible by removing both data and parity symbols. Further shortening is obtained by removing individual bits from the first row of a 2D code (using **xShortB**).

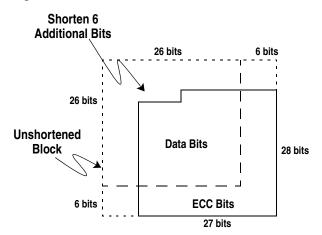

The following examples discuss shortening in a 2D code. Assume a 456 bit block size is required with code rate of approximately 0.6. The base code chosen before shortening is the (32,26)x(32,26) code which has a data size of 676 bits. Shortening all rows by 5 and all columns by 4 results in a (27,21)x(28,22) code with a data size of 462 bits. To get the exact block size, the first row of the product is shortened by an addition 6 bits. The final code is a (750,456) code with a code rate of 0.608. Figure 17 shows the structure of the resultant block. This shortening is programed into the device by writing **xShortX** to 5, **xShortY** to 4, and **xShortB** to 6.

#### Figure 17: Structure of Shortened Code

#### 3.3.2 HELICAL INTERLEAVER

Helical interleaving transmits data in a helical fashion. When the channel introduces a burst of errors, the helical deinterleaver in the decoder will spread these errors across all axes of the code. The use of helical interleaving increases the burst error correcting capability of the code and increases the block latency (refer to Section 3.3.4 *Encoder Latency*).

The helical interleaver is enabled by setting **EHelical** to one (see Section 7.4.1 *TPC Constituent Code*). When helical interleaving is enabled, the **EShortX** and **EShortB** values must be set to 0 (see Section 7.4.4 *Shortening Configuration*). This constrains the shortening resolution to one row for 2D codes. All of the blocks in the encode datapath must be either interleaved or not interleaved. A mixture of interleaving blocks and non-interleaving blocks in the encoder datapath at the same time is not allowed.

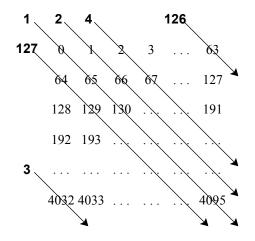

Helical interleaving is applied along a diagonal path through the encoded block. Data is output along diagonal lines from the upper left to lower right corner. The first diagonal output starts with the bit row 1, column 1 followed by the diagonal starting at row 1, column 2. The example below shows how interleaving is applied for a 2D (64,57)x(64,57) code.

#### Figure 18: Input Block

| 0    | 1    | 2   | 3  | <br>63   |  |

|------|------|-----|----|----------|--|

| 64   | 65   | 66  | 67 | <br>127  |  |

| 128  | 129  | 130 |    | <br>191  |  |

| 192  | 193  |     |    | <br>     |  |

|      |      |     |    | <br>     |  |

| 4032 | 4033 |     |    | <br>4095 |  |

*Note:* The number reflects the bit order including generated ECC bits.

The encoded, interleaved data output is taken along diagonal lines starting with bit zero as shown below. The order of the interleaving is noted for each diagonal line.

#### Figure 19: 2D Interleaving

For the (64,57)x(64,57) block, the data output is: 0, 65, 130,..., 4095, 1, 66,..., 4031, 4032, 2, 67,...,.., 63, 64,..., 4094 for a total of 4096 bits output. The AHA4525 operating as a decoder deinterleaves the block to restore it to its original order.

#### Figure 20: Encoded/Interleaved Data Output

| 0  | 65 | 130 | 4030 4095 |

|----|----|-----|-----------|

| 1  | 66 | 131 | 4031 4032 |

| 2  | 67 | 132 | 3968 4033 |

| 3  | 68 |     |           |

|    |    |     |           |

| 63 | 64 | 129 | 4029 4094 |

Data bits are output from the encoder in row order from left to right.

#### 3.3.3 INTERNAL BUFFERING

An internal encoder buffer is used to allow data to stream into and out of AHA4525. The encoder buffer is always enabled because the data flow into the encoder is not throttled by AHA4525 in either bus mode or synchronous mode. The logical size of the encoder input buffer is set via **EBufferSize** (refer to Section 7.4.3 *Buffer Configuration (Encoder Only)* for an equation to calculate **EBufferSize**).

#### 3.3.4 ENCODER LATENCY

The encoder latency is defined as the time from when the first un-encoded bit is input until the **E\_RDY** signal is asserted to indicate that a block is ready to be output. When helical interleaving is disabled and **E MODE** = 0, the approximate encoder latency in **SYSCLK**s when **PLLBYPASS** = 0 is:

$$\frac{(\text{EBufferSize} \times 16) + 31}{2} + \left(2 \times \frac{\text{SYSCLK (MHz)}}{\text{U_CLK (MHz)}}\right) + \left(2 \times \frac{\text{SYSCLK (MHz)}}{\text{E_CLK (MHz)}}\right)$$

When helical interleaving is disabled and  $E_MODE = 1$ , the approximate encoder latency in SYSCLKs is:

$$\frac{(\text{EBufferSize} \times 16) + 36}{2}$$

The EBufferSize input buffer is used to guarantee a streaming input and output.

A subsidiary of Comtech Telecommunications Corporation

Helical interleaving adds one block of latency. When helical interleaving is enabled, the encoder input buffer is not used. The worst case encoder latency in **SYSCLK**s when helical interleaving is enabled and  $E_MODE = 0$  is:

$$\left(1 \text{ encoded block size} \times \frac{\text{SYSCLK (MHz)}}{\text{U_CLK (MHz)}}\right) + \left(2 \times \frac{\text{SYSCLK (MHz)}}{\text{U_CLK (MHz)}}\right) + 24 + \left(2 \times \frac{\text{SYSCLK (MHz)}}{\text{E_CLK (MHz)}}\right)$$

When helical interleaving is enabled and **E\_MODE** = 1, the worst case encoder latency in **SYSCLK**s is:

$$(1 \text{ encoded block size} \times \frac{\text{SYSCLK (MHz)}}{\text{U}_{\text{CLK (MHz)}}}) + 26$$

If the PLL is bypassed (PLLBYPASS = 1), then the latency result in SYSCLKs must be multiplied by 4.

## 4.0 DECODER

The decode path of AHA4525 includes a counterpart for each encoder module. The encoder and decoder are isolated paths. This allows full duplex operation where the encoder and decoder may be operating with different code types and data rates.

#### 4.1 CHANNEL INTERFACE

The channel interface formats the channel data for decoding by the Turbo Product Code decoder. For best decoder performance, soft metric information from the channel is necessary.

#### 4.1.1 CHANNEL INPUT FORMATTING

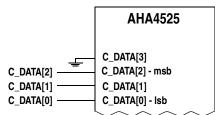

When decoding, data may be input either serially or one quantization value per handshake on C DATA[q-1:0] where q is the number of input quantization bits. The number of quantization bits is configurable based on the setting of **QBIT**[1:0] within the Quantization register in Section 7.5.1. The **QMODE**[1:0] bits within the Quantization register determine the type of input data. The input data may be 2's complement, sign/magnitude, or unsigned. All unused C DATA inputs are ignored except in configuration cycles. Note that all C DATA[3:0] inputs are used for configuration cycles in parallel mode. In parallel configuration cycles, configuration bits (15:11) are written first with configuration bit 15 input on C DATA[3]. In parallel data cycles, the lsb of the soft metric value is input on C DATA[0] and the msb is determined by **OBits**[1:0]. Figure 21 shows example connections when **QBits**[1:0] = "11" (3 input bits).

#### Figure 21: C\_DATA Interface

For QBits = "11" connect C\_DATA as shown

#### 4.2 TPC DECODER

The Turbo Product Code decoder supports block sizes up to 4096 encoded bits. The decoder supports iterative decoding of 2D codes built from extended Hamming or parity only constituent codes of length up to 64 bits.

#### 4.2.1 HELICAL DEINTERLEAVER

The helical deinterleaver is enabled by setting **DHelical** to 1 in the configuration register shown in Section 7.4.1 *TPC Constituent Code*. See Section 3.3.2 for a description of helical interleaving.

#### 4.2.2 CODE CONFIGURATION

Turbo Product Codes are specified by the constituent codes of each axis in the code. The code configuration registers in Section 7.4.1 *TPC Constituent Code* specify the code type (extended Hamming or Parity) and length of each axis.

To generate a specific block size, the product code is shortened. Shortening is discussed in detail in Section 4.2.3.

The decoder can be configured to run a specific number of iterations by programming the number of **Iterations** in the configuration register shown in Section 7.4.6 *Iterations (Decoder Only)*. The decoder can be set to detect when a block converges and stop iterating. This allows the decoder to spend more time, up to the number of iterations specified in **Iterations**, on difficult blocks and less time on

Page 18 of 55

A subsidiary of Comtech Telecommunications Corporation

less difficult blocks. This feature is enabled by setting **StopIter** in the configuration register shown in Section 7.4.5 *Feedback (Decoder Only)*.

#### 4.2.3 DECODER CODE SHORTENING

Refer to Section 3.3.1 *Encoder Code Shortening*.

#### 4.2.4 CORRECTIONS COUNT

In order to assist the system with estimation of channel bit error rates, the AHA4525 device reports the number of bits corrected in each block decoded.

The **Corrections** register (see Section 7.7.2 Status and Correction Count (Decoder Only)) contains the number of corrections between incoming (channel) data and outgoing (decoded) data. This corrections value is the corrections done on all bits in the TPC block including user data, CRC, and TPC ECC bits. The correction count is updated in the **Corrections** register after each block is decoded and is also optionally output at the end of every block as a status footer (see Section 2.5 Decoder Status Output Format).

#### 4.2.5 DESCRAMBLER

The descrambler is built with a 16 bit pseudorandom binary sequence generator with programmable polynomial, length, and initialization seed. The descrambler logic matches that of the scrambler shown in Figure 16 (refer to Section 3.2).

The generator polynomial sequence is programmed into the **DScramPoly** register. The seed for the shift register shown in Figure 16 is programmed into **DScramSeed**. Every time the descrambler is reset, it initializes to the **DScramSeed** value. The descrambler is reset at the start of every block.

#### 4.2.6 CRC CHECKING

The CRC parity bits are checked after decoding. Each packet has a separate CRC with variable length up to 32 bits. The CRC comparator circuit matches that of the encoder shown in Figure 14.

The shift register is reset at the beginning of each TPC block. Data from the TPC block is shifted into the circuit until the number of bits programmed into **DBlkSize** is reached. At this point, the contents of the CRC shift register are examined. If all bits are 0, then the CRC is correct. Otherwise, a CRC error is detected and the **CRCErr** status flag is set in the decoder status footer (see Section 2.5 *Decoder Status Output Format*). The **CRCErr** flag can also be read from the status register shown in Section 7.7.2 *Status and Correction Count (Decoder Only)*.

#### 4.2.7 DECODER LATENCY

The decoder latency is defined as the time from when the last channel bit is input until the **D\_RDY** signal is asserted to indicate that a block is ready to be output. In the following equations, **DCodeX** is **DCodeX[2:0]**, **DCodeY** is **DCodeY[2:0]**. The approximate decoder latency in **SYSCLKs** when **PLLBYPASS** = 0 is:

If **DCodeX** is not 0,

$$x\_latency = \frac{2^{\mathbf{DCodeX}} \times (2^{\mathbf{DCodeY}} - \mathbf{DShortY})}{4} + 2^{\mathbf{DCodeX}} + 16$$

If  $\mathbf{DCodeX} = 0$ , x\_latency = 0.

If **DCodeY** is not 0,

$$y\_latency = \frac{2^{\mathbf{DCodeY}} \times (2^{\mathbf{DCodeX}} - \mathbf{DShortX})}{4} + 2^{\mathbf{DCodeY}} + 16$$

If **DCodeY** = 0, y latency = 0.

iter\_clocks = (x\_latency + y\_latency) × **Iterations**

When  $\mathbf{D}_{\mathbf{MODE}} = 1$ ,

latency =

$$29 + \frac{\text{iter\_clocks}}{2} + \frac{\text{DShortB}}{4}$$

When  $\mathbf{D}_{\mathbf{MODE}} = 0$ ,

latency =

$$\frac{2 \times SYSCLK (MHz)}{C_CLK (MHz)} + 27 + \frac{2 \times SYSCLK (MHz)}{D_CLK (MHz)} + \frac{iter_clocks}{2} + \frac{DShortB}{4}$$

If the PLL is bypassed (PLLBYPASS = 1), then the latency result in SYSCLKs must be multiplied by 4.

Table 2 gives an abridged list of possible codes supported by AHA4525, along with the latency in **SYSCLKs** for 4, 6, and 12 iterations with the CRC disabled. This table applies to a synchronous (**D\_MODE** = 0) port configuration with the internal PLL enabled (**PLLBYPASS** = 0) and assumes that the frequency of  $C_{CLK} = SYSCLK$ . This is a very small subset of supported codes. Comtech AHA Corporation (CAC) can provide software to assist the code selection process.

#### Table 2: Partial Code List and Decoder Datapath Latency

| CODE<br>(X)x(Y)x(Z) | BLOCK<br>SIZE<br>(bits) | DATA<br>SIZE<br>(bits) | 4 ITERATIONS<br>(SYSCLKs)* | 6 ITERATIONS<br>(SYSCLKs)* | 12 ITERATIONS<br>(SYSCLKs)* |

|---------------------|-------------------------|------------------------|----------------------------|----------------------------|-----------------------------|

| (64,63)x(64,63)     | 4096                    | 3969                   | 4445                       | 6665                       | 13277                       |

| (64,57)x(64,57)     | 4096                    | 3249                   | 4445                       | 6653                       | 13277                       |

| (32,31)x(32,31)     | 1024                    | 961                    | 1245                       | 1853                       | 3677                        |

| (32,26)(x(32,26)    | 1024                    | 676                    | 1245                       | 1853                       | 3677                        |

| (64,57)x(32,26)     | 2048                    | 1482                   | 2333                       | 3485                       | 6941                        |

| (64,57)x(64,63)     | 4096                    | 3591                   | 4445                       | 6665                       | 13277                       |

| (64,57)x(32,31)     | 2048                    | 1767                   | 2333                       | 3485                       | 6941                        |

| (32,26)x(16,11)     | 512                     | 286                    | 701                        | 1037                       | 2045                        |

| (32,26)x(16,15)     | 512                     | 390                    | 701                        | 1037                       | 2045                        |

\* The number of SYSCLKs is assuming the PLL is enabled (PLLBYPASS=0) and is accurate to within 2%. If the PLL is not enabled (PLLBYPASS=1), then the latency in SYSCLKs must be multiplied by 4.

## Table 3: Partial Code List and Performance - Synchronous Interface

| CODE<br>(X)x(Y)x(Z) | BLOCK<br>SIZE<br>(bits) | DATA<br>SIZE<br>(bits) | CODE<br>RATE | 6 ITER<br>CODING<br>GAIN<br>(dB) | 4 ITER<br>Channel/<br>Data*<br>(Avg Mbit/sec) | 6 ITER<br>Channel/<br>Data*<br>(Avg Mbit/sec) | 12 ITER<br>Channel/<br>Data*<br>(Avg Mbit/sec) |

|---------------------|-------------------------|------------------------|--------------|----------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------|

| (64,63)x(64,63)     | 4096                    | 3969                   | 0.969        | 3.2                              | 46.4/45.0                                     | 31.0/30.0                                     | 15.5/15.0                                      |

| (64,57)x(64,57)     | 4096                    | 3249                   | 0.793        | 7.3                              | 46.4/36.9                                     | 31.0/24.5                                     | 15.5/12.3                                      |

| (32,31)x(32,31)     | 1024                    | 961                    | 0.938        | 3.2                              | 42.3/39.6                                     | 28.1/26.4                                     | 14.1/13.3                                      |

| (32,26)x(32,26)     | 1024                    | 676                    | 0.660        | 7.2                              | 42.3/27.9                                     | 28.1/18.6                                     | 14.1/9.3                                       |

| (64,57)(x(32,26)    | 2048                    | 1482                   | 0.724        | 7.2                              | 44.5/32.3                                     | 29.6/21.5                                     | 14.9/10.8                                      |

| (64,57)x(64,63)     | 4096                    | 3591                   | 0.877        | 5.4                              | 46.4/40.8                                     | 31.0/27.1                                     | 15.5/13.6                                      |

| (64,57)x(32,31)     | 2048                    | 1767                   | 0.863        | 5.4                              | 44.5/38.4                                     | 29.6/25.6                                     | 14.9/12.8                                      |

| (32,26)x(16,11)     | 512                     | 286                    | 0.559        | 6.8                              | 38.4/21.4                                     | 25.5/14.3                                     | 12.8/7.1                                       |

| (32,26)x(16,15)     | 512                     | 390                    | 0.762        | 5.4                              | 38.4/29.3                                     | 25.5/19.5                                     | 12.8/9.8                                       |

\* The input and output rates assume a 50 MHz SYSCLK frequency when the PLL is enabled or a 200 MHz SYSCLK frequency when the PLL is bypassed. The port clocks C\_CLK and D\_CLK are assumed to be running at 95 MHz.

| CODE<br>(X)x(Y)x(Z) | BLOCK<br>SIZE<br>(bits) | DATA<br>SIZE<br>(bits) | CODE<br>RATE | 6 ITER<br>CODING<br>GAIN<br>(dB) | 4 ITER<br>Channel/<br>Data*<br>(Avg Mbit/sec) | 6 ITER<br>Channel/<br>Data*<br>(Avg Mbit/sec) | 12 ITER<br>Channel/<br>Data*<br>(Avg Mbit/sec) |

|---------------------|-------------------------|------------------------|--------------|----------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------|

| (64,63)x(64,63)     | 4096                    | 3969                   | 0.969        | 3.2                              | 44.3/43.0                                     | 29.6/28.6                                     | 14.9/14.4                                      |

| (64,57)x(64,57)     | 4096                    | 3249                   | 0.793        | 7.3                              | 44.3/35.3                                     | 29.6/23.4                                     | 14.9/11.8                                      |

| (32,31)x(32,31)     | 1024                    | 961                    | 0.938        | 3.2                              | 40.4/37.9                                     | 26.9/25.3                                     | 13.5/12.6                                      |

| (32,26)x(32,26)     | 1024                    | 676                    | 0.660        | 7.2                              | 40.0/26.3                                     | 26.9/17.8                                     | 13.5/8.9                                       |

| (64,57)x(32,26)     | 2048                    | 1482                   | 0.724        | 7.2                              | 42.5/30.8                                     | 28.3/20.5                                     | 14.3/10.3                                      |

| (64,57)x(64,63)     | 4096                    | 3591                   | 0.877        | 5.4                              | 44.3/38.9                                     | 29.6/25.9                                     | 14.9/13.0                                      |

| (64,57)x(32,31)     | 2048                    | 1767                   | 0.863        | 5.4                              | 42.5/36.6                                     | 28.3/24.5                                     | 14.3/12.1                                      |

| (32,26)x(16,11)     | 512                     | 286                    | 0.559        | 6.8                              | 36.6/20.4                                     | 24.4/13.6                                     | 12.1/6.8                                       |

| (32,26)x(16,15)     | 512                     | 390                    | 0.762        | 5.4                              | 36.6/28.0                                     | 24.4/18.6                                     | 12.1/9.3                                       |

\* The input and output rates assume a 50 MHz SYSCLK frequency when the PLL is enabled or a 200 MHz SYSCLK frequency when the PLL is bypassed. The read and write strobes C\_WR\_N and D\_RD\_N are assumed to be running at 50 MHz.

#### 4.2.8 CODE PERFORMANCE

Tables 3 and 4 give code rate, coding gain, and maximum channel and user (decoded) data rates for the same abridged list of possible codes that was shown in Table 2. The data rate calculations assume that the frequency of **SYSCLK** is 50 MHz. The coding gain is measured on a Binary Input Additive White Gaussian Noise (AWGN) channel at 10<sup>-6</sup> Bit Error Rate (BER) and 6 iterations. CAC can provide software to assist in code BER performance analysis.

## 5.0 PHASE LOCK LOOP

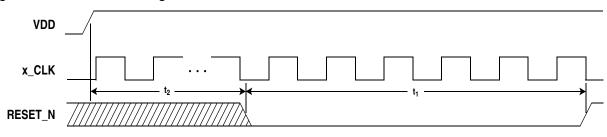

The AHA4525 contains an internal PLL which is used to multiply the input **SYSCLK** frequency by 4 for internal clocking. The internal PLL has a minimum input **SYSCLK** frequency of 20 MHz and a maximum input **SYSCLK** frequency of 50 MHz (see Section 11.1 *SYSCLK Clock Timing*). The PLL can not lock to frequencies below 20 MHz.

The internal PLL is enabled when pin **PLLBYPASS** = 0. If **PLLBYPASS** = 1, the internal PLL is bypassed and the input **SYSCLK** directly drives the internal logic.

When the PLL is bypassed, the latency and throughput are reduced by a factor of 4 given the same input **SYSCLK** frequency. The throughput and latency are identical when the PLL is bypassed and a 4x **SYSCLK** frequency is used when compared to the throughput and latency when the PLL is enabled and a 1x **SYSCLK** frequency is used (refer to Section 3.3.4 *Encoder Latency* and Section 4.2.7 *Decoder Latency*).

## 6.0 GENERAL OUTPUT SIGNALS

The AHA4525 contains a general output signal for the encoder and a general output signal for the decoder that can be used to control external logic or for system debugging. The signals can be driven to a 1 or 0 or can be driven according to events within the device including load complete, decode complete, empty, etc. (see Section 7.7.1 for a complete list of available status outputs).

## 7.0 REGISTER DESCRIPTIONS

## 7.1 CONFIGURATION SEQUENCE

The following sequence should be followed when configuring the device. The encoder and decoder configuration sequences are identical. The following configuration sequence is described in terms of the decoder, but all descriptions, except where explicitly stated, apply to the encoder.

The decoder is reset when **RESET\_N** = 0. After the rising edge of **RESET\_N**, the decoder is idle. The first write to the decoder is expected to start a configuration cycle. The order of configuration is not important. The last configuration cycle is specified by either the "rwb" bit = 1 or "last" bit = 1 (see Section 2.3 *Configuration Cycle Format*). Data is not expected to follow the configuration cycles if the last configuration cycle is a read or if the DNoBlock bit was set (see Section 7.7.1 *Control*).

## 7.2 REGISTER LIST

There are 2 complete register sets in the AHA4525 device: one for the encoder and one for the decoder. Registers used in both the encoder and decoder have the same address but are accessed through either the encoder or decoder data interface. In Table 5, the register bit name does not include the E for encoder register or D for decoder register when the register is common to both the encoder and decoder. Registers that are specific to the encoder or decoder are labelled with the E for encoder or D for decoder. All register bits labelled as "*res*" are reserved and must be written to 0. Reads from reserved registers return unpredictable values.

| REGISTER BIT NAME     | CONFIG    | ADDRESS      | BIT | REGISTER SECTION                               |  |  |  |  |

|-----------------------|-----------|--------------|-----|------------------------------------------------|--|--|--|--|

| ActualIterations[7:0] | read only | 0x3d         | 7:0 | Section 7.7.3 Actual Iterations (Decoder Only) |  |  |  |  |

| [,]                   | 0         | 0x11         | 3:0 |                                                |  |  |  |  |

|                       | 1         | 0x11         | 7:4 |                                                |  |  |  |  |

| BlkSize[11:8]         | 2         | 0x12         | 3:0 |                                                |  |  |  |  |

|                       | 3         | 0x12         | 7:4 |                                                |  |  |  |  |

|                       | 0         | 0x13         |     | Section 7.4.2 Block Size                       |  |  |  |  |

|                       | 1         | 0x14         | 7.0 |                                                |  |  |  |  |

| BlkSize[7:0]          | 2         | 0x15         | 7:0 |                                                |  |  |  |  |

|                       | 3         | 0x16         |     |                                                |  |  |  |  |

|                       | 0         | 0x09         |     |                                                |  |  |  |  |

| CodeV[2:0]            | 1         | 0x0b         | 7.1 |                                                |  |  |  |  |

| CodeX[3:0]            | 2         | 0x0d         | 7:4 |                                                |  |  |  |  |

|                       | 3         | 0x0f         |     | Section 7.4.1 TPC Constituent Code             |  |  |  |  |

|                       | 0         | 0x09         |     | Section 7.4.1 II C Constituent Code            |  |  |  |  |

| CodeY[3:0]            | 1         | 0x0b         | 3:0 |                                                |  |  |  |  |

| Code 1 [5.0]          | 2         | 0x0d         | 5.0 |                                                |  |  |  |  |

|                       | 3         | 0x0f         |     |                                                |  |  |  |  |

| Corrections[11:8]     | read only | 0x3b         | 3:0 | Section 7.7.2 Status and Correction Count      |  |  |  |  |

| Corrections[7:0]      | read only | 0x3c         | 7:0 | (Decoder Only)                                 |  |  |  |  |

| CRCEnable             | all       | 0x00         | 5   | Section 7.3.1 CRC and Scrambler Configuration  |  |  |  |  |

| CRCErr                | read only | 0x3b         | 4   | Section 7.7.2 Status and Correction Count      |  |  |  |  |

| CRCPoly[31:24]        |           | 0x01         |     | (Decoder Only)                                 |  |  |  |  |

| CRCPoly[31:24]        | -         | 0x01<br>0x02 |     |                                                |  |  |  |  |

| CRCPoly[15:8]         | all       | 0x02<br>0x03 | 7:0 | Section 7.3.1 CRC and Scrambler Configuration  |  |  |  |  |

| CRCPoly[7:0]          | { }       | 0x03<br>0x04 |     | Section 7.5.1 CRC and Scrumbler Configuration  |  |  |  |  |

| CRCSize[4:0]          | all       | 0x04         | 4:0 |                                                |  |  |  |  |

| DOutputECC            | all       | 0x00<br>0x0a |     | Section 7.4.1 TPC Constituent Code             |  |  |  |  |

|                       |           |              |     |                                                |  |  |  |  |

| DStatus               | all       | 0x26         | 6   | Section 7.7.1 Control                          |  |  |  |  |

#### Table 5: Register Bits - Alphabetical

PS4525\_0204

A subsidiary of Comtech Telecommunications Corporation

| REGISTER BIT NAME | CONFIG | ADDRESS | BIT             | REGISTER SECTION                                 |  |  |  |

|-------------------|--------|---------|-----------------|--------------------------------------------------|--|--|--|

|                   | 0      | 0x28    |                 |                                                  |  |  |  |

| EBufferSize[8]    | 1      | 0x29    | 7:0             | Section 7.4.3 Buffer Configuration (Encoder      |  |  |  |

| EDunerSize[0]     | 2      | 0x2a    | 7.0             | Only)                                            |  |  |  |

|                   | 3      | 0x2b    |                 |                                                  |  |  |  |

| EPassThrough      | all    | 0x0a    | 6               | Section 7.4.1 TPC Constituent Code               |  |  |  |

|                   | 0      | 0x28    |                 |                                                  |  |  |  |

| FeedbackX[4:0]    | 1      | 0x2a    | 4:0             |                                                  |  |  |  |

| Teedodek/[4.0]    | 2      | 0x2c    | <del>т</del> .0 |                                                  |  |  |  |

|                   | 3      | 0x2e    |                 |                                                  |  |  |  |

|                   | 0      | 0x28    |                 |                                                  |  |  |  |

| FeedbackY[4:2]    | 1      | 0x2a    | 7:5             | Section 7.4.5 Feedback (Decoder Only)            |  |  |  |

|                   | 2      | 0x2c    | 1.5             | Section 7:4.5 Freedback (Decoder Only)           |  |  |  |

|                   | 3      | 0x2e    |                 |                                                  |  |  |  |

|                   | 0      | 0x29    |                 |                                                  |  |  |  |

| FeedbackY[1:0]    | 1      | 0x2b    | 1:0             |                                                  |  |  |  |

| recuback I [1.0]  | 2      | 0x2d    |                 |                                                  |  |  |  |

|                   | 3      | 0x2f    |                 |                                                  |  |  |  |

| GOutConfig[2:0]   | all    | 0x26    | 5:3             | Section 7.7.1 Control                            |  |  |  |

|                   | 0      | 0x0a    |                 |                                                  |  |  |  |

| Helical           | 1      | 0x0c    | 7               | Section 7.4.1 TPC Constituent Code               |  |  |  |

| Tichcal           | 2      | 0x0e    | /               | Section 7:4.1 II C Constituent Code              |  |  |  |

|                   | 3      | 0x10    |                 |                                                  |  |  |  |

|                   | 0      | 0x36    |                 |                                                  |  |  |  |

| Iterations[7:0]   | 1      | 0x37    | 7:0             | Section 7.4.6 Iterations (Decoder Only)          |  |  |  |

| iterations[7.0]   | 2      | 0x38    | 7.0             | Section 7:4.0 nerations (Decoder Only)           |  |  |  |

|                   | 3      | 0x39    |                 |                                                  |  |  |  |

| NoBlock           | all    | 0x26    | 2               | Section 7.7.1 Control                            |  |  |  |

| NoConfig          | all    | 0X20    | 7               |                                                  |  |  |  |

| QBits[1:0]        | all    | 0x3a    | 3:2             | Section 7.5.1 <i>Quantization (Decoder Only)</i> |  |  |  |

| QMode[1:0]        | all    |         | 1:0             | Section 7:5:1 Quantization (Decoder Only)        |  |  |  |

| ScramEnable       | all    | 0x00    | 6               |                                                  |  |  |  |

| ScramPoly[15:8]   | all    | 0x05    |                 |                                                  |  |  |  |

| ScramPoly[7:0]    | all    | 0x06    | 7:0             | Section 7.3.1 CRC and Scrambler Configuration    |  |  |  |

| ScramSeed[15:8]   | all    | 0x07    | 7.0             |                                                  |  |  |  |

| ScramSeed[7:0]    | all    | 0x08    |                 |                                                  |  |  |  |

17

m

comtech aha corporation

|                             | 001/5/0   | 4000500 | DIT |                                        |  |  |  |  |