# 13-Bit to 26-Bit Registered Buffer

#### **Product Features**

- PI74 SSTV16859 is designed for low-voltage operation, V<sub>DD</sub>=V<sub>DDQ</sub>=2.3V to 2.7V

- Supports SSTL 2 Class II specifications on outputs

- All Inputs are SSTL\_2 Compatible, except RESET which is LVCMOS.

- Designed for DDR Memory

- · Flow-Through Architecture

- Packages:

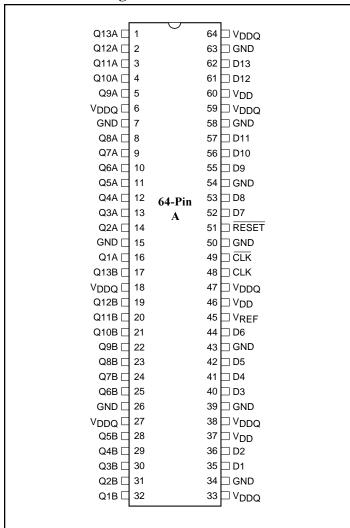

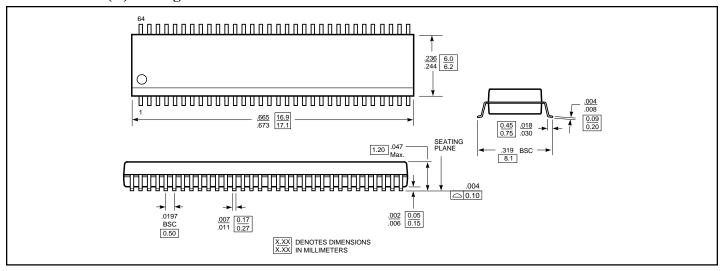

64-pin, 240-mil wide plastic TSSOP (A)

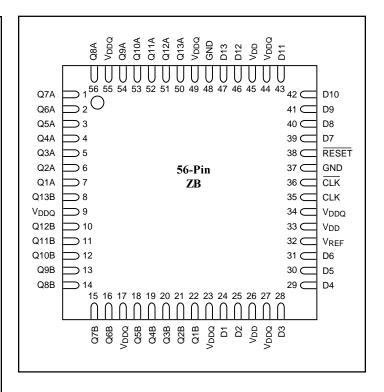

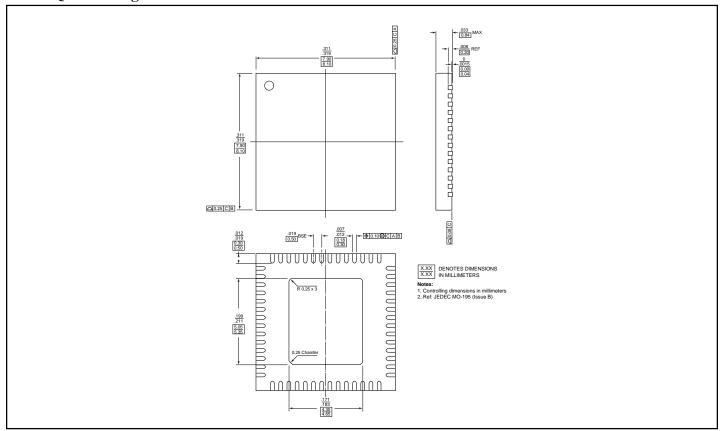

56-pin, Plastic Very Thin Fine Pitch Quad Flat No Lead QFN (ZB)

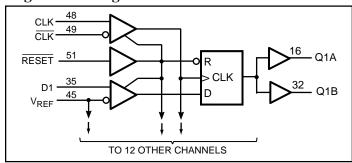

### Logic Block Diagram - TSSOP

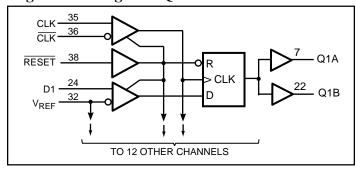

### Logic Block Diagram - QFN

### **Product Pin Description**

| Pin Name           | Description                              |  |  |  |

|--------------------|------------------------------------------|--|--|--|

| RESET              | Reset (Active Low) LVCMOS                |  |  |  |

| CLK                | Clock Input, Positive Differential Input |  |  |  |

| CLK                | Clock Input, Negative Differential Input |  |  |  |

| D                  | Data Input, D1-D13                       |  |  |  |

| Q                  | Data Output, Q1-Q13                      |  |  |  |

| GND                | Ground                                   |  |  |  |

| $V_{ m DD}$        | Core Supply Voltage, 2.5V Nominal        |  |  |  |

| $V_{\mathrm{DDQ}}$ | Output Supply Voltage, 2.5V Nominal      |  |  |  |

| $V_{ m REF}$       | Input Reference Voltage, 1.25V Nominal   |  |  |  |

## **Product Description**

Pericom Semiconductor's PI74SSTV16859 logic circuit is produced using the Company's advanced 0.35 micron CMOS technology, achieving industry leading speed.

All inputs are compatible with the JEDEC standard for SSTL\_2, except the LVCMOS reset (RESET) input. All outputs are SSTL\_2, Class II compatible.

The device operates from a differential clock (CLK and  $\overline{\text{CLK}}$ ). Data registered at the crossing of CLK going HIGH, and  $\overline{\text{CLK}}$  going LOW.

$\begin{array}{l} \underline{\mbox{The PI74SSTV16859}} \ supports \ low-power standby \ operation. \ When } \\ \overline{\mbox{RESET}} \ is \ LOW, \ the \ differential \ input \ receivers \ are \ disabled, \ and \ undriven \ (floating) \ data, \ clock \ and \ reference \ voltage \ (V_{REF}) \ inputs \ are \ allowed. \ In \ addition, \ when \ \overline{\mbox{RESET}} \ is \ LOW, \ all \ \underline{\mbox{registers}} \ are \ reset, \ and \ all \ outputs \ are \ forced \ LOW. \ The \ LVCMOS \ \overline{\mbox{RESET}} \ input \ must \ always \ be \ held \ at \ a \ valid \ logic \ HIGH \ or \ LOW \ level. \end{array}$

To ensure defined outputs from the register before a stable clock has been supplied,  $\overline{RESET}$  must be held in the LOW state during power up.

In the DDR DIMM application,  $\overline{RESET}$  is specified to be completely asynchronous with respect to CLK and  $\overline{CLK}$ . Therefore, no timing relationship can be guaranteed between the two. When entering  $\overline{RESET}$ , the register will be cleared and the outputs will be driven LOW quickly, relative to the time to disable the differential input receivers, thus ensuring no glitches on the output. However, when coming out of  $\overline{RESET}$ , the register will become active quickly, relative to the time to enable the differential input receivers. When the data inputs are LOW, and the clock is stable, during the time from the LOW-to-HIGH transition of  $\overline{RESET}$  until the input receivers are fully enabled, the design must ensure that the outputs will remain LOW.

Pericom's PI74SSTV16859 is characterized for operation from 0°C to 70°C.

#### Truth Table<sup>(1)</sup>

|       | Outputs          |                  |                  |                   |

|-------|------------------|------------------|------------------|-------------------|

| RESET | CLK              | CLK              | D                | Q                 |

| L     | X or<br>Floating | X or<br>Floating | X or<br>Floating | L                 |

| Н     | 1                | <b>\</b>         | Н                | Н                 |

| Н     | 1                | <b>\</b>         | L                | L                 |

| Н     | L or H           | L or H           | X                | Qo <sup>(2)</sup> |

#### Notes:

1. H = High Signal Level

L = Low Signal Level

↑ = Transition LOW-to-HIGH

$\downarrow$  = Transition HIGH-to-LOW

X = Irrelevant or floating

2. Output level before the indicated steady state input conditions were established.

### Product Pin Configurations

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 1. The input and output negative voltage ratings may be excluded if the input and output clamp ratings are observed.

- 2. This value is limited to 3.6V Maximum.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

**Maximum Ratings** (Above which the useful life may be impaired. For user guidelines, not tested.)

| Item                                                  | Symbol/<br>Conditions                                                     | Ratings                          | Units |

|-------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------|-------|

| Storage temperature                                   | $T_{stg}$                                                                 | -65 to 150                       | °C    |

| Supply voltage                                        | V <sub>DD</sub> or V <sub>DDQ</sub>                                       | -0.5 to 3.6                      |       |

| Input voltage <sup>(1,2)</sup>                        | $V_{\rm I}$                                                               | -0.5 to V <sub>DD</sub><br>+0.5  | V     |

| Output voltage <sup>(1,2)</sup>                       | $V_{\rm O}$                                                               | -0.5 to<br>V <sub>DDQ</sub> +0.5 |       |

| Input clamp current                                   | I <sub>IK</sub> , V <sub>I</sub> <0<br>or V <sub>I</sub> >V <sub>DD</sub> | ±50                              |       |

| Output clamp<br>current                               | $I_{OK}, V_O < 0$ or $V_O > V_{DDQ}$                                      | ±50                              | A     |

| Continuous output current                             | $I_{O}, V_{O} = 0$<br>to $V_{DDQ}$                                        | ±50                              | mA    |

| V <sub>DD</sub> , V <sub>DDQ</sub> or GND current/pin | I <sub>DD</sub> , I <sub>DDQ</sub><br>or I <sub>GND</sub>                 | ±100                             |       |

| Package Thermal Impedance <sup>(3)</sup>              | $	heta J_A$                                                               | 55                               | °C/W  |

# $\textbf{Recommended Operating Conditions}^{(4)}$

| Parameters       | Description                                |               | Min.                    | Nom.         | Max.                     | Units |

|------------------|--------------------------------------------|---------------|-------------------------|--------------|--------------------------|-------|

| V <sub>DD</sub>  | Supply Voltage                             |               | 2.3                     | 2.5          | 2.7                      |       |

| V <sub>DDQ</sub> | I/O Supply Voltage                         |               | 2.3                     | 2.5          | 2.7                      |       |

| V <sub>REF</sub> | Reference Voltage $V_{REF} = 0.5X V_{DDQ}$ |               | 1.15                    | 1.25         | 1.35                     |       |

| V <sub>TT</sub>  | Termination Voltage                        |               | V <sub>REF</sub> -0.04  | $V_{ m REF}$ | V <sub>REF</sub> +0.04   |       |

| VI               | Input Voltage                              |               | 0                       |              | V <sub>DD</sub>          |       |

| V <sub>IH</sub>  | AC High -Level Input Voltage               |               | V <sub>REF</sub> +310mV |              |                          |       |

| V <sub>IL</sub>  | AC Low -Level Input Voltage                | Data Issuesta |                         |              | V <sub>REF</sub> – 310mV | V     |

| V <sub>IH</sub>  | DC High -Level Input Voltage               | Data Inputs   | V <sub>REF</sub> +150mV |              |                          |       |

| V <sub>IL</sub>  | DC Low -Level Input Voltage                |               |                         |              | V <sub>REF</sub> –150mV  |       |

| V <sub>IH</sub>  | High -Level Input Voltage                  | DECET         | 1.7                     |              |                          |       |

| V <sub>IL</sub>  | Low -Level Input Voltage                   | RESET         |                         |              | 0.7                      |       |

| V <sub>ICR</sub> | Common-mode input range                    | CIV CIV       | 0.97                    |              | 1.53                     |       |

| $V_{ m ID}$      | Differential Input Voltage                 | CLK, CLK      | 360                     |              |                          |       |

| I <sub>OH</sub>  | High-Level Output Current                  |               |                         |              | -20                      | mA    |

| I <sub>OL</sub>  | Low-Level Output Current                   |               |                         |              | 20                       |       |

| T <sub>A</sub>   | Operating Free-Air Temperature             |               | 0                       |              | 70                       | °C    |

#### Note:

<sup>4.</sup> The  $\overline{RESET}$  input of the device must be held at  $V_{DD}$  or GND to ensure proper device operation. The differential inputs must not be floating, unless  $\overline{RESET}$  is LOW.

# **DC** Electrical Characteristics

(Over the Operating Range,  $T_A = 0$ °C to +70°C,  $V_{DD} = 2.5V \pm 200$ mV,  $V_{DDQ} = 2.5V \pm 200$ mV)

| Parameters               |                                                  | Test Conditions $V_{\mathrm{DD}}$                                                                                                                                                                                                      |             | Min.        | Тур.                 | Max. | Units |                                       |    |

|--------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------|------|-------|---------------------------------------|----|

| $V_{IK}$                 |                                                  | $I_{\rm I} = -18 \text{mA}$                                                                                                                                                                                                            |             | 2.3V        |                      |      | -1.2  |                                       |    |

|                          | 17                                               | $I_{OH} = -100 \mu A$                                                                                                                                                                                                                  |             | 2.3V-2.7V   | V <sub>DD</sub> -0.2 |      |       |                                       |    |

|                          | $V_{OH}$                                         | $I_{OH} = -16$ mA                                                                                                                                                                                                                      |             | 2.3V        | 1.95                 |      |       | V                                     |    |

|                          | <b>1</b> 7                                       | $I_{\rm OL} = 100 \mu A$                                                                                                                                                                                                               |             | 2.3V-2.7V   |                      |      | 0.2   |                                       |    |

|                          | $V_{OL}$                                         | I <sub>OH</sub> =16mA                                                                                                                                                                                                                  |             | 2.3V        |                      |      | 0.35  |                                       |    |

| $I_{\mathrm{I}}$         | All Inputs                                       | $V_{I} = V_{DD}$ or GND                                                                                                                                                                                                                |             | 2.7V        |                      |      | ±5    |                                       |    |

| Ţ                        | Standby<br>(Static)                              | RESET = GND                                                                                                                                                                                                                            |             |             |                      |      | 10    | μA                                    |    |

| $I_{DD}$                 | Operating (Static)                               | $\overline{RESET} = V_{DD},$ $V_{I} = V_{IH(AC)} \text{ or } V_{IL (AC)}$                                                                                                                                                              | $I^{O} = 0$ |             |                      |      |       | TBD                                   | mA |

|                          | Dynamic operating - clock only                   | $\overline{RESET} = V_{DD},$ $V_{I} = V_{IH(AC)} \text{ or } V_{IL(AC)},$ $CLK \text{ and } \overline{CLK} \text{ switching}$ $50\% \text{ duty cycle.}$                                                                               |             | 2.7V        |                      |      | TBD   | μΑ/<br>clock<br>MHz                   |    |

| I <sub>DDD</sub>         | Dynamic<br>Operating -<br>per each data<br>input | $\overline{RESET} = V_{DD},$ $V_{I} = V_{IH(AC)} \text{ or } V_{IL(AC)},$ $CLK \text{ and } \overline{CLK} \text{ switching } 50\%$ $duty \text{ cycle. One data input switching }$ at half clock frequency, 50% $duty \text{ cycle.}$ |             |             |                      |      | TBD   | μΑ/<br>clock<br>MHz/<br>data<br>input |    |

| r <sub>OH</sub>          | Output High                                      | $I_{O} = -20 \text{mA}$                                                                                                                                                                                                                |             | 22.4.27     | TDD                  |      | TDD   |                                       |    |

| $r_{\rm OL}$             | Output Low                                       | $I_{\rm O} = 20 {\rm mA}$                                                                                                                                                                                                              |             | 2.3 to 2.7V | TBD                  |      | TBD   | Ω                                     |    |

| $r_{\mathrm{O}(\Delta)}$ | r <sub>OH - rOL</sub>   each<br>separate bit     | $I_{O} = 20 \text{mA}, T_{A} = 25^{\circ}\text{C}$                                                                                                                                                                                     |             |             |                      |      | TBD   |                                       |    |

|                          | Data Inputs $V_I = V_{REF} \pm 350 \text{mV}$    |                                                                                                                                                                                                                                        | 2.5V        | 2.5         |                      | 2.5  |       |                                       |    |

| $C_{\mathbf{i}}$         | CLK and CLK                                      | $\overline{\zeta}$ $V_{ICR}$ =1.25V, $V_{I(PP)}$ = 360mV $V_{I}$ = $V_{DD}$ or GND                                                                                                                                                     |             |             | 2.5                  |      | 3.5   | pF                                    |    |

|                          | RESET                                            |                                                                                                                                                                                                                                        |             |             | TBD                  |      | TBD   |                                       |    |

# **Timing Requirements** (over recommended operating free-air temperature range, unless otherwise noted)

|                      |                                                                                                                                                                                                   |                          | $V_{DD} = 2.5V \pm 0.2V$ |      | I India |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|---------|

|                      |                                                                                                                                                                                                   |                          | Min.                     | Max. | Units   |

| $f_{clock}$          | Clock frequency                                                                                                                                                                                   |                          |                          | 200  | MHz     |

| $t_{\mathrm{W}}$     | Pulse Duration, CLK, CLK high or lo                                                                                                                                                               | W                        | 2.5                      |      |         |

| t <sub>act</sub> †   | Differential Inputs active time, data inputs must be low after RESET high.  Differential Inputs inactive time, data and clock inputs must be held at valid levels (not floating) after RESET Low. |                          | 22                       |      |         |

| t <sub>inact</sub> † |                                                                                                                                                                                                   |                          | 22                       |      |         |

|                      | Setup time, fast slew rate <sup>(5,7)</sup>                                                                                                                                                       | Data before CLK↑, CLK↓   | 0.75                     |      | ns      |

| $t_{ m su}$          | Setup time, slow slew rate <sup>(6,7)</sup>                                                                                                                                                       | Data before CLK 1, CLK 1 | 0.9                      |      |         |

| _                    | Hold time, fast slew rate <sup>(5,7)</sup>                                                                                                                                                        | Data after CLK↑, CLK↓    | 0.75                     |      |         |

| t <sub>h</sub>       | Hold time, slow slew rate <sup>(6,7)</sup>                                                                                                                                                        | Data after CLK 1, CLK    | 0.9                      |      |         |

- **Notes:** 5. For data signal input slew rate  $\geq 1 \text{ V/ns}$ .

- 6. For data signal input slew rate  $\geq 0.5 \text{V/ns}$  and < 1 V/ns.

- 7. CLK,  $\overline{\text{CLK}}$  signals input slew rates are  $\geq 1 \text{V/ns}$ .

- † This parameter is not necessarily production tested.

# **Switching characteristics**

Over recommended operating free-air temperature range, unless otherwise noted. (See test circuits and switching waveforms).

|                  |                       |             | $V_{DD} = 2.5V \pm 0.2V$ |      |      |       |

|------------------|-----------------------|-------------|--------------------------|------|------|-------|

| Parameter        | From (Input)          | To (Output) | Min.                     | Тур. | Max. | Units |

| f <sub>max</sub> |                       |             | 200                      |      |      | MHz   |

| $t_{\rm pd}$     | $CLK, \overline{CLK}$ | Q           | 1.1                      |      | 2.8  | ***   |

| $t_{ m phl}$     | RESET                 | Q           |                          |      | 5.0  | ns    |

5

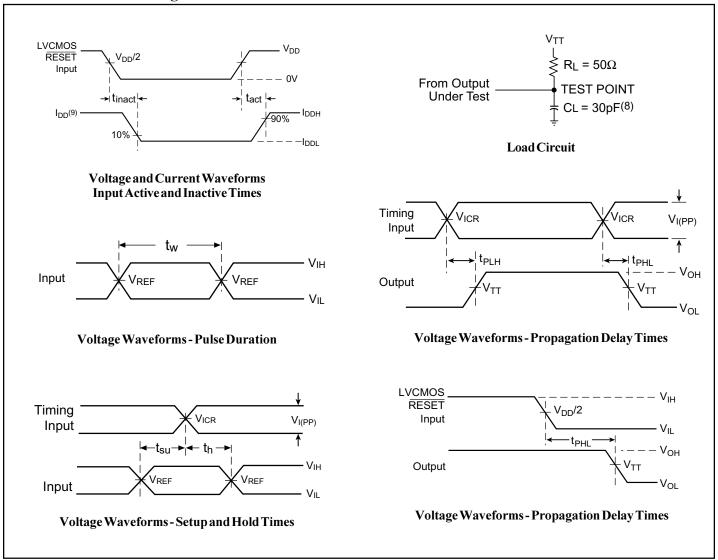

# Test Circuit and Switching Waveforms

Parameter Measurement Information ( $V_{DD}=2.5V\pm0.2V$ )

6

#### Notes:

- 8.  $C_L$  includes probe and jig capacitance.

- 9.  $I_{DD}$  tested with clock and data inputs held at  $V_{DD}$  or GND, and  $I_{O} = 0$ mA.

- 10. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$ 10 MHz,  $Z_{\rm O}$  = 50 ohms. Input slew rate = 1V/ns  $\pm$ 20% (unless otherwise specified).

- 11. The outputs are measured one at a time with one transition per measurement.

- 12.  $V_{TT} = V_{REF} = V_{DDQ}/2$

- 13.  $V_{IH} = V_{REF} + 350 \text{mV}$  (ac voltage levels) for SSTL inputs.  $V_{IH} = V_{DD}$  for LVCMOS input.

- 14.  $V_{IL} = V_{REF} + 350 \text{mV}$  (ac voltage levels) for SSTL inputs.  $V_{IL} = GND$  for LVCMOS input.

- 15.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

PS8508A 08/30/01

# 64-Pin TSSOP(A) Package

# 56-Pin QFN Package

# **Ordering Information**

| Ordering Code   | Package Type | Temperature Range |

|-----------------|--------------|-------------------|

| PI74SSTV16859A  | 64-Pin TSSOP | 090 45 7090       |

| PI74SSTV16859ZB | 56-Pin QFN   | 0°C to 70°C       |

# **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com